EMI預兼容排放測量軟件 - 手冊

2019-04-17 16:48:29

的產(chǎn)生原因是復雜的,音頻文件本身、DAC芯片的解碼、電源干擾、接地回路干擾、外部信號干擾都會產(chǎn)生底噪,而耳機的靈敏度也會影響底噪的大小。***吧網(wǎng)友給出的通過“降低小米手機推力”來提高聲音純凈...

2021-07-28 09:50:11

最近在測試TLV320AIC3106時,發(fā)現(xiàn)在設置增益后有不同程度的底噪。

測量無增益情況下(PGA=0dB),外部無信號輸入時,示波器的LRCLK與數(shù)據(jù)對應關系I2S主模式輸出

(16位的模式,從圖中至少可以看出后7-8位一直都有非0數(shù)據(jù)在變化)

是否可以認為這些都是噪聲?

2024-11-05 07:59:30

你好,我在使用AD9129中發(fā)現(xiàn),AD9129輸出會出現(xiàn)偶發(fā)性底噪過高,原因不明,出現(xiàn)幾率大約1/10,即對AD9129按照芯片手冊推薦的初始化序列進行配置后,有幾率會出現(xiàn)底噪過高,主信號還是有的

2023-12-12 08:33:13

你好,我在使用AD9129中發(fā)現(xiàn),AD9129輸出會出現(xiàn)偶發(fā)性底噪過高,原因不明,出現(xiàn)幾率大約1/10,即對AD9129按照芯片手冊推薦的初始化序列進行配置后,有幾率會出現(xiàn)底噪過高,主信號還是有的

2018-08-13 09:28:39

為了更好的摸底使用AD9694,根據(jù)ad9694-500ebz制作了一個小DEMO板,但是自己做的這個板子數(shù)據(jù)采集回來底噪在-98dbc左右(不加模擬時鐘,空采),同樣情況下我用ADI

2023-12-04 06:11:17

ADAU1372ADAU1777ADAU1702 等等這些codec芯片,在未加載程序時,DAC的模擬輸出端噪聲(底噪)+紋波只有4mV左右;但是在加載了任何程序之后,就出現(xiàn)輸出端的噪聲(底噪)+紋波變成50mV。這個是用的官方的評估板測試的。想問這是什么原因?如何進行改善?

2023-11-29 06:40:53

問一個ADC AD9628-125的問題,使用中發(fā)現(xiàn),采樣輸出信號的底噪與輸入信號功率關系密切,沒有輸入信號,噪底很干凈,噪聲水平與預期相當,使用19MHz -16dBm的單音輸入測試,顯示spur

2023-12-06 06:51:41

來自網(wǎng)友的提問: 我用16位的ADC的輸入短接到共模電平上, 把輸出數(shù)據(jù)直接分析,發(fā)現(xiàn)最小2位數(shù)一直在變,這兩位應該是噪聲吧,算下來大約是1.08mV.改用電池供電以后,這個值也差不多.請問底噪有這么大的噪聲么?都短路了.一般的ADC能直接輸出幾位的精度呢?

2018-11-02 09:25:41

AIC3104如果關掉AGC,PGA設置為0,無環(huán)境底噪,聲音聽起來不錯,但是靈敏度很差,必須嘴對著MIC說話才有很好的效果,PGA設置越高,環(huán)境底噪就越大。

如果開啟AGC,PGA設置為0,無論

2024-10-23 06:17:09

的底噪;

4、對AIC3106的內(nèi)部相關寄存器進行重新配置,最終得到如附件中的音頻文件,戴耳機,把電腦音量調(diào)到最大,也會有底噪。

請問有沒有其它好的辦法把此類底噪濾除?

2024-11-04 08:03:36

HMC702開啟掃頻模式,噪底會比單點頻輸出時的噪底惡化10dB左右,而且,在恢復回點頻輸出以后,噪底不會恢復,只有reset后才恢復,我想請問一下這是什么原因,以及怎么解決這個問題,謝謝!

2018-08-22 07:26:40

把ADC教接地,也有-60dB左右底噪。

請問

1.有辦法測試codec I2S輸出數(shù)據(jù)噪聲,諧波數(shù)據(jù)嗎?(方便判斷是PCM1864引入還是DSP C5517引入)

2.諧波及底噪可能會是由什么引入的呢?

2024-10-15 06:17:32

我用PGA280+AD7765進行信號采集。

發(fā)現(xiàn)只有AD7765輸入端短接,噪底很低。但是PGA280+AD7765一起測試,輸入端短接的時候噪底很高,請問是為什么啊。

下面是原理圖。

2024-08-09 07:27:12

探頭3、一個20 dB寬帶預放 八、EMI測試軟件ES-SCANR&S?ES-SCAN是一個應用于ESRP、ESL和ESPI預兼容EMI測試接收機的經(jīng)濟型Windows應用程序,同時也

2019-10-15 14:29:54

我的問題如下

1. 隨著PGA音量的抬高是不是同時將底噪也進行了放大?

2. 這樣的放大是不是芯片固有的現(xiàn)象?能否進一步降低頻譜底噪?

2024-10-24 06:15:29

您好!有個問題想請教下,望指導,該項目比較緊急。具體問題如下:

1.問題描述:現(xiàn)在做的是一款藍牙耳機,藍牙主控是用CSR的芯片,耳放芯片用的是TPA2012D2,現(xiàn)在出現(xiàn)的問題是底噪很大

2024-08-20 06:13:50

3100D2的底噪問題怎么解決?謝謝

2024-10-31 06:58:18

TPA3118底噪里面有滋滋聲音,電源的輸入電容很靠近芯片了,然后總是有滋滋聲

2024-10-12 08:09:41

在測試TPA6304的信噪比時發(fā)現(xiàn),輸出1Vrms時的信噪比只有74dB(要求>80dB),底噪在220uV(6304的SPEC在60uV),麻煩提供優(yōu)化建議,謝謝。附件是測試報告,PCB和原理圖。

2024-09-30 06:19:41

ad8376將底噪抬高!如何解決!

2023-11-27 08:00:46

我在測量ad性能時,對ad采集到的信號作fft,得到的幅頻圖通常如下圖所示,我的疑問是:底噪之上除了信號和諧波外的譜線是什么,它們?yōu)槭裁磿霈F(xiàn),受什么因素影響?期待大佬答疑解惑,感激不盡!

2022-02-16 23:17:45

輸入(斷開電路),依然有比較大的底噪,初步確定為3106本身存在底噪,

錄音文件見附件,

請問要怎么去消除或者降低這個底噪?

2024-10-12 08:23:44

用于汽車音頻系統(tǒng)設計,經(jīng)常會出現(xiàn)噪底太大,產(chǎn)生人耳在安靜的環(huán)境下就能感受到的雜聲,能不能以反傾銷 1401為例幫分析下我們一般汽車應用中這種噪底主要產(chǎn)生源?降低這些噪底有啥一般有效的方法?例如結合吉瑪斯圖軟件算法的一些建議啥的。

2023-11-29 07:51:32

為什么底噪的好壞關乎著示波器的生產(chǎn)力?

2021-05-10 06:27:07

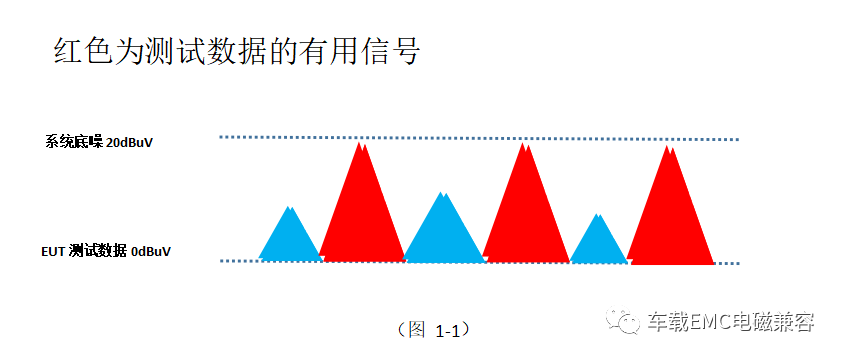

了輻射源的噪聲。一般我們認為測試過程中,底噪的水平是保持不變的。因此,我們要求底噪比限值低6dB以上,這樣便可以確保測試時只要抬升超過6dB,就說明輻射源的噪聲功率超過了背景噪聲,可以確保測試的準確性

2023-05-08 16:43:48

低噪放輸入端連接濾波器后,低噪放的增益會下降9db,求助各位大神分析原因?

2021-11-05 15:20:11

在測試1298底噪的時候,部分通道出現(xiàn)了尖峰噪聲,見下圖(從下至上依次為通道1~8,縱軸單位uV)。

通道2、6、8出現(xiàn)了不同程度上的尖峰,請問各位,這一般可能是由什么原因引起的?

2024-12-10 06:51:00

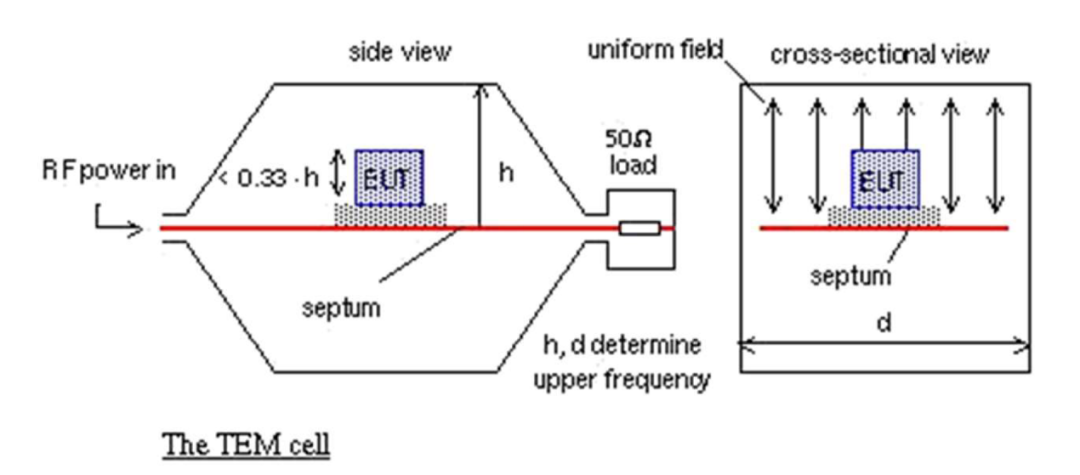

抑制噪訊的發(fā)生,有鑒于此本文要探討如何在PCB的Layout階段,充分應用改善技巧抑制EMI噪訊的強度。測試條件如圖1所示測試場地為室內(nèi)3m半電波暗室,預定測試頻率范圍為30MHz~1000MHz的電

2020-10-21 16:00:27

問題:如何通過驅動高功率LED降低EMI?

2019-03-05 14:33:29

寬帶預放 EMI測試軟件ES-SCANR&S?ES-SCAN是一個應用于ESRP、ESL和ESPI預兼容EMI測試接收機的經(jīng)濟型Windows應用程序,同時也可支持ESCI,F(xiàn)SL以及

2019-11-19 09:18:21

為什么錄音底噪很大,沙沙的聲音。應該從哪些方面降低呢?有沒有哪位同仁給下建議

2021-12-30 06:59:55

學習階段,求問26-34G寬帶低噪放后兩級的反饋為什么可以實現(xiàn)降低低頻增益,提高低頻穩(wěn)定性的。

2021-06-25 07:56:16

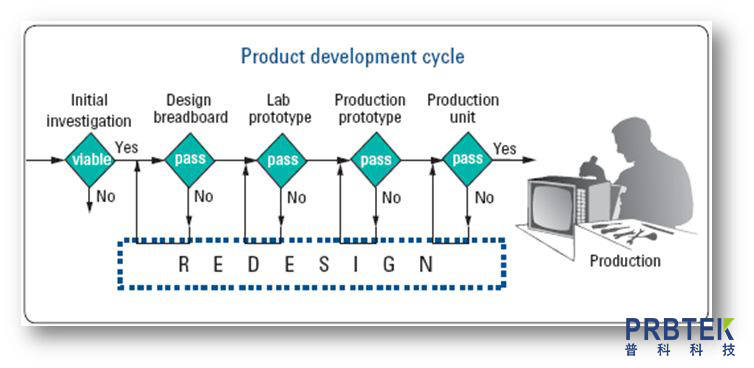

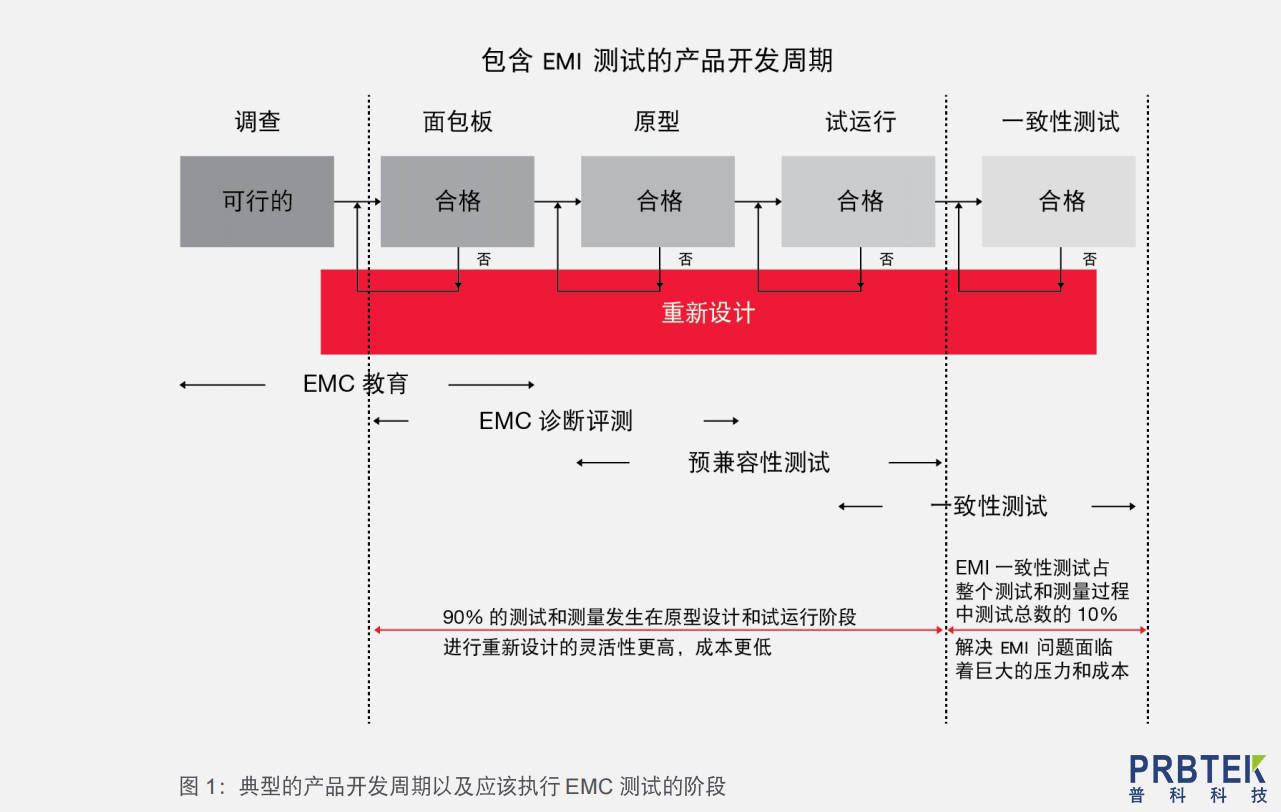

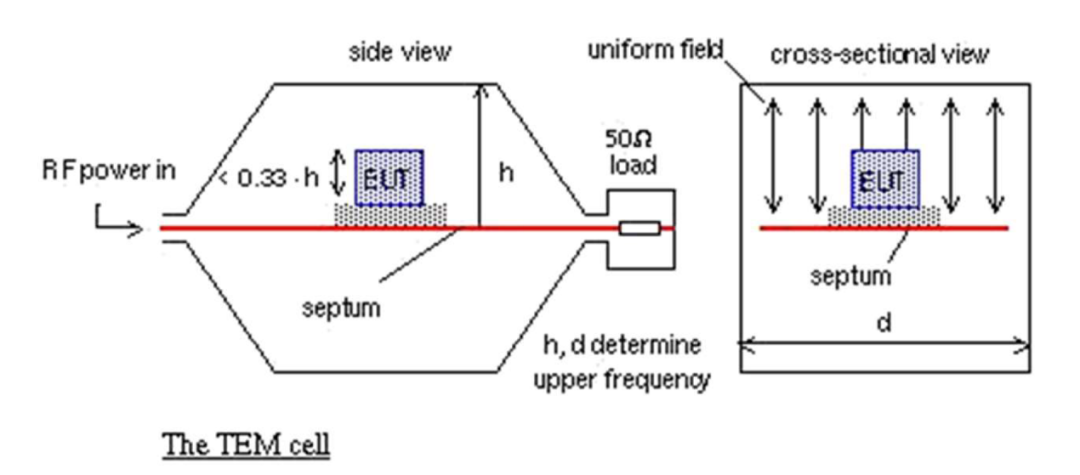

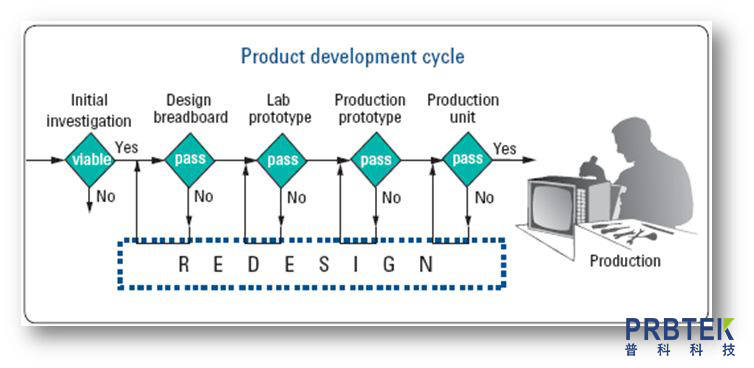

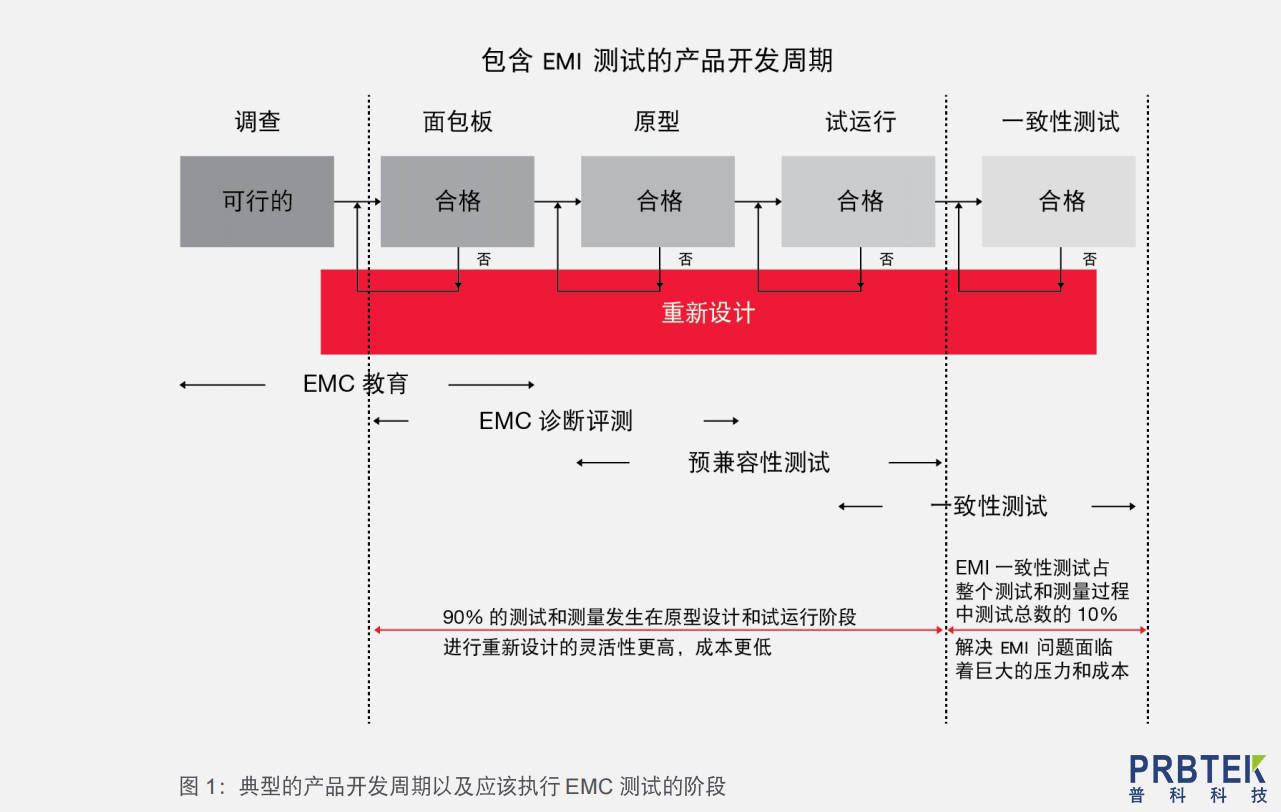

本文將重點考察EMI和RFI測試。由于測試難度和測試成本,這個階段經(jīng)常被忽略。但是,隨著設計期限的迫近,忽略這個步驟可能會導致意外事件和延遲。我們強烈推薦在設計早期測試EMC問題,以避免不必要

2016-09-07 15:42:10

ADAU1372 \ ADAU1777 \ ADAU1702 等等這些CODEC芯片,在沒有加載程序時,DAC的模擬輸出端噪聲(底噪)+紋波只有4mV左右;但是在加載了任何程序之后,就出現(xiàn)輸出端的噪聲(底噪)+紋波變成50mV。這個是用的官方的評估板測試的。想問這是什么原因?如何進行改善?

2018-08-06 07:05:57

用于汽車音頻系統(tǒng)設計,經(jīng)常會出現(xiàn)噪底太大,產(chǎn)生人耳在安靜的環(huán)境下就能感受到的雜聲,能不能以ADAU1401為例幫分析下我們一般汽車應用中這種噪底主要產(chǎn)生源?降低這些噪底有啥一般有效的方法?例如結合SigmaStudio軟件算法的一些建議啥的。

2018-08-03 08:06:01

ADAU1372\ADAU1777\ADAU1702 等等這些codec芯片,在未加載程序時,DAC的模擬輸出端噪聲(底噪)+紋波只有4mV左右;但是在加載了任何程序之后,就出現(xiàn)輸出端的噪聲(底噪)+紋波變成50mV。這個是用的官方的評估板測試的。想問這是什么原因?如何進行改善?

2018-08-06 09:04:43

為什么經(jīng)過ADC采樣后,我用matlab仿真后,底噪在-100左右,而ADC芯片資料上都在-120左右,請問如何降低ADC的底噪?analogchina-admin

2018-08-09 08:40:04

為什么經(jīng)過ADC采樣后,我用matlab仿真后,底噪在-100左右,而ADC芯片資料上都在-120左右,請問如何降低ADC的底噪?

2023-12-12 06:56:44

1kHz,1Vrms的正弦波數(shù)字信號輸入至DAC8830,在測試點TP107處進行模擬信號測量(斷開了后級電路),測得輸出信號頻譜如下圖,噪底基本在-100dBV以下,信號質(zhì)量可以接受。

但由于實際使用

2024-11-13 07:59:18

ad8376將底噪抬高!如何解決!見圖!測試條件!輸入輸出與外界斷開!5V外部電源 單獨供電!標準匹配 實際 需要輸入信號為70M帶寬28M調(diào)制信號!附件085628g83mmmj6mw5bwqqm.png80.8 KB085633b93i9j431fpadg8g.png85.7 KB

2018-11-13 15:05:52

關于耳機放大芯片設計初期未能消除的底噪,用戶有方法將其降低嗎

2019-05-08 07:55:38

請問音頻底噪測試時,應該在音頻信號分析儀上如何設置濾波器?是否還要添加硬件濾波器?

a-weight濾波器具體是啥意思,怎么個算法?是否有a-weight濾波器的相關paper文檔

2024-11-04 08:09:54

各位大牛:

麻煩請教一個問題,運算放大器的底噪這個如何獲取啊??就是用頻譜分析儀看一個低通濾波器的質(zhì)量,但是發(fā)現(xiàn)底噪好大,雜散很多,請問這個從放大器的那個指標可以計算理論的啊

2023-11-20 07:10:42

適合于汽車電子的經(jīng)濟高效的EMI預兼容測試系統(tǒng)汽車電子企業(yè),由于產(chǎn)品本身體積很小,但是又需要和整車一起進行電磁兼容測試,因此在建設電磁兼容測試手段時,需要慎重考慮。能容下汽車整車的暗室,其建設成

2009-10-06 12:19:16

、適用研發(fā)和生產(chǎn)的EMI預認證方案測試方向:電源傳導干擾和3GHz近場輻射干擾測試專業(yè)EMI接收機方案本套配備9kHz~3GHz EMI測試專業(yè)接收機、LISN網(wǎng)絡、五件套3G近場探頭和近場探頭預放

2020-09-04 17:46:04

就太遲了,從而導致解決問題所付出的代價太大,因此EMI預認證測試技術,使得在產(chǎn)品研制的過程中能通過EMI預測試手段來發(fā)現(xiàn)問題,以使設計人員有針對性的采取措施較早地解決問題,降低糾錯成本并提高認證測試

2019-07-23 06:21:37

你好,咨詢一個有關鎖相環(huán)芯片的問題: 使用ADIsimPLL仿真軟件進行仿真,發(fā)現(xiàn)鎖相環(huán)芯片4152HV芯片底噪在低頻處是平的,而其它芯片,比如ADF4002芯片底噪包含1/f噪聲,請問這是什么原因

2019-02-19 10:07:02

電子產(chǎn)品發(fā)展使得EMI問題越來越復雜多樣化,幾乎所有電子硬件工程師工作上都會面臨不同程度電磁波干擾(EMI)問題,本文將從基礎物理角度說明EMI信噪定義與判別

2010-10-26 15:33:25 723

723 不僅耳機存在信噪比的問題,電子測試設備同樣很關注信噪比,就如示波器,其本底噪聲(簡稱底噪)就是一個非常關鍵的參數(shù)。

2014-08-01 15:58:43 4651

4651 。Mostengineers采用良好的設計實踐,以盡量減少EMI問題的可能性。發(fā)送之前的產(chǎn)品出符合testing.These技術,降低風險,是今天常見的設計過程中進行預一致性測試和原型階段,以確定并解決潛在的EMI問題,該產(chǎn)品將在測試中完成最后階段。 通過文檔,可了解以下內(nèi)容:

2016-04-20 14:07:28 269

269 如何使用頻譜分析儀進行低成本的EMI預一致性測試 RSA306 EMI

2016-06-06 15:09:14 40

40 更強的魯棒性。因此美國國家半導體開發(fā)出具有增強對EMI魯棒性的運放以克服電磁干擾的問題。連同這些EMI輻射加固運放,我們將引入一種參數(shù)以明確定這種運放的EMI魯棒性:EMI抑制比(EMIRR)。本應注釋介紹了EMIRR參數(shù)的背景,細節(jié)和使用。

2017-06-12 10:08:05 7

7 靜噪基礎第一章,需要EMI靜噪濾波器(EMIFIL?)的原因

2018-01-24 16:09:01 9

9 靜噪基礎第六章,EMI靜噪濾波器

2018-01-24 16:25:01 4

4 Agilent 射頻產(chǎn)品市場拓展工程師 李健 著重介紹安捷倫全新EMI預兼容測試方案。在電源產(chǎn)品中,開關電路在高頻通斷過程中不可避免會產(chǎn)生電磁干擾。而電源設計和生產(chǎn)廠商在解決電磁干擾的過程中,往往受

2018-06-25 11:40:00 5033

5033 EMI 故障排查:通過觀察干擾信號的頻譜,優(yōu)化設計,提高 EMI 一致性測試通過率。

2018-10-17 16:34:00 6198

6198 RS預兼容EMI測試解決方案的用途:依據(jù)企業(yè)內(nèi)部或者民標/軍標進行傳導輻射EMI測量。這些解決方案能夠在產(chǎn)品設計和研發(fā)的初期,給元器件,模塊,和設備制造商提供有效的幫助,使研發(fā)人員可以提前采取相應

2020-07-23 16:48:17 741

741 RS預兼容EMI測試解決方案的用途:依據(jù)企業(yè)內(nèi)部或者民標/軍標進行傳導輻射EMI測量。這些解決方案能夠在產(chǎn)品設計和研發(fā)的初期,給元器件,模塊,和設備制造商提供有效的幫助,使研發(fā)人員可以提前采取相應

2020-07-23 16:40:03 1300

1300 EMI測試成本高,同時,為了滿足合規(guī)要求,能有效降低EMI的設計又是十分重要的。充分了解產(chǎn)生電磁場的來源可為低EMI設計奠定堅實的基礎。

2020-01-21 16:48:00 2602

2602

RIGOL的EMI量測應用提供完整的EMI 預合規(guī)測試解決方案,包括掃描,峰值測試,限制線和多個同時CISPR檢波器。通過EMI量測模式,工程師可以在整個設計過程中比較,分析EMI問題并生成報告

2020-03-15 10:56:15 1322

1322 就太遲了,從而導致解決問題所 付出的代價太大,因此EMI預認證測試技術,使得在產(chǎn)品研制的過程中能通過EMI預測試手段來發(fā)現(xiàn)問題,以使設計人員有針 對性的采取措施較早地解決問題,降低糾錯成本并提高認證測試的一次性通過率。 在中國電子工

2020-12-29 10:28:00 0

0 2020國際電磁兼容暨微波天線展覽會 將于2020年10月27日-29日在上海舉行 是德科技參展展位號:#405 期待您的到來! 是德科技作為測試測量領域的領導者,將在展會上展出面向EMI預兼容測試

2020-10-22 09:52:43 3127

3127 某品牌平板電腦制造商,由于前期沒有做 EMI 診斷測試,送機構檢測 EMI認證不通過,在測試+整改數(shù)月后仍沒法改善,導致生產(chǎn)滯后,市場被競爭對手占據(jù),損失超過千萬。

2022-03-18 17:04:43 7193

7193 一般情況下量產(chǎn)的芯片的底噪都是正常值,幾百微幅,但在實際使用中會遇到各種各樣的底噪,先判斷底噪是怎么產(chǎn)生,底噪的產(chǎn)生有三種類型。

2022-11-09 16:07:36 9351

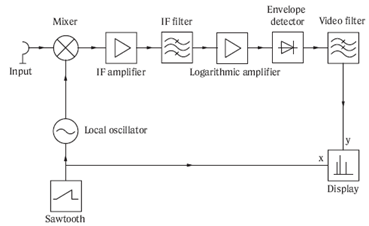

9351 ±5dBm范圍之內(nèi),太強可能導致頻譜儀過載。 直接標定法操作步驟(推薦) : Step 1:設置合適的中心頻率和Span,使得能夠顯示信號頻譜并覆蓋需要測試的頻偏范圍。 Step 2:將頻譜儀射頻前端衰減度設置為0dB,以降低底噪,提高相噪測試精度,這一

2022-12-13 15:36:01 1464

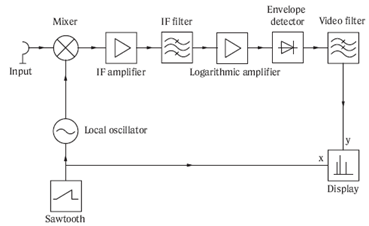

1464 開始研習頻譜儀原理的時候,曾經(jīng)有過這樣的疑惑“為什么降低VBW不會降低底噪”。

2023-06-13 11:20:26 11573

11573

EMI 預兼容測試和 EMI 故障排查 避免產(chǎn)品整體研發(fā)完成后才交付 EMI 實驗室進行測試 EMI 預兼容測試:在最早的時間發(fā)現(xiàn)電磁干擾的問題 EMI 故障排查:通過觀察干擾信號的頻譜,優(yōu)化

2024-04-01 10:31:23 1099

1099

的高頻擾竄電網(wǎng),或對設備和應用環(huán)境造成干擾。 EMI不管是國內(nèi)還是國外標準或者認證,基本都會涉及到EMI測試,如果前期設計產(chǎn)品的時候沒有考慮到EMI,那么等產(chǎn)品出來做認證的時候,就會導致因測試不過拿不到相關證書,之前的產(chǎn)品又要重新設計,花費大量的人力物力,得不償失。

2024-04-08 12:00:37 1297

1297 底噪,也稱為背景噪聲,是指在沒有輸入信號時示波器屏幕上顯示的隨機波動。測量底噪對于評估示波器的性能和確定測量系統(tǒng)的噪聲水平非常重要。

2024-05-30 16:38:24 4328

4328 頻譜分析儀是電子測量領域中最常用的儀器之一,它可以實現(xiàn)對信號頻譜特性的測量和分析。在進行各種信號測試時,頻譜分析儀的性能指標都會對測量結果產(chǎn)生一定的影響。其中,頻譜分析儀的底噪水平是一個非常關鍵

2024-06-18 11:17:39 1039

1039

通信系統(tǒng)和廣播系統(tǒng)到各種電子元器件,它們可以生成猝發(fā)、脈沖、連續(xù)波或調(diào)制信號。 為了使產(chǎn)品可以進入全球市場,電子設備制造商必須遵守特定地區(qū)或國家的EMC 法規(guī),確保其設備符合法規(guī)要求。 EMI 預兼容性測試的意義 1. 降低項目結束時達不到EMI 要求

2024-07-08 11:12:51 1225

1225

電子發(fā)燒友網(wǎng)站提供《超低底噪、低EMI、帶PBTL、2x30W 立體聲音頻功率放大器LTK52205數(shù)據(jù)手冊.pdf》資料免費下載

2024-08-12 15:03:38 15

15 為確保產(chǎn)品符合電磁兼容性(EMC)標準,能夠穩(wěn)定可靠地運行,許多企業(yè)會對產(chǎn)品進行EMI測試,從而提升品質(zhì)競爭力以及降低成本風險,滿足客戶需求。傳統(tǒng)的EMI輻射發(fā)射測試通常在具有大型屏蔽室的認證

2024-09-04 17:24:48 1278

1278

,EMI測試在產(chǎn)品設計早期階段的介入是必要的。一般來說,電子類產(chǎn)品開發(fā)過程中,EMI測試的實施常分為:EMI診斷和調(diào)試、EMI預認證測試、EMI一致性測試這幾個階段

2025-05-16 19:00:10 631

631

顯示的跡線,也很好的顯示了示波器的底噪。這個底噪對于示波器是不可避免的,主要由前端和ADC等有源器件引起。今天我們就來測試一下這個底噪。測試準備在測試之前,先將示波

2025-05-21 17:33:58 835

835

2024年9月,是德科技發(fā)布了全新硬件14bitADC的臺式示波器,它采用了UXR示波器的超低底噪前端技術,將示波器的噪聲水平大幅度降低。基于14bitADC和低噪聲模擬前端技術,HD3示波器的底噪

2025-12-03 17:32:01 495

495

電子發(fā)燒友App

電子發(fā)燒友App

評論