本文介紹了時(shí)鐘擴(kuò)頻技術(shù)的原理、分類,結(jié)合它在攝像頭的具體應(yīng)用案例,與傳統(tǒng)EMI抑制手段的實(shí)際效果進(jìn)行對比,突顯時(shí)鐘擴(kuò)頻技術(shù)在抑制時(shí)鐘EMI上的優(yōu)勢。目前,時(shí)鐘擴(kuò)展頻譜技術(shù)被廣泛使用在圖像采集、圖像

2018-05-18 02:13:00 3137

3137

在多時(shí)鐘設(shè)計(jì)中可能需要進(jìn)行時(shí)鐘的切換。由于時(shí)鐘之間可能存在相位、頻率等差異,直接切換時(shí)鐘可能導(dǎo)致產(chǎn)生glitch。

2020-09-24 11:20:38 6410

6410

01、如何決定FPGA中需要什么樣的時(shí)鐘速率 設(shè)計(jì)中最快的時(shí)鐘將確定 FPGA 必須能處理的時(shí)鐘速率。最快時(shí)鐘速率由設(shè)計(jì)中兩個(gè)觸發(fā)器之間一個(gè)信號的傳輸時(shí)間 P 來決定,如果 P 大于時(shí)鐘周期 T,則

2020-11-23 13:08:24 4644

4644

跨時(shí)鐘域路徑分析報(bào)告分析從一個(gè)時(shí)鐘域(源時(shí)鐘)跨越到另一個(gè)時(shí)鐘域(目標(biāo)時(shí)鐘)的時(shí)序路徑。

2020-11-27 11:11:39 6743

6743

信號回溝,即波形邊緣的非單調(diào)性,是時(shí)鐘的大忌,尤其是出現(xiàn)在信號的門限電平范圍內(nèi)時(shí),由于容易導(dǎo)致誤觸發(fā),更是兇險(xiǎn)無比。所以當(dāng)客戶測試發(fā)現(xiàn)時(shí)鐘信號回溝,抱著一心改板的沉痛心情找到高速先生時(shí),高速先生

2020-11-26 09:58:01 10822

10822 今天我們將討論時(shí)鐘如何影響精密 ADC,涉及時(shí)鐘抖動(dòng)、時(shí)鐘互調(diào)和時(shí)鐘的最佳 PCB 布局實(shí)踐。

2023-04-11 09:13:22 2034

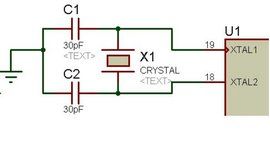

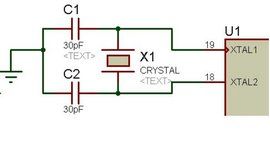

2034 上篇文章我們講了時(shí)鐘信號的幾個(gè)重要參數(shù),今天我們簡單講一下在設(shè)計(jì)中最常用到的幾種時(shí)鐘信號產(chǎn)生的方法,由于篇幅限制,我們不對具體的原理進(jìn)行講述,有興趣的朋友可以在網(wǎng)上搜索相應(yīng)的文章進(jìn)行深入了解,另外

2019-06-05 04:20:28

PLL不僅被廣泛用在通信系統(tǒng)中產(chǎn)生方便調(diào)節(jié)的不同頻點(diǎn)的高頻率本振信號(LO),還被廣泛用在處理器、FPGA、通信器件中用于生成器件內(nèi)部的高速時(shí)鐘。USB接口芯片的時(shí)鐘產(chǎn)生及內(nèi)部PLLDDS生成任意頻率

2019-06-06 04:20:03

了這些寄生信號。整合 BB 濾波器可最大限度地消除這些寄生信號。本文將探討這些寄生信號是如何出現(xiàn)在調(diào)制器輸出端的。圖 1:OIP3 測量頻譜分析儀截圖在圖 1 所示的頻譜分析儀截圖中,有兩個(gè) RF

2018-09-19 14:43:36

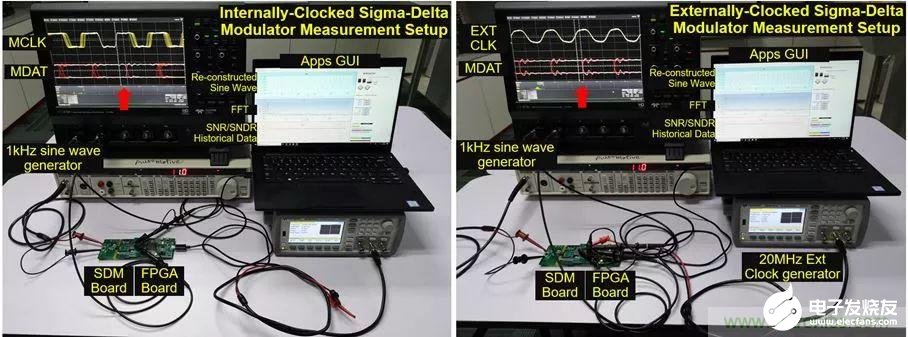

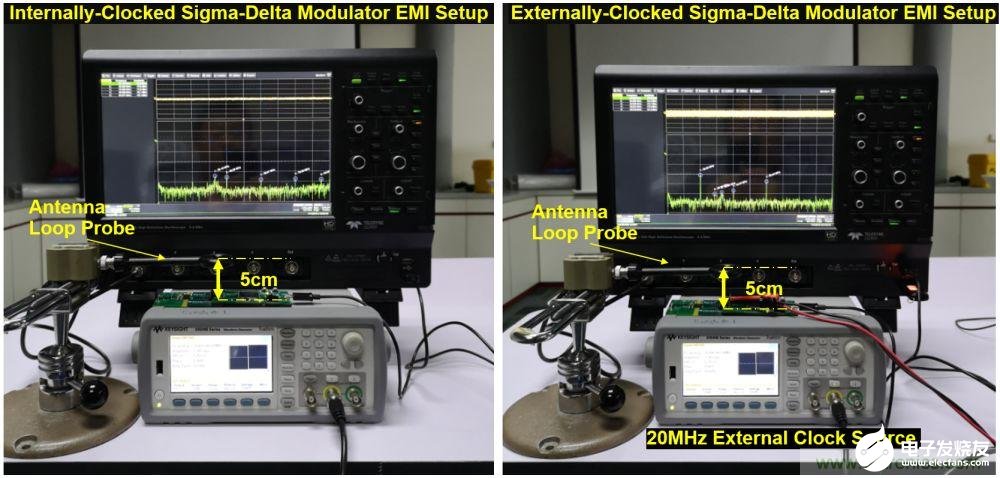

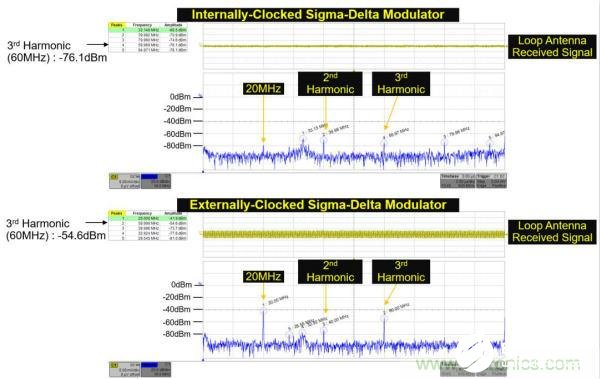

設(shè)置,用于測量兩類Σ-Δ調(diào)制器的時(shí)鐘信號的EMI從圖6中示波器捕獲的圖像可以清楚看出,外時(shí)鐘源產(chǎn)生的EMI要高得多,在時(shí)鐘信號頻率及其諧波處達(dá)到峰值。例如,對于60MHz的三次諧波,外時(shí)鐘源產(chǎn)生的EMI比內(nèi)時(shí)鐘Σ-Δ調(diào)制器輸出時(shí)鐘信號的高20dB。

2020-10-21 16:12:12

速率時(shí)鐘或數(shù)據(jù)將被破壞。(使用瞬態(tài)脈沖頻率為100 kHz。)操作理論電路信息AD7400A隔離∑-Δ調(diào)制器將模擬輸入信號轉(zhuǎn)換為高速(10 MHz典型)的單位數(shù)據(jù)流;調(diào)制器的單位數(shù)據(jù)的時(shí)間平均值與輸入

2020-09-25 17:55:01

什么是時(shí)鐘脈沖?為什么CPU需要時(shí)鐘?CPU的時(shí)鐘信號是如何產(chǎn)生的?

2021-10-20 07:21:14

包括有源晶振、無源晶振、時(shí)鐘產(chǎn)生器等。MCG 模塊提供九種不同的工作模式,分別是:鎖頻環(huán)片內(nèi)時(shí)鐘模式( FEI),鎖頻環(huán)片外時(shí)鐘模式(FEE),鎖頻環(huán)旁路片內(nèi)時(shí)鐘模式(FBI),鎖頻環(huán)旁路片外時(shí)鐘模式

2015-02-10 15:39:48

(HSE,HSI,LSE,LSI)產(chǎn)生的過程比430簡單許多,430的幾個(gè)時(shí)鐘源(XT1CLK,XT2CLK,VLOCLK,REFOCLK,DCOCLK,DLOCLKDIV)在產(chǎn)生時(shí)還有一些基礎(chǔ)的配置。二、時(shí)鐘源產(chǎn)生模塊分析1、osc模塊這一部分是外接了一個(gè)振蕩器(可以是手表晶體振蕩器、標(biāo).

2022-02-15 06:17:26

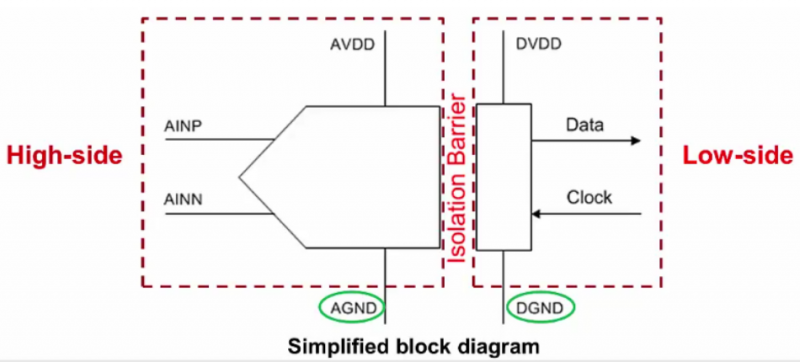

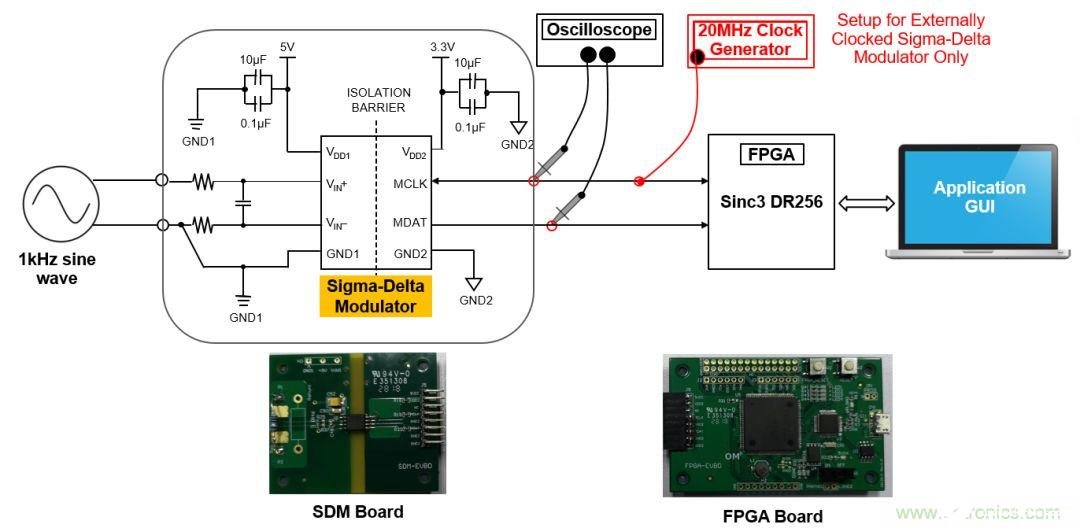

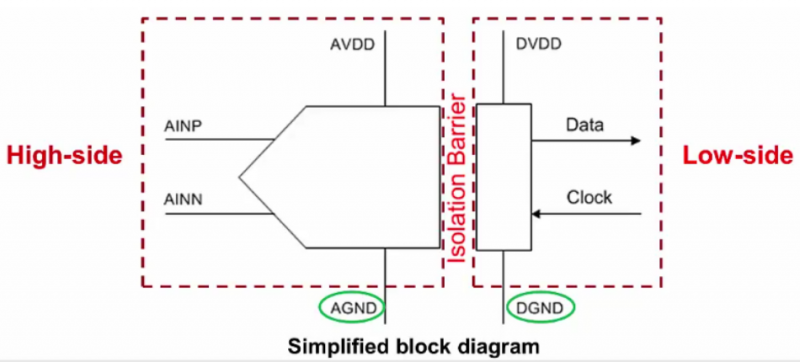

的基本分析開始,如圖1所示。 圖 1:Δ-Σ調(diào)制器內(nèi)部框圖 調(diào)制器根據(jù)調(diào)制器時(shí)鐘運(yùn)行,決定了輸入的采樣間隔。調(diào)制循環(huán)通過對輸入采樣和1位DAC之間的差分進(jìn)行積分而開始。比較器根據(jù)積分器值確定下一個(gè)調(diào)制器

2019-08-12 04:45:06

我使用FPGA產(chǎn)生一個(gè)5MHz的時(shí)鐘信號,0V-3.3V。為了測試產(chǎn)品的穩(wěn)定性,需要在這個(gè)時(shí)鐘信號的低電平位置疊加一個(gè)脈沖信號,此脈沖信號也是由FPGA產(chǎn)生,頻率約為250Mhz。

我的問題是

2024-08-19 07:18:41

擴(kuò)頻時(shí)鐘調(diào)制器DS1081L資料下載內(nèi)容主要介紹了:DS1081L引腳功能DS1081L功能和特性DS1081L應(yīng)用范圍DS1081L內(nèi)部方框圖DS1081L極限參數(shù)DS1081L典型應(yīng)用電路

2021-04-02 07:34:06

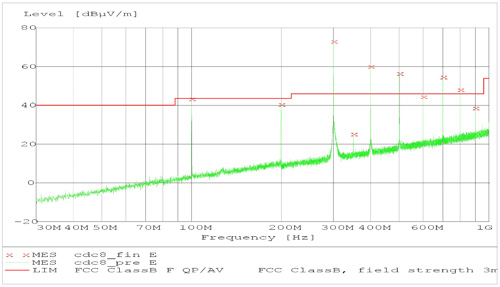

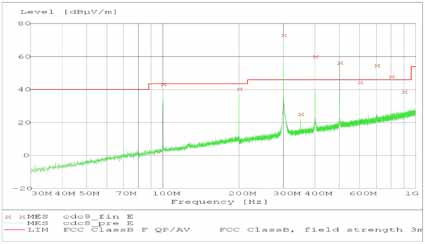

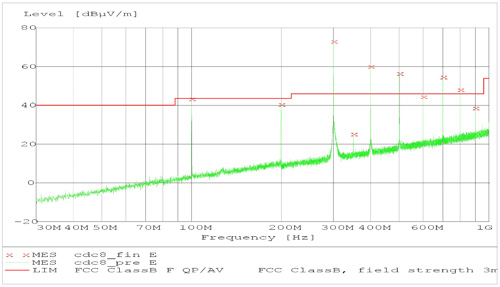

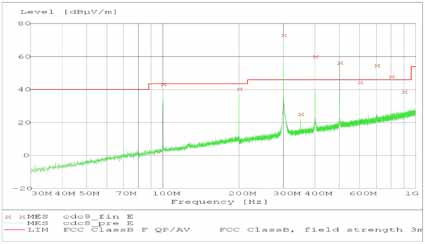

,EMI 可通過頻譜分析儀測量,如圖1 所示。圖中,綠色信號存在一些超出紅色 FCC 屏蔽的頻率分量(300MHz、400MHz 和 500MHz 等)。 控制時(shí)鐘引起 EMI 的一些方法都基于上述兩種

2018-09-19 14:42:35

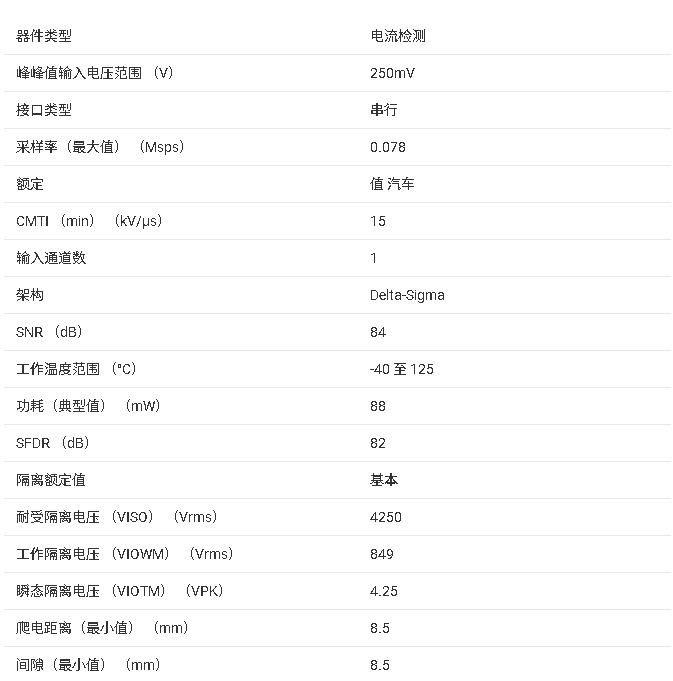

MS2400是瑞盟科技推出的一款二階Σ-Δ調(diào)制器,集成片上數(shù)字隔離器,能將模擬輸入信號轉(zhuǎn)換為高速1位碼流。調(diào)制器對輸入信號連續(xù)采樣,無需外部采樣保持電路。模擬信號輸入滿量程為±320 mV,轉(zhuǎn)換后

2021-10-12 12:14:32

存在于信號之間的寄生電感/電容,或者通過電源或接地連接的無用耦合,從而產(chǎn)生 EMI;或者2)直接通過電子/磁輻射,即輻射性 EMI。由于兩個(gè)原因,時(shí)鐘信號常歸咎于 EMI。即使時(shí)鐘低頻率運(yùn)行,較好的時(shí)鐘

2022-11-23 06:43:42

我做的一個(gè)基于DSP的系統(tǒng)中,DSP做主處理器,控制著整個(gè)系統(tǒng),包括信號處理,整體調(diào)度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統(tǒng)的邏輯控制和譯碼。DSP的時(shí)鐘輸入為15MHz

2023-06-19 06:43:17

時(shí)鐘產(chǎn)生和分發(fā)設(shè)計(jì)指南:在您設(shè)計(jì)時(shí)鐘電路時(shí)是否僅僅因?yàn)槟承┓椒ㄔ谶^去一直沿用,所以就采用它呢?或者您曾經(jīng)使用過某個(gè)器件僅僅是因?yàn)槠渌O(shè)計(jì)中使用了它?這種現(xiàn)象在如

2009-09-06 09:01:45 0

0 應(yīng)用軟件根據(jù)BYPASS信號的值來決定是否使用PLL。如果使用PLL,那么它總是輸出一個(gè)200MHz的時(shí)鐘信號,并且聯(lián)合系統(tǒng)分頻器(SYSDIV)共同產(chǎn)生系統(tǒng)時(shí)鐘。饋送到PWM模塊的時(shí)鐘由系

2009-11-07 14:01:59 14

14 16MHZ至134MHZ擴(kuò)展頻譜時(shí)鐘調(diào)制器DS1083L是擴(kuò)展頻譜時(shí)鐘調(diào)制器IC可降低時(shí)間數(shù)字電子設(shè)備的EMI

2010-04-09 15:19:22 18

18

SPWM調(diào)制方法對比分析

摘要:對比分析了三種正弦波脈寬調(diào)制(SPWM)控制方法,指出各自的優(yōu)缺點(diǎn)及應(yīng)用,給出了一些數(shù)學(xué)

2009-07-06 13:33:51 14120

14120

AD7400: 隔離式Σ-Δ調(diào)制器

AD7400*是一款二階Σ-Δ調(diào)制器,采用ADI公司iCoupler®技術(shù)的片內(nèi)數(shù)字隔離,能將模擬輸入信號轉(zhuǎn)換為高速的1比特?cái)?shù)據(jù)流。AD7400采用5V電源供

2009-09-25 08:48:40 2505

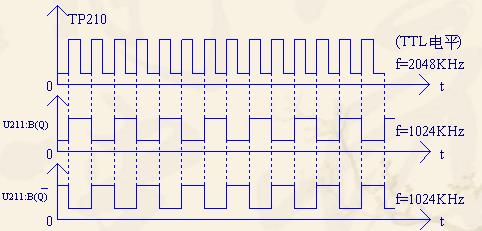

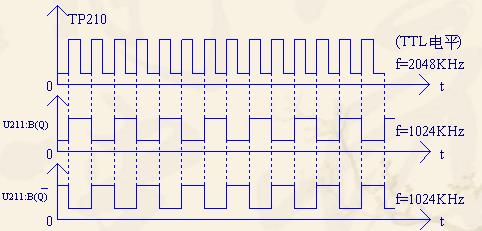

2505 2048KHz(2M)時(shí)鐘信號產(chǎn)生電路

2009-10-11 10:20:02 3300

3300

控制板級時(shí)鐘分配期間出現(xiàn)的EMI

今天,我們來談?wù)勊须娮酉到y(tǒng)都存在的一種常見問題——電磁干擾也即 EMI,并側(cè)重討論時(shí)鐘的影響。

從廣義來講,EMI&n

2010-01-19 11:13:14 2234

2234

控制板級時(shí)鐘分配期間出現(xiàn)的 EMI

今天,我們來談?wù)勊须娮酉到y(tǒng)都存在的一種常見問題——電磁干擾也即 EMI,并側(cè)重討論時(shí)鐘的影響。

從廣義來講,EMI 是

2010-01-21 09:36:19 1092

1092

本文簡要介紹了SSC擴(kuò)頻時(shí)鐘的基本概念以及如何使用力科示波器進(jìn)行信號的擴(kuò)頻時(shí)鐘的測試。

2011-05-17 11:23:34 6000

6000

所謂門控時(shí)鐘就是指連接到觸發(fā)器時(shí)鐘端的時(shí)鐘來自于組合邏輯;凡是組合邏輯在布局布線之后肯定會(huì)產(chǎn)生毛刺,而如果采用這種有毛刺的信號來作為時(shí)鐘使用的話將會(huì)出現(xiàn)功能上的錯(cuò)

2011-09-07 16:11:32 35

35 應(yīng)用于高能效電子產(chǎn)品的首要高性能硅方案供應(yīng)商安森美半導(dǎo)體(ON Semiconductor)推出新系列的有源時(shí)鐘產(chǎn)生器集成電路(IC),管理時(shí)鐘源的電磁干擾(EMI)及射頻干擾(RFI),為所有依賴于時(shí)鐘的

2011-10-18 09:11:24 921

921 基于AD9540產(chǎn)生多時(shí)鐘輸出

2011-11-25 00:02:00 31

31 基于片上偏差對芯片性能的影響,分析對比了時(shí)鐘樹設(shè)計(jì)與時(shí)鐘網(wǎng)格設(shè)計(jì),重點(diǎn)分析了時(shí)鐘網(wǎng)格抗OCV影響的優(yōu)點(diǎn),并利用實(shí)際電路應(yīng)用兩種方法分別進(jìn)行設(shè)計(jì)對比,通過結(jié)果分析,驗(yàn)證

2012-05-07 14:13:14 36

36 ASM3P2182A是一個(gè)多才多藝的擴(kuò)頻頻率調(diào)制器專門為范圍廣泛的輸入時(shí)鐘頻率從25兆赫到210兆赫。 ASM3P2182A可以產(chǎn)生EMI減少時(shí)鐘從OSC或生成一個(gè)系統(tǒng)時(shí)鐘。 ASM3P2182A

2017-04-06 10:24:19 7

7 SSCG是一種Active且低成本的解決EMI問題的方案,可以在保證時(shí)鐘信號完整性的基礎(chǔ)上應(yīng)對更廣頻率范圍內(nèi)EMI問題。相比傳統(tǒng)上使用Ferrite Beads和RF Chokes抑制EMI

2018-08-22 14:45:27 10026

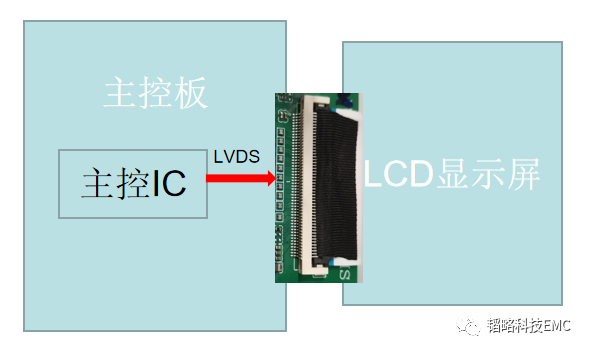

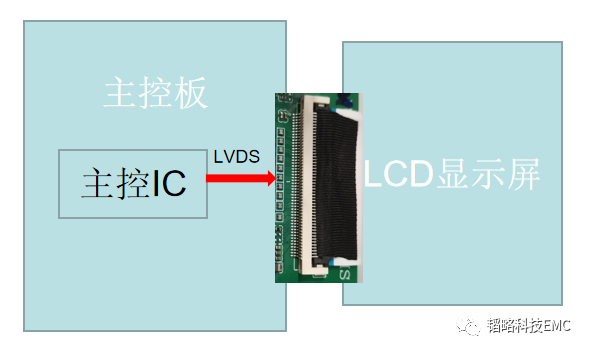

10026 對信號進(jìn)行調(diào)制,將信號能量擴(kuò)展到一個(gè)較寬的頻率范圍內(nèi),能有效的抑制系統(tǒng)的EMI問題。一、具體案列分析:客戶的樣機(jī)是工業(yè)類機(jī)器人,樣機(jī)中帶屏,屏的時(shí)鐘取自主芯片。如上圖,這是客戶沒有整改之前測試的實(shí)驗(yàn)

2018-11-06 14:53:48 1275

1275 首先,我們看一下時(shí)鐘信號中最常見到的波形 - 矩形波(尤其是方波更常用)。在較低時(shí)鐘頻率的系統(tǒng)中我們看到的基本上都是以矩形波為主的時(shí)鐘信號,因?yàn)殡娐坊旧隙际强?b class="flag-6" style="color: red">時(shí)鐘的邊沿(上升沿或下降沿)進(jìn)行

2018-12-06 11:53:10 64395

64395

電子產(chǎn)品多功能化、高速化、小型化的發(fā)展,意味著對內(nèi)部時(shí)鐘頻率的要求將越來越高。因?yàn)?b class="flag-6" style="color: red">時(shí)鐘信號是周期信號,所以在頻域上的能量是集中在某個(gè)頻率上的,這也就造成了時(shí)鐘EMI測試超標(biāo)的問題。

2019-02-02 16:25:00 6853

6853 內(nèi)同步時(shí)鐘的時(shí)鐘信號是從驅(qū)動(dòng)端直接發(fā)到接收端的。之前的博文提到,共同時(shí)鐘系統(tǒng)時(shí)序裕量較小,頻率無法繼續(xù)提升的一個(gè)關(guān)鍵因素之一就是Tco,受限于工藝等因素,這個(gè)Tco很難做到太小,比如SDRAM的Tco max一般有5.4ns。

2019-06-05 14:59:45 1664

1664

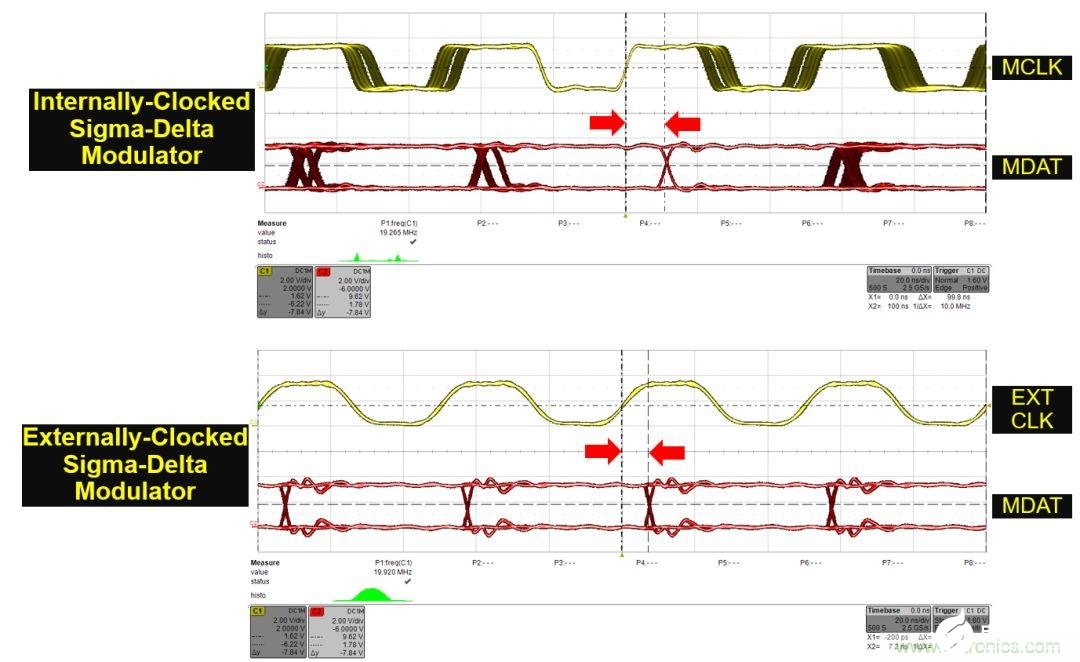

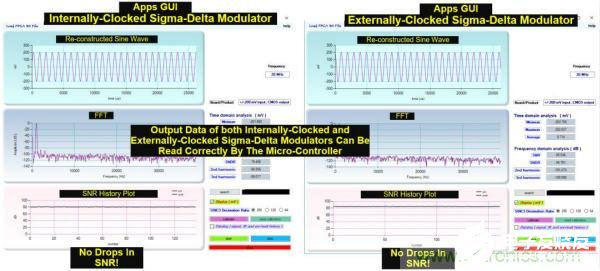

隔離的Σ-Δ調(diào)制器長期以來被證明可以在嘈雜的工業(yè)電機(jī)應(yīng)用環(huán)境中提供非常高的精度和強(qiáng)勁的電流和電壓感測能力。有兩類隔離型Σ-Δ調(diào)制器:一種是在IC內(nèi)部產(chǎn)生時(shí)鐘信號;另一種是從外部時(shí)鐘源接收時(shí)鐘信號。

2019-07-27 09:22:29 1184

1184 隔離調(diào)制器是一種將模擬輸入信號轉(zhuǎn)換為由0和1組成的高速數(shù)字比特流,同時(shí)使用隔離層將輸入和輸出電路隔離開來的Δ-Σ調(diào)制器。該隔離層對電磁干擾有很強(qiáng)的抵抗力,電磁干擾通常稱為EMI。干擾由外部源產(chǎn)生且會(huì)對電路產(chǎn)生負(fù)面影響。

2019-09-14 10:02:00 2441

2441

時(shí)鐘樹不僅可以做到高扇出,還可以做到讓時(shí)鐘信號到達(dá)各個(gè)觸發(fā)器的時(shí)刻盡可能一致,也即保證時(shí)鐘信號到達(dá)時(shí)鐘域內(nèi)不同觸發(fā)器的時(shí)間差最小。

2020-03-08 17:37:00 9341

9341

SSDCI1108AF是減少電磁干擾(EMI)的時(shí)鐘發(fā)生器。利用內(nèi)調(diào)制器對振蕩頻率進(jìn)行周期性的微調(diào),可以使不必要的電磁干擾(EMI)峰值衰減。SSDCI1108AF接收來自基本晶體或外部基準(zhǔn)的輸入時(shí)鐘,并鎖定到該輸入時(shí)鐘,以傳遞1x調(diào)制時(shí)鐘輸出。

2020-04-17 08:00:00 14

14 。 不要隨意將內(nèi)部信號作為時(shí)鐘,如門控時(shí)鐘和分頻時(shí)鐘,而要使用CLKDLL或者DCM產(chǎn)生的時(shí)鐘,或者可以通過建立時(shí)鐘使能或者DCM產(chǎn)生不同的時(shí)鐘信號。 FPGA盡量采取同步設(shè)計(jì),也就是所有時(shí)鐘都是同一個(gè)源頭,如果使用兩個(gè)沒有相位關(guān)系的異步時(shí)鐘,必須

2020-12-11 10:26:44 2426

2426 電子產(chǎn)品多功能化、高速化、小型化的發(fā)展,意味著對內(nèi)部時(shí)鐘頻率的要求將越來越高。因?yàn)?b class="flag-6" style="color: red">時(shí)鐘信號是周期信號,所以在頻域上的能量是集中在某個(gè)頻率上的,這也就造成了時(shí)鐘EMI測試超標(biāo)的問題。

2020-11-11 10:33:28 6136

6136 時(shí)鐘產(chǎn)生模塊將選定的時(shí)鐘源分頻,產(chǎn)生多種不同的時(shí)鐘頻率供多個(gè)模塊使用。例如:總線時(shí)鐘、FlexBus時(shí)鐘等。多功能時(shí)鐘發(fā)生器MCG模塊為MCU提供了多種時(shí)鐘源選擇,內(nèi)部包含了一個(gè)鎖頻環(huán)和一個(gè)鎖相環(huán),分別對內(nèi)部參考時(shí)鐘信號和外部時(shí)鐘參考信號進(jìn)行倍頻。

2020-11-12 16:59:41 12

12 在本文中,將詳細(xì)研究這兩類隔離-調(diào)制器的輸出數(shù)據(jù)信號完整性。并通過簡單的電磁干擾(EMI)測試設(shè)置、對由這兩類-調(diào)制器的高頻時(shí)鐘信號產(chǎn)生的EMI進(jìn)行比較。 對輸出數(shù)據(jù)信號完整性和時(shí)鐘信號電磁干擾

2020-11-18 14:59:50 1450

1450 超低抖動(dòng)時(shí)鐘的產(chǎn)生與分配

2021-04-18 14:13:51 8

8 時(shí)鐘毛刺注入是現(xiàn)實(shí)環(huán)境中有效且常用的故障注入方法。時(shí)鐘毛刺注入是通過在正常時(shí)鐘周期中引入一段毛刺時(shí)鐘,使得一個(gè)或多個(gè)觸發(fā)器接受錯(cuò)誤狀忞而修改指令、破壞數(shù)據(jù)或狀態(tài),最終倢芯片內(nèi)的秘密信息隨著產(chǎn)生

2021-04-26 14:20:04 9

9 有一個(gè)有趣的現(xiàn)象,眾多數(shù)字設(shè)計(jì)特別是與FPGA設(shè)計(jì)相關(guān)的教科書都特別強(qiáng)調(diào)整個(gè)設(shè)計(jì)最好采用唯一的時(shí)鐘域。換句話說,只有一個(gè)獨(dú)立的網(wǎng)絡(luò)可以驅(qū)動(dòng)一個(gè)設(shè)計(jì)中所有觸發(fā)器的時(shí)鐘端口。雖然這樣可以簡化時(shí)序分析以及

2021-05-10 16:51:39 4652

4652

PLL設(shè)計(jì)和時(shí)鐘頻率產(chǎn)生機(jī)理免費(fèi)下載。

2021-06-07 14:36:43 22

22 stm32內(nèi)部時(shí)鐘有哪些時(shí)鐘源 在STM32中,可以用內(nèi)部時(shí)鐘,也可以用外部時(shí)鐘,在要求進(jìn)度高的應(yīng)用場合最好用外部晶體震蕩器,內(nèi)部時(shí)鐘存在一定的精度誤差。 內(nèi)部時(shí)鐘有2個(gè)時(shí)鐘源可以選分別是HSI

2021-07-22 10:38:57 19057

19057 有一個(gè)有趣的現(xiàn)象,眾多數(shù)字設(shè)計(jì)特別是與FPGA設(shè)計(jì)相關(guān)的教科書都特別強(qiáng)調(diào)整個(gè)設(shè)計(jì)最好采用唯一的時(shí)鐘域。換句話說,只有一個(gè)獨(dú)立的網(wǎng)絡(luò)可以驅(qū)動(dòng)一個(gè)設(shè)計(jì)中所有觸發(fā)器的時(shí)鐘端口。雖然這樣可以簡化時(shí)序分析以及

2021-09-23 16:39:54 3632

3632 門控時(shí)鐘的設(shè)計(jì)初衷是實(shí)現(xiàn)FPGA的低功耗設(shè)計(jì),本文從什么是門控時(shí)鐘、門控時(shí)鐘實(shí)現(xiàn)低功耗的原理、推薦的FPGA門控時(shí)鐘實(shí)現(xiàn)這三個(gè)角度來分析門控時(shí)鐘。 一、什么是門控時(shí)鐘 門控時(shí)鐘技術(shù)(gating

2021-09-23 16:44:47 15514

15514

時(shí)鐘發(fā)生器用于產(chǎn)生時(shí)鐘,并提供給CPU和外部硬件設(shè)備。UPD78F0527有如下三種系統(tǒng)時(shí)鐘。(1)主系統(tǒng)時(shí)鐘①通過連接一個(gè)振蕩器到X1和X2,該振蕩電路產(chǎn)生fx=1到20MHZ的時(shí)鐘;②使用內(nèi)部

2021-10-28 13:36:18 10

10 振蕩器 產(chǎn)生內(nèi)部時(shí)鐘 SMCLK 子系統(tǒng)時(shí)鐘時(shí)鐘系統(tǒng)配置寄存器DCO控制寄存器 DCOCTL1、DCOx 頻率選擇 8種頻率2、MODx DAC調(diào)制器設(shè)定 微調(diào)DCO 的輸出頻率基本時(shí)鐘系統(tǒng)控制寄存器 BCSCTL1 BCSCTL2BCSCTL11、XT2OFF :XT2高速晶振開關(guān)

2021-11-19 21:06:06 18

18 信號-SOC-IN OSC-OUT懸空HSI:8MHz RC產(chǎn)生 做系統(tǒng)時(shí)鐘或2分頻后PLL輸入相對HSE優(yōu)點(diǎn)為啟動(dòng)時(shí)間短 置“1”,輸出時(shí)鐘釋放系統(tǒng)復(fù)位1 HSIAL[7:0]位...

2021-12-02 13:36:06 0

0 信號-SOC-IN OSC-OUT懸空HSI:8MHz RC產(chǎn)生 做系統(tǒng)時(shí)鐘或2分頻后PLL輸入相對HSE優(yōu)點(diǎn)為啟動(dòng)時(shí)間短 置“1”,輸出時(shí)鐘釋放系統(tǒng)復(fù)位1 HSIAL[7:0]位...

2021-12-22 18:59:46 0

0 如果用單獨(dú)的時(shí)鐘信號板,一般采用什么樣的接口,來保證時(shí)鐘信號的傳輸受到的影響小?

2022-09-16 08:58:49 3405

3405

本章的主要內(nèi)容: 分析時(shí)鐘驅(qū)動(dòng)器、時(shí)鐘信號的特殊布線 改進(jìn)時(shí)鐘信號分配的特殊電路

2022-09-20 14:55:40 0

0 的扇出型緩沖器,是一種將一路時(shí)鐘源信號通過頻率復(fù)制生成多路時(shí)鐘信號的器件,通常時(shí)鐘緩沖器還兼具有時(shí)鐘分配,格式轉(zhuǎn)換和電平轉(zhuǎn)換的功能。 對于需要多路時(shí)鐘信號的電子系統(tǒng)來說,時(shí)鐘源加時(shí)鐘緩沖器的方案可以有效降低系統(tǒng)成本,簡化電路設(shè)計(jì),為系統(tǒng)多個(gè)組件提供多路參

2022-10-18 18:36:54 30571

30571

時(shí)鐘信號在很大程度上決定了整個(gè)設(shè)計(jì)的性能和可靠性,盡量避免使用FPGA內(nèi)部邏輯產(chǎn)生的時(shí)鐘,因?yàn)樗苋菀讓?dǎo)致功能或時(shí)序出現(xiàn)問題。內(nèi)部邏輯(組合邏輯)產(chǎn)生的時(shí)鐘容易出現(xiàn)毛刺,影響設(shè)計(jì)的功能實(shí)現(xiàn);組合邏輯固有的延時(shí)也容易導(dǎo)致時(shí)序問題。

2022-10-26 09:04:51 1877

1877 控制板級時(shí)鐘分配期間出現(xiàn)的 EMI

2022-11-07 08:07:32 0

0 隔離放大器的輸入級由一個(gè)驅(qū)動(dòng)輸入放大器-ΔΣ調(diào)制器的輸入放大器組成。輸入放大器的增益由內(nèi)部精度電阻器進(jìn)行固定和設(shè)置,ΔΣ調(diào)制器則使用內(nèi)部參考電壓和時(shí)鐘發(fā)生器來將模擬輸入信號轉(zhuǎn)換為數(shù)字位流。

2023-02-10 15:12:49 1593

1593 RF DAC的無雜散動(dòng)態(tài)范圍受到嚴(yán)重的數(shù)字do主開關(guān)的限制,這會(huì)干擾模擬輸出信號。介紹了一種擴(kuò)頻時(shí)鐘發(fā)生器(SSCG)的設(shè)計(jì)、布局和仿真。SSCG調(diào)制用于切換DAC數(shù)字塊的時(shí)鐘頻率,以減少DAC

2023-02-14 16:43:56 0

0 時(shí)鐘電路是一種電路,它可以產(chǎn)生定期的時(shí)鐘信號,用于控制電子設(shè)備的運(yùn)行。

它的特點(diǎn)是可以產(chǎn)生定期的時(shí)鐘信號,可以控制電子設(shè)備的運(yùn)行,可以提高電子設(shè)備的精度和可靠性。時(shí)鐘電路的應(yīng)用非常廣泛,它可

2023-02-20 18:16:38 9334

9334 系統(tǒng)時(shí)序設(shè)計(jì)中對時(shí)鐘信號的要求是非常嚴(yán)格的,因?yàn)槲覀兯械臅r(shí)序計(jì)算都是以恒定的時(shí)鐘信號為基準(zhǔn)。但實(shí)際中時(shí)鐘信號往往不可能總是那么完美,會(huì)出現(xiàn)抖動(dòng)(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 5281

5281 理想值附近的一個(gè)范圍內(nèi),從而造成相鄰的時(shí)鐘邊沿存在偏差。在時(shí)序分析時(shí),時(shí)鐘抖動(dòng)是一個(gè)重要的因素。多種因素會(huì)導(dǎo)致時(shí)鐘抖動(dòng),包括PLL回路噪聲、電源紋波、熱噪聲以及信號之間的串?dāng)_等。

2023-06-09 09:40:50 3109

3109

有一個(gè)有趣的現(xiàn)象,眾多數(shù)字設(shè)計(jì)特別是與FPGA設(shè)計(jì)相關(guān)的教科書都特別強(qiáng)調(diào)整個(gè)設(shè)計(jì)最好采用唯一的時(shí)鐘域。換句話說,只有一個(gè)獨(dú)立的網(wǎng)絡(luò)可以驅(qū)動(dòng)一個(gè)設(shè)計(jì)中所有觸發(fā)器的時(shí)鐘端口。雖然這樣可以簡化時(shí)序分析以及

2023-08-23 16:10:01 1376

1376 芯片為什么要時(shí)鐘信號 芯片是現(xiàn)代電子設(shè)備的核心組成部分,廣泛應(yīng)用于計(jì)算機(jī)、手機(jī)、電視等各個(gè)領(lǐng)域。芯片內(nèi)部有著復(fù)雜的電子元件和電路結(jié)構(gòu),這些元件和電路結(jié)構(gòu)需要進(jìn)行同步操作,以實(shí)現(xiàn)正確的工作。因此,芯片

2023-09-01 15:38:11 3031

3031 一定的影響。因此,為了抑制時(shí)鐘電路產(chǎn)生的電磁輻射,需要采取一些措施來降低其產(chǎn)生的電磁輻射水平。 一、由于時(shí)鐘電路產(chǎn)生的電磁輻射的頻率高,因此采用電源濾波器是比較常見的手段。電源濾波器可以減少電源電壓中的高頻

2023-09-12 17:06:49 1523

1523 件、計(jì)算機(jī)、數(shù)字電路和通訊協(xié)議等設(shè)備的信號。它的主要作用是進(jìn)行時(shí)序控制,使數(shù)據(jù)傳輸和處理的時(shí)序保持一致。時(shí)鐘信號一般由計(jì)時(shí)器產(chǎn)生,其具有一定的周期性、穩(wěn)定性和精度。 時(shí)鐘信號的主要信號參數(shù)包括周期、頻率、精度和占空比等,

2023-09-15 16:28:12 4353

4353 ,CPU/Clock 作為芯片中的核心,是需要時(shí)鐘信號的。 那么,什么是時(shí)鐘信號? 時(shí)鐘信號,是指芯片中的一個(gè)定時(shí)信號,用來指導(dǎo)芯片的工作節(jié)奏、同步各個(gè)部件的工作狀態(tài)。簡單來說,時(shí)鐘信號是一種規(guī)律性的振蕩信號,控制著芯片內(nèi)各種部

2023-09-15 16:28:14 4268

4268 時(shí)鐘信號怎么產(chǎn)生的 時(shí)鐘信號是一種重要的信號,它在電子設(shè)備中廣泛應(yīng)用。時(shí)鐘信號的產(chǎn)生與傳輸是現(xiàn)代電子設(shè)備中不可或缺的基礎(chǔ)技術(shù)之一。時(shí)鐘信號的精確性和準(zhǔn)確性是現(xiàn)代電子設(shè)備能夠?qū)崿F(xiàn)高速計(jì)算等復(fù)雜操作

2023-09-15 16:28:22 3630

3630 是數(shù)據(jù)信號(SDA)。SCL信號是在IIC通信中非常重要的一個(gè)信號,它確定了數(shù)據(jù)的傳輸速率以及同步時(shí)序。 IIC時(shí)鐘信號的產(chǎn)生需要硬件支持,一般通過外部晶振或者內(nèi)部時(shí)鐘源產(chǎn)生。在IIC總線使用過程中,時(shí)鐘信號的頻率很重要,必須要與所有設(shè)備的時(shí)鐘頻率保持一致。一般來說,為了保證

2023-09-19 17:16:02 3252

3252 方法來使不同步的時(shí)鐘信號同步。下面我們就來詳細(xì)講解這些方法。 1. 時(shí)鐘緩沖器同步法 時(shí)鐘緩沖器同步法是指通過一個(gè)時(shí)鐘緩沖器來同步兩個(gè)不同步的時(shí)鐘信號。其原理是將一個(gè)時(shí)鐘信號通過一個(gè)緩沖器反轉(zhuǎn),產(chǎn)生一個(gè)相反的信號,

2023-10-18 15:23:48 2931

2931 可以說是計(jì)算機(jī)運(yùn)行的重要組成部分之一。 時(shí)鐘芯片的工作原理: 時(shí)鐘芯片是通過一系列簡單的電路來實(shí)現(xiàn)的,它內(nèi)部包含一個(gè)晶體振蕩器,用來產(chǎn)生一個(gè)穩(wěn)定的基準(zhǔn)信號。這個(gè)基準(zhǔn)信號通過分頻器分成不同頻率的信號輸出到不同的電

2023-10-25 15:02:33 8943

8943 。 單片機(jī)要實(shí)現(xiàn)數(shù)據(jù)處理和執(zhí)行程序,需要一個(gè)時(shí)鐘信號來引導(dǎo)CPU的運(yùn)行。單片機(jī)可以使用片內(nèi)時(shí)鐘振蕩方式和外部時(shí)鐘方式兩種方式來產(chǎn)生時(shí)鐘信號,這兩種方式具體有什么區(qū)別呢? 1. 片內(nèi)時(shí)鐘振蕩方式 片內(nèi)時(shí)鐘振蕩方式是指單片

2023-10-25 15:02:36 2187

2187 它可以被用來同步各種電子設(shè)備的操作。 產(chǎn)生時(shí)鐘信號的器件主要有晶振、石英諧振器、電容器、電感、晶體管等。其中,晶振和石英諧振器是最常用的兩種器件。 晶振是一種由壓電晶體制成的振蕩器。當(dāng)施加電場時(shí),晶體會(huì)振動(dòng)產(chǎn)

2023-10-25 15:07:45 2236

2236 如何用時(shí)鐘振蕩器產(chǎn)生穩(wěn)定的100hz或1hz的時(shí)鐘信號? 時(shí)鐘信號是電子系統(tǒng)中至關(guān)重要的組成部分,用于同步各種信號和操作。它需要穩(wěn)定、準(zhǔn)確、可靠地工作,以確保系統(tǒng)性能。時(shí)鐘信號的產(chǎn)生可以通過許多

2023-10-25 15:07:55 2951

2951 什么是時(shí)鐘電路?什么是脈沖?時(shí)鐘電路是如何生成脈沖的? 時(shí)鐘電路是一種電路,它產(chǎn)生的周期性的信號被用作計(jì)算機(jī)系統(tǒng)的基準(zhǔn)。時(shí)鐘電路產(chǎn)生的信號被稱為時(shí)鐘脈沖或時(shí)鐘信號。在計(jì)算機(jī)系統(tǒng)中,時(shí)鐘信號用于同步

2023-10-25 15:14:17 3577

3577 時(shí)鐘合成器和時(shí)鐘發(fā)生器是兩種用于產(chǎn)生時(shí)鐘信號的電子器件,它們在功能和應(yīng)用上有一些區(qū)別。

2023-11-09 10:26:56 1541

1541 時(shí)鐘電路是指用于產(chǎn)生穩(wěn)定、精確的時(shí)間基準(zhǔn)信號的電路。這種電路通常采用晶體振蕩器或者其他穩(wěn)定的振蕩器作為時(shí)鐘源,產(chǎn)生固定頻率的信號。時(shí)鐘信號被廣泛應(yīng)用于數(shù)字系統(tǒng)、通信系統(tǒng)、計(jì)算機(jī)系統(tǒng)等各種電子設(shè)備中,用于同步和控制各種操作和數(shù)據(jù)傳輸。

2023-11-17 09:50:08 4358

4358 如何有效解決LVDS時(shí)鐘EMI問題

2023-11-23 09:04:46 1825

1825

什么是時(shí)鐘信號?數(shù)字電路的時(shí)鐘信號是怎么產(chǎn)生呢? 時(shí)鐘信號,也稱為時(shí)鐘脈沖,是用于同步數(shù)字電路中所有操作的基本信號。它提供了一個(gè)參考頻率,使得所有電路元件都能按照同樣的節(jié)奏進(jìn)行工作。時(shí)鐘信號是一個(gè)

2024-01-25 15:40:52 15223

15223 芯片為什么要時(shí)鐘信號 時(shí)鐘芯片的作用是什么? 時(shí)鐘信號在芯片中起著非常重要的作用。它是芯片的“心臟”,相當(dāng)于人體的心臟,用于同步和控制芯片中的各個(gè)功能模塊之間的操作。時(shí)鐘信號可以提供一個(gè)穩(wěn)定的時(shí)間

2024-01-29 18:11:31 8060

8060 SPICE是一種用于模擬和分析電子電路的計(jì)算機(jī)程序。在SPICE仿真中,產(chǎn)生時(shí)鐘信號是許多電路設(shè)計(jì)和模擬任務(wù)中的關(guān)鍵步驟。

2024-02-06 14:22:01 2627

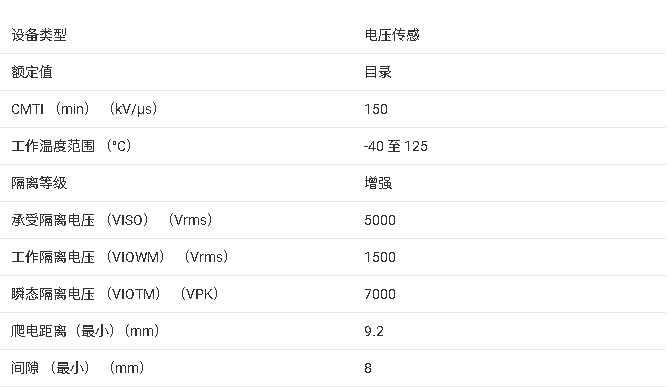

2627 電子發(fā)燒友網(wǎng)站提供《AMC1333M10具有10MHz內(nèi)部時(shí)鐘的±1V 輸入、增強(qiáng)型隔離式Δ-Σ精密調(diào)制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-08-16 11:18:09 0

0 時(shí)鐘抖動(dòng)(Clock Jitter)是時(shí)鐘信號領(lǐng)域中的一個(gè)重要概念,它指的是時(shí)鐘信號時(shí)間與理想事件時(shí)間的偏差。這種偏差不僅影響數(shù)字電路的時(shí)序性能,還可能對系統(tǒng)的穩(wěn)定性和可靠性造成不利影響。以下是對時(shí)鐘抖動(dòng)工作原理的詳細(xì)闡述,內(nèi)容將圍繞其定義、類型、產(chǎn)生原因、影響及應(yīng)對措施等方面展開。

2024-08-19 17:58:11 5343

5343 電子發(fā)燒友網(wǎng)站提供《隔離式調(diào)制器與MCU之間的數(shù)字接口的時(shí)鐘邊沿延遲補(bǔ)償.pdf》資料免費(fèi)下載

2024-09-06 11:18:05 0

0 在數(shù)字電路設(shè)計(jì)中,時(shí)鐘信號扮演著至關(guān)重要的角色。理想的時(shí)鐘信號是一串無限連續(xù)的脈沖序列,除了電平要求外,其邊沿應(yīng)非常陡峭,有些系統(tǒng)還要求時(shí)鐘具有50%的占空比。從電磁兼容性(EMC)的角度來看,理想

2024-09-13 14:18:06 1134

1134 電子發(fā)燒友網(wǎng)站提供《從晶體振蕩器產(chǎn)生時(shí)鐘信號.pdf》資料免費(fèi)下載

2024-09-18 14:32:55 0

0 一前言隨著信息技術(shù)和半導(dǎo)體技術(shù)的快速發(fā)展,電子產(chǎn)品的類型和功能模塊日益多樣化,對此要求的傳輸速率也日益提高。其中時(shí)鐘頻率的不斷提升,同時(shí)也帶來了更多的EMI時(shí)鐘問題。時(shí)鐘EMI問題的處理還受到了很多

2025-03-11 11:34:02 1108

1108

該AMC0386是一款精密的電流隔離三角積分 (ΔΣ) 調(diào)制器,具有高壓、高阻抗輸入和外部時(shí)鐘。輸入設(shè)計(jì)為直接連接到高壓信號源。

隔離柵將系統(tǒng)中在不同共模電壓電平下運(yùn)行的部分分開。隔離柵具有很強(qiáng)的抗磁干擾能力,并經(jīng)認(rèn)證可提供高達(dá) 5kVRMS (60s) 的增強(qiáng)隔離。

2025-10-23 13:55:41 432

432

AMC1204-Q1 是一款 1 位數(shù)字輸出、隔離式 Δ-Σ 調(diào)制器,時(shí)鐘頻率高達(dá) 20 MHz。調(diào)制器輸出的數(shù)字隔離由二氧化硅(SiO ~2~ )屏障,具有很強(qiáng)的抗磁干擾能力。該屏障經(jīng)認(rèn)證可提供

2025-11-17 10:59:50 446

446

AMC1204和AMC1204B為1位數(shù)字輸出,隔離δσ(ΔΣ)調(diào)制器,時(shí)鐘頻率最高可達(dá)20 MHz。調(diào)制器輸出的數(shù)字隔離由二氧化硅(SiO)提供 ~2~ )屏障,具有高度的磁干擾能力。該屏障已經(jīng)

2025-11-19 11:22:28 1176

1176

在現(xiàn)代高速數(shù)字系統(tǒng)中,時(shí)鐘信號的完整性直接影響著系統(tǒng)的性能和穩(wěn)定性。時(shí)鐘緩沖器作為時(shí)鐘樹設(shè)計(jì)的核心組件,承擔(dān)著信號分配、噪聲隔離和時(shí)序優(yōu)化的關(guān)鍵任務(wù)。隨著5G通信、AI芯片和數(shù)據(jù)中心等領(lǐng)域的快速發(fā)展

2025-12-16 15:57:19 259

259

電子發(fā)燒友App

電子發(fā)燒友App

評論