并行數(shù)據(jù)信號(hào)才能達(dá)到的總線帶寬。 PCI總線使用并行總線結(jié)構(gòu),在同一條總線上的所有外部設(shè)備共享總線帶寬,而PCIe總線使用了高速差分總線,并采用端到端的連接方式,因此在每一條PCIe鏈路中只能連接兩個(gè)設(shè)備。這使得PCIe與PCI總線采用的

2020-11-21 10:42:13 5345

5345

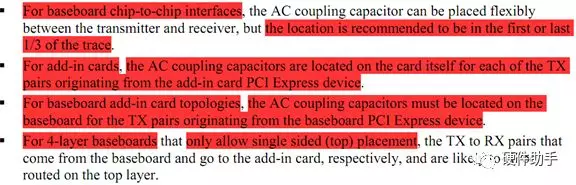

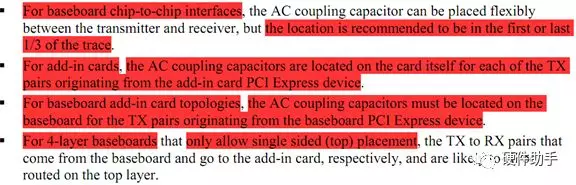

本篇主要介紹PCIe總線的AC耦合電容、總線的去加重等高速信號(hào)調(diào)整技術(shù)。 AC耦合電容可以參考之前的文章《邏輯電平之差分互連AC耦合電容(7)》,本文主要針對(duì)PCIe接口介紹AC耦合電容的實(shí)際使用

2020-12-22 16:54:15 15497

15497

一、PCIe概況 隨著現(xiàn)代處理器技術(shù)的發(fā)展,使用高速差分總線替代并行總線已是大勢(shì)所趨。與單端并行信號(hào)相比,高速差分信號(hào)可以使用更高的時(shí)鐘頻率,從而可以使用更少的信號(hào)線達(dá)到更高的通訊速度。PCIe總線

2020-12-31 11:10:49 10248

10248

最近幾期,我們將通過(guò)專欄的方式向大家介紹一個(gè)更加常用的高速接口——PCIe接口。"Peripheral Component Interconnect Express"(PCIe或PCI-E)是一種串行擴(kuò)展總線標(biāo)準(zhǔn),計(jì)算機(jī)利用該接口可以擴(kuò)展連接一個(gè)或多個(gè)外圍設(shè)備。

2023-09-26 11:37:37 11907

11907

本帖最后由 eehome 于 2013-1-5 10:11 編輯

PCIE總線基本資料

2012-08-06 10:47:57

`PCIE總線的FPGA設(shè)計(jì)方法`

2015-10-30 14:30:52

控制器 x1 接口,能讓 PC 方便地連接到 CAN 總線上,即插即用,安裝簡(jiǎn)單方便。PCIe-9110IM 提供 1 個(gè)完全獨(dú)立的 CAN 通道,符合 CAN2.0B 規(guī)范(兼容 CAN 2.0A

2022-10-31 06:11:43

PCIe是什么?PCIe的架構(gòu)是由哪些部分組成的?PCIe總線和PCI總線有哪些不同之處呢?

2021-10-26 08:10:07

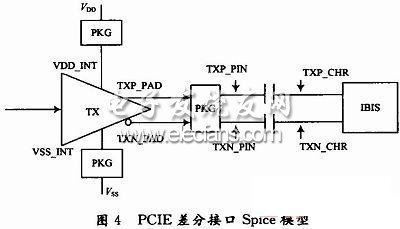

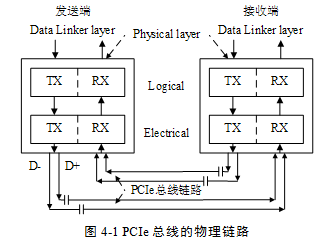

PCIe提供了一種可裁減高速串行I/O點(diǎn)到點(diǎn)的總線連接。PCIe的LAN是一個(gè)全雙工的通道,由一對(duì)接收差分對(duì)和一對(duì)發(fā)送差分對(duì)構(gòu)成。PCIe的帶寬可以通過(guò)增減LANE數(shù)來(lái)調(diào)整。PCIe規(guī)范定義了x1

2019-06-03 07:09:56

PCIe總線概述隨著現(xiàn)代處理器技術(shù)的發(fā)展,在互連領(lǐng)域中,使用高速差分總線替代并行總線是大勢(shì)所趨。與單端并行信號(hào)相比,高速差分信號(hào)可以使用更高的時(shí)鐘頻率,從而使用更少的信號(hào)線,完成之前需要許多單端并行數(shù)據(jù)信號(hào)才能達(dá)到的總線帶寬。PCI總線使用并行總線結(jié)構(gòu),在同一條總線上的所有外...

2021-07-29 07:07:06

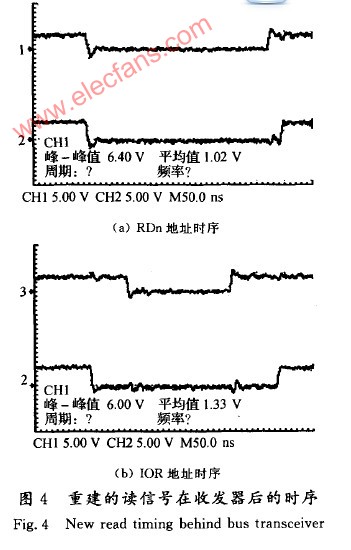

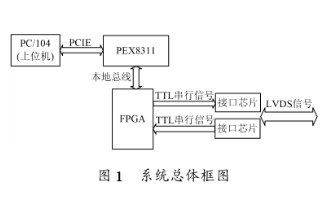

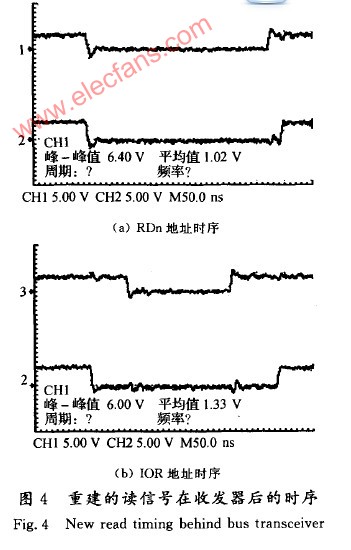

摘要:通過(guò)分析920T核ARM 處理器的高速片上系統(tǒng)總線AHB時(shí)序及其靜態(tài)存儲(chǔ)控制器SMC接口模型,研究IBM PC/AT和IEEE PC/104總線規(guī)范,提出一種在ARM

2010-08-31 09:18:27

PCIE 總線接口芯片

2024-06-21 02:49:39

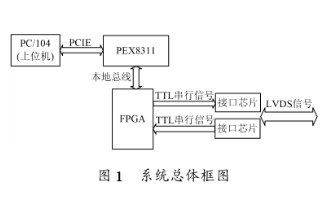

東哥好,請(qǐng)教一個(gè)問(wèn)題:我在用CPLD做數(shù)字采集卡,AD芯片采集了的數(shù)據(jù)放到fifo里面,然后通過(guò)半滿信號(hào)告訴pc104總線取數(shù)據(jù),二者之間加了hct245,可是控制hct245的傳輸數(shù)據(jù)方向的管腳DIR和PC104總線的讀數(shù)據(jù)的信號(hào)不怎么匹配的好,請(qǐng)教有什么好的解決辦法么?謝謝。。。

2013-07-22 10:12:25

;Intel最新的FPGA則QPI也是比較常用的。對(duì)于傳輸視頻:MIPI、BT.656、BT.1120這些接口也是非常常見的。高速接口我們只介紹PCIe,這也是非常常見的數(shù)據(jù)通信接口,在加速卡、數(shù)據(jù)中心,都是

2022-08-19 16:32:22

和帶寬。

時(shí)鐘速度和同步 :

FPGA的時(shí)鐘管理是實(shí)現(xiàn)高性能PCIe設(shè)計(jì)的關(guān)鍵。如果時(shí)鐘頻率設(shè)置不當(dāng)或時(shí)鐘源不穩(wěn)定,可能會(huì)導(dǎo)致數(shù)據(jù)丟失和性能下降。

信號(hào)完整性 :

高速信號(hào)在FPGA引腳與外部設(shè)備

2024-05-27 16:17:41

Cfg_mgmt接口發(fā)送給PCIE硬核,當(dāng)配置請(qǐng)求的總線號(hào)不為0時(shí),請(qǐng)求以PCIe配置請(qǐng)求TLP的格式從axis_rq接口發(fā)送到PCIE硬核,然后由硬核驅(qū)動(dòng)數(shù)據(jù)鏈路層和物理層通過(guò)PCIe3.0X4接口

2025-08-09 14:37:11

Cfg_mgmt接口發(fā)送給PCIE硬核,當(dāng)配置請(qǐng)求的總線號(hào)不為0時(shí),請(qǐng)求以PCIe配置請(qǐng)求TLP的格式從axis_rq接口發(fā)送到PCIE硬核,然后由硬核驅(qū)動(dòng)數(shù)據(jù)鏈路層和物理層通過(guò)PCIe3.0X4接口

2025-08-03 22:00:21

PCI-104總線驅(qū)動(dòng)程序

2012-10-20 22:11:13

這款芯片主要是使設(shè)備支持SDXC UHS-I標(biāo)準(zhǔn)的大容量高速存儲(chǔ)的SD卡,SDXC標(biāo)準(zhǔn)的SD卡目前的容量在64GB~2TB,存儲(chǔ)速度達(dá)到104MB/秒。另外這款芯片還有CF, ATA等接口橋接功能

2011-03-24 17:41:45

,減少了數(shù)據(jù)通信的擁堵和沖突,每個(gè)PCIE464控制卡擁有獨(dú)立的的通信通道,可以直接與CPU進(jìn)行數(shù)據(jù)交換,無(wú)需等待其他設(shè)備釋放總線資源,從而實(shí)現(xiàn)更高的數(shù)據(jù)傳輸速率。特別適用于高速數(shù)據(jù)采集、高速數(shù)據(jù)處理等

2024-01-24 09:48:21

,它還支持多通道連接,通過(guò)增加通道數(shù)量可以進(jìn)一步提升總帶寬。

優(yōu)勢(shì)

高帶寬:與傳統(tǒng)總線相比,PCIe能夠提供更高的帶寬。例如,在x16通道的PCIe4.0接口下,總帶寬可達(dá)32GB/s,這使得大量的數(shù)據(jù)

2025-03-25 15:21:18

:能使用xiinx 的PCIE ip核完成讀寫功能對(duì)以上課程有興趣的同學(xué)點(diǎn)下面鏈接學(xué)習(xí) : 明德?lián)PFPGA課程_PCIE高速接口XILINX.ISE教程_嗶哩嗶哩_bilibili這只是我們明德?lián)P課程

2022-02-14 09:50:22

。因?yàn)楣た貦C(jī)的總線為PC104,因此需要設(shè)計(jì)PC104與DSP之間的通信接口。系統(tǒng)中以Altera公司的一片F(xiàn)PGA芯片EPlK50來(lái)對(duì)該接口和數(shù)據(jù)采集過(guò)程中的邏輯控制與FIFO進(jìn)行設(shè)計(jì)。下面主要闡述

2019-05-07 07:00:09

之前沒(méi)有了解過(guò)PC104PLUS總線,我的理解是該總線就是PCI BUS與ISA的組合,該總線兼容PCI。但是呢,我現(xiàn)在想做一個(gè)底板,核心板是Intel的E3845,它有PCIE的接口,底板想做

2019-07-22 10:41:59

Express 總線的 4 路 10G 雙緩沖光纖通道適配器,板卡具有 4 通道 SFP+萬(wàn)兆光纖接口,x8 PCIE 主機(jī)接口,具有 2 組 64 位 DDR3 SDRAM 作為高速緩存,可以實(shí)現(xiàn)

2017-03-11 14:05:16

的技術(shù)轉(zhuǎn)讓以及相關(guān)的技術(shù)培訓(xùn)此外,本公司還研制基于flash的大規(guī)模數(shù)據(jù)存儲(chǔ)系統(tǒng),以及基于各種高速處理器的高速并行處理板卡。如有需求請(qǐng)按以下聯(lián)系方式聯(lián)系.email:ryan_pcie@163.com

2010-11-08 23:25:23

Ultrascale 對(duì)外接口:1.多個(gè)標(biāo)準(zhǔn)的FIFO接口或AXI4-Stream數(shù)據(jù)總線2.擴(kuò)展的RAM接口,支持BAR1映射空間 性能指標(biāo):1.PCIe 2.0 x4:DMA Read(C2H)速率大于

2020-11-25 22:27:25

高速,在12MHz晶振的MCS51單片機(jī)控制的數(shù)據(jù)采集系統(tǒng)中,可以滿足與PC104 ISA總線接口實(shí)時(shí)通信的要求,通信速率達(dá)200Kbps。 1 系統(tǒng)總體設(shè)計(jì)方案用CPLD實(shí)現(xiàn)單片機(jī)與PC104

2019-06-20 05:00:02

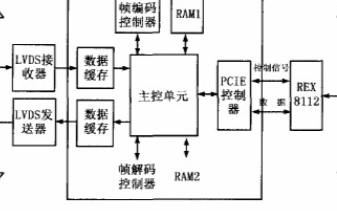

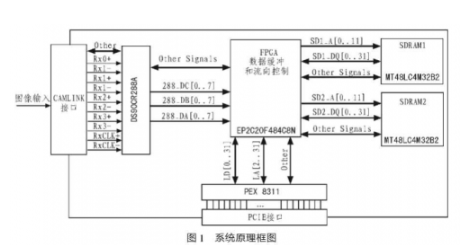

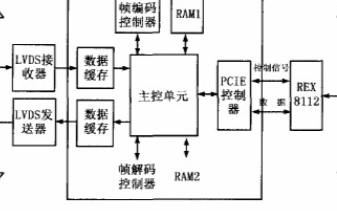

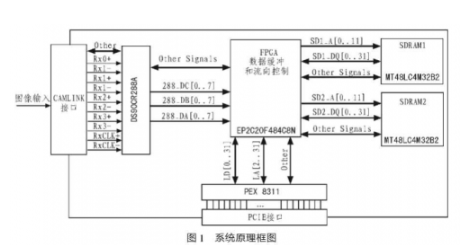

總線實(shí)現(xiàn)數(shù)據(jù)交互,并提供數(shù)字視頻信號(hào)給壓縮存儲(chǔ)單元和圖像處理單元。系統(tǒng)硬件結(jié)構(gòu)簡(jiǎn)單,工作穩(wěn)定可靠,能夠廣泛應(yīng)用于圖像處理領(lǐng)域。關(guān)鍵詞:DVI;Camlink;圖像處理;PAL引言 帶有DVI接口

2019-06-10 05:00:07

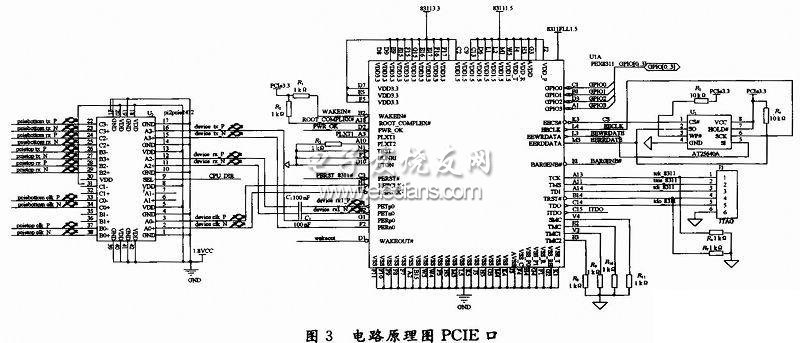

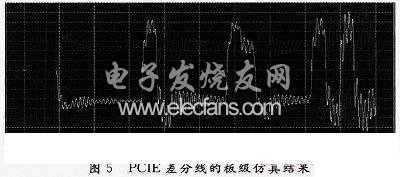

描述符表。根據(jù)實(shí)際使用的PCIE總線通道數(shù)和DMA長(zhǎng)度的不同,實(shí)際測(cè)試得到的總線速度也不同,表3給出了參考數(shù)據(jù)。5 結(jié)語(yǔ)使用FPGA來(lái)設(shè)計(jì)PCIE總線擴(kuò)展卡,可以省去專用的PCIE接口芯片,降低了硬件

2019-05-21 05:00:02

:一種為高速100Kbit/s,另一種為低速12~14.5Kbit/s。通常高速用于軍用飛機(jī)中,低速用于民用飛機(jī)中。ARINC429接口模塊的硬件設(shè)計(jì) 設(shè)計(jì)思路PC/104系統(tǒng)支持8位或16位的并行數(shù)據(jù)

2019-04-16 07:00:04

, 因此如何來(lái)實(shí)現(xiàn)該監(jiān)控系統(tǒng)中大量數(shù)據(jù)的高效、快速、準(zhǔn)確地采集和傳輸成為設(shè)計(jì)該監(jiān)控系統(tǒng)所面臨的一個(gè)主要難題。而本文所研究的基于PCI 總線的高速數(shù)據(jù)通信卡的設(shè)計(jì)正是解決上述難題的關(guān)鍵技術(shù)之一。PCI

2010-09-22 08:51:09

數(shù)據(jù)采集與控制單元,以CYPRESS公司的高速USB接口芯片CY7C68001為基礎(chǔ),利用DSP片上A/D轉(zhuǎn)換器采集數(shù)據(jù),經(jīng)處理后把數(shù)據(jù)通過(guò)USB總線傳輸至PC機(jī),PC機(jī)接收到數(shù)據(jù)后按照用戶的要求通過(guò)

2019-05-07 09:40:04

基于USB總線的高速數(shù)據(jù)采集系統(tǒng)介紹了一種基于USB總線的高速數(shù)據(jù)采集系統(tǒng),討論了USB控制器EZ-USB FX2?CY7C68013?的性能及傳輸方式?給出了該系統(tǒng)的硬件和基于GPIF主控方式實(shí)現(xiàn)

2009-04-11 17:20:15

PCIe總線通信過(guò)程是怎樣的?是什么原理?如何利用PCIe DMA總線實(shí)現(xiàn)一個(gè)基于FPGA的PCIe 8位數(shù)據(jù)采集卡?

2021-09-17 07:16:03

本設(shè)計(jì)采用了復(fù)雜可編程器件CPLD,用CPLD完成了PC104總線與429總線通訊的主要電路,大大節(jié)省了硬件資源,本文著重介紹了CPLD部分的設(shè)計(jì)。

2021-04-29 06:47:46

本文給出了基于PXI總線接口的高速數(shù)字化儀模塊的設(shè)計(jì)實(shí)現(xiàn)方法,介紹了高速數(shù)據(jù)采集系統(tǒng)中LVDS接口、LVPECL接口電路結(jié)構(gòu)及連接方式,并在所設(shè)計(jì)的數(shù)字化儀模塊中得到應(yīng)用。

2021-04-14 06:18:38

PCI-E X1總線標(biāo)準(zhǔn)規(guī)定的第二條差分信號(hào)線,用于接收數(shù)據(jù)。

三、PCIe接口的PCB設(shè)計(jì)

PCI-e x1接口的PCB設(shè)計(jì)需要遵循以下規(guī)范和注意事項(xiàng),這些規(guī)范能確保信號(hào)質(zhì)量和穩(wěn)定性。

1、差

2024-11-05 14:25:10

針腳是數(shù)據(jù)針腳。它用于低帶寬的設(shè)備如聲卡、網(wǎng)卡或其他不需要高速數(shù)據(jù)傳輸?shù)脑O(shè)備。2.PCIe x4:PCIe x4接口有四個(gè)數(shù)據(jù)通道,提供比x1接口更高的帶寬,插槽的長(zhǎng)度為39mm,分為前后兩組,一組

2025-08-21 16:51:24

本文提出了一種新的包括PCI9054單周期讀、寫和存儲(chǔ)器映射傳輸?shù)脑O(shè)計(jì),并討論了通用PCI總線高速數(shù)據(jù)采集卡的實(shí)現(xiàn)方案。

2021-06-08 06:28:30

PC104是嵌入式工控機(jī)的一種,其外部總線接口為PC104總線。使用堆疊的方式可以將多個(gè)PC104主板結(jié)合到一起,并通過(guò)螺栓固定,保證系統(tǒng)的牢固可靠,應(yīng)對(duì)惡劣的使用環(huán)境。由于PC104具有功耗低,體積小,擴(kuò)展性高,功能強(qiáng)大等優(yōu)點(diǎn),其已經(jīng)在航空航天、軍用武器裝備、工業(yè)控制等領(lǐng)域得到了廣泛的使用。

2019-09-27 06:30:40

本文介紹了一種基于PCI總線的高速噪聲檢測(cè)系統(tǒng),介紹了采用PCI 9052作為PCI總線接口芯片的數(shù)據(jù)采集部分的設(shè)計(jì)原理,并說(shuō)明了數(shù)據(jù)采集卡的高速采樣和速率可變的實(shí)現(xiàn)原理,給出了底層硬件同上層軟件的連接實(shí)現(xiàn)。

2021-04-09 06:21:14

一塊帶有PCIE接口的FPGA,一塊PCIE轉(zhuǎn)USB3.0板卡,想通過(guò)FPGA控制PCIE轉(zhuǎn)USB3.0板卡,實(shí)現(xiàn)USB3.0讀入數(shù)據(jù),經(jīng)過(guò)FPGA高速處理,不需要經(jīng)過(guò)電腦CPU。請(qǐng)問(wèn)各位專家:1.

2014-12-25 22:54:58

,AD采集到的數(shù)據(jù)需要經(jīng)過(guò)接口轉(zhuǎn)換層、FPGA的PCIeIP核、PCIe總線等才能到達(dá)計(jì)算機(jī)IO內(nèi)存空間。完成內(nèi)存地址映射后,用戶程序就可以從該內(nèi)存讀取數(shù)據(jù),進(jìn)行數(shù)據(jù)處理。在實(shí)際多線程的數(shù)據(jù)傳輸中,還會(huì)

2018-11-08 16:22:22

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)摘要:目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來(lái)設(shè)計(jì),其通用性、靈活性差,不能

2009-10-30 15:09:49

PCIe-8034 是一塊4口USB 3.0主控卡,專為工業(yè)自動(dòng)化和機(jī)器視覺(jué)相關(guān)應(yīng)用設(shè)計(jì)。USB 3.0或稱作高速USB,是一項(xiàng)新興的總線技術(shù),10倍于USB2.0的傳輸速度,尤其適用于高速數(shù)據(jù)存儲(chǔ)

2022-04-02 15:46:45

基于PCI-Express的高速數(shù)據(jù)交換設(shè)計(jì)及應(yīng)用:摘要: 提出了利用PCIE總線技術(shù)實(shí)現(xiàn)數(shù)據(jù)高速傳輸?shù)姆桨福Y(jié)合共享內(nèi)存、DMA等技術(shù)設(shè)計(jì)了基于PCI鄄Express總線的高速數(shù)據(jù)傳輸卡,實(shí)現(xiàn)

2009-05-26 23:36:45 33

33 本文根據(jù)SPI 同步串行接口的通信協(xié)議,介紹了在CPLD 中利用VHDL 語(yǔ)言實(shí)現(xiàn)PC/104

總線擴(kuò)展SPI 接口的設(shè)計(jì)原理和編程思想。通過(guò)該方法的介紹,使得那些沒(méi)有SPI

接口功能的

2009-05-30 09:28:18 41

41 PCIe-6314 是一塊4口USB 3.0主控卡,專為工業(yè)自動(dòng)化和機(jī)器視覺(jué)相關(guān)應(yīng)用設(shè)計(jì)。USB 3.0或稱作高速USB,是一項(xiàng)新興的總線技術(shù),10倍于USB2.0的傳輸速度,尤其適用于高速數(shù)據(jù)存儲(chǔ)

2022-10-26 17:53:07

在簡(jiǎn)要介紹了嵌入式PC/104 總線標(biāo)準(zhǔn)的基礎(chǔ)上,討論了基于該總線構(gòu)建的數(shù)據(jù)采集系統(tǒng)及其在機(jī)械加工設(shè)備狀態(tài)監(jiān)測(cè)中的應(yīng)用。本文對(duì)數(shù)據(jù)采集系統(tǒng)的組成、軟硬件設(shè)計(jì)、功能特點(diǎn)等

2009-07-30 14:35:17 55

55 PCI 總線接口控制器的設(shè)計(jì)是基于PCI總線的應(yīng)用設(shè)計(jì)的關(guān)鍵所在。本文在介紹PCI9054接口控制器的基礎(chǔ)上,給出了一種通用的高速數(shù)據(jù)采集接口的設(shè)計(jì),并提出了一種新的包括PCI9054單

2009-07-30 15:33:13 18

18 PCI 總線是先進(jìn)的高性能32/64 位局部總線,成為微機(jī)總線標(biāo)準(zhǔn)。PCI 總線接口設(shè)計(jì)較其它總線接口設(shè)計(jì)復(fù)雜,本文討論了接口設(shè)計(jì)的方案,選擇CH365 作為接口芯片,描述了數(shù)據(jù)采集

2009-08-19 10:19:55 27

27 通用串行總線作為一種嶄新的微機(jī)總線接口規(guī)范,其特點(diǎn)使其非常適合高速數(shù)據(jù)采集系統(tǒng)。文中介紹了一種基于USB 接口的數(shù)據(jù)采集板卡的設(shè)計(jì),包括硬件設(shè)計(jì)、固件設(shè)計(jì)、基于WINDOWS

2009-08-24 09:51:31 24

24 光纖接口,可以實(shí)現(xiàn) 4 路 QSFP28 100G 光纖的數(shù)據(jù) 實(shí)時(shí)采集、實(shí)時(shí)緩存與 PCIE 高速傳輸。該板卡采用 Xilinx 的高性能 Virtex Ultr

2025-12-23 15:52:33

PCI總線接口技術(shù)及其在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

一種基于PCI總線的高速數(shù)據(jù)采集傳輸系統(tǒng)的實(shí)現(xiàn),討論了PCI總線控制器9054的性能及三種傳輸模式,

2009-12-08 14:39:06 1338

1338

摘要:通過(guò)分析920T核ARM 處理器的高速片上系統(tǒng)總線AHB時(shí)序及其靜態(tài)存儲(chǔ)控制器SMC接口模型,研究IBM PC/AT和IEEE PC/104

2010-07-21 15:57:32 2133

2133

基于PCIe總線的超

2011-01-06 17:22:00 104

104 本文設(shè)計(jì)利用工控機(jī)上的PC104總線,通過(guò)共享雙端口RAM的方式,實(shí)現(xiàn)工控機(jī)與DSP之間的高速數(shù)據(jù)交換。本文詳細(xì)介紹了系統(tǒng)設(shè)計(jì)的基本思路,PC104與雙口RAM的硬件連接方式及其設(shè)計(jì)要點(diǎn)。

2011-04-15 15:02:22 91

91 本文說(shuō)明的這種PC104總線與DSP的數(shù)據(jù)通訊接口設(shè)計(jì),也可以作為采用其他計(jì)算機(jī)總線與DS P進(jìn)行16位數(shù)據(jù)通訊接口設(shè)計(jì)的參考。

2011-08-01 17:37:37 4626

4626 將PCIE與PCI、K1.X等總線技術(shù)進(jìn)行比較,分析它的技術(shù)特性和優(yōu)勢(shì),剖析數(shù)據(jù)包在各層中的流動(dòng)過(guò)程。/并且詳細(xì)闡述基于FPGA的兩種盯行性實(shí)現(xiàn)方案,即采用第三方PHY接口器件和低成本

2011-08-31 17:42:49 156

156 開發(fā)了多DSP雷達(dá)信號(hào)處理板卡。對(duì)DSP互連、DSP與FPGA通信以及基于Xilinx FPGA的PCIE總線進(jìn)行設(shè)計(jì)。系統(tǒng)可擴(kuò)展性好、效率高。用DriverStudio開發(fā)了WDM總線驅(qū)動(dòng)程序,具有很好的通用性和可移植

2012-05-28 17:40:08 75

75 一種基于ISA總線的高速同步數(shù)據(jù)采集擴(kuò)展卡,討論了經(jīng)合理的邏輯控制以協(xié)調(diào)高速A/D轉(zhuǎn)換與快速存儲(chǔ)操作的總線接口技術(shù),以及用極少的PC機(jī)I/O口地址資源實(shí)現(xiàn)數(shù)據(jù)的快速交換的方法

2012-06-06 09:53:31 1925

1925 設(shè)備間,其是一種基于數(shù)據(jù)包、串行、點(diǎn)對(duì)點(diǎn)的互連,因此所連接設(shè)備獨(dú)享通道帶寬。根據(jù)使用的版本號(hào)和通道數(shù),其性能具有可擴(kuò)展性。對(duì)于PCIe 2.0,每條通道在每個(gè)方向上的數(shù)據(jù)傳輸速率是5.0 Gbits-1。從PCIe1~PCIe16,能滿足一定時(shí)間內(nèi)出現(xiàn)的低速設(shè)備和高速設(shè)備的需求

2017-10-13 10:41:03 30

30 PCIE總線的多DSP系統(tǒng)接口設(shè)計(jì)

2017-10-31 10:42:03 23

23 和在PCM-5825上驗(yàn)證接口設(shè)計(jì)的X86匯編語(yǔ)言程序。 關(guān)鍵詞 DSP HPI PC104總線 FPGA VHDL源代碼 在一款嵌入式數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)中,采用TMS320VC54

2017-11-06 14:30:42 3

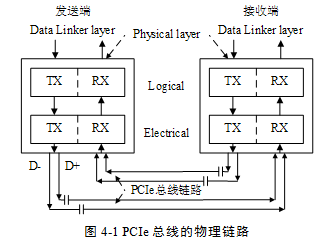

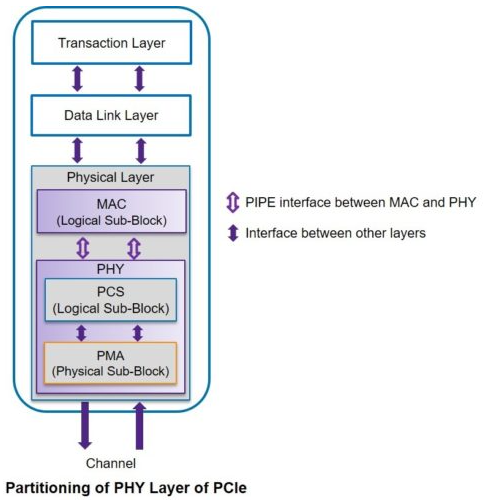

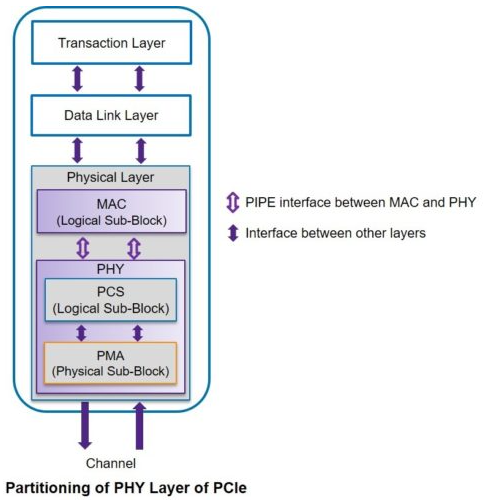

3 與PCI總線不同,PCIe總線使用端到端的連接方式,在一條PCIe鏈路的兩端只能各連接一個(gè)設(shè)備,這兩個(gè)設(shè)備互為是數(shù)據(jù)發(fā)送端和數(shù)據(jù)接收端。PCIe總線除了總線鏈路外,還具有多個(gè)層次,發(fā)送端發(fā)送數(shù)據(jù)時(shí)將通過(guò)這些層次,而接收端接收數(shù)據(jù)時(shí)也使用這些層次。PCIe總線使用的層次結(jié)構(gòu)與網(wǎng)絡(luò)協(xié)議棧較為類似。

2017-12-12 10:37:12 172661

172661 PC/104是最早由瑞士邏輯提出的一種工業(yè)總線標(biāo)準(zhǔn),它由最早的PC/104總線發(fā)展到PC/104+總線,直到目前的PC/104 Express,分別對(duì)應(yīng)ISA總線、PCI總線和PCIE總線。由于它是

2020-03-17 08:07:00 11032

11032

PCI Express是一種高性能互連協(xié)議,被廣泛應(yīng)用于網(wǎng)絡(luò)適配、圖形加速器、網(wǎng)絡(luò)存儲(chǔ)、大數(shù)據(jù)傳輸以及嵌入式系統(tǒng)等領(lǐng)域。在高速互連領(lǐng)域中,使用高速差分總線替代并行總線是大勢(shì)所趨。

2018-10-05 17:44:00 40345

40345 總線進(jìn)行高速數(shù)據(jù)采集,可以簡(jiǎn)化電路設(shè)計(jì),而且這種高速數(shù)據(jù)采集接口模塊可以在多次設(shè)計(jì)中重復(fù)使用,縮短產(chǎn)品的

2019-01-28 18:06:01 886

886 的基于PCIE總線的計(jì)算機(jī)板卡,以及將原先基于ISA總線或者PCI總線的板卡升級(jí)到PCIE總線上。PCIE總線與其它主流總線相比,速度更快,實(shí)時(shí)性更好,可控性更佳,所以CH367適用于高速實(shí)時(shí)的I/O控制卡、通訊接口卡、數(shù)據(jù)采集卡等。

2019-11-05 11:42:52 5778

5778

并行接口,用于制作低成本的基于PCIE總線的計(jì)算機(jī)板卡,以及將原先基于ISA總線或者PCI總線的板卡升級(jí)到PCIE總線上。PCIE總線與其它主流總線相比,速度更快,實(shí)時(shí)性更好,可控性更佳,所以CH368適用于高速實(shí)時(shí)的I/O控制卡、通訊接口卡、數(shù)據(jù)采集卡等。

2019-11-05 14:13:56 8408

8408

隨著電子技術(shù)的飛速發(fā)展,微處理器、存儲(chǔ)器技術(shù)的不斷革新,傳統(tǒng)的并行總線PCI逐漸成為系統(tǒng)整體性能的瓶頸。新一代的PCIE總線是最新的總線接口標(biāo)準(zhǔn),它變革了PCI總線并行傳輸?shù)膫鬏斈J剑捎?b class="flag-6" style="color: red">高速串行

2020-01-16 09:53:00 11307

11307

圖像采集和處理技術(shù)在機(jī)器視覺(jué)和圖像分析等諸多領(lǐng)域應(yīng)用十分廣泛。隨著高速的 PCI Express(PCIE)總線的出現(xiàn),基于 PCIE 接口的高速數(shù)據(jù)采集卡將在數(shù)據(jù)傳輸和處理量很大的場(chǎng)合發(fā)揮越來(lái)越重要的作用。

2020-07-16 17:02:04 3931

3931

被稱之為物理接口。 協(xié)議就是傳輸數(shù)據(jù)的規(guī)則。 我們通常說(shuō)的PCIE,既可以是PCIE信號(hào),也可以是PCIE接口、PCIE總線,還可以是PCIE協(xié)議。之所以這么復(fù)雜,主要原因就是每個(gè)人對(duì)概念認(rèn)知的差異。再比如,只要百度一下串行和并行,就會(huì)

2021-05-11 14:28:27 6414

6414

電子發(fā)燒友網(wǎng)站提供《PCIE總線接口芯片CH368技術(shù)手冊(cè).pdf》資料免費(fèi)下載

2022-09-09 14:59:23 8

8 電子發(fā)燒友網(wǎng)站提供《PCIE總線接口芯片CH367技術(shù)手冊(cè).pdf》資料免費(fèi)下載

2022-09-09 11:31:44 7

7 電子發(fā)燒友網(wǎng)站提供《PCIe 9110IM PCIe總線轉(zhuǎn)CAN設(shè)備手冊(cè).pdf》資料免費(fèi)下載

2022-10-17 10:59:17 3

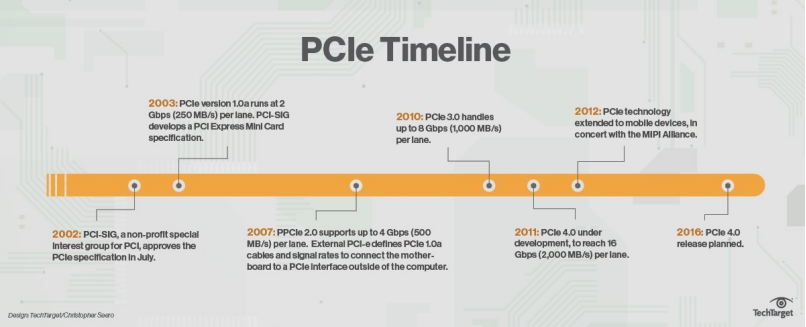

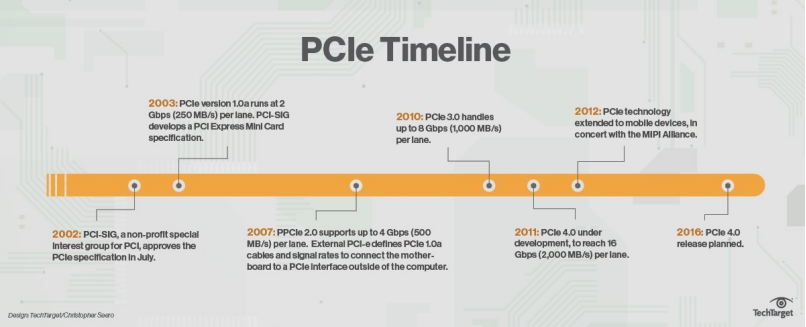

3 PCIe標(biāo)準(zhǔn)自從推出以來(lái),1代和2代標(biāo)準(zhǔn)已經(jīng)在PC和Server上逐漸普及,用于滿足高速顯卡、高速存儲(chǔ)設(shè)備對(duì)于高速數(shù)據(jù)傳輸?shù)囊蟆3鲇谥С指?b class="flag-6" style="color: red">總線數(shù)據(jù)吞吐率的目的,PCI-SIG組織在2010年制定了PCIe 3.0,即PCIe 3代的規(guī)范,數(shù)據(jù)速率達(dá)到8Gbps。

2022-10-20 09:59:21 9220

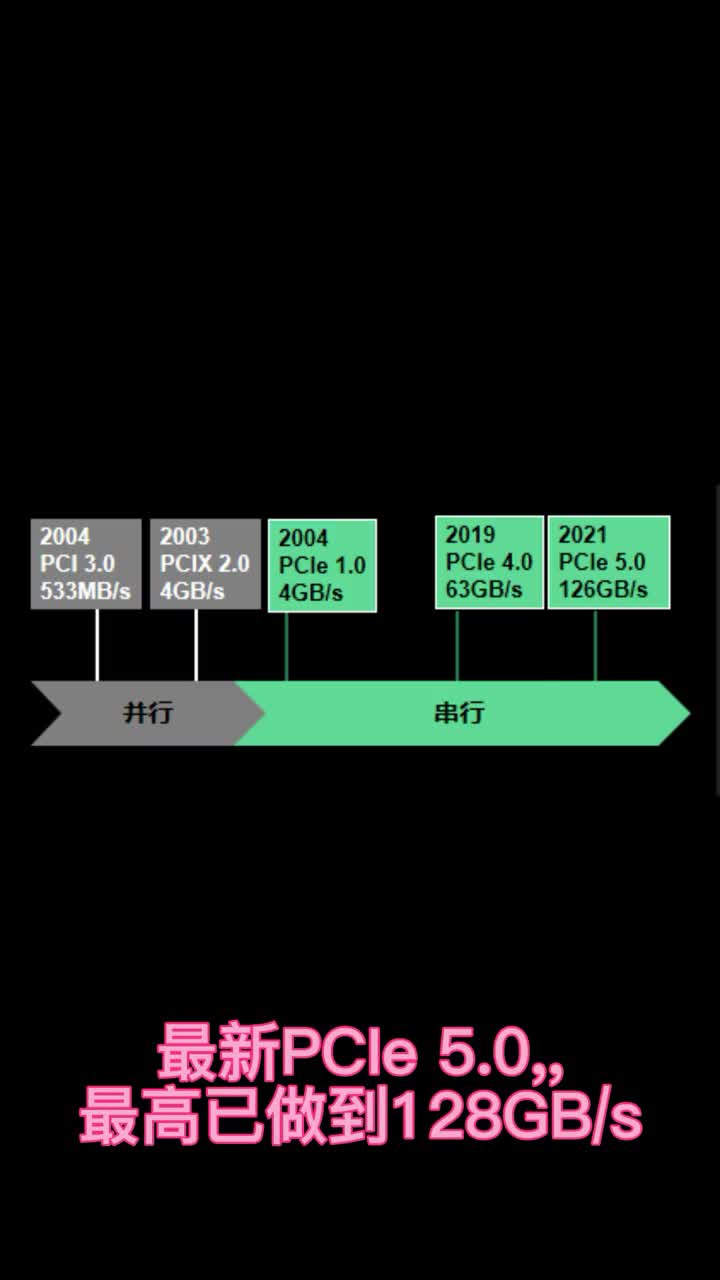

9220 PCIe全稱PCI-Express,中文名稱為高速串行總線。4.0是PCIe的一個(gè)版本,代表了系統(tǒng)總線的吞吐量,與CPU、GPU、顯卡的數(shù)據(jù)傳輸速率息息相關(guān)。

2022-12-05 14:19:30 15790

15790 PCIe 是一種多層串行總線協(xié)議,可實(shí)現(xiàn)雙單工鏈路。由于其專用的點(diǎn)對(duì)點(diǎn)拓?fù)洌峁?b class="flag-6" style="color: red">高速數(shù)據(jù)傳輸和低延遲。為了加快基于 PCIe 的子系統(tǒng)的驗(yàn)證和設(shè)備開發(fā)時(shí)間,英特爾定義了 PIPE(PCI

2023-05-26 11:43:19 5983

5983

PCIe是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),自2003年推出以來(lái),已經(jīng)成為服務(wù)器(Server)和PC上的重要接口。今天為大家簡(jiǎn)單介紹一下PCIe的發(fā)展歷史以及它的工作原理。 一、PCIe的由來(lái)

2023-07-04 18:15:03 23558

23558 電子發(fā)燒友網(wǎng)站提供《基于PCIE總線的多DSP系統(tǒng)接口設(shè)計(jì)和驅(qū)動(dòng)開發(fā).pdf》資料免費(fèi)下載

2023-10-24 09:36:29 0

0 PCIe是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),自2003年推出以來(lái),已經(jīng)成為服務(wù)器(Server)和PC上的重要接口。今天為大家簡(jiǎn)單介紹一下PCIe的發(fā)展歷史以及它的工作原理。

2023-12-20 10:00:06 3739

3739

(Peripheral Component Interconnect Express)是一種

高速串行

總線,用于計(jì)算機(jī)硬件設(shè)備之間的

數(shù)據(jù)傳輸。

PCIe 4.0和

PCIe 3.0是

PCIe總線的兩個(gè)不同版本,它們?cè)趥鬏?/div>

2024-07-10 10:12:09 15333

15333 PCIe接口的反射內(nèi)存卡是一種用于實(shí)時(shí)網(wǎng)絡(luò)的硬件設(shè)備。它將反射內(nèi)存集成在卡上,通過(guò)PCIe(PCIExpress)總線與計(jì)算機(jī)進(jìn)行連接。反射內(nèi)存卡的主要作用是在多個(gè)獨(dú)立計(jì)算機(jī)之間實(shí)現(xiàn)高速、低延遲

2024-09-04 10:38:26 1745

1745

PCI Express(PCIe)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),主要用于計(jì)算機(jī)內(nèi)部硬件設(shè)備之間的連接。以下是PCIe接口的工作原理的簡(jiǎn)要概述: 串行通信 :與傳統(tǒng)的并行PCI總線不同,PCIe

2024-11-06 09:19:16 5698

5698 隨著計(jì)算機(jī)技術(shù)的飛速發(fā)展,數(shù)據(jù)傳輸速度和處理能力的需求也在不斷提高。PCIe(Peripheral Component Interconnect Express)作為一種高效的數(shù)據(jù)傳輸接口,已經(jīng)成為

2024-11-13 10:22:38 5796

5796 在現(xiàn)代計(jì)算機(jī)系統(tǒng)中,PCI Express(PCIe)接口已經(jīng)成為連接各種高速設(shè)備的標(biāo)準(zhǔn)。從顯卡到固態(tài)硬盤,再到網(wǎng)絡(luò)接口卡,PCIe提供了一種高速的數(shù)據(jù)傳輸方式。然而,PCIe的帶寬并不是無(wú)限

2024-11-13 10:33:25 3936

3936 隨著數(shù)據(jù)傳輸需求的日益增長(zhǎng),計(jì)算機(jī)硬件接口也在不斷進(jìn)化。PCIe(Peripheral Component Interconnect Express)作為連接計(jì)算機(jī)內(nèi)部組件的高速串行總線標(biāo)準(zhǔn),已經(jīng)

2024-11-13 10:35:28 20174

20174 、網(wǎng)卡和聲卡等,以實(shí)現(xiàn)高效的數(shù)據(jù)傳輸。以下是對(duì)PCIe數(shù)據(jù)傳輸協(xié)議的介紹: 一、PCIe協(xié)議的基本概念 PCIe協(xié)議定義了一系列規(guī)范和要求,以實(shí)現(xiàn)在主機(jī)系統(tǒng)和外圍設(shè)備之間高效、可靠地進(jìn)行數(shù)據(jù)通信。它采用了高速串行點(diǎn)對(duì)點(diǎn)雙通道高帶寬傳輸方式,所連接的設(shè)備分配獨(dú)享通道帶寬,不共享總線,

2024-11-26 16:12:57 5876

5876 PCIE737是一款基于PCIE總線架構(gòu)的KU115 FPGA的12路光纖通道處理平臺(tái),該板卡具有1個(gè)PCIe Gen3x8主機(jī)接口、3個(gè)QSFP+ 40G光纖接口,可以實(shí)現(xiàn)3路QSFP+ 40G光纖的數(shù)據(jù)實(shí)時(shí)采集、實(shí)時(shí)緩存與PCIE高速傳輸。

2025-11-03 16:31:23 574

574

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論