串行互連接口的速率在過去幾年里得到了顯著提高,每線的速率從2.5Gbit/s提高到10Gbit/s,而每個接口可以容納1到32線。8B10B作為互連接口的一種編碼技術,設計簡單、性能出眾,因此成為應用最廣泛的技術。然而,它的系統開銷高達25%,問題突出。為了解決這個問題,設計者們一直在探尋改進的方法。本文就將介紹一些低開銷的編碼技術,并討論它們的優勢與存在的問題。

編碼技術基礎理論

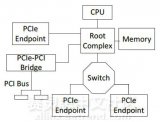

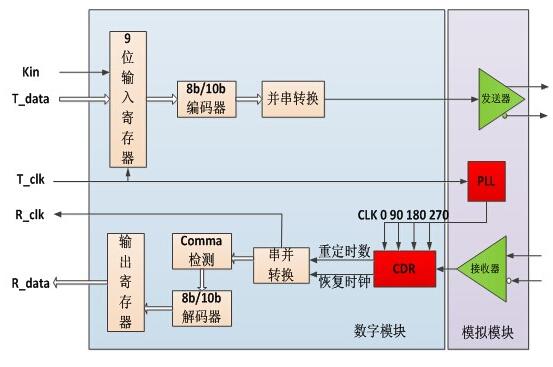

目前,高速接口正在被廣泛應用于包括SATA、SAS、高速PCI等多種標準中。這些接口的速率甚至可以達到并超過每線10Gbits/s。同時,所有主流ASIC和FPGA平臺也都支持這些高速接口技術。從結構上看,這些高速接口主要包括三個組成部分:

電路部分(串行/解串行)

物理部分(實現編碼)

鏈路與協議部分(高層)

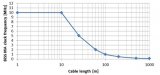

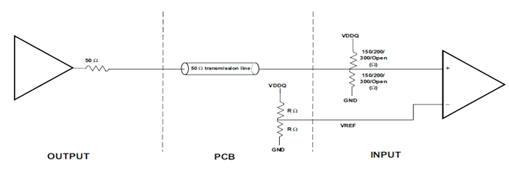

支持多速率、多協議的串行/解串行器已經實現。以OIF(光互聯論壇)為例,他們已經為兩組速率制定了電路規范,分別為5Gbits/s-6.375Gbits/s和10Gbits/s-11Gbits/s。OIF同樣為兩種應用距離制定了規范,分別為短距離(采用一個連接器,8英寸)和長距離(采用兩個連接器,40英寸)。串行/解串行器還可以被設計用來滿足更多的規范,包括不同的速率、距離、電路規格等等。

物理部分的主要任務是對數據進行編碼,以保證串行/解串行器的正常運行。這些編碼的目的包括:確保必須的變換(“1”到“0”和“0”到“1”的變換),保證穩定的直流均衡(“0”碼與“1”碼的個數相當),以及滿足其它標準的要求(最大化信道帶寬利用率,提高對誤差的容忍能力等等)。

以Manchester編碼為例,這種編碼技術被廣泛應用于10Mbit/s以太網連接中。它的編碼方式非常簡單,就是將“1”編碼為“01”,將“0”編碼為“10”。從編碼原理我們可以推斷出:

最大相同連續字符數為2(正常情況下連續出現兩個以上連續“0”或“1”是不可能的)。

保證穩定的直流均衡(“0”的個數與“1”的個數總是相同的)。

具備1bit誤碼糾錯能力(“00”或者“11”是無效碼)。

高達100%的系統開銷。

擾碼技術是串行鏈路常用的另一種編碼技術。這種技術將偽隨機序列與原始碼流混合,以實現轉換、直流均衡等目的。偽隨機發生器由線性反饋移位寄存器產生的最長序列(m序列)構成1。此序列的周期為2n,其中n為線性反饋移位寄存器特征多項式的最高階。例如SONET/SDH的特征多項式為x7+x6+1,它的序列長度為27-1,即127。

擾碼器包括兩種類型,分別為邊擾碼器與自同步擾碼器。通常,邊擾碼器的寄存器狀態與發送數據異或構成它的下一個狀態,這需要在輸入與輸出之間“重置/同步”擾碼器狀態。自同步擾碼器直接將輸入數據作為擾碼器狀態,不需要重置和同步過程。

8B10B編碼技術

8B10B是應用最廣泛的編碼技術。它被用于串行連接SCSI、串行ATA、光纖鏈路、吉比特以太網、XAUI(10吉比特接口)、PCI Express總線、InfiniBand、Seria RapidIO、HyperTransport總線以及IEEE1394b接口(火線)技術中。

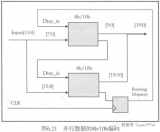

8B10B2將8bit代碼組合編碼成10bit代碼,代碼組合包括256個數據字符編碼和12個控制字符編碼(如表1所示)。通過仔細選擇編碼方法可以獲得不同的優化特性。這些特性包括滿足串行/解串行器功能必須的變換;確保“0”碼元與“1”碼元個數的一致,又稱為直流均衡;確保字節同步易于實現(在一個比特流中找到字節的起始位);以及對誤碼率有足夠的容忍能力和降低設計復雜度。

8B10B中所有的編碼都具備3到10種變換。每個碼字確保:

在一行中不會產生超過四個連“1”或連“0”;

“1”與“0”的不平衡度(不平衡度指“0”的個數減去“1”的個數)不會超過2個碼字(5個“1”/5個“0”,4個“1”/6個“0”或4個“0”/6個“1”)。

8B10B采用一種簡單的方法保證了編碼的直流平衡。在不平衡時,采用兩個10bit字符表示一個8bit字符,其中一個稱為RD-,表示“1”的個數比“0”多2個,另一個稱為RD+,表示“1”的個數比“0”少2個。選取合適的RD字符可以保證不平衡度不大于1。同時,采用只有在控制字符(K28.5,K28.1,K28.7)中才有的特殊字符可以保證同步定位的準確。

8B10B借助總共268個字符及它們的反轉碼,還可以檢測任何可能破壞不平衡的誤碼。但是,即使接收機接收到了正確的碼字,有時它們也有可能因為不平衡性而導致誤碼,這種現象被稱為誤碼復制。8B10B編碼技術將8bit數據分成3bit和5bit兩組,因此可以看作是3B4B和5B6B編碼技術的組合。

改進傳統8B10B編碼技術的一種方法是,在編碼之前增加擾碼過程。有證據證明,特殊的模式3或差分群時延可能會導致重復模式產生不可預測的誤碼。解決這個問題最直接的辦法就是在編碼之前對數據進行擾碼。

以上這些特點保證了8B10B編碼成為使用最廣泛的編碼技術。它最主要的缺點只有一個,就是高達25%的系統開銷。

低開銷編碼

最近,人們提出了幾種降低8B10B編碼技術系統開銷的改進方法。這些改進主要基于以下兩個基礎:一是隨著鏈路速率與數量的增加,25%系統開銷的問題顯得越來越突出;二是集成技術的進步,使得硬件復雜度不再像過去那樣重要。

在這些低開銷的改進技術中,有四個非常相似的技術脫穎而出,受到人們的廣泛關注:

64B66B編碼技術,應用于10G以太網4;

OIF CEIP5;

10GBase-KR6,應用于10GbE背板連接;

Interlaken7。

這些技術的共同點是,都以提高硬件設計復雜度(門數目)為代價,換取了較低的系統開銷。

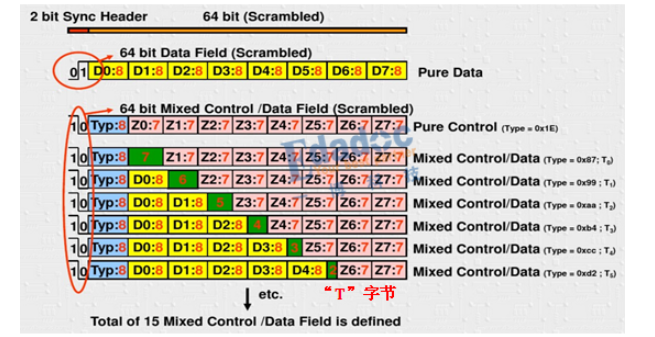

64B66B編碼技術。這種技術應用于10G以太網(10GBase-R),是一種編碼與擾碼相結合的技術。首先,數據被分成8個字節一組(總共64比特)。然后,這些字節采用自同步擾碼實現隨機化,其特征多項式為x58+x39+1。最后,如果這些8字節組是數據字符,那么會加上“01”標識;如果有一個或多個字節是控制字符,那么就會加上“10”標識。

在此編碼技術中,將8個字節的字符(由8B10B編碼定義,可能是數據或控制字符)編碼為64比特長字符的過程通常被稱為轉換代碼。GFP-T8為組合8B10B的8比特為64比特字符提供了標準方法。而10GbE為10G以太網和10Gbit/s光纖鏈路提供了相關子集的映射表。用于同步定位的“01”和“10”比特不參與擾碼過程。這是因為其它比特在擾碼后可能取任何值,只有同步比特“01”和“10”在經歷長途傳輸后基本保持不變。同步比特還可以保證每隔66比特至少會發生一次轉換。

CEI-P編碼技術。這種技術由OIF定義。它的系統開銷與64B66B編碼相等,大約為3%。當然,它還有很多不同之處。

CEI-P采用邊擾碼,特征多項式為x17+x14+1。這樣做的優點是可以有效防止誤碼復制的產生(擾碼的狀態不會受之前產生的誤碼影響),缺點是需要在發送與接收之間同步擾碼狀態。

當邊擾碼與線路誤碼無關時,如果發送數據與擾碼值相同(或恰好相反),那么擾碼器會輸出非常長的“1”或“0”序列。而這種非常長的擾碼輸出序列比短的序列對誤碼的容忍能力更強。

CEI-P編碼采用幀同步取代定位同步。64B66B采用同步比特實現定位,而CEI-P將24個64比特碼字看作一幀,這樣用1個比特就可以實現數據或控制字符的判定。附加的24比特用于誤碼校驗與信令。其中誤碼校驗使用20比特,采用fire-code技術,可以糾正長達7比特的突發誤碼串。

10GBase-KR編碼技術。這種技術的系統開銷與CEI-P一致,都是3%,主要的不同在于幀的長度是32個碼字,而不是24個碼字。這樣一來糾錯碼長度就是32比特,可以糾正比CEI-P更長的突發誤碼串。而它采用的擾碼規則與10GbE相似。只不過它的擾碼多項式與10GBase-R一致,寄存器采用的初始序列為“010101……”,而且每一幀重置一次。

Interlaken PHY編碼技術。Interlaken編碼技術的系統開銷為4.5%(64/67)。它的碼字基于64比特。與其它低開銷編碼技術相比,Interlaken的主要不同之處在于:

同步信號為3個比特,其中兩個比特用于區分數據與控制,一個比特用于標識數據是否轉化。數據轉化比特的目的與8B10B類似,都是為了保證直流平衡;

Interlaken采用與10GbE相同的邊擾碼特征多項式實現擾碼。這樣可以避免因采用自同步擾碼器所導致的誤碼復制問題。一個同步碼字用于傳遞擾碼器狀態,而且它非常長的擾碼長度保證不會出現很長的連“0”或者連“1”;

整個鏈路采用CRC32循環冗余校驗方式保證誤碼校驗。

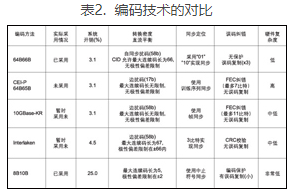

表2對比了以上討論的幾種編碼技術的異同,主要包括以下幾點:

實際采用情況;

系統開銷;

轉換密度與直流平衡;

同步定位;

誤碼(保護、校驗、復制);

硬件復雜度(門數目)。

雖然8B10B編碼行之有效,而且被廣泛采用,但是它高達25%系統開銷的缺點在未來數百吉比特鏈路與系統應用中顯得越來越突出。現在已經有若干種低開銷的編碼技術,它們具備不同的優勢與缺點。但是到目前為止,還沒有哪種低開銷技術能夠脫穎而出,成為繼8B10B之后被廣泛采用的首選技術。不過,本文所提到的幾種技術都以提高硬件復雜度為代價,以滿足低開銷的要求。

責任編輯:gt

電子發燒友App

電子發燒友App

評論