本例程詳細(xì)介紹了如何在FPGA上實現(xiàn)Serial RapidIO(SRIO)通信協(xié)議,并通過Verilog語言進(jìn)行編程設(shè)計。SRIO作為一種高速、低延遲的串行互連技術(shù),在高性能計算和嵌入式系統(tǒng)中廣

2025-11-12 14:38:17 5408

5408

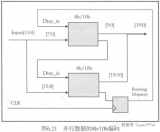

USB 3.0的傳輸編碼方式與USB 2.0有所不同,從USB 3.0規(guī)范中我們了解到,USB 3.0采用的是8b/10b編碼方式

2011-11-22 16:22:57 10296

10296

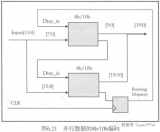

為了在USB 3.0中實現(xiàn)數(shù)據(jù)的8 b/10 b編解碼,把8b/10b編解碼分解成5 b/6 b編解碼和3 b/4 b編解碼,然后在FPGA上實現(xiàn)了具體的硬件電路。

2011-11-30 11:38:18 4000

4000

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-12-12 09:19:08 3688

3688

無線電系統(tǒng),基帶信號處理,無線仿真平臺,高速圖像采集、處理等。支持熱插拔,設(shè)計芯片可以滿足工業(yè)級要求。 2、處理板技術(shù)指標(biāo)SRIO 4X交換網(wǎng)絡(luò)連接兩片DSP以及兩片Virtex-6 FPGASRIO

2015-05-19 17:34:31

4X交換網(wǎng)絡(luò)連接兩片DSP以及兩片Virtex-6 FPGASRIO 4X交換網(wǎng)絡(luò)連接4組SRIO 4X至VPX P1;具備一個SRIO 4X交換芯片;具備高速RocketIO數(shù)據(jù)傳輸鏈路;具備

2014-05-30 11:36:40

UD PCIe-402全國產(chǎn)化信號處理模塊為標(biāo)準(zhǔn)PCIe全高半長的結(jié)構(gòu),對外支持PCIe2.0×8通信,也可以采用千兆以太網(wǎng)接口進(jìn)行通信,模塊為100%國產(chǎn)化設(shè)計。FPGA芯片選用國產(chǎn)

2023-05-09 20:07:51

8b/10b編碼是一種用于減少數(shù)據(jù)線上的低效能時鐘信號傳輸?shù)募夹g(shù),通過在數(shù)據(jù)流中插入特殊的控制字符,來同步數(shù)據(jù)和時鐘。在Verilog中實現(xiàn)8b/10b編碼器可以通過以下步驟完成:

定義8b/10b

2024-03-26 07:55:35

8b/10b編碼用的控制字是K28.5,但是解碼時用非K28.5的控制字能把數(shù)據(jù)解碼出來嗎?

2019-01-02 14:47:15

小弟最近在調(diào)用Aurora 8b/10b IP模塊時,在用modelsim功能仿真時,一切正常。 但是直接使用了例化后的example,并將Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

使用ISE 14.1,我試圖在Virtex-4 FX中生成一個簡單的Aurora 8B / 10B內(nèi)核。核心似乎生成(生成完整的.vhd函數(shù)模型文件),但不會在.vho文件中生成任何代碼以實例化到我

2019-03-20 15:43:41

我開發(fā)了一個應(yīng)用程序,包括Userapp,Aurora IP 8b10b v8.3,兩個FIFO(Tx和Rx)和sram模塊。我使用ISim模擬了總應(yīng)用程序。我得到了所需的結(jié)果。現(xiàn)在,我的疑問

2020-03-30 08:49:04

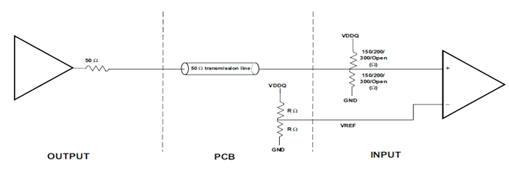

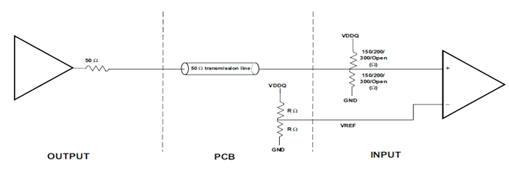

(Virtex-5)或19.2Gbps(Virtex-6)2. 高速LVDS數(shù)據(jù)發(fā)送:訓(xùn)練序列產(chǎn)生,數(shù)據(jù)成幀,8B/10B編碼,數(shù)據(jù)并行轉(zhuǎn)串行,隨路時鐘產(chǎn)生等3. 高速LVDS數(shù)據(jù)接收:接收時鐘檢測(檢測接收時鐘

2012-05-21 09:32:15

你好。如今,我設(shè)計了使用Virtex-6的主板。我想知道Virtex-6是否有專用的PLL輸出引腳(clkout引腳)。我檢查了Virtex-6系列概述Virtex-6 FPGA時鐘資源用戶指南

2020-06-12 10:05:21

嗨,XilinxIDF站點表明IDF僅支持Virtex-4,Virtex-5,Spartan-6和7系列FPGA。我可以在Xilinx Virtex-6 FPGA上使用IDF嗎?有沒有人嘗試過使用IDF和Virtex-6 FPGA?謝謝,季米特里斯

2020-07-08 15:56:53

三種常見嵌入式設(shè)備通信協(xié)議是什么?

2021-12-23 08:17:02

串行總線協(xié)議PCIe、ASI和sRIO之間有什么不同?

2021-05-25 07:05:09

協(xié)議分析儀作為網(wǎng)絡(luò)通信和嵌入式系統(tǒng)調(diào)試的核心工具,需支持從低速總線到高速接口、從有線到無線的廣泛協(xié)議。以下是常見協(xié)議分類及典型應(yīng)用場景,幫助選擇適合的分析儀:一、高速串行總線協(xié)議1. 計算機(jī)外設(shè)接口

2025-07-17 15:40:38

之間傳輸單獨的RGB顏色、音頻數(shù)據(jù)和輔助數(shù)據(jù)。視頻傳輸格式采用TMDS編碼,二進(jìn)制數(shù)據(jù)采用8b/10b算法編碼。 HDMI 2.0規(guī)范允許TMDS比特率高達(dá)6gbps,TMDS時鐘率為TMDS比特率

2020-04-26 15:51:14

你好, 我正在使用Aurora 8B / 10B v5.3 IP內(nèi)核,Virtex 5 FPGA用于使用SFP電纜的GB收發(fā)器。我使用核心生成器創(chuàng)建了IP核,獲得了示例設(shè)計(所有文件)。我模擬了示例

2020-04-07 14:52:25

的邏輯1或邏輯0有多個位沒有變化時,信號的轉(zhuǎn)換就會因為電壓位階的關(guān)系而造成信號錯誤。直流平衡的最大好處便是可以克服以上問題。8B/10B編碼是目前許多高速串行總線采用的一種編碼機(jī)制,如1394b

2018-12-11 11:04:22

RocketIO高速串行接口本人在北京工作6年以上,從事FPGA外圍接口設(shè)計,熟練使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX協(xié)議,Aurora協(xié)議

2014-03-01 18:46:35

Xilinx Virtex-6系列選型1 Xilinx公司Virtex-6 FPGA共有3個系列:Virtex-6 LXT – 高邏輯密度,高速串行收發(fā)器,高密度IOVirtex-6 HXT – 高

2012-02-28 14:56:59

系列芯片,核心板支持Xilinx Zynq-7035、Zynq-7045和Zynq-7100三種型號。開發(fā)板由核心板+底板組成,外設(shè)資源豐富,板載2路千兆以太網(wǎng)接口(PS+PL)、PCIe2.0x8

2024-09-02 17:18:43

imx6q 開發(fā)板, 使用forlinx.com 上對應(yīng)的內(nèi)核linux 4.1.15-2018.10.23, uboot-2016.03-r0, 插入pcie2.0的卡開機(jī)后,dmesg報錯

2022-01-10 07:23:12

/11011232.html

參考二:高速串行總線系列(1)8B/10B編碼技術(shù)

https://blog.51cto.com/u_15338162/5198192

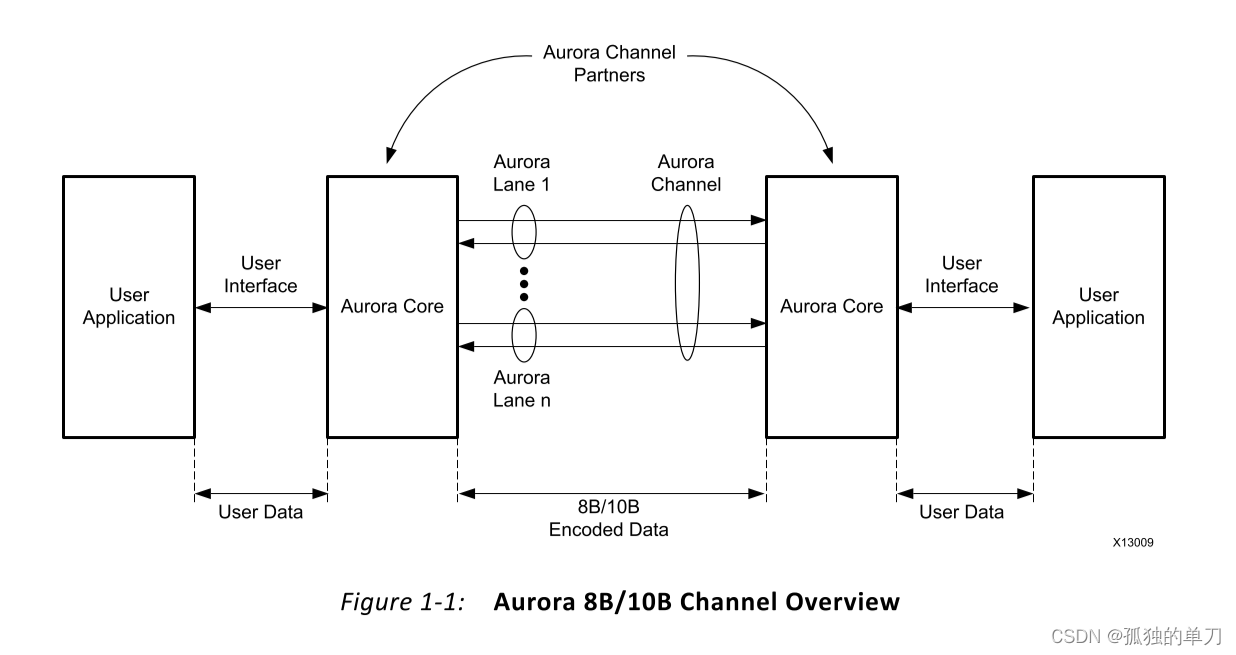

參考三:Aurora 協(xié)議學(xué)習(xí)理解

2024-11-14 21:29:37

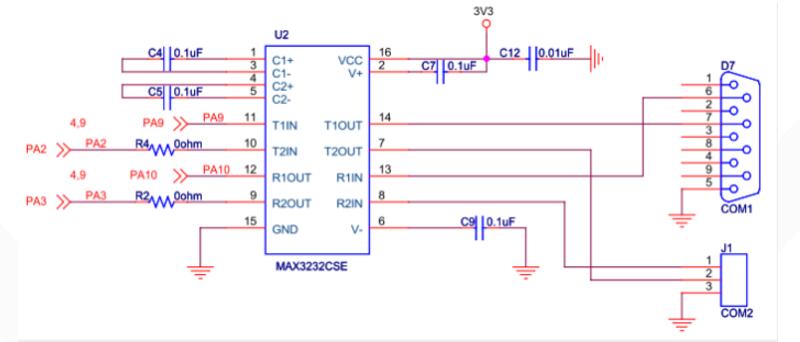

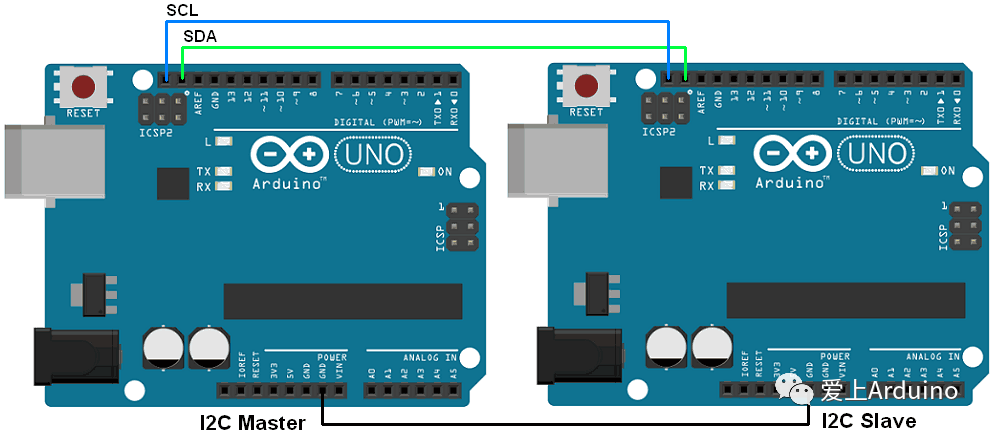

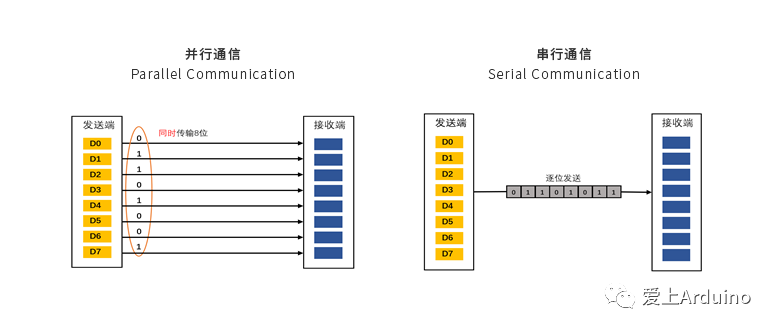

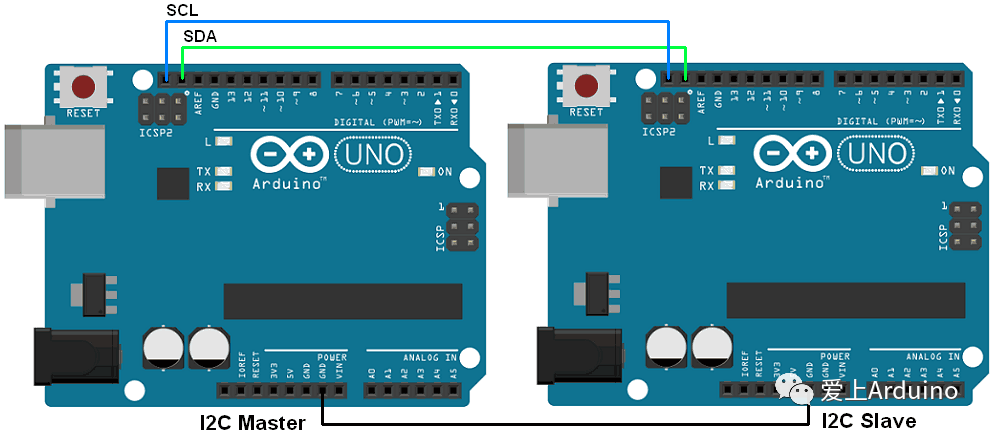

UART、 I2C 和 SPI 是單片機(jī)系統(tǒng)中最常用的三種通信協(xié)議。1、初步介紹SPI 是一種高速的、全雙工、同步通信總線,標(biāo)準(zhǔn)的 SPI 也僅僅使用 4 個引腳,常用于單片機(jī)和 EEPROM

2021-11-18 09:22:58

單片機(jī)系統(tǒng)中最常用的三種通信協(xié)議是什么?

2022-02-17 06:03:46

(Virtex-5)或19.2Gbps(Virtex-6)或22.4Gbps(Kintex-7)2. 高速LVDS數(shù)據(jù)發(fā)送:訓(xùn)練序列產(chǎn)生,數(shù)據(jù)成幀,8B/10B編碼,數(shù)據(jù)并行轉(zhuǎn)串行,隨路時鐘產(chǎn)生等3.

2014-03-01 18:47:47

(Virtex-6)或22.4Gbps(Kintex-7)2. 高速LVDS數(shù)據(jù)發(fā)送:訓(xùn)練序列產(chǎn)生,數(shù)據(jù)成幀,8B/10B編碼,數(shù)據(jù)并行轉(zhuǎn)串行,隨路時鐘產(chǎn)生等3. 高速LVDS數(shù)據(jù)接收:接收時鐘檢測(檢測接收

2014-03-20 22:58:55

你好,我正在嘗試使用Aurora 8B / 10B建立僅傳輸(流媒體)。現(xiàn)在使用Vivado 2014.4進(jìn)行模擬階段。我知道GTXE2_COMMON原語需要在設(shè)計中使用以包含一個QUAD PLL

2020-08-14 08:49:13

嗨,我正在嘗試將Aurora與Virtex-6 LX240t配合使用。示例設(shè)計是由核心生成器(11.5和12.1)生成的測試代碼。當(dāng)我使用環(huán)回模式(近端PCS和PMA)進(jìn)行測試時,兩者都能正常工作

2020-06-02 13:14:40

本方案是以CME最新的低功耗系列FPGA的HR03為平臺,實現(xiàn)8/10b的SerDes接口,包括SERDES收發(fā)單元,通過完全數(shù)字化的方法實現(xiàn)SERDES的CDR(Clock Data

2019-10-21 07:09:44

“HTG-V6-PCIE”。賽普拉斯CY7C67300 EZ-Host?可編程嵌入式USB Hostand外設(shè)控制器提供USB 2.0接口。是否可以通過賽普拉斯USB配置Virtex-6 FPGA?當(dāng)我嘗試

2020-07-08 07:17:34

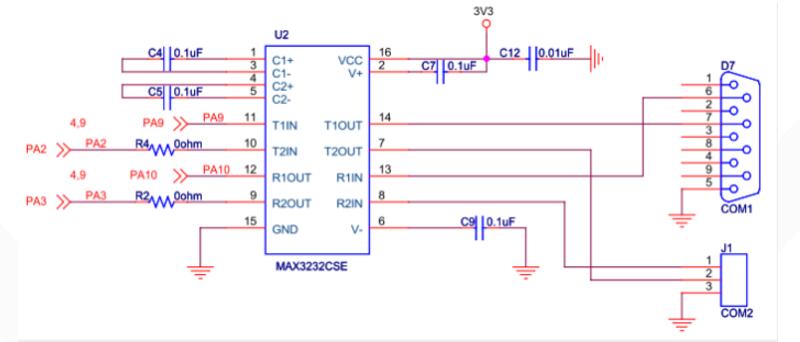

RXD。RS232和RS485協(xié)議:RS485、RS232都是基于串口控制器的協(xié)議,只不過他們倆只是對串口控制器加了一些電氣上面的處理使得串口傳輸?shù)臄?shù)據(jù)更遠(yuǎn)和更穩(wěn)定而已。舉個形象的例子:串口、RS485、RS232這三種協(xié)議都是表示從A車站發(fā)送100個旅客到B車站的,串口協(xié)議只是規(guī)定100個旅客從A車站到

2021-12-14 06:22:31

通過研究CAN2.0B協(xié)議規(guī)范,對報文格式的分析和標(biāo)識符的分配,設(shè)計出了基于CAN總線的智能建筑監(jiān)控系統(tǒng)的通信協(xié)議。

2021-06-02 06:48:03

大家好,我使用的是Vivado 2016.4和Virtex 7 XC7VX485T FPGA。我需要知道是否有一個選項可以禁用Aurora IP Core 8B / 10B中的時鐘補(bǔ)償功能。我可以看到IP核心文件,但它們都是只讀的。謝謝,馬諾

2020-08-18 09:43:40

親愛的先生,我正在使用Vivado 2015.4。我想在收發(fā)器向?qū)е惺褂猛ǖ澜壎ǎ獵B在手冊中是灰色的。另外,我找不到在收發(fā)器向?qū)е袉⒂?b class="flag-6" style="color: red">8b / 10b編碼器的方法。如果你能給我一些建議,我將不勝感激。問候,泰迪王

2020-08-04 08:32:57

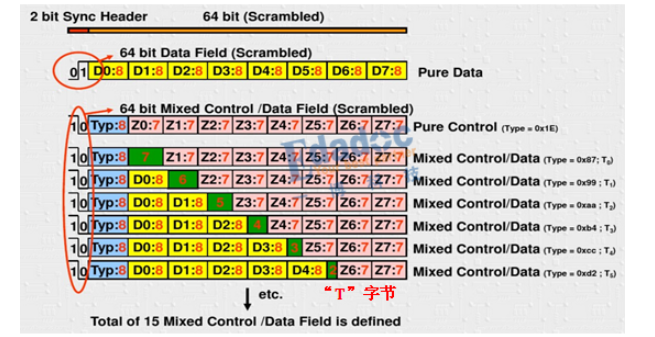

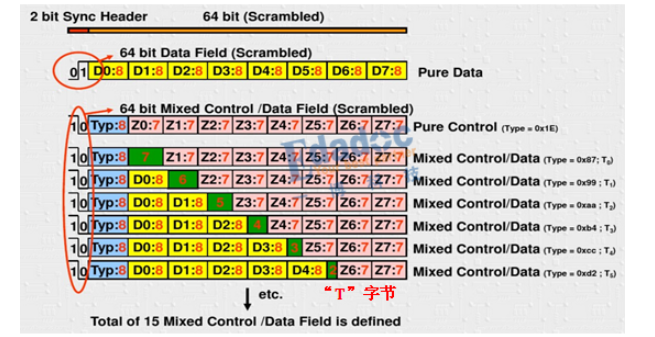

作者:黃剛上文說完了8B/10B之后,我們再來說說貌似更復(fù)雜的64B/66B編碼。很多人可能在想,8B/10B編碼主要作用的優(yōu)化直流平衡,從8bit中插2個bit進(jìn)去,這樣的話最終效果能夠使長0或者

2019-07-19 07:35:57

用于高速串行設(shè)計和一致性測試的專用配置的數(shù)字串行分析儀型號 探頭尖端的增強(qiáng)帶寬擴(kuò)展到支持多個帶寬步驟以實現(xiàn)高級信號完整性獨特的串行碼型觸發(fā)高達(dá) 3.125 Gb/s 和 8b/10b 標(biāo)準(zhǔn)協(xié)議觸發(fā),用于

2021-12-22 14:40:11

用ASM1184e和RTL8111HS做的一個PCIE2.0轉(zhuǎn)四口網(wǎng)卡,目前網(wǎng)卡識別不到,有做過類似的可否指導(dǎo)一二,必有重謝!

2023-10-31 17:22:10

大家好,Vivado版本:15.2FPGA:Artix 7 xc7a50tAurora 8b / 10b IP v11.0(Rev 1) - 使用VHDL創(chuàng)建車道:1我最近一直面臨著Aurora

2020-08-06 09:34:12

你好我對DSP和SRIO之間的通信感興趣。有人知道virtex-6 FPGA是否有srio引腳,以及如何配置?

2020-06-14 14:22:51

一、高速接口

8B/

10B的作用? 在數(shù)字

通信中編碼和加擾的作用是不同的。編碼通常有信源編碼和信道編碼,

8b/

10b是信道編碼,信道編碼的作用是通過增加冗余(此外冗余為2

b)以提高數(shù)據(jù)傳輸?shù)目煽啃浴<?/div>

2022-01-18 06:16:43

Virtex-6 FPGA GTX收發(fā) User Guide:This document shows how to use the GTX transceivers in Virtex®-6

2009-12-31 17:05:28 25

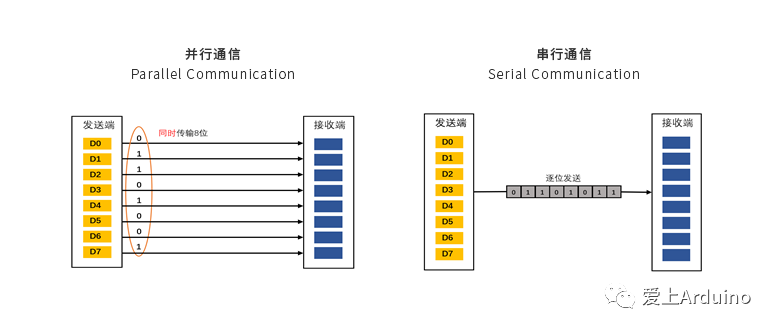

25 采用Xilinx 公司Virtex- II Pro 系列FPGA 內(nèi)嵌得SERDES 模塊———RocketIO 作為高速串行協(xié)議的物理層, 利用其8B/10B的編解碼和串化、解串功能, 實現(xiàn)了兩板間基于數(shù)據(jù)幀的簡單高速串行傳輸

2010-09-22 08:44:28 28

28 探討了一種基于串行通信的簡單、高效的通信協(xié)議制定方法。實驗結(jié)果證明,該協(xié)議有效提高了串行通信的通信效率。

2010-12-03 17:22:53 18

18 此課程將教會你:1)描述Spartan-6 和Virtex-6 FPGA的6輸入LUT和CLB建設(shè)的所有功能;2)指定Spartan-6 和Virtex-6的CLB資源和可用的Slice配置;3)定義可用的RAM和DSP資源塊;4)正確設(shè)計I/O塊和S

2010-12-14 15:09:48 0

0 賽靈思最新一代Virtex-6 FPGA系列兼容PCI Express 2.0標(biāo)準(zhǔn)

賽靈思公司宣布其最新一代Virtex-6 FPGA系列兼容PCI Express 2.0標(biāo)準(zhǔn),與前一代產(chǎn)品系列相比功耗降低

2009-07-29 14:39:46 1119

1119 賽靈思最新一代Virtex-6 FPGA系列兼容PCI Express 2.0標(biāo)準(zhǔn)

賽靈思公司宣布其最新一代Virtex-6 FPGA系列兼容PCI Express 2.0標(biāo)準(zhǔn),與前一代產(chǎn)品系列相比功耗降低50%,與競爭產(chǎn)品相

2009-11-11 16:46:51 1123

1123 Virtex-6 FPGA ML605開發(fā)評估技術(shù)方案

Virtex-6 FPGA是Xilinx公司的目標(biāo)設(shè)計平臺,提供集成的軟件和硬件,有利于設(shè)計集中力量進(jìn)性產(chǎn)品創(chuàng)新. Virtex-6系列包括LXT, SXT和HXT子系列,適

2010-04-22 18:07:58 4151

4151

摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統(tǒng)設(shè)計方案。與現(xiàn)有的8B/10B編解碼方案相比,該方案是一種利用FPGA實現(xiàn)8B/lOB編解碼的模塊方

2011-05-26 11:08:20 4329

4329

一種高效的串行通信協(xié)議的制定及實現(xiàn)

2011-11-09 18:08:51 56

56 PCIE 3.0相對于它的前一代PCIE 2.0的最主要的一個區(qū)別是速率由5GT/s提升到了8GT/s。為了保證數(shù)據(jù)傳輸密度和直流平衡以及時鐘恢復(fù),PCIE 2.0中使用了8B/10B編碼,即將每8位有效數(shù)據(jù)編碼為10位

2012-12-03 11:45:13 57

57 CAN_2.0中文_通信協(xié)議。

2016-03-30 16:51:06 25

25 漢邦DVR通信協(xié)議規(guī)范2.0

2017-01-04 14:19:49 0

0 基于減少8B/10B編碼器占用的邏輯資源和保證該編碼器誤碼率為0的目的,采用查表法和組合邏輯實現(xiàn)相結(jié)合的方法設(shè)計實現(xiàn)了符合嵌入式互連規(guī)范Rapidl0協(xié)議的8B/10B編碼器,通過偽隨機(jī)二進(jìn)制序列

2017-11-06 17:04:21 7

7 Xilinx公司的Virtex-6 FPGA包括Virtex-6 LXT FPGA,Virtex-6 SXT FPGA和Virtex-6 HXT FPGA三個亞系列,采用40nm

2017-11-24 16:26:40 2715

2715 spartan-6/6L和Virtex-6的器件庫

2018-02-05 12:04:37 29

29 為了提高串行數(shù)據(jù)傳輸?shù)目煽啃裕F(xiàn)在很多更高速率的數(shù)字接口采用的是對數(shù)據(jù)進(jìn)行編碼后再做并串轉(zhuǎn)換的方式…

2018-03-14 16:23:59 18523

18523 除了差分總線,PCIe還引入了嵌入式時鐘的技術(shù)(Embedded Clock),即發(fā)送端不再向接收端發(fā)送時鐘,但是接收端可以通過8b/10b的編碼從數(shù)據(jù)Lane中恢復(fù)出時鐘。

2018-04-19 09:20:19 18873

18873

本文首先介紹了STM32串口硬件電路及串口編程,其次介紹了STM32的三種串口通信協(xié)議,最后介紹了STM32串口通信程序設(shè)計要點。

2018-05-25 09:33:21 39196

39196

需要注意的是PCIe Spec并沒有規(guī)定彈性緩存的具體位置,設(shè)計者可以將彈性緩存放在8b/10b解碼器之前,也可以把彈性緩存放在8b/10b解碼器之后。不過,Mindshare的建議是將彈性緩存放置于8b/10b解碼器之前的。

2018-09-08 09:59:41 7245

7245

Virtex?-6 FPGA內(nèi)置支持PCIExpress?Gen2兼容接口。

本視頻介紹了在ML605評估套件上運(yùn)行的用于PCI Express技術(shù)的Virtex-6 FPGA集成模塊的三個演示。

2018-11-22 06:30:00 3739

3739 本章介紹virtex-6 FPGA GTH收發(fā)器向?qū)В⑻峁┫嚓P(guān)信息,包括其他資源、技術(shù)支持和向xilinx提交反饋。向?qū)ё詣訄?zhí)行創(chuàng)建HDL包裝器的任務(wù),以配置virtex-6設(shè)備中的高速串行GTH收發(fā)器。

2019-02-20 09:35:45 4

4 很多人可能在想,8B/10B編碼主要作用的優(yōu)化直流平衡,從8bit中插2個bit進(jìn)去,這樣的話最終效果能夠使長0或者長1的位數(shù)不超過5位,達(dá)到很好的效果。那64B/66B編碼方式呢?在從64個bit

2021-04-01 12:01:38 9977

9977

下面詳細(xì)介紹了6個功能模塊及其應(yīng)用特點:并行接口、串行接口、時鐘分布電路、8B/10B編解碼電路、PRBS測試以及相關(guān)寄存器訪問控制接口MDIO。

2021-06-26 16:10:42 7686

7686

? 論序 8b/10b編碼/解碼是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的編解碼方式。在發(fā)送端,編碼電路將串行輸入的8比特一組的數(shù)據(jù)轉(zhuǎn)變成10比特一組

2021-09-26 09:56:22 10820

10820

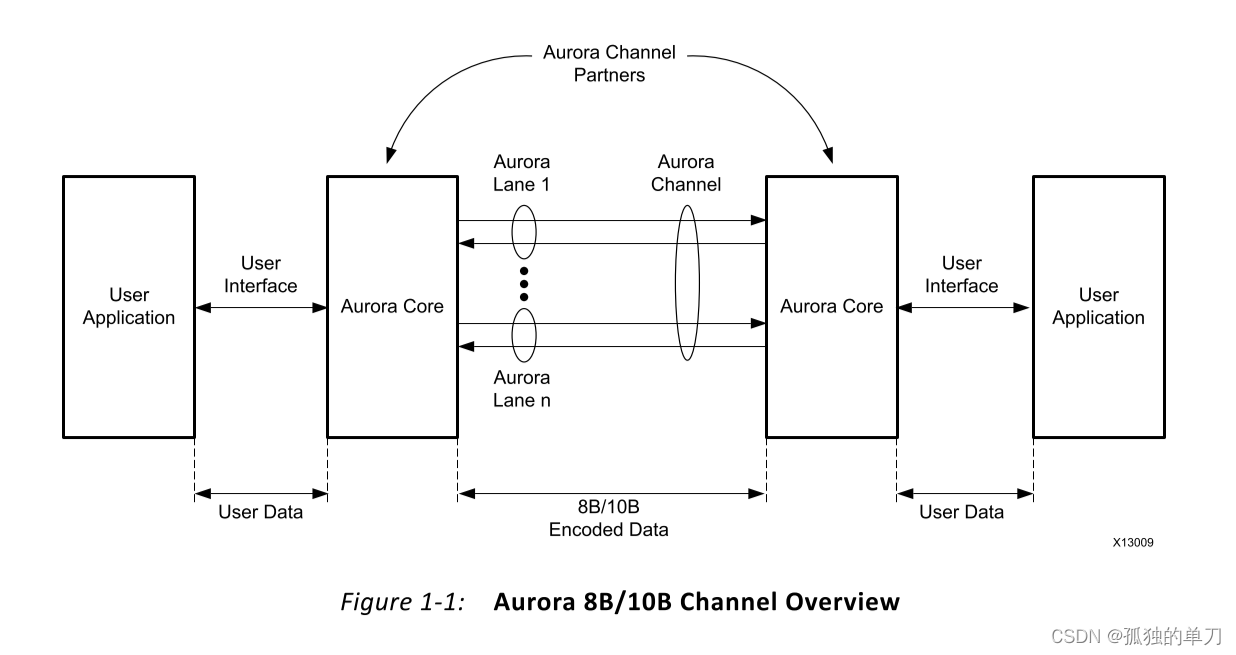

Aurora 協(xié)議是一個用于在點對點串行鏈路間移動數(shù)據(jù)的可擴(kuò)展輕量級鏈路層協(xié)議(由Xilinx開發(fā)提供)。這為物理層提供透明接口,讓專有協(xié)議或業(yè)界標(biāo)準(zhǔn)協(xié)議上層能方便地使用高速收發(fā)器

2022-02-16 16:21:24 11012

11012

首先咱們說說什么是CAN2.0b,它是CANBUS的一種協(xié)議類型,用人話說就是定義規(guī)則。它和can2.0A是目前應(yīng)用的最為普遍的協(xié)議,被稱作為是傳統(tǒng)CAN。其中CAN2.0A協(xié)議僅支持標(biāo)幀格式,而

2022-07-04 09:40:02 9385

9385 傳輸速率為每秒傳輸量GT/s,而不是每秒位數(shù)Gbps,因為傳輸量包括不提供額外吞吐量的開銷位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b編碼方案,導(dǎo)致占用了20% (= 2/10)的原始信道帶寬。

2022-08-02 09:45:34 2662

2662 8b/10b最常見的是應(yīng)用于光纖通訊和LVDS信號的。由于光模塊光模塊只能發(fā)送亮或者不亮,也就是0或者1這兩種狀態(tài)這種單極性碼,那么這會存在一個問題,如果傳輸中出現(xiàn)較長的連0或者連1(例如

2022-11-12 15:47:27 17676

17676 UART、I2C和SPI是嵌入式世界里最常見的三種通信協(xié)議。在閱讀教程,或者購買模塊時常常看見“這個模塊是用I2C協(xié)議驅(qū)動的”, “兩個設(shè)備之間數(shù)據(jù)走SPI”諸如此類的描述,很多新手覺得是什么高階的知識就一知半解得略過去略了。今天小編簡略地為大家介紹一下這三種協(xié)議,以及它們各自的優(yōu)缺點。

2023-02-13 10:30:58 6427

6427

UART、I2C和SPI是嵌入式世界里最常見的三種通信協(xié)議。在閱讀教程,或者購買模塊時常常看見“這個模塊是用I2C協(xié)議驅(qū)動的”, “兩個設(shè)備之間數(shù)據(jù)走SPI”諸如此類的描述,很多新手覺得是什么高階的知識就一知半解得略過去略了。今天小編簡略地為大家介紹一下這三種協(xié)議,以及它們各自的優(yōu)缺點。

2023-02-13 10:31:00 3620

3620

數(shù)據(jù)從遠(yuǎn)程設(shè)備(假設(shè)為DSP的SRIO端)傳輸過來,F(xiàn)PGA端(假設(shè)我們這端為FPGA的SRIO端口)通過RX接收到串行數(shù)據(jù),先到達(dá)物理層進(jìn)行時鐘恢復(fù),串并轉(zhuǎn)換,之后進(jìn)行8b/10b解碼操作、CRC校驗,這一系列的操作都在物理層完成,之后進(jìn)入傳輸層

2023-03-03 10:19:53 1638

1638 M32C/8B 組數(shù)據(jù)表

2023-04-20 18:56:32 0

0 M32C/8B群硬件手冊

2023-04-20 18:57:22 0

0 PCIe 標(biāo)準(zhǔn)之間的主要差異。 PCIe 3.0 PCIe2.0的傳輸速率為5 GT/s,但由于8b/10b編碼方案的開銷占比為20%,因此單lane的傳輸帶寬為4Gb/s。PCIe 3.0及以后

2023-07-26 08:05:01 2654

2654

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-09-04 18:19:18 2358

2358

本文開源一個FPGA高速串行通信項目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收發(fā)器,本工程主要是圍繞該IP核采用Vivado提供的例程創(chuàng)建。

2023-10-01 09:48:00 9986

9986

傳輸速率為每秒傳輸量GT/s,而不是每秒位數(shù)Gbps,因為傳輸量包括不提供額外吞吐量的開銷位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b編碼方案,導(dǎo)致占用了20% (= 2/10)的原始信道帶寬。

2024-01-16 14:42:02 3612

3612

SRIO(Serial RapidIO)交換芯片是一種高性能的通信芯片,專門設(shè)計用于實現(xiàn)基于SRIO協(xié)議的數(shù)據(jù)交換和傳輸。SRIO是一種點對點串行通信協(xié)議,廣泛應(yīng)用于嵌入式系統(tǒng)、高性能計算、網(wǎng)絡(luò)通信

2024-03-16 16:40:42 5525

5525 (通用串行總線) USB是一種廣泛使用的串行通信協(xié)議,用于連接計算機(jī)和各種外部設(shè)備,如鍵盤、鼠標(biāo)、打印機(jī)等。USB協(xié)議有多個版本,包括USB 1.1、USB 2.0、USB 3.0、USB 3.1和USB 4.0。每個版本都有不同的傳輸速率和特性。 USB 1.1的最大傳輸速率為12Mbps,而

2024-05-31 16:11:03 2641

2641 Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設(shè)計。本文深入分析了Aurora、PCI Express和Serial RapidIO這三種在Xilinx系統(tǒng)設(shè)計中關(guān)鍵的串行通信協(xié)議。介紹了它們的特性、優(yōu)勢和應(yīng)用場景,以及如何在不同需求下選擇合適的協(xié)議。

2025-11-14 15:02:11 2357

2357

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論