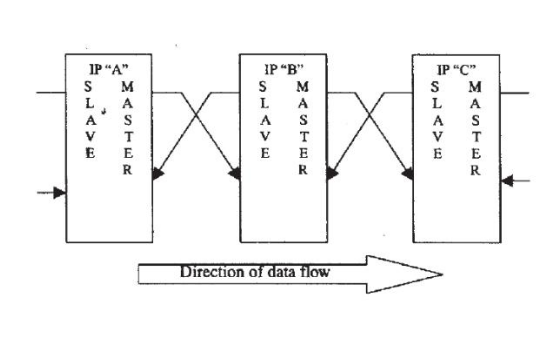

本文介紹了采用IXP425作為核心主控單元和3片DM642作為核心數據處理單元的會議電視多點控制單元的硬件設計原理和實現方法。主控制器IXP425模塊完成網絡發送/接收、數據調度、PCI控制等功能

2018-02-11 03:23:00 2082

2082

am5728是ti sitara系列高性能soc,得益于異構多核處理架構,cpu內集成了多核dsp、多核pru、iva-hd、gpu等協處理單元,通過硬件加速的方式極大增強cpu的數據、多媒體處理

2023-10-09 07:26:55

80C51單片機片內RAM低128個存儲單元劃分為哪4個主要部分?各部分主要功能是什么?

2011-10-08 16:10:02

目前,可重構計算平臺所支持的動態軟硬件劃分粒度多處于線程級或指令級,但線程級劃分開銷太大,而指令級劃分又過于復雜,因此很難被用于實際應用之中。本文設計并實現了一種支持過程級動態軟硬件劃分的可重構片上

2010-05-28 13:40:38

片內外設就是片上外設,同一種意思不同說法而已。片內外設和片外外設的區別:片內、外設是兩個概念,片內指做成芯片的集成電路內部,簡稱片內,片外同理顯而易見;外設是外部設備的簡稱,是指集成電路芯片外部

2021-07-23 06:34:56

**STM32H750_QSPI_W25QXX_XIP_仿真**最近在調試STM32H750片子,擔心片內flash不夠用,在QSPIbank2外掛了 W25Q40CL做XIP,當然也可以copy到

2021-08-18 07:06:11

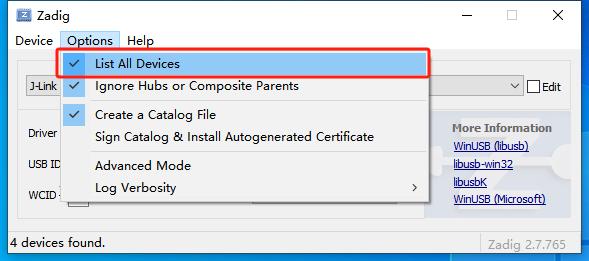

調試硬件配置實用程序使您能夠連接到在您的開發平臺和PC之間提供接口的調試硬件單元。

提供了以下實用程序:

RVI配置IP實用程序使用此實用程序在調試硬件單元上配置IP地址。

這使您能夠通過以太網訪問

2023-08-12 06:54:13

就可以了。這就是為什么大家經常看到說支持2個硬件斷點和數目不限的軟件斷點。但這里還是要提醒以下,如果2個斷點單元都用于硬件斷點,那用戶就不可以設置軟件斷點了。4 - 在FLASH內進行調試在FLASH

2011-12-02 19:35:01

塊還提供粗略的時間戳功能。該塊的主要用途是:支持 printf 風格調試跟蹤操作系統和應用程序事件發出診斷系統信息 HTM,AHB 跟蹤宏單元HTM 可顯示無法使用 ETM 從內核跟蹤推斷的總線信息

2014-10-13 09:26:54

的時間戳功能。該塊的主要用途是:支持 printf 風格調試跟蹤操作系統和應用程序事件發出診斷系統信息 HTM,AHB 跟蹤宏單元HTM 可顯示無法使用 ETM 從內核跟蹤推斷的總線信息:了解多層總線

2018-05-11 13:53:21

ATM交換軟件的核心部分----信令軟件包括用戶到網絡信令和網絡到網絡信令(即UNI/NNI信令)都將放在中心控制單元的硬件上運行。本文主要探討中心控制單元的硬件設計與實現。中心控制單元為網管代理提供

2009-05-25 16:38:13

,程序停止運行,調試器可通過 DAP 對 M0 的內核狀態和片內的外設狀態及存儲單元進行查詢;且內核和外設可以被復原,程序繼續執行。當使用調試仿真工具通過 SWD 接口連接到 CW32F030,進入調試模式,通過芯片內核中的 DAP 硬件調試模塊進行調試操作。

2025-12-15 06:18:36

Flash上的應用,是不支持片內FLASH?不支持的話我想非阻塞的接收socket數據就不能用select了?那我應該用什么方式呢?多謝各位了。。。

2023-05-11 11:16:12

1 功能概述該工程實例內部系統功能框圖如圖所示。我們通過IP核例化一個FIFO,定時寫入數據,然后再讀出所有數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內FIFO

2019-04-08 09:34:42

FPGA硬件系統的調試方法在調試FPGA電路時要遵循一定的原則和技巧,才能減少調試時間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進行FPGA硬件系統的調試。(1)首先在焊接硬件電路時,只焊接

2012-08-12 11:52:54

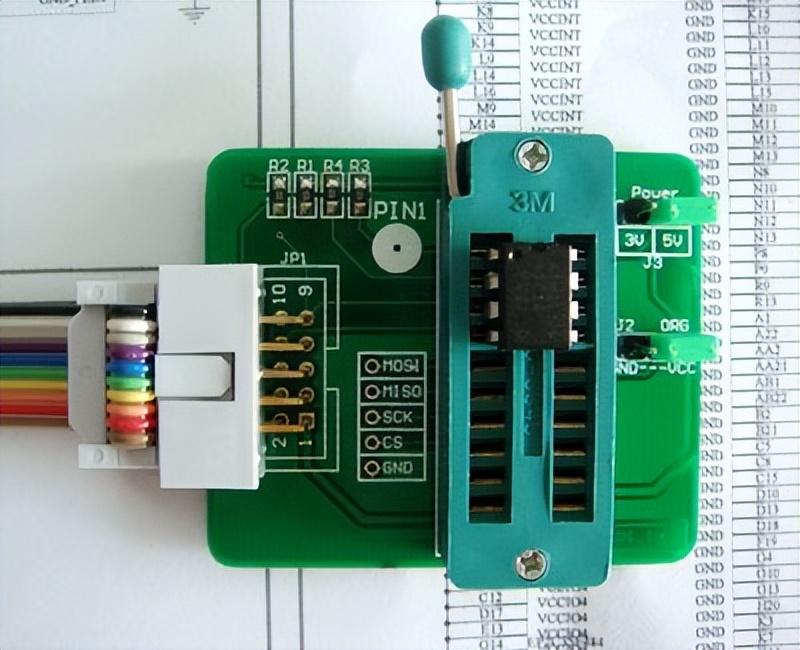

大家了解GD32VF103片內CRC單元的應用方法。

系統環境

Windows 10-64bit

軟件平臺

NucleiStudio IDE 202102版或 PlatformIO IDE

硬件需求

2023-08-16 07:13:14

想要問問,HarmonyOS智能硬件是怎么實現總線驅動開發的?

2020-09-18 10:37:53

請教Arm專家大俠: SOC內SRAM各存儲單元, 其“每次上電冷啟動后、還未寫入應用數據前的初始狀態數據”是否是由其硬件電路保證總是一樣的(全0或全1)?不會隨機變化(有時為0有時為1)? 能否從硬件原理角度簡單說明下? 謝謝。

2022-08-19 15:37:40

怎樣去操作STM32的片內FLASH呢?STM32片內FLASH的主存儲塊有哪些功能?

2021-11-02 08:14:48

STM32的片內FLASH可分為哪幾類?如何去使用STM32的片內FLASH呢?

2021-11-01 06:36:28

STM32的片內FLASH有何功能?怎樣進行FLASH的擦除編程工作呢?

2021-11-02 08:04:17

怎么去操作STM32的FLSAH呢?STM32的片內FLASH有何功能?

2021-11-01 06:35:06

STM32的片內FLASH可分成哪幾部分?STM32的FLASH共有幾個鍵值呢?

2021-11-02 07:08:52

你好!我想對我的軟件進行單元測試,TouchGFX 對此有任何支持嗎?

2022-12-01 06:37:16

的在線邏輯分析儀chipscope,我們可以觀察FPGA片內ROM、FIFO和RAM的讀寫時序,也可以只比較ROM預存儲的數據和RAM最后讀出的數據,確認整個讀寫緩存過程中,數據的一致性是否實現。 2

2016-03-16 12:43:36

請問proteus 是否支持模擬片內AD轉換?找了一些帶有內置8路10位ADC轉換的芯片,正要試試AD功能,突然想到,PROTEUS貌似只能仿真芯片的內核比如8051、8052等等,對于芯片內置

2013-04-20 15:22:09

XADC的片內溫度/電壓數據讀取出來,同樣使用IIC總線傳輸數據到LCD上,完成芯片溫度的采集。 實現過程:1.根據引腳分配連接開發板和LCD1602。2.生成比特流下載到開發板中,LCD即可顯示。開關

2021-07-30 15:37:27

STM32的片內FLASH可分為哪幾類?STM32的片內FLASH有何功能?

2021-11-03 07:57:23

嵌入式跟蹤宏單元所記錄的跑飛前后一段時間內MCU執行的所有指令,在查找此類復雜問題的原因時非常有幫助。ETM嵌入式跟蹤宏單元ETM Trace調試功能的實現依賴于芯片上的ETM嵌入式跟蹤宏單元,ETM

2021-03-05 14:49:09

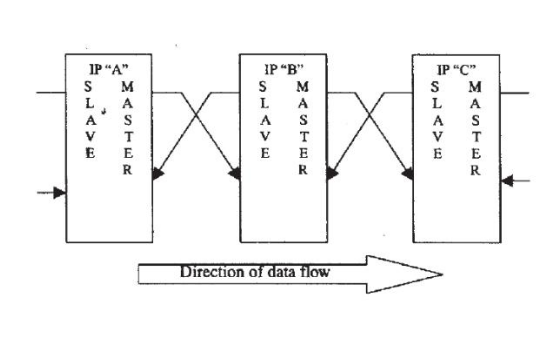

1 CHI的片上互聯總線片上互聯是將SoC內部不同模塊連接起來的結構,如前文提到過的硬件系統結構中, Interconnect Bus就是片上互聯。需要支持模塊之間的高速數據傳輸,高效地互聯互通

2022-06-29 16:28:32

的硬件投資成本和使用成本。 本文介紹一種AMC系列多回路智能監控單元(見圖1)的設計方法,最多實現3個三相回路(或9個單相回路)的電參量測量;結合RS485總線技術及上位機軟件,可實現數據及狀態信息遠傳

2011-12-16 20:50:43

的二線制總線。它通過SDA(串行數據線)及SCL(串行同步時鐘線)兩根線在連到總線上的器件之間傳送信息,通過軟件尋址實現片選,減少了器件片選線的連接。CPU不僅能通過指令將某個功能單元電路掛靠或摘離總線

2018-12-03 15:17:53

專門用于DSP與其他總線或CPU進行通信。主機是通過HPI控制寄存器(HPIC),地址寄存器(HPIA),數據寄存器(HPID)訪問DSP的片內RAM,從而實現與DSP通信的。DSP只能訪問HPIC

2018-12-17 11:29:06

摘要:介紹了采用IXP425作為核心主控單元和3片DM642作為核心數據處理單元的會議電視多點控制單元的硬件設計原理和實現方法。主控制器IXP425模塊完成網絡發送/接收、數據調度、PCI控制等功能

2019-06-28 08:05:49

值相比較,確定訪問是否落在本設備的地址空間范圍內;或確定是否被選作配置訪問的目標設備。同時對地址期C/BE信號線的值進行命令譯碼,確定總線訪問的類型,本模塊支持配置讀、寫和內存讀、寫4種PCI總線訪問

2019-05-29 05:00:02

各位專家好:

??????? 關于多片C6678的同步調試問題想咨詢下:

?????? 我打算做兩個板子,每個板子上集成兩片C6678的芯片,板間通信打算用光傳輸,現在想咨詢的問題是在用CCS進行調試的時候,這個能不能實現同步調試,比如在某個時間一起停下來,去看看各自寄存器或者變量的值。謝謝。

2018-06-21 02:37:42

方案說是以后可能要用到調試多片DSP,我想知道如何調試多片DSP? ?

2019-07-05 04:55:36

對于SH1,SH2等內建FLASH的單片機,由于內建了高速FLASH存儲器,我們可以使用E10A等仿真器直接在FLASH ROM里設置硬件斷點,可以很方便的進行調試。 但是對于SH2A,SH3

2014-12-29 15:25:14

的斷點數量限制為CPU調試單元支持的硬件斷點數。J-Link的“無限Flash斷點”適用于片內和外擴的Flash,包括通過內存映射添加的QSPI閃存。無限Flash斷點的實現方式Segger J-Link

2022-05-12 10:49:43

如何去完成MCU片內Flash(閃存)的擦除與讀寫任務呢?怎樣在調試助手上查看其結果?

2021-11-25 08:30:43

基本正常,我覺得SPI接口以及外圍硬件不會有問題,問題應該在時序上。但是9957手冊對RAM數據讀寫所言甚少,ADI網站上的能找到的參考代碼頁都沒有涉及RAM讀寫的部分。不知哪位專家能夠指點一下,到底如何正確配置9957片內RAM?

謝謝!

2023-12-13 06:51:40

我采用的是新華龍的c8051f413,現在想要讀取片內溫度傳感器的溫度,現在已經把ad都配置好了,然后我配置了片內溫度傳感器的通道和使能片內溫度傳感器,這樣就可以了嗎?

2019-08-09 04:35:10

STM32的片內FLASH分成哪幾部分呢?怎樣去操作STM32的片內FLASH呢?

2021-11-01 07:39:22

`想要實現當鼠標點中表格控件的某一個單元格時,將單元格內的值輸出來。等待大神的幫助……`

2015-12-17 11:25:02

我看好多芯片都支持AES硬件運算單元,感覺用起來的卻沒有幾個,不知道芯源這方面是不是和其他芯片的AES硬件一樣呢?我也想知道,這種硬件單元一般用在哪個場合比較多呢

2025-12-03 06:27:21

通用bootloader不選“支持spi flash”,download放于片內flash,正常啟動,ota正常,app驅動at45db161讀寫正常。通用bootloader選“支持spi

2024-03-22 07:45:56

等原因導致以FPGA實現比較困難。本文所述通過CH365芯片可以快速實現PCI接口電路的設計,支持ISA總線接口向PCI總線接口的升級,并且由CH365芯片的本地硬件地址功能可以實現原系統軟件無需修改

2019-04-29 07:00:09

潤和Hi3861V100芯片迷你無線仿真USB Open OCD調試板多功能調試器

2023-03-28 13:07:10

彩電總線調試數據大全

1.進入總線方法:在正常開機后,按遙控器上的“PSTD”、“SSTD”、“CALL”、“POWER”組合鍵進入維修菜單,此時,圖象模式變為“標準”、視頻

2008-10-08 18:09:03 65

65 在總線的主設備上增設了實時操作系統的任務優先級分配機制,基于蒙特卡羅選擇實現總線仲裁器的仲裁策略,建立不同類型的從設備存儲器模型。運用SystemC在交易級實現整個總線

2009-04-11 08:54:10 7

7 膠印機印刷單元的調試原理:3.7 印刷單元的調試原理

1.壓印滾筒是印刷單元的基準

印刷單元各部分組件的作用及調節已分別講敘過,那么把它們放在一起應該

2009-09-21 17:02:36 15

15 論文簡要介紹了智能家庭網絡,詳細描述了一種基于歐洲設備安裝總線(EIB)的智能家庭網絡系統總線耦合單元的設計與實現,詳細介紹了其通信協議棧的原理和實現機制,并進

2009-12-22 11:00:15 23

23 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 本文介紹一種基于PCI Express 總線的高速數據采集卡的設計方案及功能實現。給出系統的基本結構及單元組成,重點闡述系統硬件設計的關鍵技術和本地總線的控制邏輯,詳細探

2010-09-22 08:15:04 62

62 摘 要:提出了一種采用片內PLL實現實速掃描測試的方案。在該方案中,移入測試向量時使用測試儀提供的時鐘,激勵施加和響應捕獲采用片內PLL生成的高速時鐘,從而降低了實速掃

2010-10-11 11:19:02 33

33 摘要:基于IP可重用的設計方法,利用WISHBONE總線協議,把兩個已成功開發出的具有自主知識產權的THUMP內核在一個芯片上,實現了片上多處理器FPGA。開發重點是實

2009-06-20 15:29:35 839

839

產品概述VPX361是一款基于3U VPX總線架構的8路射頻收發子模塊,板卡采用1片XCZU47DR RFSOC來實現8路射頻信號的高速采集、信號生成以及處理,并進行智能目標

2025-11-03 16:35:26

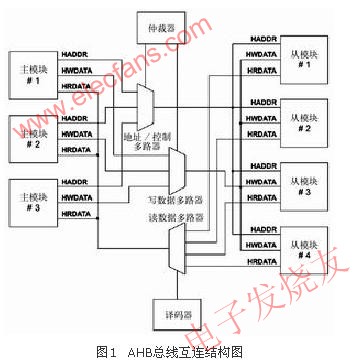

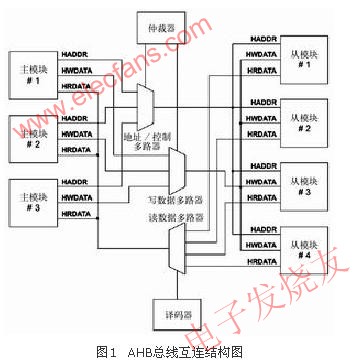

AMBA片上總線

AMBA 2.0規范包括四個部分:AHB、ASB、APB和Test Methodology。AHB的相互連接采用了傳統的帶有主模塊和從模塊的共享總線

,接口與互連功能分離,

2010-09-01 10:59:10 2347

2347

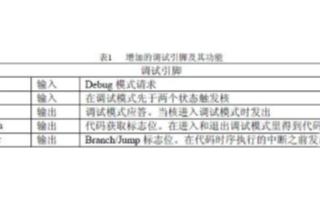

以 龍芯1號 處理器為研究對象,探討了嵌入式處理器中在片調試功能的設計實現方法。大大方便了軟件開發與系統調試

2011-06-29 17:45:26 48

48 本內容提供了2812片內ADC采樣時間計算。1)序列采樣模式(SMODE = 0)[attach]12497[/attach]

2011-09-05 11:39:36 3830

3830 設計開發了嵌入式實時操作系統VxWorks 的一種基于PC104 總線的板載支持包, 完成了相關的外圍驅動程序設計和調試工作。

2011-09-07 16:09:04 54

54 介紹了基于硬件描述語言Verilog HDL設計的SDX總線與Wishbone總線接口轉化的設計與實現,并通過Modelsim進行功能仿真,在QuartusⅡ軟件平臺上綜合,最終在Altera公司的CycloneⅢ系列FPGA上調試。實驗

2012-01-11 10:21:21 25

25 基于總線的多DSP的交叉調試器的設計與實現

2016-05-19 13:41:19 9

9 TI C6000系列的DSP的內部總線架構、存儲系統和各種外設(如EDMA3和PRU等),特別是片內的程序數據RAM和Cache系統,以及外設的EDMA控制器,Video port,McBSP,McASP以及SRIO接口等。

2016-12-29 14:10:10 8109

8109

本文檔內容介紹了調試數字硬件設計的步驟,以及框架原理圖,供網友參考。

2017-09-15 18:54:54 4

4 總線的多DSP交叉調試器的設計與實現

2017-10-19 10:50:18 2

2 瑞士硬件工具制造商Abatron宣布它的Linux硬件調試工具現在支持Cavium的Octeon和Octeon Plus處理器。這家公司宣稱:Abatron的BDI2000 和 BDI3000 調試

2017-10-20 09:58:58 1

1 本文以workbench 為平臺,vxworks 為操作系統,chipscope 為分析工具,介紹了完整的ARINC429 協議和422協議的FPGA 硬件調試,通過硬件調試發現modelsim

2017-11-18 08:56:01 23632

23632

片上系統的出現使得芯片可以實現更加復雜的功能,獲取更高的性能,但同時其內部信號也變得越來越難以觀察和控制,相應的測試和調試工作也遇到了難以克服的時間復雜性困難。國際半導體技術路線圖

2017-12-01 02:01:34 564

564

性能的優劣。面對日趨多樣的ECU和通信總線類型,開發一種支持多總線的、通用靈活的標定系統,具有非常高的實用價值[1]。目前,CAN總線作為一種可靠的汽車總線已經廣泛應用于高檔汽車,因而多數標定系統都是

2018-06-20 14:29:00 11554

11554

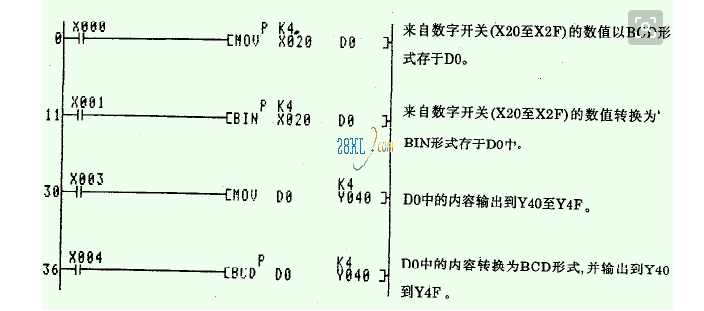

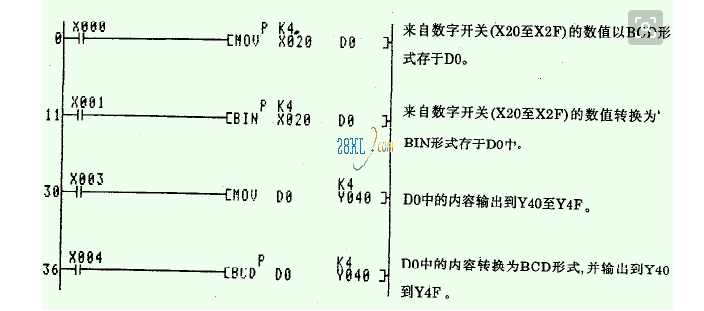

把二進制數轉換成 BCD 碼,是很常見的,做而論道以前也發表過這樣的程序。 但是,過去都是用寄存器,如果要求用片內RAM單元,就少見了。 當然,也可以把片內RAM單元的數據,先傳送到寄存器,再利用

2018-05-19 01:18:00 4301

4301

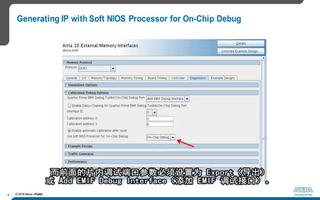

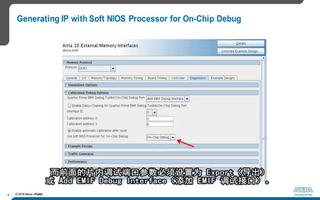

使用片內調試 Nios 軟核處理器

2018-06-20 05:53:00 3888

3888

AVR單片機片內TWI總線的原理和使用

2018-07-11 00:27:00 3735

3735

IP復用是片上系統時代的核心技術之一。由于IP核的設計千差萬別,它們要能夠直接連接,就要遵守相同的接口標準。在片上系統中,處理器核和所有外設通過共享總線互通互聯,因此這些IP核必須遵守相同的總線

2018-07-04 09:02:32 5769

5769

隨著芯片規模的增大和復雜度的上升,片內信號的觀測和控制更加困難,對芯片的測試及調試的難度也在不斷上升,芯片的測試和調試問題成為制約整個行業發展的重要因素。如何合理地對數字信號處理器進行可測性設計、建立調試支持成為數字信號處理器設計的核心問題之一。

2019-03-22 17:04:08 2

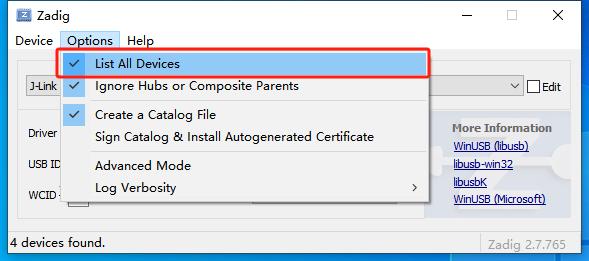

2 用CCES調試硬件目標

2019-08-19 06:07:00 4079

4079 多個ADM1260器件可以相連,將電壓時序控制器解決方案從10 V供電軌擴展至40 V。這可以通過使用一個片內總線和ADI Power Studio工具實現,該工具可將多個器件虛擬化為單一器件。

2019-06-17 06:21:00 2223

2223 片內總線負責連接CPU芯片內部的各個模塊,包括CPU核心以及顯示核心、內存控制器等輔助模塊。

2020-07-21 17:22:37 4267

4267 為了能讓嵌入式微處理器的片上調試功能也能夠像高級語言編程工具那樣支持斷點設置、單步執行、寄存器內容的查看和內存內容查看等功能,文章提出了一種在線調試模塊設計,此設計為嵌入式微處理器增加了一些專用

2021-03-23 14:55:48 3282

3282

面向硬件實現的HEVC幀內編碼快速算法

2021-06-21 16:30:15 10

10 單片機系統硬件的靜態調試和動態調試綜述

2021-07-18 10:59:14 3

3 和事件跟蹤、指令跟蹤等。 有很多網友反應,Keil MDK在調試的時候,會遇到各種問題,下面就簡單講述一下Keil MDK調試時,軟件和硬件的一些要求。 1.邏輯分析儀它要求目標硬件支持 SWO 或

2021-11-16 09:15:53 3717

3717 地址為 40H、88H 的位,該位所在字節的字節地址分別為__ 和__ 。答:28H,88H4. 片內字節地址為 2AH 單元最低位的位地址是__ ;片內字節地址為 A8H 單元的最低位的 位地址為__ 。答:50H,A8H5. 若 A 中的內容為 63H,那么,P 標志位的值為__ 。答:0

2021-11-23 17:06:43 7

7 1. 引言SPI : serial perripheral interface 串行外圍設備接口SPI總線是硬件上用的比較多的一種串行總線,高速傳輸,無應答無校驗。這里簡單記錄一下SPI總線的一些

2021-12-22 19:18:59 8

8 J-Link支持一項名為“無限Flash斷點”(Unlimited Flash Breakpoints)的調試功能。“無限Flash斷點”允許用戶在Flash中調試時設置無限數量的斷點。如果沒有此功能,在Flash中能夠設置的斷點數量限制為CPU調試單元支持的硬件斷點數。

2022-05-07 09:54:43 2853

2853 在硬件方案設計中,需滿足測試工具的外設需求,常用外設包含觸摸式顯示屏、TF存儲卡、EtherCAT總線從站、MetroLink-Ⅲ總線從站、鍵盤等,調試用外設包含串口調試工具、OTG調試工具、鼠標等。

硬件整體設計框架如圖1所示。

2022-11-02 14:52:10 1649

1649 所有J-Link型號(J-Link PRO、J-Link ULTRA+、J-Link PLUS和J-Link BASE)最新硬件版本現在都支持通過JTAG和SWD接口高速下載和調試。

2023-04-14 14:20:26 2965

2965 片內和片間非均勻性是什么?有什么作用呢? 片內和片間非均勻性是指光學元件(如透鏡)表面上的厚度/形狀/折射率等參數的變化,以及元件之間的相對位置誤差所引起的光學性能差異。這種非均勻性在光學系統中

2023-12-19 11:48:19 1512

1512 電子發燒友網站提供《實現多軸電機驅動系統內的多片C2000 PWM同步.pdf》資料免費下載

2024-09-03 09:25:17 2

2 新的硬件支持包不僅無需耗時的手寫代碼優化和驗證,還支持處理器在環測試 MathWorks 今天宣布,推出針對 Qualcomm? Hexagon? 神經處理單元(NPU)的硬件支持包。該處理單元嵌入

2024-09-23 11:59:05 905

905 硬件調試是硬件系統設計、開發和制造過程中不可或缺的一環,旨在對可能出現的問題進行分析和解決。以下是進行硬件調試的一般步驟和方法: 一、準備階段 熟悉設計文檔:在開始調試之前,需要詳細閱讀和理解硬件

2024-11-10 10:17:40 2894

2894

摘要: 本文深入探討了 JLink 調試器在嵌入式系統硬件調試中的應用,詳細闡述了 JLink 驅動配置的方法以及硬件調試技巧。本文以國科安芯的AS32系列MCU芯片為例,通過分析 JLink

2025-06-12 23:20:26 1405

1405

電子發燒友App

電子發燒友App

評論