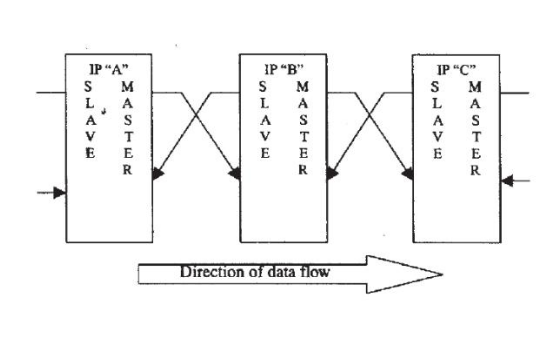

本文介紹了采用IXP425作為核心主控單元和3片DM642作為核心數(shù)據(jù)處理單元的會議電視多點(diǎn)控制單元的硬件設(shè)計(jì)原理和實(shí)現(xiàn)方法。主控制器IXP425模塊完成網(wǎng)絡(luò)發(fā)送/接收、數(shù)據(jù)調(diào)度、PCI控制等功能

2018-02-11 03:23:00 2082

2082

am5728是ti sitara系列高性能soc,得益于異構(gòu)多核處理架構(gòu),cpu內(nèi)集成了多核dsp、多核pru、iva-hd、gpu等協(xié)處理單元,通過硬件加速的方式極大增強(qiáng)cpu的數(shù)據(jù)、多媒體處理

2023-10-09 07:26:55

80C51單片機(jī)片內(nèi)RAM低128個(gè)存儲單元劃分為哪4個(gè)主要部分?各部分主要功能是什么?

2011-10-08 16:10:02

目前,可重構(gòu)計(jì)算平臺所支持的動態(tài)軟硬件劃分粒度多處于線程級或指令級,但線程級劃分開銷太大,而指令級劃分又過于復(fù)雜,因此很難被用于實(shí)際應(yīng)用之中。本文設(shè)計(jì)并實(shí)現(xiàn)了一種支持過程級動態(tài)軟硬件劃分的可重構(gòu)片上

2010-05-28 13:40:38

片內(nèi)外設(shè)就是片上外設(shè),同一種意思不同說法而已。片內(nèi)外設(shè)和片外外設(shè)的區(qū)別:片內(nèi)、外設(shè)是兩個(gè)概念,片內(nèi)指做成芯片的集成電路內(nèi)部,簡稱片內(nèi),片外同理顯而易見;外設(shè)是外部設(shè)備的簡稱,是指集成電路芯片外部

2021-07-23 06:34:56

**STM32H750_QSPI_W25QXX_XIP_仿真**最近在調(diào)試STM32H750片子,擔(dān)心片內(nèi)flash不夠用,在QSPIbank2外掛了 W25Q40CL做XIP,當(dāng)然也可以copy到

2021-08-18 07:06:11

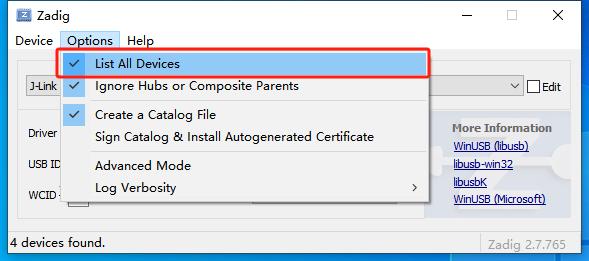

調(diào)試硬件配置實(shí)用程序使您能夠連接到在您的開發(fā)平臺和PC之間提供接口的調(diào)試硬件單元。

提供了以下實(shí)用程序:

RVI配置IP實(shí)用程序使用此實(shí)用程序在調(diào)試硬件單元上配置IP地址。

這使您能夠通過以太網(wǎng)訪問

2023-08-12 06:54:13

就可以了。這就是為什么大家經(jīng)常看到說支持2個(gè)硬件斷點(diǎn)和數(shù)目不限的軟件斷點(diǎn)。但這里還是要提醒以下,如果2個(gè)斷點(diǎn)單元都用于硬件斷點(diǎn),那用戶就不可以設(shè)置軟件斷點(diǎn)了。4 - 在FLASH內(nèi)進(jìn)行調(diào)試在FLASH

2011-12-02 19:35:01

塊還提供粗略的時(shí)間戳功能。該塊的主要用途是:支持 printf 風(fēng)格調(diào)試跟蹤操作系統(tǒng)和應(yīng)用程序事件發(fā)出診斷系統(tǒng)信息 HTM,AHB 跟蹤宏單元HTM 可顯示無法使用 ETM 從內(nèi)核跟蹤推斷的總線信息

2014-10-13 09:26:54

的時(shí)間戳功能。該塊的主要用途是:支持 printf 風(fēng)格調(diào)試跟蹤操作系統(tǒng)和應(yīng)用程序事件發(fā)出診斷系統(tǒng)信息 HTM,AHB 跟蹤宏單元HTM 可顯示無法使用 ETM 從內(nèi)核跟蹤推斷的總線信息:了解多層總線

2018-05-11 13:53:21

ATM交換軟件的核心部分----信令軟件包括用戶到網(wǎng)絡(luò)信令和網(wǎng)絡(luò)到網(wǎng)絡(luò)信令(即UNI/NNI信令)都將放在中心控制單元的硬件上運(yùn)行。本文主要探討中心控制單元的硬件設(shè)計(jì)與實(shí)現(xiàn)。中心控制單元為網(wǎng)管代理提供

2009-05-25 16:38:13

,程序停止運(yùn)行,調(diào)試器可通過 DAP 對 M0 的內(nèi)核狀態(tài)和片內(nèi)的外設(shè)狀態(tài)及存儲單元進(jìn)行查詢;且內(nèi)核和外設(shè)可以被復(fù)原,程序繼續(xù)執(zhí)行。當(dāng)使用調(diào)試仿真工具通過 SWD 接口連接到 CW32F030,進(jìn)入調(diào)試模式,通過芯片內(nèi)核中的 DAP 硬件調(diào)試模塊進(jìn)行調(diào)試操作。

2025-12-15 06:18:36

Flash上的應(yīng)用,是不支持片內(nèi)FLASH?不支持的話我想非阻塞的接收socket數(shù)據(jù)就不能用select了?那我應(yīng)該用什么方式呢?多謝各位了。。。

2023-05-11 11:16:12

1 功能概述該工程實(shí)例內(nèi)部系統(tǒng)功能框圖如圖所示。我們通過IP核例化一個(gè)FIFO,定時(shí)寫入數(shù)據(jù),然后再讀出所有數(shù)據(jù)。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內(nèi)FIFO

2019-04-08 09:34:42

FPGA硬件系統(tǒng)的調(diào)試方法在調(diào)試FPGA電路時(shí)要遵循一定的原則和技巧,才能減少調(diào)試時(shí)間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進(jìn)行FPGA硬件系統(tǒng)的調(diào)試。(1)首先在焊接硬件電路時(shí),只焊接

2012-08-12 11:52:54

大家了解GD32VF103片內(nèi)CRC單元的應(yīng)用方法。

系統(tǒng)環(huán)境

Windows 10-64bit

軟件平臺

NucleiStudio IDE 202102版或 PlatformIO IDE

硬件需求

2023-08-16 07:13:14

想要問問,HarmonyOS智能硬件是怎么實(shí)現(xiàn)總線驅(qū)動開發(fā)的?

2020-09-18 10:37:53

請教Arm專家大俠: SOC內(nèi)SRAM各存儲單元, 其“每次上電冷啟動后、還未寫入應(yīng)用數(shù)據(jù)前的初始狀態(tài)數(shù)據(jù)”是否是由其硬件電路保證總是一樣的(全0或全1)?不會隨機(jī)變化(有時(shí)為0有時(shí)為1)? 能否從硬件原理角度簡單說明下? 謝謝。

2022-08-19 15:37:40

怎樣去操作STM32的片內(nèi)FLASH呢?STM32片內(nèi)FLASH的主存儲塊有哪些功能?

2021-11-02 08:14:48

STM32的片內(nèi)FLASH可分為哪幾類?如何去使用STM32的片內(nèi)FLASH呢?

2021-11-01 06:36:28

STM32的片內(nèi)FLASH有何功能?怎樣進(jìn)行FLASH的擦除編程工作呢?

2021-11-02 08:04:17

怎么去操作STM32的FLSAH呢?STM32的片內(nèi)FLASH有何功能?

2021-11-01 06:35:06

STM32的片內(nèi)FLASH可分成哪幾部分?STM32的FLASH共有幾個(gè)鍵值呢?

2021-11-02 07:08:52

你好!我想對我的軟件進(jìn)行單元測試,TouchGFX 對此有任何支持嗎?

2022-12-01 06:37:16

的在線邏輯分析儀chipscope,我們可以觀察FPGA片內(nèi)ROM、FIFO和RAM的讀寫時(shí)序,也可以只比較ROM預(yù)存儲的數(shù)據(jù)和RAM最后讀出的數(shù)據(jù),確認(rèn)整個(gè)讀寫緩存過程中,數(shù)據(jù)的一致性是否實(shí)現(xiàn)。 2

2016-03-16 12:43:36

請問proteus 是否支持模擬片內(nèi)AD轉(zhuǎn)換?找了一些帶有內(nèi)置8路10位ADC轉(zhuǎn)換的芯片,正要試試AD功能,突然想到,PROTEUS貌似只能仿真芯片的內(nèi)核比如8051、8052等等,對于芯片內(nèi)置

2013-04-20 15:22:09

XADC的片內(nèi)溫度/電壓數(shù)據(jù)讀取出來,同樣使用IIC總線傳輸數(shù)據(jù)到LCD上,完成芯片溫度的采集。 實(shí)現(xiàn)過程:1.根據(jù)引腳分配連接開發(fā)板和LCD1602。2.生成比特流下載到開發(fā)板中,LCD即可顯示。開關(guān)

2021-07-30 15:37:27

STM32的片內(nèi)FLASH可分為哪幾類?STM32的片內(nèi)FLASH有何功能?

2021-11-03 07:57:23

嵌入式跟蹤宏單元所記錄的跑飛前后一段時(shí)間內(nèi)MCU執(zhí)行的所有指令,在查找此類復(fù)雜問題的原因時(shí)非常有幫助。ETM嵌入式跟蹤宏單元ETM Trace調(diào)試功能的實(shí)現(xiàn)依賴于芯片上的ETM嵌入式跟蹤宏單元,ETM

2021-03-05 14:49:09

1 CHI的片上互聯(lián)總線片上互聯(lián)是將SoC內(nèi)部不同模塊連接起來的結(jié)構(gòu),如前文提到過的硬件系統(tǒng)結(jié)構(gòu)中, Interconnect Bus就是片上互聯(lián)。需要支持模塊之間的高速數(shù)據(jù)傳輸,高效地互聯(lián)互通

2022-06-29 16:28:32

的硬件投資成本和使用成本。 本文介紹一種AMC系列多回路智能監(jiān)控單元(見圖1)的設(shè)計(jì)方法,最多實(shí)現(xiàn)3個(gè)三相回路(或9個(gè)單相回路)的電參量測量;結(jié)合RS485總線技術(shù)及上位機(jī)軟件,可實(shí)現(xiàn)數(shù)據(jù)及狀態(tài)信息遠(yuǎn)傳

2011-12-16 20:50:43

的二線制總線。它通過SDA(串行數(shù)據(jù)線)及SCL(串行同步時(shí)鐘線)兩根線在連到總線上的器件之間傳送信息,通過軟件尋址實(shí)現(xiàn)片選,減少了器件片選線的連接。CPU不僅能通過指令將某個(gè)功能單元電路掛靠或摘離總線

2018-12-03 15:17:53

專門用于DSP與其他總線或CPU進(jìn)行通信。主機(jī)是通過HPI控制寄存器(HPIC),地址寄存器(HPIA),數(shù)據(jù)寄存器(HPID)訪問DSP的片內(nèi)RAM,從而實(shí)現(xiàn)與DSP通信的。DSP只能訪問HPIC

2018-12-17 11:29:06

摘要:介紹了采用IXP425作為核心主控單元和3片DM642作為核心數(shù)據(jù)處理單元的會議電視多點(diǎn)控制單元的硬件設(shè)計(jì)原理和實(shí)現(xiàn)方法。主控制器IXP425模塊完成網(wǎng)絡(luò)發(fā)送/接收、數(shù)據(jù)調(diào)度、PCI控制等功能

2019-06-28 08:05:49

值相比較,確定訪問是否落在本設(shè)備的地址空間范圍內(nèi);或確定是否被選作配置訪問的目標(biāo)設(shè)備。同時(shí)對地址期C/BE信號線的值進(jìn)行命令譯碼,確定總線訪問的類型,本模塊支持配置讀、寫和內(nèi)存讀、寫4種PCI總線訪問

2019-05-29 05:00:02

各位專家好:

??????? 關(guān)于多片C6678的同步調(diào)試問題想咨詢下:

?????? 我打算做兩個(gè)板子,每個(gè)板子上集成兩片C6678的芯片,板間通信打算用光傳輸,現(xiàn)在想咨詢的問題是在用CCS進(jìn)行調(diào)試的時(shí)候,這個(gè)能不能實(shí)現(xiàn)同步調(diào)試,比如在某個(gè)時(shí)間一起停下來,去看看各自寄存器或者變量的值。謝謝。

2018-06-21 02:37:42

方案說是以后可能要用到調(diào)試多片DSP,我想知道如何調(diào)試多片DSP? ?

2019-07-05 04:55:36

對于SH1,SH2等內(nèi)建FLASH的單片機(jī),由于內(nèi)建了高速FLASH存儲器,我們可以使用E10A等仿真器直接在FLASH ROM里設(shè)置硬件斷點(diǎn),可以很方便的進(jìn)行調(diào)試。 但是對于SH2A,SH3

2014-12-29 15:25:14

的斷點(diǎn)數(shù)量限制為CPU調(diào)試單元支持的硬件斷點(diǎn)數(shù)。J-Link的“無限Flash斷點(diǎn)”適用于片內(nèi)和外擴(kuò)的Flash,包括通過內(nèi)存映射添加的QSPI閃存。無限Flash斷點(diǎn)的實(shí)現(xiàn)方式Segger J-Link

2022-05-12 10:49:43

如何去完成MCU片內(nèi)Flash(閃存)的擦除與讀寫任務(wù)呢?怎樣在調(diào)試助手上查看其結(jié)果?

2021-11-25 08:30:43

基本正常,我覺得SPI接口以及外圍硬件不會有問題,問題應(yīng)該在時(shí)序上。但是9957手冊對RAM數(shù)據(jù)讀寫所言甚少,ADI網(wǎng)站上的能找到的參考代碼頁都沒有涉及RAM讀寫的部分。不知哪位專家能夠指點(diǎn)一下,到底如何正確配置9957片內(nèi)RAM?

謝謝!

2023-12-13 06:51:40

我采用的是新華龍的c8051f413,現(xiàn)在想要讀取片內(nèi)溫度傳感器的溫度,現(xiàn)在已經(jīng)把a(bǔ)d都配置好了,然后我配置了片內(nèi)溫度傳感器的通道和使能片內(nèi)溫度傳感器,這樣就可以了嗎?

2019-08-09 04:35:10

STM32的片內(nèi)FLASH分成哪幾部分呢?怎樣去操作STM32的片內(nèi)FLASH呢?

2021-11-01 07:39:22

`想要實(shí)現(xiàn)當(dāng)鼠標(biāo)點(diǎn)中表格控件的某一個(gè)單元格時(shí),將單元格內(nèi)的值輸出來。等待大神的幫助……`

2015-12-17 11:25:02

我看好多芯片都支持AES硬件運(yùn)算單元,感覺用起來的卻沒有幾個(gè),不知道芯源這方面是不是和其他芯片的AES硬件一樣呢?我也想知道,這種硬件單元一般用在哪個(gè)場合比較多呢

2025-12-03 06:27:21

通用bootloader不選“支持spi flash”,download放于片內(nèi)flash,正常啟動,ota正常,app驅(qū)動at45db161讀寫正常。通用bootloader選“支持spi

2024-03-22 07:45:56

等原因?qū)е乱訤PGA實(shí)現(xiàn)比較困難。本文所述通過CH365芯片可以快速實(shí)現(xiàn)PCI接口電路的設(shè)計(jì),支持ISA總線接口向PCI總線接口的升級,并且由CH365芯片的本地硬件地址功能可以實(shí)現(xiàn)原系統(tǒng)軟件無需修改

2019-04-29 07:00:09

潤和Hi3861V100芯片迷你無線仿真USB Open OCD調(diào)試板多功能調(diào)試器

2023-03-28 13:07:10

彩電總線調(diào)試數(shù)據(jù)大全

1.進(jìn)入總線方法:在正常開機(jī)后,按遙控器上的“PSTD”、“SSTD”、“CALL”、“POWER”組合鍵進(jìn)入維修菜單,此時(shí),圖象模式變?yōu)椤皹?biāo)準(zhǔn)”、視頻

2008-10-08 18:09:03 65

65 在總線的主設(shè)備上增設(shè)了實(shí)時(shí)操作系統(tǒng)的任務(wù)優(yōu)先級分配機(jī)制,基于蒙特卡羅選擇實(shí)現(xiàn)總線仲裁器的仲裁策略,建立不同類型的從設(shè)備存儲器模型。運(yùn)用SystemC在交易級實(shí)現(xiàn)整個(gè)總線

2009-04-11 08:54:10 7

7 膠印機(jī)印刷單元的調(diào)試原理:3.7 印刷單元的調(diào)試原理

1.壓印滾筒是印刷單元的基準(zhǔn)

印刷單元各部分組件的作用及調(diào)節(jié)已分別講敘過,那么把它們放在一起應(yīng)該

2009-09-21 17:02:36 15

15 論文簡要介紹了智能家庭網(wǎng)絡(luò),詳細(xì)描述了一種基于歐洲設(shè)備安裝總線(EIB)的智能家庭網(wǎng)絡(luò)系統(tǒng)總線耦合單元的設(shè)計(jì)與實(shí)現(xiàn),詳細(xì)介紹了其通信協(xié)議棧的原理和實(shí)現(xiàn)機(jī)制,并進(jìn)

2009-12-22 11:00:15 23

23 以 FPGA 技術(shù)為基礎(chǔ),以Verilog HDL 為載體,設(shè)計(jì)了遵守Wishbone 片上總線規(guī)范的IP 核接口,實(shí)現(xiàn)了片上系統(tǒng)的IP 核互聯(lián)。

2010-01-13 15:09:14 13

13 本文介紹一種基于PCI Express 總線的高速數(shù)據(jù)采集卡的設(shè)計(jì)方案及功能實(shí)現(xiàn)。給出系統(tǒng)的基本結(jié)構(gòu)及單元組成,重點(diǎn)闡述系統(tǒng)硬件設(shè)計(jì)的關(guān)鍵技術(shù)和本地總線的控制邏輯,詳細(xì)探

2010-09-22 08:15:04 62

62 摘 要:提出了一種采用片內(nèi)PLL實(shí)現(xiàn)實(shí)速掃描測試的方案。在該方案中,移入測試向量時(shí)使用測試儀提供的時(shí)鐘,激勵施加和響應(yīng)捕獲采用片內(nèi)PLL生成的高速時(shí)鐘,從而降低了實(shí)速掃

2010-10-11 11:19:02 33

33 摘要:基于IP可重用的設(shè)計(jì)方法,利用WISHBONE總線協(xié)議,把兩個(gè)已成功開發(fā)出的具有自主知識產(chǎn)權(quán)的THUMP內(nèi)核在一個(gè)芯片上,實(shí)現(xiàn)了片上多處理器FPGA。開發(fā)重點(diǎn)是實(shí)

2009-06-20 15:29:35 839

839

產(chǎn)品概述VPX361是一款基于3U VPX總線架構(gòu)的8路射頻收發(fā)子模塊,板卡采用1片XCZU47DR RFSOC來實(shí)現(xiàn)8路射頻信號的高速采集、信號生成以及處理,并進(jìn)行智能目標(biāo)

2025-11-03 16:35:26

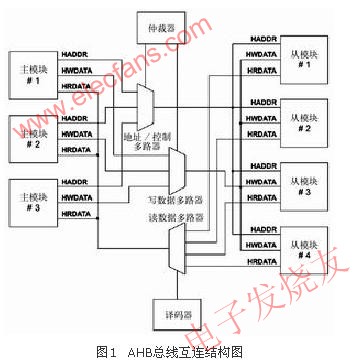

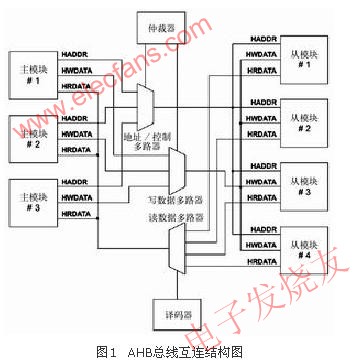

AMBA片上總線

AMBA 2.0規(guī)范包括四個(gè)部分:AHB、ASB、APB和Test Methodology。AHB的相互連接采用了傳統(tǒng)的帶有主模塊和從模塊的共享總線

,接口與互連功能分離,

2010-09-01 10:59:10 2347

2347

以 龍芯1號 處理器為研究對象,探討了嵌入式處理器中在片調(diào)試功能的設(shè)計(jì)實(shí)現(xiàn)方法。大大方便了軟件開發(fā)與系統(tǒng)調(diào)試

2011-06-29 17:45:26 48

48 本內(nèi)容提供了2812片內(nèi)ADC采樣時(shí)間計(jì)算。1)序列采樣模式(SMODE = 0)[attach]12497[/attach]

2011-09-05 11:39:36 3830

3830 設(shè)計(jì)開發(fā)了嵌入式實(shí)時(shí)操作系統(tǒng)VxWorks 的一種基于PC104 總線的板載支持包, 完成了相關(guān)的外圍驅(qū)動程序設(shè)計(jì)和調(diào)試工作。

2011-09-07 16:09:04 54

54 介紹了基于硬件描述語言Verilog HDL設(shè)計(jì)的SDX總線與Wishbone總線接口轉(zhuǎn)化的設(shè)計(jì)與實(shí)現(xiàn),并通過Modelsim進(jìn)行功能仿真,在QuartusⅡ軟件平臺上綜合,最終在Altera公司的CycloneⅢ系列FPGA上調(diào)試。實(shí)驗(yàn)

2012-01-11 10:21:21 25

25 基于總線的多DSP的交叉調(diào)試器的設(shè)計(jì)與實(shí)現(xiàn)

2016-05-19 13:41:19 9

9 TI C6000系列的DSP的內(nèi)部總線架構(gòu)、存儲系統(tǒng)和各種外設(shè)(如EDMA3和PRU等),特別是片內(nèi)的程序數(shù)據(jù)RAM和Cache系統(tǒng),以及外設(shè)的EDMA控制器,Video port,McBSP,McASP以及SRIO接口等。

2016-12-29 14:10:10 8109

8109

本文檔內(nèi)容介紹了調(diào)試數(shù)字硬件設(shè)計(jì)的步驟,以及框架原理圖,供網(wǎng)友參考。

2017-09-15 18:54:54 4

4 總線的多DSP交叉調(diào)試器的設(shè)計(jì)與實(shí)現(xiàn)

2017-10-19 10:50:18 2

2 瑞士硬件工具制造商Abatron宣布它的Linux硬件調(diào)試工具現(xiàn)在支持Cavium的Octeon和Octeon Plus處理器。這家公司宣稱:Abatron的BDI2000 和 BDI3000 調(diào)試

2017-10-20 09:58:58 1

1 本文以workbench 為平臺,vxworks 為操作系統(tǒng),chipscope 為分析工具,介紹了完整的ARINC429 協(xié)議和422協(xié)議的FPGA 硬件調(diào)試,通過硬件調(diào)試發(fā)現(xiàn)modelsim

2017-11-18 08:56:01 23632

23632

片上系統(tǒng)的出現(xiàn)使得芯片可以實(shí)現(xiàn)更加復(fù)雜的功能,獲取更高的性能,但同時(shí)其內(nèi)部信號也變得越來越難以觀察和控制,相應(yīng)的測試和調(diào)試工作也遇到了難以克服的時(shí)間復(fù)雜性困難。國際半導(dǎo)體技術(shù)路線圖

2017-12-01 02:01:34 564

564

性能的優(yōu)劣。面對日趨多樣的ECU和通信總線類型,開發(fā)一種支持多總線的、通用靈活的標(biāo)定系統(tǒng),具有非常高的實(shí)用價(jià)值[1]。目前,CAN總線作為一種可靠的汽車總線已經(jīng)廣泛應(yīng)用于高檔汽車,因而多數(shù)標(biāo)定系統(tǒng)都是

2018-06-20 14:29:00 11554

11554

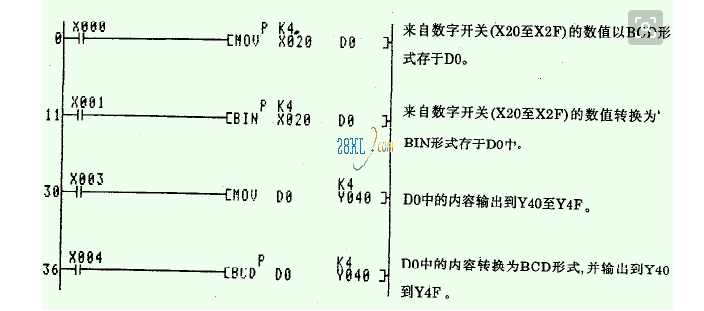

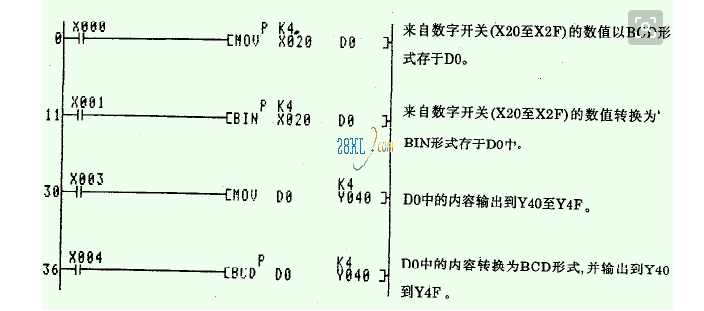

把二進(jìn)制數(shù)轉(zhuǎn)換成 BCD 碼,是很常見的,做而論道以前也發(fā)表過這樣的程序。 但是,過去都是用寄存器,如果要求用片內(nèi)RAM單元,就少見了。 當(dāng)然,也可以把片內(nèi)RAM單元的數(shù)據(jù),先傳送到寄存器,再利用

2018-05-19 01:18:00 4301

4301

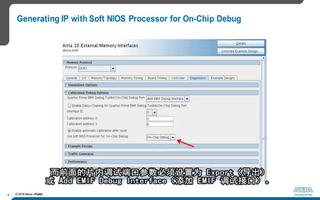

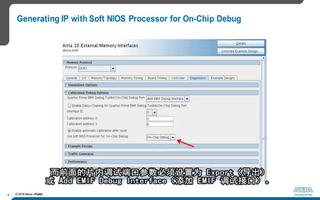

使用片內(nèi)調(diào)試 Nios 軟核處理器

2018-06-20 05:53:00 3888

3888

AVR單片機(jī)片內(nèi)TWI總線的原理和使用

2018-07-11 00:27:00 3735

3735

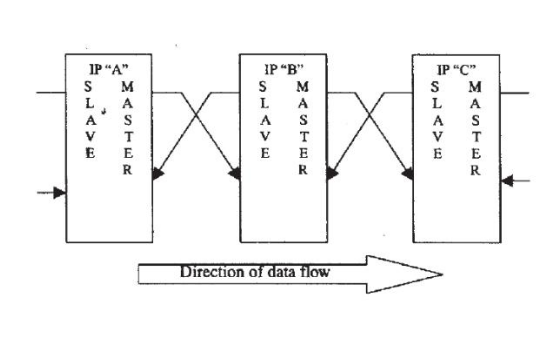

IP復(fù)用是片上系統(tǒng)時(shí)代的核心技術(shù)之一。由于IP核的設(shè)計(jì)千差萬別,它們要能夠直接連接,就要遵守相同的接口標(biāo)準(zhǔn)。在片上系統(tǒng)中,處理器核和所有外設(shè)通過共享總線互通互聯(lián),因此這些IP核必須遵守相同的總線

2018-07-04 09:02:32 5769

5769

隨著芯片規(guī)模的增大和復(fù)雜度的上升,片內(nèi)信號的觀測和控制更加困難,對芯片的測試及調(diào)試的難度也在不斷上升,芯片的測試和調(diào)試問題成為制約整個(gè)行業(yè)發(fā)展的重要因素。如何合理地對數(shù)字信號處理器進(jìn)行可測性設(shè)計(jì)、建立調(diào)試支持成為數(shù)字信號處理器設(shè)計(jì)的核心問題之一。

2019-03-22 17:04:08 2

2 用CCES調(diào)試硬件目標(biāo)

2019-08-19 06:07:00 4079

4079 多個(gè)ADM1260器件可以相連,將電壓時(shí)序控制器解決方案從10 V供電軌擴(kuò)展至40 V。這可以通過使用一個(gè)片內(nèi)總線和ADI Power Studio工具實(shí)現(xiàn),該工具可將多個(gè)器件虛擬化為單一器件。

2019-06-17 06:21:00 2223

2223 片內(nèi)總線負(fù)責(zé)連接CPU芯片內(nèi)部的各個(gè)模塊,包括CPU核心以及顯示核心、內(nèi)存控制器等輔助模塊。

2020-07-21 17:22:37 4267

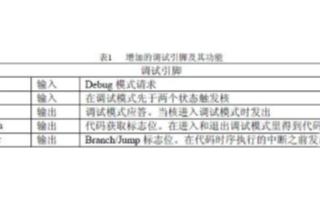

4267 為了能讓嵌入式微處理器的片上調(diào)試功能也能夠像高級語言編程工具那樣支持斷點(diǎn)設(shè)置、單步執(zhí)行、寄存器內(nèi)容的查看和內(nèi)存內(nèi)容查看等功能,文章提出了一種在線調(diào)試模塊設(shè)計(jì),此設(shè)計(jì)為嵌入式微處理器增加了一些專用

2021-03-23 14:55:48 3282

3282

面向硬件實(shí)現(xiàn)的HEVC幀內(nèi)編碼快速算法

2021-06-21 16:30:15 10

10 單片機(jī)系統(tǒng)硬件的靜態(tài)調(diào)試和動態(tài)調(diào)試綜述

2021-07-18 10:59:14 3

3 和事件跟蹤、指令跟蹤等。 有很多網(wǎng)友反應(yīng),Keil MDK在調(diào)試的時(shí)候,會遇到各種問題,下面就簡單講述一下Keil MDK調(diào)試時(shí),軟件和硬件的一些要求。 1.邏輯分析儀它要求目標(biāo)硬件支持 SWO 或

2021-11-16 09:15:53 3717

3717 地址為 40H、88H 的位,該位所在字節(jié)的字節(jié)地址分別為__ 和__ 。答:28H,88H4. 片內(nèi)字節(jié)地址為 2AH 單元最低位的位地址是__ ;片內(nèi)字節(jié)地址為 A8H 單元的最低位的 位地址為__ 。答:50H,A8H5. 若 A 中的內(nèi)容為 63H,那么,P 標(biāo)志位的值為__ 。答:0

2021-11-23 17:06:43 7

7 1. 引言SPI : serial perripheral interface 串行外圍設(shè)備接口SPI總線是硬件上用的比較多的一種串行總線,高速傳輸,無應(yīng)答無校驗(yàn)。這里簡單記錄一下SPI總線的一些

2021-12-22 19:18:59 8

8 J-Link支持一項(xiàng)名為“無限Flash斷點(diǎn)”(Unlimited Flash Breakpoints)的調(diào)試功能。“無限Flash斷點(diǎn)”允許用戶在Flash中調(diào)試時(shí)設(shè)置無限數(shù)量的斷點(diǎn)。如果沒有此功能,在Flash中能夠設(shè)置的斷點(diǎn)數(shù)量限制為CPU調(diào)試單元支持的硬件斷點(diǎn)數(shù)。

2022-05-07 09:54:43 2853

2853 在硬件方案設(shè)計(jì)中,需滿足測試工具的外設(shè)需求,常用外設(shè)包含觸摸式顯示屏、TF存儲卡、EtherCAT總線從站、MetroLink-Ⅲ總線從站、鍵盤等,調(diào)試用外設(shè)包含串口調(diào)試工具、OTG調(diào)試工具、鼠標(biāo)等。

硬件整體設(shè)計(jì)框架如圖1所示。

2022-11-02 14:52:10 1649

1649 所有J-Link型號(J-Link PRO、J-Link ULTRA+、J-Link PLUS和J-Link BASE)最新硬件版本現(xiàn)在都支持通過JTAG和SWD接口高速下載和調(diào)試。

2023-04-14 14:20:26 2965

2965 片內(nèi)和片間非均勻性是什么?有什么作用呢? 片內(nèi)和片間非均勻性是指光學(xué)元件(如透鏡)表面上的厚度/形狀/折射率等參數(shù)的變化,以及元件之間的相對位置誤差所引起的光學(xué)性能差異。這種非均勻性在光學(xué)系統(tǒng)中

2023-12-19 11:48:19 1512

1512 電子發(fā)燒友網(wǎng)站提供《實(shí)現(xiàn)多軸電機(jī)驅(qū)動系統(tǒng)內(nèi)的多片C2000 PWM同步.pdf》資料免費(fèi)下載

2024-09-03 09:25:17 2

2 新的硬件支持包不僅無需耗時(shí)的手寫代碼優(yōu)化和驗(yàn)證,還支持處理器在環(huán)測試 MathWorks 今天宣布,推出針對 Qualcomm? Hexagon? 神經(jīng)處理單元(NPU)的硬件支持包。該處理單元嵌入

2024-09-23 11:59:05 905

905 硬件調(diào)試是硬件系統(tǒng)設(shè)計(jì)、開發(fā)和制造過程中不可或缺的一環(huán),旨在對可能出現(xiàn)的問題進(jìn)行分析和解決。以下是進(jìn)行硬件調(diào)試的一般步驟和方法: 一、準(zhǔn)備階段 熟悉設(shè)計(jì)文檔:在開始調(diào)試之前,需要詳細(xì)閱讀和理解硬件

2024-11-10 10:17:40 2894

2894

摘要: 本文深入探討了 JLink 調(diào)試器在嵌入式系統(tǒng)硬件調(diào)試中的應(yīng)用,詳細(xì)闡述了 JLink 驅(qū)動配置的方法以及硬件調(diào)試技巧。本文以國科安芯的AS32系列MCU芯片為例,通過分析 JLink

2025-06-12 23:20:26 1405

1405

電子發(fā)燒友App

電子發(fā)燒友App

評論