ASIC和FPGA具有不同的價值主張,在作出選擇前必須仔細評估。兩種種技術對比。這里介紹了ASIC和FPGA 的優(yōu)勢與劣勢。

2011-03-31 17:30:09 5926

5926

RFMD全新的RF5836以單個前端模塊 (FEM)方式為 WiFi 802.11a/n 系統(tǒng)提供完整的集成解決方案。超小型的形狀因數(shù)和集成配套使客戶應用中的布局面積縮減至最小,并且大大減少了外部組件的

2012-07-05 09:41:04 1374

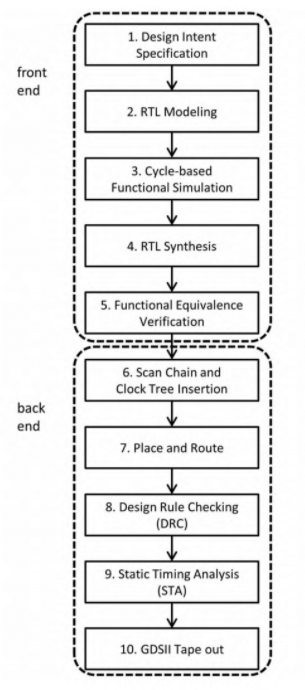

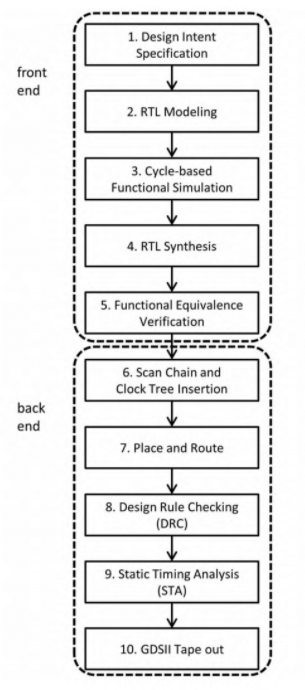

1374 FPGA的前端設計流程類似于ASIC,但后端不同。FPGA的后端部分與ASIC的主要區(qū)別在于FPGA的布局和布線。對于ASIC,place and route軟件決定IC的制造方式。

2022-06-20 16:24:12 6339

6339

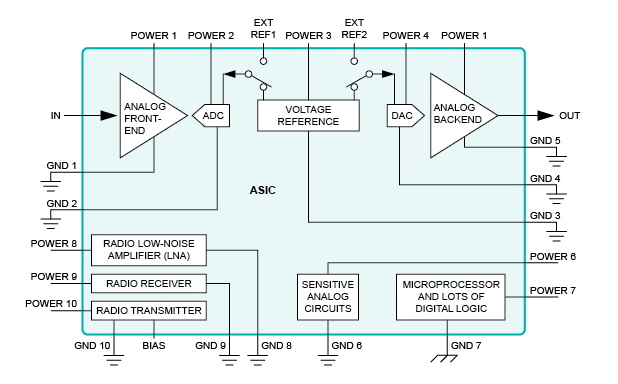

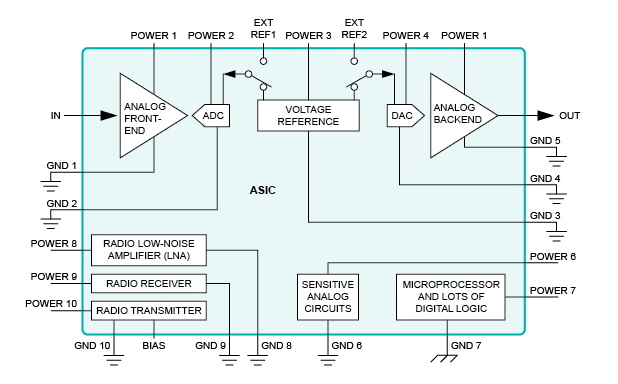

系統(tǒng)整體架構的前提下,首先應該在原理圖和PCB布線設計中自覺融合模塊化的設計思想,結合PCB的實際情況,規(guī)劃好對PCB進行布局的基本思路,如圖1所示。

2022-09-15 09:20:53 2925

2925 根據(jù)ASIC邏輯設計,優(yōu)化的約束是速度和面積。在物理設計中,我們需要對面積、速度和功率進行優(yōu)化設計。根據(jù)所需的技術節(jié)點和策略進行更好的功耗規(guī)劃,總是有助于獲得芯片的布局。

2023-07-11 09:31:43 1179

1179

有誰知道偏航角傳感器ASIC中的iWD是什么,作用是什么?

2013-05-01 11:21:42

ASIC1810 - ASIC1810 - List of Unclassifed Manufacturers

2022-11-04 17:22:44

)的。 ASIC通常被設計和使用在特定系統(tǒng)中的單個公司。開發(fā)ASIC非常昂貴、耗時、資源密集的,但ASIC確實能提供低功耗的高性能。 ASSP——專用標準產(chǎn)品 專用標準產(chǎn)品(ASSP)的設計和實施

2014-07-24 11:18:05

ASIC的設計流程是怎樣的?FPGA的開發(fā)流程又是怎樣的?

2021-11-01 07:08:47

已經(jīng)非常成熟,并且可以在傳感器的接口ASIC中實現(xiàn)。Σ-Δ閉環(huán)傳感器的架構選擇需要依據(jù)為電子Σ-Δ系統(tǒng)開發(fā)的深層技術。然而,具有自然電子-機械特性的Σ-Δ閉環(huán)傳感器在系統(tǒng)級設計與優(yōu)化時需要正確理解

2018-12-05 15:12:05

1、概念區(qū)別: ASIC(專用集成電路)是一種在設計時就考慮了設計用途的IC。 FPGA(現(xiàn)場可編程門陣列)也是一種IC。顧名思義,只要有合適的工具和適當?shù)膶I(yè)基礎,工程師就可以對FPGA

2020-12-01 17:41:49

專用集成電路(ASIC)采用硬接線的固定模式,而現(xiàn)場可編程門陣列 (FPGA)則采用可配置芯片的方法,二者差別迥異。可編程器件是目前的新生力量,混合技術也將在未來發(fā)揮作用。 與其他技術一樣,有關

2019-07-19 06:24:30

以用戶參加設計為特征的專用集成電路 (ASIC),它能實現(xiàn)整機系統(tǒng)的優(yōu)化設計,性能優(yōu)越,保密性強。專用集成電路可以把分別承擔一些功能的數(shù)個,數(shù)十個,甚至上百個通用中,小規(guī)模集成電路的功能集成在一塊芯片

2020-08-28 15:51:54

ASIC設計,會給人帶來什么?

2012-03-21 12:54:38

1ASIC 驗證技術.................................................11.1 ASIC 設計流程

2015-09-18 15:26:25

ASIC是什么?ASIC設計可以分為哪幾個部分?

2021-11-01 07:42:01

如果要破解asic,有哪些辦法?

2012-11-15 22:11:08

CENDENCE ASIC 設計不錯的中文資料

2010-04-26 11:13:49

起了。(ASIC 基本架構)四、兩者的設計流程完整的 FPGA 設計流程包括功能描述、電路設計與輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實現(xiàn)與布局布線、時序仿真、板級仿真與驗證、調(diào)試與加載配置。ASIC

2020-09-25 11:34:41

描述、電路設計與輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實現(xiàn)與布局布線、時序仿真、板級仿真與驗證、調(diào)試與加載配置。ASIC的設計流程(數(shù)字芯片)包括:功能描述、模塊劃分、模塊編碼輸入、模塊級仿真驗證

2017-09-02 22:24:53

FPGA/ASIC高性能數(shù)字系統(tǒng)設計 狀態(tài)機與數(shù)據(jù)路徑 1 有限狀態(tài)機 1.1 基本概念 1.2 狀態(tài)機分類 1.3 狀態(tài)機描述方法 1.4 狀態(tài)機的編碼風格 1.5 可綜合的fsm編碼 1.6

2011-03-02 09:35:30

RT-Thread Studio怎么為單個c文件打開編譯器優(yōu)化

2024-02-19 06:45:33

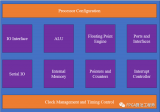

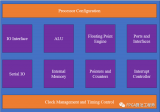

設計。 現(xiàn)代ASIC常包含整個32-bit處理器,類似ROM、RAM、EEPROM、Flash的存儲單元和其他模塊. 這樣的ASIC常被稱為SoC(片上系統(tǒng))。 FPGA是ASIC的近親,一般通過

2012-02-27 17:46:03

我已經(jīng)完成了我的fpga實現(xiàn),如何轉向asic實現(xiàn)?我們正在使用ieee_proposed。這項技術具體嗎?

2020-03-19 09:28:49

簡歷投遞郵箱: nahu@nvidia.com咨詢電話/QQ : 021-61041985/ 2604987025We are nowlooking for an ASIC PD

2017-07-21 18:01:25

很快,ASIC這種開發(fā)周期,很要命。

綜合上述原因,GPU才有了現(xiàn)在的大好局面。

在AI訓練上,GPU的算力強勁,可以大幅提升效率。

在AI推理上,輸入一般是單個對象(圖像),所以要求要低一點,也

2024-01-23 19:08:55

的功能子模塊的互連線大致等長。Astro工具的使用 Synopsys公司的Astro是在ASIC設計中流行的后端物理實現(xiàn)工具,是深亞微米芯片設計進行設計優(yōu)化、布局、布線、計算時延的設計環(huán)境。Astro

2012-11-09 19:04:35

不同模型的NPU,而不是硬編碼和只支持優(yōu)化特定模型的NPU。在ASIC中,加速特定NN算子的數(shù)字硬件模塊可以與通用NPU一起使用。盡管這些模塊的架構是固定的,但它們還是可以在一定程度上進行配置:例如,接受

2023-02-08 15:26:46

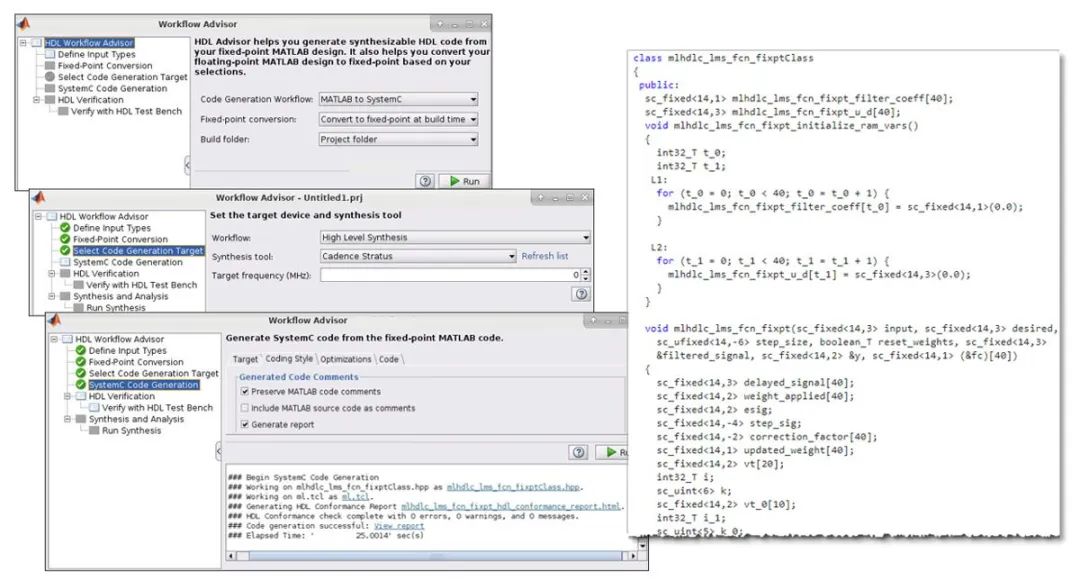

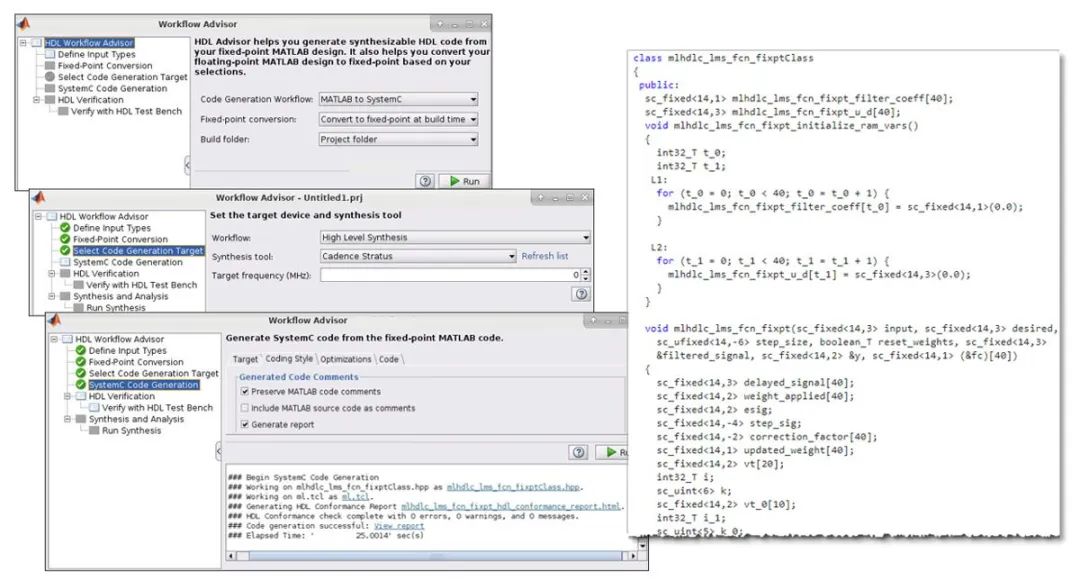

相比,能夠為通信和多媒體應用提供高達10倍速的更高的設計和驗證能力。Synphony HLS為ASIC 和 FPGA的應用、架構和快速原型生成最優(yōu)化的RTL。Synphony HLS解決方案架構圖

2019-08-13 08:21:49

行相應處理,更換光模塊、更換尾纖、清潔尾纖頭、重新盤熔纖盒、更換法蘭等。 4.轉接點較多的光纜,要逐一檢查光交、清潔光纖頭或更換光路。 5.BBU和RRU距離遠,跳接較多,優(yōu)化BBU與RRU的路由,減少光

2020-12-03 14:50:52

現(xiàn)在的ASIC綜合器可以綜合出經(jīng)過優(yōu)化的乘法、除法和求模的電路嗎?也就是說在Verilog代碼里直接用*、/和%就可以實現(xiàn)相應運算嗎?

2014-11-12 16:35:26

如何檢測低能量、高密度的X射線輻射?如何對ASIC進行測試?

2021-04-13 06:23:20

ASIC與SoC器件的成本不斷上升,迫使半導體廠商不斷擴大每種器件的市場應用范圍,以提高投資回報率。軟件使用的趨勢還在不斷加強,這作為一種有效的機制,擴大了單個器件的市場使用范圍,因為軟件內(nèi)容能帶

2019-07-11 08:25:57

ASIC設計文檔:ANSI c++ Standard

2009-04-11 15:12:11 43

43 GPRS優(yōu)化思路總結報告:一、概述 2二、無線優(yōu)化的思路 2三、(E)GPRS網(wǎng)絡資源容量分析優(yōu)化 53.1、(E)GPRS網(wǎng)絡拓撲結構 63.2、GB口分析優(yōu)化 63.3、ABIS口分析

2009-07-27 21:29:34 26

26 ASIC設計技術及其發(fā)展研究:對ASIC 設計的工作流程和相關工具軟件進行了簡要介紹,并概括了ASIC 設計的發(fā)展過程和較新趨勢,以促進大家對芯片設計領域的認識和了解。1、引言

2009-12-13 20:02:51 11

11 數(shù)字下變頻器中坐標變換模塊的ASIC 實現(xiàn)成都電子科技大學通信與信息工程學院劉欣 林水生 李廣軍摘要:本文介紹了一種基于CORDIC 算法的數(shù)字下頻器(DDC)中坐標變換模塊的

2009-12-24 10:54:50 13

13 基于ASIC/SoC的UART核的設計

摘要:本文描述了通用異步收發(fā)機UART(Universal Asynchronous Receive Transmitter)核的一種優(yōu)化設計實現(xiàn)的設計流程。通過采用劃分功能模塊使結構直觀

2010-06-19 09:55:32 26

26 數(shù)字下變頻器中坐標變換模塊的ASIC實現(xiàn)

1.引言 數(shù)字下變頻(DDC)技術是軟件無線電接收機的核心技術。其基本功能是從輸人的寬帶高速數(shù)字信

2007-08-15 16:32:54 1561

1561 平臺ASIC架構突破傳統(tǒng)ASIC設計局限性

采用先進半導體工藝,結構化ASIC平臺可以提供更多經(jīng)預定義、預驗證和預擴散的金屬層,并支持各種存儲器接口,能簡化接口設計

2009-12-27 13:33:33 1669

1669

ASIC,ASIC是什么意思

ASIC(Application Specific Integrated Circuits)即專用集成電路,是指應特定用戶要求和特定電子系統(tǒng)的需要而設計、制造

2010-03-26 17:10:27 8082

8082 基于標準單元ASIC設計

基于標準單元的設計是指把一些基本單元乃至具有相當強功能的模塊預先設計好,作為標準單元存入CAD 系統(tǒng)中,

2010-03-26 17:12:43 1347

1347 金屬基板模塊電源EMI優(yōu)化從鋁基板電源模塊,PCB布局布線出發(fā)分析了鋁基板模塊的EMI模型以及造成EMI差的原因。

2011-09-21 17:29:20 42

42 本文描述ASIC驗證方法和過程,有助于ASIC設計者對驗證的認識。模擬是驗證ASIC并產(chǎn)生測試矢量的唯一途徑,設計者可以對ASIC芯片或者在ASIC應用系統(tǒng)中進行功能和時序模擬。

2012-05-24 09:32:47 23

23 本文描述ASIC驗證方法和過程,有助于ASIC設計者對驗證的認識。模擬是驗證ASIC并產(chǎn)生測試矢量的唯一途徑,設計者可以對ASIC芯片或者在ASIC應用系統(tǒng)中進行功能和時序模擬。

2012-05-24 09:32:47 27

27 (E)GPRS 優(yōu)化思路通信網(wǎng)絡優(yōu)化,GSM上網(wǎng),PDCH,EDGEGPRS.

2016-01-14 15:21:36 4

4 ASIC設計在尺寸和復雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。

2017-02-11 16:26:11 1342

1342

基于STM32的空氣凈化控制系統(tǒng),包含溫濕度,粉塵傳感器模塊設計思路。

2017-08-30 16:43:02 17

17 ASIC設計在尺寸和復雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。然而,這些設計中仍然保留有1/3(那就是說,所有ASIC設計中的1/9

2017-11-25 09:05:02 1312

1312 文檔分享一個藍牙4.0模塊控制LED彩燈調(diào)光調(diào)色設計思路,分為兩大類:第一類:1 個手機控制 1 個 LED 彩燈,可實現(xiàn) 3 種控制方式;第二類:1 個手機控制多個 LED 彩燈

2018-03-23 14:55:37 34

34 分享一個串口WiFi模塊實現(xiàn)遠程控制電飯煲的設計思路,通過串口wifi模塊可以在手機app上遠程操控電飯煲,相比定時的效果更好!

2018-04-26 16:57:56 77

77 MSP430超低功耗微控制器上的定時器模塊通常以單個時基為基礎輸出幾個不同的輸出——一個定時器周期。

2018-05-08 09:47:23 6

6 指紋識別模塊的硬件設計采用 SOPC的設計思路[1],在FPGA內(nèi)部實現(xiàn)指紋讀取 UART接口、FLASH存儲器接口、SDRAM控制器、PIO控制的鍵盤和 LCD顯示接口。

2018-08-18 09:45:12 1254

1254

該模塊能實現(xiàn)32路12位的A,D數(shù)據(jù)采集和16路的TTL電平輸入輸出控制。文本介紹了此模塊的設計思路、實現(xiàn)過程、FPGA編程以及它們的應用。實踐證實模塊工作性能穩(wěn)定、可靠性高、使用方便。

2018-10-15 18:21:06 14

14 推出ASIC級全可編程架構

2018-11-30 06:03:00 2949

2949 FPGA是可編程ASIC。 ASIC:專用集成電路,它是面向專門用途的電路,專門為一個用戶設計和制造的。

2018-12-15 09:58:46 6158

6158 一旦僅用于膠合邏輯,F(xiàn)PGA已經(jīng)發(fā)展到可以在單個器件上構建片上系統(tǒng)(SoC)設計的程度。門和功能的數(shù)量急劇增加,以與傳統(tǒng)上僅通過ASIC設備提供的功能相競爭。本文介紹了FPGA設計方法優(yōu)于ASIC的一些優(yōu)勢,包括早期上市,輕松過渡到結構化ASIC,以及降低NRE成本。

2019-09-14 12:28:00 2923

2923 所謂ASIC代表“特定應用集成電路”,它們是針對特定哈希算法而進行優(yōu)化的專用挖礦硬件。ASIC礦機被用于加密貨幣挖礦,且絕大多數(shù)只能用于這種應用。就效率而言,ASIC礦機明顯要比GPU要更加強大。

2019-10-31 11:25:30 3070

3070 本文首先介紹了asic的概念,其次介紹了ASIC的特點,最后介紹了ASIC設計過程。

2020-04-23 10:53:45 9964

9964 本文檔的主要內(nèi)容詳細介紹的是FPGA模塊化設計與AlteraHardCopy結構化ASIC。

2021-01-20 17:03:51 7

7 電子發(fā)燒友網(wǎng)為你提供VoLTE優(yōu)化思路干貨資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-23 08:42:03 9

9 電子發(fā)燒友網(wǎng)為你提供日常網(wǎng)絡優(yōu)化思路資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-25 08:41:02 2

2 FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現(xiàn)(第四屆星載電源技術學術研討會)-該文檔為FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現(xiàn)總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 11:05:19 6

6 直流充電樁電源模塊磁性器件優(yōu)化(軍用通信電源技術有哪些)-直流充電樁電源模塊磁性器件優(yōu)化,很好的論文!

2021-09-27 12:42:21 32

32 近年來,關于定制ASIC的優(yōu)勢被談論的很多。特別是,隨著工業(yè)物聯(lián)網(wǎng)(IIoT)的發(fā)展,越來越多的原始設備制造商(OEM)正在尋求開發(fā)定制ASIC,以獲得滿足其嚴格要求的具有針對性且優(yōu)化的產(chǎn)品。由于

2021-09-30 09:27:06 5885

5885 【GCC編譯優(yōu)化系列】實戰(zhàn)分析C工程代碼可能遇到的編譯問題及其解決思路

2022-07-10 23:15:27 2426

2426

ASIC設計中詳細設計方案的確定非常重要,同樣的設計,別人可以用比你小30%的面積和少30%的處理時間來實現(xiàn),這才是設計工程師的價值體現(xiàn)之處。任何設計在最開始的時候都是一頭霧水,場景復雜,各種耦合

2022-10-12 15:27:25 1381

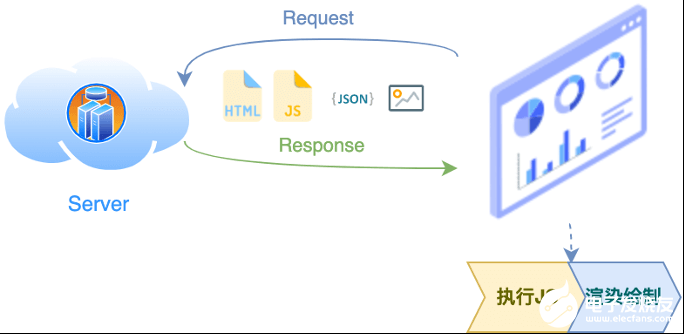

1381 本文旨在整理常見Web前端性能優(yōu)化的思路,可供前端開發(fā)參考。因為力求精簡,限于篇幅,所以并未詳述具體實施方案。 基于現(xiàn)代Web前端框架的應用,其原理是通過瀏覽器向服務器發(fā)送網(wǎng)絡請求,獲取必要

2022-10-18 14:21:28 1507

1507

FPGA vs ASIC 相同點 都設計使用硬件描述語言(HDL),如VHDL或Verilog。但ASIC相比于FPGA開發(fā)上,代碼風格更為隨意,因為FPGA是先有電路,后有代碼,ASIC是先有代碼

2022-11-28 10:30:13 2052

2052 常規(guī)的伺服優(yōu)化調(diào)整一般需要用到SERVO GUIDE 軟件,而對于一些不是很懂該軟件操作的客戶或者在現(xiàn)場無法進行在線聯(lián)網(wǎng)調(diào)整的情況下,手動調(diào)整就顯得比較關鍵實用,在此提供手動伺服優(yōu)化調(diào)整思路。

2023-01-29 12:18:56 4328

4328 控制器設計上有兩種思路,集中式和分散式。集中式的控制器設計將機器人的大多數(shù)電子模塊(驅動電源模塊、伺服驅動模塊、通信模塊、IO模塊)都集成在控制器中,大多機器人廠商會選擇這種設計,整體打包給下游廠商。

2023-02-08 09:47:31 2347

2347 在硬件層面,ASIC 芯片由基本硅材料、磷化鎵、砷化鎵、氮化鎵等材料構成。在物理結構層面,ASIC 芯片模塊由外掛存儲單元、電源管理器、音頻畫面處理器、網(wǎng)絡電路等IP核拼湊而成。

2023-02-08 10:02:41 8400

8400 本篇文章是GEMM優(yōu)化的第一個部分,在這篇文章中,只說優(yōu)化思路和分析。

2023-05-25 09:03:40 4861

4861

ASIC設計在尺寸和復雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進展意味著這些設計中的2/3能夠使用單個FPGA進行建模。然而,這些設計中仍然保留有1/3(那就是說,所有ASIC設計中的1/9

2023-06-04 16:50:01 2194

2194 沒有關于 ASIC 確切含義的官方聲明,而且許多電子專業(yè)人士可能并不總是就 ASIC 到底是什么或特定組件是否應歸類為 ASIC 達成一致。

2023-06-15 09:41:51 2003

2003

根據(jù)ASIC邏輯設計,優(yōu)化的約束是速度和面積。在物理設計中,我們需要對面積、速度和功率進行優(yōu)化設計。根據(jù)所需的技術節(jié)點和策略進行更好的功耗規(guī)劃,總是有助于獲得芯片的布局。

2023-07-09 11:28:33 1402

1402

ASIC 設計是開發(fā)復雜電子系統(tǒng)的過程。該系統(tǒng)可制造成特殊用途的半導體設備,通常用于大批量應用或具有嚴格的功耗、性能和尺寸限制的應用。ASIC 系統(tǒng)設計人員使用高級語言并通過仿真和可視化來開發(fā)和評估算法。

2023-07-20 10:29:04 1761

1761

我們有個業(yè)務,會調(diào)用其他部門提供的一個基于http的服務,日調(diào)用量在千萬級別。使用了httpclient來完成業(yè)務。之前因為qps上不去,就看了一下業(yè)務代碼,并做了一些優(yōu)化,記錄在這里。

2023-09-12 11:18:15 1067

1067 噪聲是混合信號 ASIC 中的一個常見問題,會降低性能并危及產(chǎn)品的完成度。本應用筆記提供了添加外部電路的提示和技巧,使許多 ASIC 可用于原型設計或作為終產(chǎn)品進行交付。討論了通過校正模擬電路中的噪聲、進行調(diào)整、校準增益和偏移以及清潔電源來優(yōu)化 ASIC 的方法。

2023-10-04 17:30:00 611

611

單個MOS管可以構成的模塊? 單個MOS管可以構成各種各樣的電路模塊,這些電路模塊可以應用在不同的領域,例如電力電子、通信、計算機等。本文將詳細介紹單個MOS管可以構成的模塊及其應用。 1.

2023-09-18 18:20:48 1652

1652 本作品基于Ansys SIwave,Icepak和Mechanical,對射頻頻率綜合集成模塊進行了電熱力多場聯(lián)合分析和優(yōu)化設計。對電熱力綜合性能進行了優(yōu)化,同時實現(xiàn)了面積縮減目標。實測結果驗證了電熱仿真的準確性。

2023-10-15 15:33:50 1304

1304

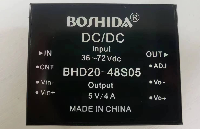

DC電源模塊的價格因素是什么?如何進行成本優(yōu)化?

2023-11-08 10:52:12 1596

1596

BOSHIDA DC電源模塊的能效優(yōu)化探索與應用 DC電源模塊的能效優(yōu)化探索與應用是一項重要的研究領域。能效優(yōu)化可以提高電源模塊的功率轉換效率,減少能源的浪費,降低電源模塊的發(fā)熱量,延長其使用壽命

2023-12-22 11:16:17 944

944

DC電源模塊的能效優(yōu)化探索與應用是一項重要的研究領域。能效優(yōu)化可以提高電源模塊的功率轉換效率,減少能源的浪費,降低電源模塊的發(fā)熱量,延長其使用壽命。以下是一些能效優(yōu)化的探索和應用方向:

2023-12-22 14:28:01 1016

1016

BOSHIDA ?AC/DC電源模塊的設計與優(yōu)化 AC/DC電源模塊是一種將交流電轉換成直流電的設備,廣泛應用在各種電子設備中。其設計和優(yōu)化是為了提高轉換效率、降低功耗和提高性能穩(wěn)定性。本文將從

2024-05-17 13:44:42 1111

1111

電子發(fā)燒友網(wǎng)站提供《單個 MSP430? 計時器模塊的多時基應用說明.pdf》資料免費下載

2024-09-13 11:09:19 0

0 隨著現(xiàn)在AI的快速發(fā)展,使用FPGA和ASIC進行推理加速的研究也越來越多,從目前的市場來說,有些公司已經(jīng)有了專門做推理的ASIC,像Groq的LPU,專門針對大語言模型的推理做了優(yōu)化,因此相比GPU這種通過計算平臺,功耗更低、延遲更小,但應用場景比較單一,在圖像/視頻方向就沒有優(yōu)勢了。

2024-10-29 14:12:01 2770

2770

ASIC(Application-Specific Integrated Circuit,應用特定集成電路)集成電路性能優(yōu)化是一個復雜而關鍵的過程,涉及多個層面的技術和策略。以下是一些關鍵的優(yōu)化方法

2024-11-20 15:52:41 2061

2061 在現(xiàn)代電子系統(tǒng)中,效率和性能是衡量一個系統(tǒng)優(yōu)劣的關鍵指標。隨著技術的發(fā)展,ASIC集成電路因其高度定制化和優(yōu)化的特性,在提高系統(tǒng)效率方面發(fā)揮著越來越重要的作用。 ASIC的定義和特點 ASIC是一種

2024-11-20 15:57:40 1462

1462 的性能和能效比。以下是對ASIC集成電路在人工智能中應用的分析: 一、ASIC集成電路的優(yōu)勢 高性能 :ASIC針對特定應用進行優(yōu)化設計,可以充分發(fā)揮硬件的并行處理能力,實現(xiàn)高性能計算。這使得ASIC在處理人工智能任務時,如深度學習、神經(jīng)網(wǎng)絡計算等,能夠表現(xiàn)出更高的計算速度和更低的延遲。 高

2024-11-20 16:03:44 3285

3285 FPGA與ASIC的區(qū)別 FPGA(現(xiàn)場可編程門陣列)和ASIC(專用集成電路)是兩種不同的集成電路技術,它們在多個方面存在顯著的區(qū)別: FPGA ASIC 基本定義 由通用的邏輯單元組成,可以通過

2024-12-02 09:51:54 1816

1816 如何優(yōu)化光模塊性能 優(yōu)化光模塊性能可以從多個方面入手,以下是一些關鍵方法: 提高傳輸速率 : 增加波特率 :這是提高光模塊傳輸速率的一種直接方法,但需要注意信噪比問題。 使用多路并行傳輸技術 :通過

2024-12-02 14:42:31 2025

2025 Verilog與ASIC設計的關系 Verilog作為一種硬件描述語言(HDL),在ASIC設計中扮演著至關重要的角色。ASIC(Application Specific Integrated

2024-12-17 09:52:26 1542

1542

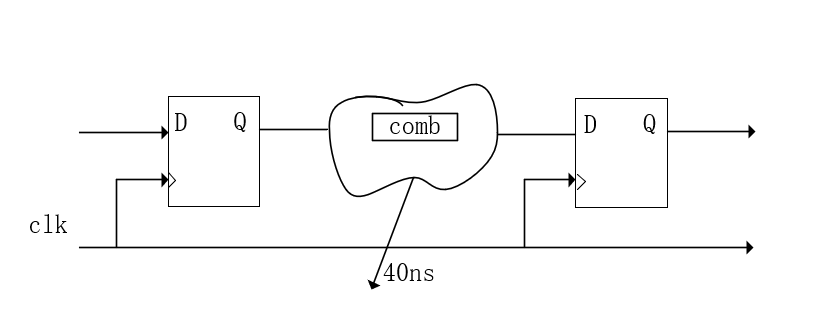

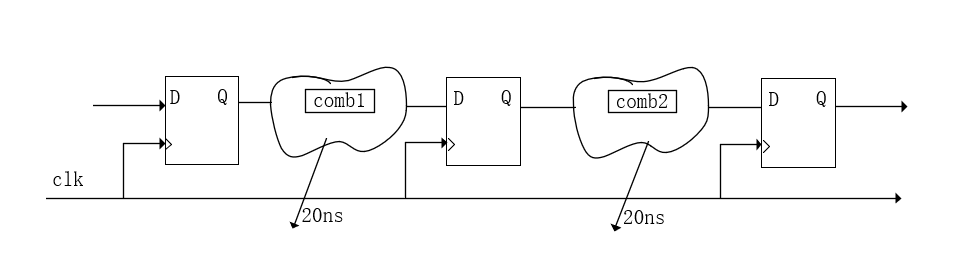

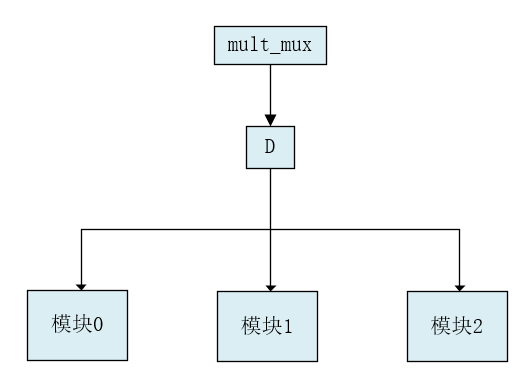

任何的數(shù)字電路都可以等效成組合邏輯加D觸發(fā)器打拍,兩個D觸發(fā)器之間的組合邏輯路徑?jīng)Q定了,系統(tǒng)的工作頻率,決定芯片的性能。所以為了提高芯片的工作頻率,使用流水線技術在組合邏輯中插入寄存器。

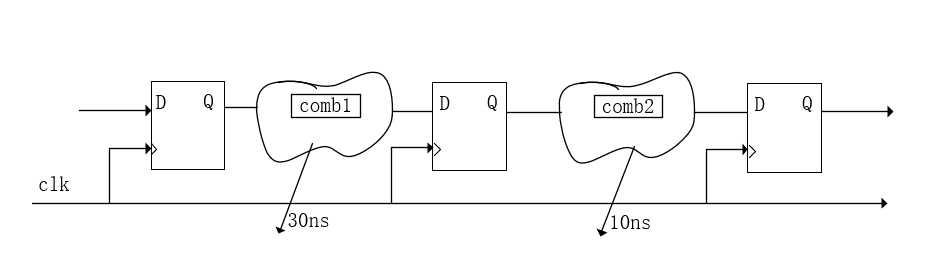

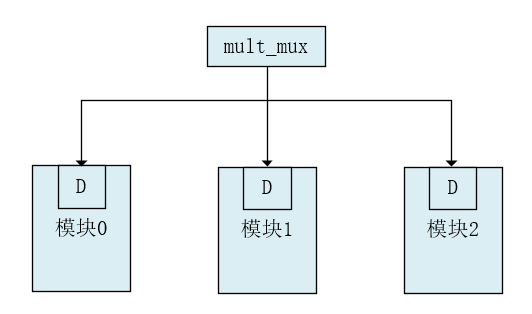

任何的數(shù)字電路都可以等效成組合邏輯加D觸發(fā)器打拍,兩個D觸發(fā)器之間的組合邏輯路徑?jīng)Q定了,系統(tǒng)的工作頻率,決定芯片的性能。所以為了提高芯片的工作頻率,使用流水線技術在組合邏輯中插入寄存器。  插入寄存器的位置需要慎重選擇,不同的位置數(shù)據(jù)的打拍所消耗的寄存器的數(shù)量也不同,比方說你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省則省。

插入寄存器的位置需要慎重選擇,不同的位置數(shù)據(jù)的打拍所消耗的寄存器的數(shù)量也不同,比方說你在位置a消耗25bit寄存器,位置b消耗20bit寄存器,能省則省。  前面插入寄存器的位置使得comb1的延遲為30ns,comb2的延遲為10ns,系統(tǒng)的最高工作頻率是由最長路徑?jīng)Q定的。也就是說你這個系統(tǒng)最高工作頻率的周期,不小于30ns,前面是插入pipeline,這個時候我們不改變時序,采用重定時技術,使得各個組合邏輯之間的延遲相當。 ?

前面插入寄存器的位置使得comb1的延遲為30ns,comb2的延遲為10ns,系統(tǒng)的最高工作頻率是由最長路徑?jīng)Q定的。也就是說你這個系統(tǒng)最高工作頻率的周期,不小于30ns,前面是插入pipeline,這個時候我們不改變時序,采用重定時技術,使得各個組合邏輯之間的延遲相當。 ?

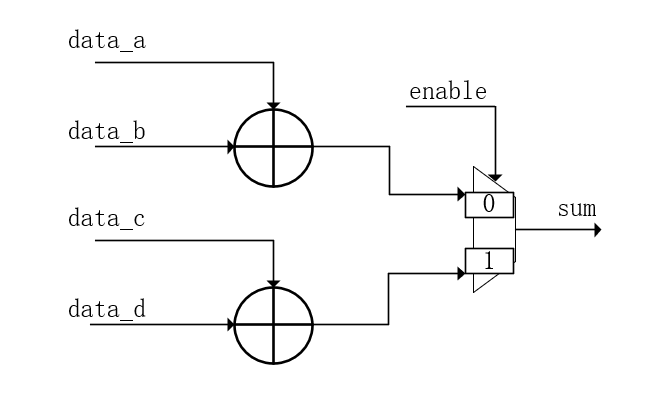

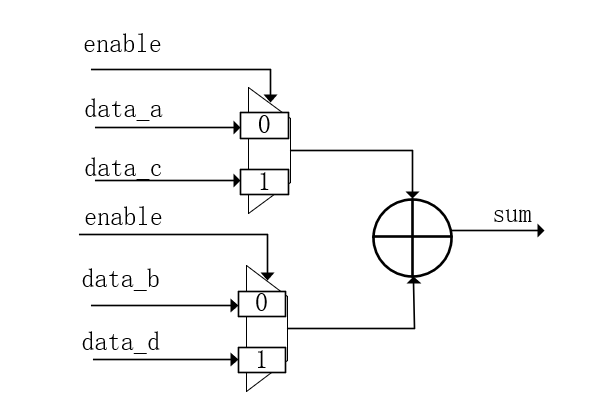

這里的加法器可以換成任何邏輯或模塊。

這里的加法器可以換成任何邏輯或模塊。 修改前

修改前  修改后 修改完后的寄存器省了很多,但是乘法器的輸出寄存器負載會變大,不過后端綜合時約束了max_fan_out工具會自動插buffer和復制寄存器,經(jīng)過實測還是會節(jié)省很多面積,把一些優(yōu)化工作可以交給工具去做,了解它,信任它,使用它。

修改后 修改完后的寄存器省了很多,但是乘法器的輸出寄存器負載會變大,不過后端綜合時約束了max_fan_out工具會自動插buffer和復制寄存器,經(jīng)過實測還是會節(jié)省很多面積,把一些優(yōu)化工作可以交給工具去做,了解它,信任它,使用它。 電子發(fā)燒友App

電子發(fā)燒友App

評論