檢查雙向晶閘管的好壞(方法之二)

利用整流二極管,能夠迅速判定雙向晶閘管究

2009-07-28 08:22:12 2836

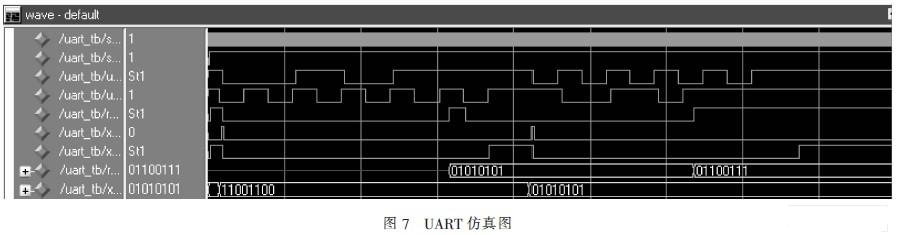

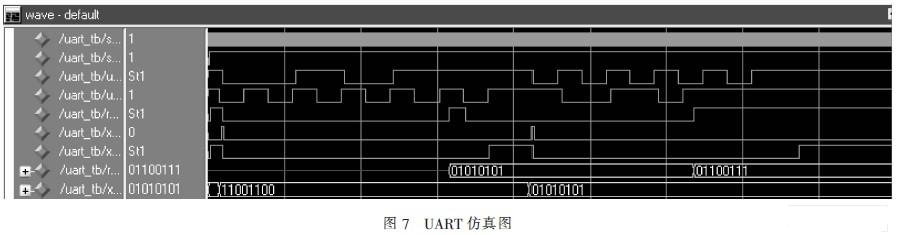

2836 1 UART原理

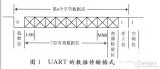

串行通信是指外部設備和計算機間使用一根數據線(另外需要地線,可能還需要控制線)進行數據傳輸的方式。數據在一根數據線上一位一位傳輸,每一位數

2010-08-02 09:37:50 2825

2825

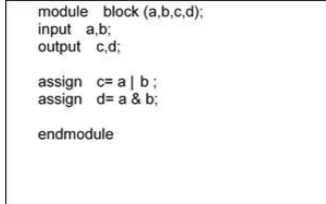

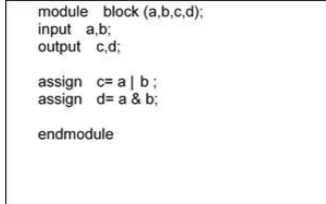

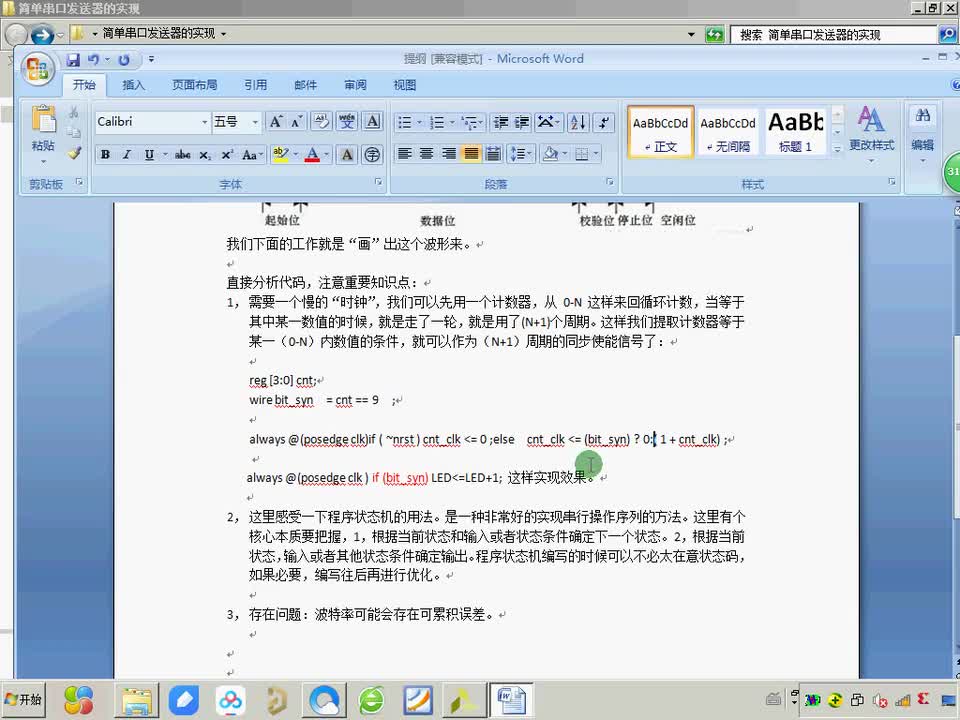

Verilog的基本設計單元是“模塊”(block)。一個模塊是由兩部分組成的,一部分描述接口,另一部分描述邏輯功能,即定義輸入是如何影響輸出的。

2019-06-26 15:30:40 13055

13055

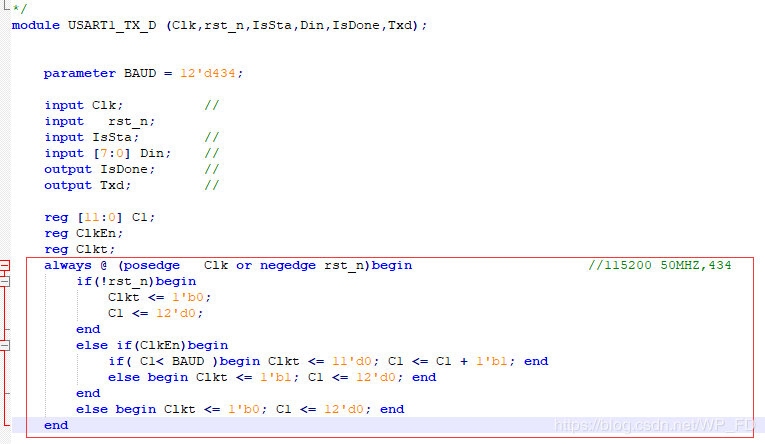

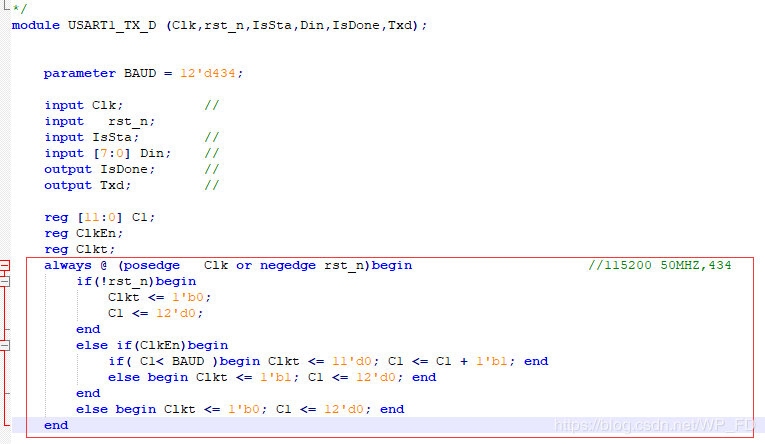

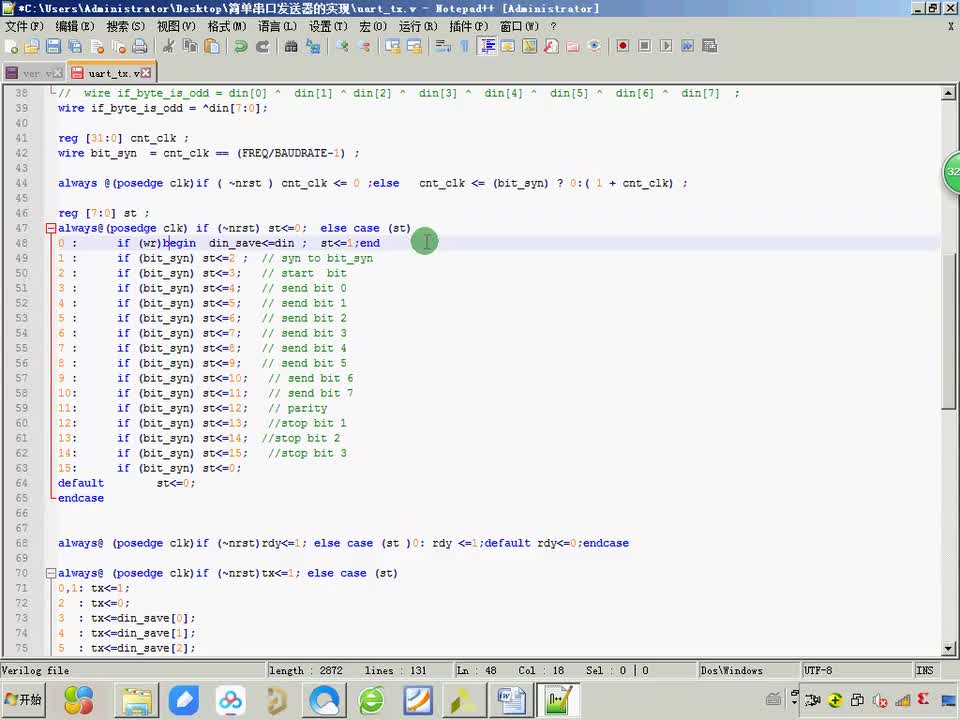

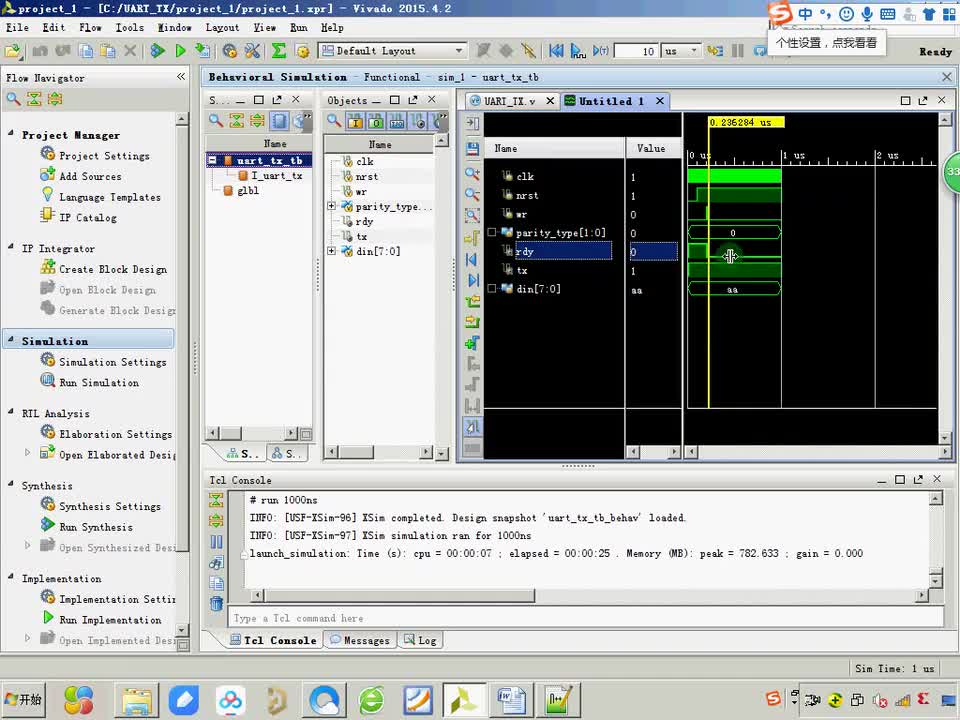

在 ZYNQ進階之路2 中我們講解了PL端PWM呼吸燈的設計,本節我們講解PL端實現串口UART的發送設計; 首先新建一個串口發送的工程,工程建立在ZYNQ進階之路1中已經講述,這里不再累述; 下面

2020-11-25 17:26:21 4349

4349

在做模塊劃分時,通常會出現這種情形,某個大的模塊中包含了一個或多個功能子模塊,verilog是通過模塊調用或稱為模塊實例化的方式來實現這些子模塊與高層模塊的連接的.

2025-05-03 10:29:00 1390

1390

特權同學的《FPGA/CPLD邊學邊練---快速入門Verilog/VHDL》中的UART串口收發實驗發送數據和接收的數據不一致。在每個有效數據的后面都會多兩個數據。比如發送的有效數據是:FF。則

2017-11-30 09:25:44

Verilog 和 VHDL。本應用說明 Verilog 在數字 UART(通用異步接收器和發送器)的設計和驗證中的使用。

UART 由兩個獨立的 HDL 模塊組成。一個模塊實現發送器,而另一個模塊實現接收器

2024-04-01 14:41:47

Verilog實現接收的數據進行發送。

2017-05-19 23:03:45

今天學習了UART的相關知識,完成了用上位機輸入字符串然后在虛擬終端上進行顯示。首先應該將設I|O口的功能設置為UART,具體有PINSEL來實現。然后是UART的初始化,主要要先是DLB=1,即另

2013-11-29 21:13:23

1.1 FPGA雙沿發送之Verilog HDL實現1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿發送之Verilog HDL實現;5)結束語。1.1.2 本節

2021-07-26 06:20:59

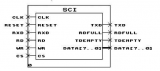

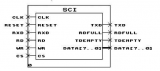

`UART 主要由 UART 內核、信號監測器、移位寄存器、波特率發生器、計數器、總線選擇器和奇偶校驗器總共 7 個模塊組成,如圖 5-5 所示。圖 5-5 UART 實現原理圖UART 各個模塊

2018-10-18 09:51:47

本帖最后由 mr.pengyongche 于 2013-4-30 03:27 編輯

dsp設計100問(之二)[url=www.7773.cc]

2011-10-30 22:10:12

UART 內核模塊是整個設計的核心,所以它也是整個設計中最為復雜的模塊。由于 UART 內核模塊的整體結構比較復雜,下面的內容將從模塊接口、狀態機設計和實現代碼 3 方面介紹UART 內核的實現方法

2018-10-24 09:58:36

如圖所示在uart中怎么用verilog實現輸出A轉換到a

2019-10-16 16:26:11

//;=================================================================*//; 模塊功能說明: UART Transmit

2014-07-08 23:08:28

串行通信的工作方式有哪些?如何實現Verilog串口發送及接收一個字節數據呢?

2021-11-11 06:48:39

怎么實現STM32 UART HAL數據發送?

2021-12-14 07:18:54

的按鈕,電話應用程序將數據通過藍牙發送到模塊,模塊將uart發送到目標。目標響應,模塊從uart接收數據并將數據發送回電話。當然可以。

2020-04-20 10:07:50

發燒友們好,我正在開始學習fpga的知識,現在尋求一個基于verilog的uart程序,要求是初始位一位,終止位一位,數據位8位,實現回環功能。大家能幫助一下我嗎?

2020-05-10 22:53:19

請問Verilog怎么實現UART/RS232/RS485收發自動校調功能,降低接收誤碼率?

2021-06-21 07:27:16

UART 4 UART參考設計,Xilinx提供Verilog代碼 uart verilog

THIS DESIGN IS PROVIDED TO YOU "AS IS". XILINX

2009-06-14 08:56:25 156

156 本文介紹了I2C總線規范,并根據該規范對I2C進行模塊化設計,用Verilog HDL 語言對每個模塊進行具體描述,并通過模塊之間的調用,基本實現了I2C的主機從機的發送和接收功能。

2009-06-15 10:44:03 144

144 This manual describes the Verilog portion of Synopsys FPGACompiler II / FPGA Express application

2009-07-23 10:01:29 79

79 文章介紹了一種采基于FPGA 實現UART電路的方法,并對系統結構進行了模塊化分解以適應自頂向下的設計方法。采用有限狀態機對接收器模塊和發送器模塊進行了設計,所有功能的

2009-08-15 09:27:55 46

46 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。關鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 24

24 本文設計了一種基于 FPGA 的UART 核,該核符合串行通信協議,具有模塊化、兼容性和可配置性,適合于SoC 應用。設計中使用Verilog HDL 硬件描述語言在Xilinx ISE 環境下進行設計、仿真,

2009-11-27 15:48:51 20

20 IO模擬UART實現

本應用用于擴展UART端口,在單片機自帶的UART口不夠用的情況下,使用GPIO和定時器實現模擬UART通信。可增加兩個模擬的UART模塊。

2010-03-26 09:20:40 69

69 文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實現UART異步串行通信的硬件接口電路及各部分硬件模塊,以及用硬件

2010-08-06 16:24:13 55

55 CAM350 技巧之二

1. 問:cam350v8.0 以上怎樣自定義快捷健?答:在菜單欄空白處,單擊鼠標右鍵,點customize 進入。選擇keybo

2007-01-25 12:02:36 3139

3139 摘 要 :UART是廣泛使用的串行數據通訊電路。本設計包含UART發送器、接收器和波特率發生器。設計應用EDA技術,基于FPGA/CPLD器件設計與實現UART。

2009-06-20 13:14:52 1267

1267

檢查晶閘管的觸發能力(方法之二)

對于大功率晶閘管,因其通態壓降較大,加之

2009-07-28 08:17:29 1052

1052 高速PCB設計指南之二

第一篇 高密度(HD)電路的設計

本文介紹,許多人把芯片規模的BGA封裝看作是由

2009-11-11 14:59:19 539

539 GPS應用基礎知識之二

1. GPS的設置 GPS拿到手,如果是新機器要定位,上次已經提

2010-02-08 10:53:57 642

642 階梯波發生器之二

此種發生器其構成不太復雜,并有較好的性能。它是以前述矩形脈沖發生器、鋸齒波發生器、遲滯比較器為基本單元電路,并配上二極管

2010-04-22 15:45:34 5342

5342

C8051F310設計的UART擴展實現

UART數據發送協議作為一種簡單的數據發送協議,被大量的使用在當前各種數字外設的數據傳輸上。但是現在的PC機存在無UART接口或接口較

2010-05-27 10:15:41 2971

2971

Name : uart // File Name?? : uart.v// Function??? : Simp

2010-06-05 12:12:03 6550

6550 在xo640上實現一個簡單的Uart,能夠解析串口數據,并在寄存器中存儲,用FIFO實現數據的傳遞。那么后期可以通過開發板上的串口經CPLD訪問各種數據。比如PC=CPLD=EEPROM等等,極大方便后期

2011-08-05 16:54:46 2181

2181 UART 是廣泛使用的串行數據通訊電路。本設計包含UART 發送器、接收器和波特率發生器。設計應用EDA 技術,基于FPGA/CPLD 器件設計與實現UART。

2011-12-17 00:15:00 59

59 數字系統設計:VERILOG實現 (第2版)

2015-11-30 10:21:33 0

0 STM32 UART 發送數據丟失最后一個字節

2015-12-04 15:10:46 0

0 verilog語言開發的串口模塊程序,測試可用。

2015-12-25 10:25:19 6

6 Proteus之矩陣式鍵盤的識別之二,很好的Proteus資料,快來下載不學習吧。

2016-04-18 16:42:32 0

0 Labview之動態窗口樣式之二,很好的Labview資料,快來下載學習吧。

2016-04-19 10:56:22 0

0 Labview之二維數組數據顯示,很好的Labview資料,快來下載學習吧。

2016-04-19 11:30:48 0

0 C#教程之二進制存取圖片,很好的C#資料,快來學習吧。

2016-04-20 15:27:47 9

9 C語言教程之二分查找,很好的C語言資料,快來學習吧。

2016-04-22 11:06:08 0

0 簡單的Verilog ,不是很全面,但是基本的還是有的,里面只有一些 基本的元器件。

2016-05-18 14:53:57 0

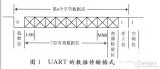

0 異步串行數據的一般格式是:起始位+數據位+停止位,其中起始位1位,8位數據位,奇校驗、偶校驗或無校驗位;停止位可以是1、2位,LSB first: 2.接收原理: 由于UART是異步傳輸,沒有傳輸

2017-02-09 09:41:11 1412

1412

NiosⅡ的UART設計與實現

2017-10-31 15:09:03 17

17 Verilog是描述復雜的硬件電路,設計人員總是將復雜的功能劃分為簡單的功能,模塊是提供每個簡單功能的基本結構。

2017-11-20 16:49:36 5885

5885

使用Verilog描述硬件的基本設計單元是模塊(module)。構建復雜的電子電路,主要是通過模塊的相互連接調用來實現的。模塊被包含在關鍵字module、endmodule之內。實際的電路元件。Verilog中的模塊類似C語言中的函數

2017-12-08 17:20:57 11274

11274 和UART優缺點的基礎,提出了一種基于FPGA采用硬件設計HCI-UART的實現方式。本設計在Quartus II 9.0集成設計環境下,采用硬件描述語言Verilog分模塊設計完成,設計經過Modelsim 6.4a仿真與驗證。

2017-12-11 13:22:51 12702

12702

STM32 UART_發送數據丟失最后一個字節

2018-04-10 11:23:41 3

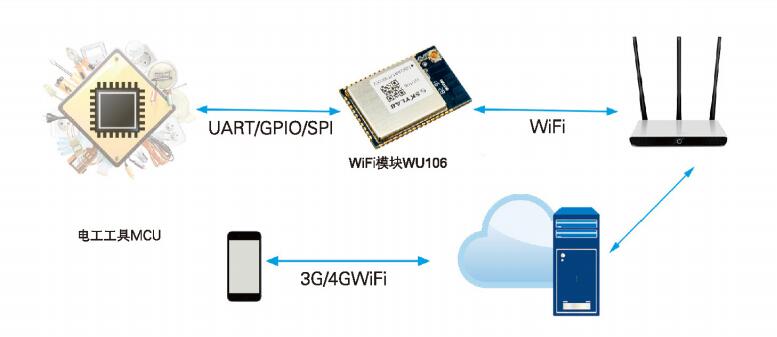

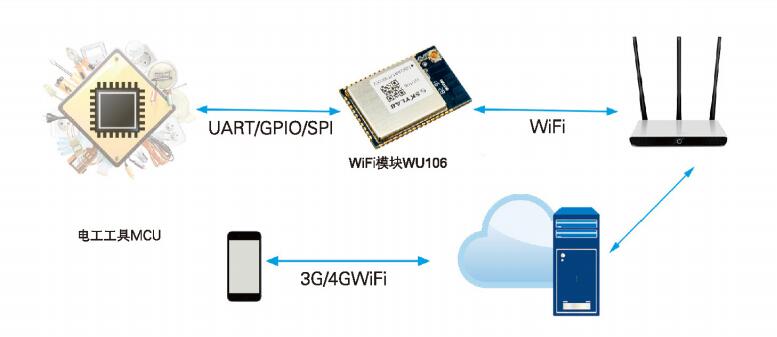

3 TCP/IP協議棧,能夠實現用戶串口或TTL電平數據到無線網絡之間的轉換。通過UART接口WiFi模塊,傳統的串口設備也能輕松接入無線網絡,適合于各類智能家居或智能硬件中,比如現在很多帶WiFi功能的電視

2018-07-30 11:24:50 3834

3834 串口透明數據傳輸模式,并且具有多模安全能力。內置TCP/IP協議棧和IEEE802.11協議棧,能夠實現用戶串口到無線網絡之間的轉換。 UART接口WiFi模塊 UART接口WiFi模塊是基于UART

2018-08-13 07:38:01 812

812 FPGA芯片卻沒有這個特點,所以使用FPGA作為處理器可以有兩個選擇,第一個選擇是使用UART芯片進行串并轉換,第二個選擇是在FPGA內部實現UART功能。

2019-10-18 07:54:00 3397

3397

本文檔的主要內容詳細介紹的是常用模塊的Verilog HDL設計詳細資料免費下載。

2018-10-16 11:12:54 20

20 字符發送的過程描述:在UART的發送過程中先將數據輸入到發送數據寄存器中(TDR)此時(TXE)被硬件置1,之后TDR寄存器將數據串行移入到發送移位寄存器中,將數據在TX端口發送,此時(TC)被硬件置1。發送與接收是逆過程。

2018-11-08 16:59:25 9886

9886 TCP/IP協議棧,能夠實現用戶串口或TTL電平數據到無線網絡之間的轉換。串口WiFi模塊工作方式分別是透傳模式和命令模式,透傳模式下,不管發送什么數據給模塊,模塊都不會進行處理(退出透傳模式的相關指令

2019-01-14 09:27:02 11633

11633

隨著物聯網智能家居應用的日漸豐富,越來越多的 WiFi 工程師開始更多的關注 UART 串口 WiFi 模塊,為讓新手工程師更快的將 UART 串口 WiFi 模塊應用于各類智能家居應用中,本篇 SKYLAB 君簡單為大家介紹 UART 串口 WiFi 模塊的工作原理及應用。

2019-01-08 08:00:00 24

24 接收控制模塊與發送控制模塊內部都有一個波特率時鐘產生模塊(BuadRate_set),用于將電路輸入時鐘(clk)進行分頻產生波特率時鐘,用于接收和發送數據控制。

2019-02-04 11:21:00 4580

4580

UART(UniversalAnynchrONousReceiverTransmitter,通用異步接收發送器)是廣泛應用的串行數據傳輸協議之一,其應用范圍遍及計算機外設、工控自動化等場合。雖然

2019-09-03 09:01:10 3076

3076

UART需要使用DMA發送嗎?

2020-03-07 16:57:28 7939

7939 HDL和VHDL的使用比率大概是80%和20%,在中國,大多數電子行業企業都采用Verilog。而模塊化的設計讓Verilog HDL語言具有思路清晰、邏輯關系明確、可讀性強等特點,模塊化的設計在 Verilog HDL語法設計中也成為主流。

2020-03-25 08:00:00 4

4 的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 15:51:05 12

12 的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 17:28:03 10

10 電子發燒友網站提供(電源反饋設計速成篇之二仿真篇)資料免費下載。

2020-11-11 11:41:32 23

23 本文主要介紹verilog基礎模塊,夯實基礎,對深入學習FPGA會有很大幫助。

2022-02-08 15:04:08 3315

3315

本教程解釋了如何在基于Verilog的設計中包含Altera的庫模塊,這些設計是使用Quartus R:II軟件實現的。

2021-01-22 15:34:12 4

4 1、 關于如何在VHDL模塊調用一個Verilog模塊 在VHDL模塊聲明一個要與調用的Verilog模塊相同名稱的元件(component),元件的名稱和端口模式應與Verilog模塊的名稱和輸入

2021-04-30 14:06:04 11930

11930

的是一個周期高電平,也可兩個)(無校驗位) 1、prescale是完成一個bit需要主時鐘計數的次數(其和主時鐘以及波特率之間的關系參考網上文章) 2、進入uart模塊的異步信號,最好使用提供的同步器同步 3、異步復位信號最好使用提供的同步器同步 4、波特率任

2021-05-27 18:05:00 3057

3057 基于FPGA的UART模塊設計與實現介紹說明。

2021-06-01 09:43:30 20

20 MCU-串口發送實現例程倉庫:https://gitee.com/ll0_0ll/MCU-UART1.串口發送寄存器為空中斷+RingBuff初始化一段內存空間作循環隊列發送數據時,先將數據放到循環

2021-10-28 12:21:01 10

10 UART通信的數據幀格式,波特率等,設置UART部件的工作模式等。二、設計要求實現用串口助手給開發板發送一個數字,開發板接收這個數字并加一后回送,并在此基礎上實現主機發送不同的數字控制開發板上的LED...

2021-11-03 20:06:01 13

13 功耗,并且集成了豐富的外設模塊,可以滿足工業和消費等多種應用。MSP430FR2311中的eUSCI_A0支持UART通訊,本文對此UART模塊的寄存器配置進行了詳細的分析和計算,以幫助工程師對此

2022-01-11 10:43:11 2853

2853 單片機pic24GPIO模擬uart發送我們經常遇到那種uart資源不夠的情況,這時就需要使用gpio來模擬uart資源。下面就是使用兩個定時器和兩個gpio來完成模擬。‘’’void

2021-11-16 13:51:02 5

5 TMC2225模塊UART調試TMC2225模塊UART調試硬件連線串口調測TMC2225模塊UART調試TMC2225可以通過UART配置相關參數。比較簡便的是通過PC的串口進行調測。硬件連線硬件

2021-12-04 16:36:09 52

52 收完成,則不再接收數據到指定緩沖區,返回超時標志(HAL_TIMEOUT)發送函數:HAL_UART_Transmit()接收函數:HAL_UART_Receive()CubeMX配置 :(二)中斷收發特點:利用中斷收發,不會占滿資源簡介:發送:把發送緩沖區指針指向要發送的

2021-12-24 18:44:54 5

5 stm32串口中斷通信,實現上位機控制開始發送和停止發送一、準備工作二、程序編寫三、效果展示一、準備工作本文所使用的硬件設備為野火的指南者開發板,利用商家提供的例程完成串口的中斷通信。所要實現的功能

2021-12-24 18:49:09 17

17 Uart比較簡單,所以僅對tx作比較詳細的注釋,但里面一些內容還是值得新手學習的

2022-07-01 17:08:50 2116

2116 有人使用STM32H743做產品開發, DMA 傳輸待發送的數據到 UART 發送寄存器做后續UART通信。在開啟D-Cache的情況下,發現UART沒法發送更新過的數據。

2022-11-23 09:02:19 2470

2470 UART協議由三根線組成,Tx,Rx,Gnd即發送、接收與地,不包含時鐘線,屬于全雙工異步串行通信協議。

2022-12-15 12:10:46 1177

1177 實現一個在ARM中通過APB總線連接的UART模塊(Universal Asynchronous Receiver/Transmitter),包括設計與驗證兩部分。

2023-06-05 11:48:38 3065

3065

和接收部分相反,UART發送數據部分是CPU將需要發送的數據寫到發送數據寄存器(TX_DATA),發送模塊進行數據的發送。

2023-06-05 15:59:52 3587

3587

電子發燒友網站提供《UART發送數據丟失最后一個字節.pdf》資料免費下載

2023-08-01 17:57:48 1

1 在芯片設計中,UART(Universal Asynchronous Receiver/Transmitter,通用異步接收/發送器)模塊是一個非常重要的外設模塊。

2023-10-09 14:10:59 2284

2284 2021年第三代半導體系列報告之二

2023-01-13 09:05:55 4

4 電子元器件行業汽車電子及半導體系列報告之二

2023-01-13 09:07:36 2

2 保持在高電壓電平。為了開始數據傳輸,發送 UART 將數據線從高電平拉到低電平(從 1 到 0)。接收 UART 在數據線上檢測到這種從高到低的變化,并開始讀取實際數據。通常,只有一個起始位。 數據位:數據位是從發送方傳輸到接收方的

2023-11-09 17:42:21 1509

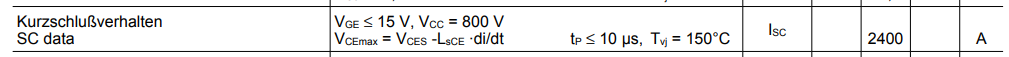

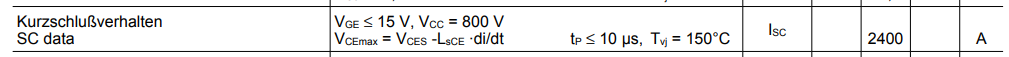

1509 功率半導體冷知識之二:IGBT短路時的損耗

2023-12-05 16:31:25 1499

1499

以用來實現與其他外設或者外部設備的數據交互。 然而,在一些情況下,用戶可能會遇到UART3無法發送數據的問題。在接下來的文章中,我們將深入探討這個問題,并提供一些解決方案。 首先,我們需要確定問題出現的具體情況。當UART3無法發送數據時,我們可以逐步排除可能的原因。首先,我們

2024-01-09 10:57:21 3043

3043 眾所周知,序列發送模塊可以不需要腳本代碼實現測試中特定控制報文序列的發送,該模塊多用于循環順序控制的測試案例中。序列發送模塊的常用場景,主要是針對一些新開發的產品需要通過該模塊來驗證產品功能等等

2024-02-19 14:00:11 1431

1431

Verilog是一種硬件描述語言(HDL),廣泛應用于數字電路設計和硬件驗證。在Verilog中,模塊是構建電路的基本單元,而模塊端口對應方式則用于描述模塊之間信號傳遞的方式。本文將介紹

2024-02-23 10:20:32 3071

3071

電子發燒友App

電子發燒友App

評論