microblaze和jtag-to-axi(jtag2axi)雖然也提供了訪問axi總線的能力,但是依賴于xilinx平臺。而uart-to-axi(uart2axi4)橋接器并不依賴任何平臺

2025-12-02 10:05:43 1842

1842

AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI

2020-12-04 12:22:44 9054

9054

構成的傳輸數據的通道, 一般由數據線、地址線、 控制線構成。?Xilinx從6系列的 FPGA 開始對 AXI 總線提供支持, 此時 AXI 已經發展到

2020-12-25 14:07:02 6724

6724

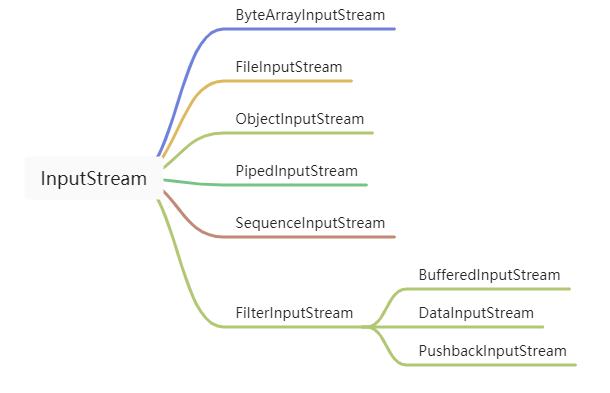

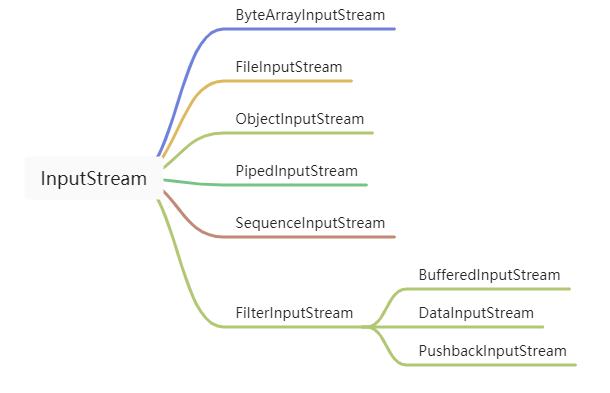

存到磁盤文件中或者從網絡上下載數據并加載到內存中,這個過程都是一種單向且有順序的數據傳輸,被稱之為流。 IO 就是 Input 輸入和 Output 輸出。輸入輸出以內存為中心的流向劃分的。傳輸數據到內存就是輸入流,從內存中輸出數據就是輸出流。 InputStream InputStre

2023-10-10 16:16:49 2346

2346

位流驗證,對于芯片研發是一個非常重要的測試手段,對于純軟件開發人員,最難理解的就是位流驗證。在FPGA芯片研發中,位流驗證是在做什么,在哪些階段需要做位流驗證,如何做?都是問題。

2025-04-25 09:42:51 2204

2204

大家好我在Zedboard上遇到了AXI Video DMA的問題。我正在嘗試在zedboard上進行簡單的vdma測試演示。這是我的步驟。我想發送自己的圖片(每像素32位)進行FPGA處理。我將自

2019-03-01 12:26:32

的 DDR 內存位置。該數據可以通過觀察 VivadoILA 來對比。輸出路徑需要 AXI Stream FIFO 斷言 Tready 信號。為此,我們需要使用 MicroBlaze 上運行的軟件配置

2022-11-04 11:03:18

的數據流標識符。xilinx封裝的ip中沒有此信號。 9.TDEST 用于提供路由信息,xilinx封裝的ip中沒有此信號。 10.TUSER AXI4協議留給用戶自定義的。xilinx封裝的ip中沒有

2021-01-08 16:52:32

嗨eveyone,我是這個論壇的新人。如果我弄錯了,我道歉。我正在嘗試使用AXI Stream協議傳輸數據包。這些數據包包括512 * 32位數據。使用1 kHz時鐘使能發送重新生成的數據包。我

2019-04-15 13:51:29

我正在使用AXI流FIFO將數據流式傳輸到Rx端,最終也將通過AXI總線從處理器讀回。當我嘗試讀取“base_address + 0x1C”時,系統掛起......以前有人遇到過這種情況嗎?在閱讀

2019-04-24 12:54:04

。 AXI4-Stream:(For high-speed streamingdata.)面向高速流數據傳輸;去掉了地址項,允許無限制的數據突發傳輸規模。 Stream的理解,可以想象一下

2022-10-14 15:31:40

,只不過是專門針對視頻、圖像等二維數據的。除了上面的還有一個AXI-CDMA IP核,這個是由PL完成的將數據從內存的一個位置搬移到另一個位置,無需CPU來插手。上面的IP是完成總線協議轉換,如果需要

2022-04-08 10:45:31

:視頻流數據位寬,一般由VDMA前端輸入自動確定;

Line Buffer Depth:S_AXIS_S2MM或S_AXIS_MM2S通道FIFO,當輸入輸出視頻幀率相當時,可以適當選擇較小深度,當

2025-10-28 06:14:54

是否可以將數據總線寬度配置為24位?我檢查了8, 16位和32位之間的差異,只改變了最后8位中的第七十九行(CyuU3pIPIBGPGIFIFBuxCONFIG)。我需要24位數據寬度和SPI為我的啟動從SPI閃存(固件)。如果我查看數據表中的PIN表,可以看到數據總線和SPI總線之間沒有交叉點。

2019-08-21 09:02:22

ipcore,VDMA和AXI4-視頻輸出。輸入視頻來自具有PAL輸出的視頻源,分辨率為576 * 720 @ 27MHz。從PAL相機捕獲并由解碼器接收的輸入視頻和來自16位數據的視頻在axi4流ipcore

2020-08-10 08:48:04

請問同時使用ADS1282的兩個差分通道進行采集,采用RDATA來通過命令讀取數據,那么是會同時輸出AIN1和AIN2的數據嗎?輸出順序是什么樣的呢?

另外,ADS1282的32位和24位輸出應該怎么設置呢?

謝謝。

2024-11-25 08:17:39

本章描述了AXI流協議,并給出了一些流類型的例子。

2023-08-08 07:54:37

位數據流處理器負責完成程序中所有有關數據的操作。位數據流處理器實際上就是一個序列發生器,它控制發送緩沖器、接收 FIFO 和 CAN 總線之間的數據流,同時它也執行錯誤檢測、仲裁、位填充和 CAN

2018-12-21 18:19:17

除數和商通道以及必要的時鐘和復位邏輯接口。每個AXI總線通道總是包括tdata tuser tlast 和握手信號tvalid tready,其中tuser為附加信息,tlast表示流模式下最后一個數據

2018-08-13 09:27:32

: xilinx.com:ip:axi_vdma:6.2 ERROR: [Common 17-39] 'create_bd_cell' failed due to earlier errors. while

2020-10-06 22:22:12

查看2015年11月發布的JTAG-to_AXI IP產品指南(PG174)(據我所知,最新版本)第19頁,它顯示了創建“具有8個32位數據”的寫AXI突發事務的示例。這不可能是正確的。這看起來只

2020-05-20 09:11:18

傳輸和亂序傳輸等,并且數據位寬也受到限制。由于不需要支持大多數高性能功能,AXI4-Lite所需的資源也較少。

AXI4-Stream:主要用于高速數據流數據傳輸。相比于其他總線協議

2025-06-02 23:05:19

與寫通道分離,從而具有并行處理的能力,大幅提高了總線傳輸帶寬和傳輸效率。AXI4總線可分為寫通道和讀通道。寫通道由寫地址通道、寫數據通道、寫響應通道組成。寫地址通道數據流從主機指向從機,主要傳遞地址

2025-05-17 10:27:56

大幅提高總線的數據吞吐量。AXI4 總線共有五個通道。其中,寫地址通道和寫數據通道數據流由主機指向從機,分別用于發送地址信息和數據信息。寫響應通道數據流由從機指向主機,用于反饋寫指令的完成狀態。

讀通道

2025-06-24 18:02:23

端口從PS DDR獲取3840x2160 @ 24Hz或@ 30Hz或@ 60Hz的視頻分辨率嗎?我們需要改變AXI VDMA的頻率嗎?對于1080p,我們使用150Mhz。謝謝,拉梅什以上來自于谷歌

2019-04-09 06:10:12

。Video in to AXI4-Stream IP核的輸入端口為視頻數據流,而OV7725攝像頭輸出的數據為行場同步信號控制的8位數據,這兩個端口不可以直接連接,需要先經過數據的轉換才能連接,因此本次實驗

2020-09-05 15:42:58

LCD接口時序的IP核。ZYNQ中提供了AXI4-Stream to Video Out IP核,可以將VDMA輸出的AXI4-Stream數據流轉換成視頻協議的數據流(包括并行數據、視頻同步信號等

2020-09-04 11:15:28

我使用VDMA,AXI互連器和DDR3進行了設計,以實現視頻幀緩沖。我遇到了一個問題,即在完成第一幀之后,VDMA卡在第二幀的開頭。我通過AXI lite讀取了VDMA的寄存器來檢查狀態:34h

2019-03-14 15:28:45

目前使用的axi pcie 采用legacy中斷。中斷產生后如何清楚標志位。。?文檔說相偏移0x138寫1就可以。可是為什么還是有中斷請求。???

2014-12-06 18:56:52

]).

現在有以下兩個問題:

1.兩個調制器都是輸出1位的數據流,那合并之后數據流是幾位的呢?

2.如果取所有可能的情況,Y[n]的輸出范圍就是-24~+25,這個又要怎么理解呢?

2025-02-05 09:10:08

想知道,如果我啟用AXI4Stream,我可以從AXI流端口(m_axis_tdata)獲取輸出采樣數據嗎?或者它仍然只能從DRP端口獲取。配置如下圖所示。問候穆罕默德·

2020-05-20 14:53:11

流經同軸電纜進入DVB碼流輸入模塊,轉換為8位并行輸出。核心控制模塊對并行數據進行緩存,并采用DMA方式傳輸給PCI總線,完成本地總線和PCI總線的可靠通信。DVB碼流輸入模塊本文選用ASI接口。ASI

2018-12-07 10:34:34

我必須為具有64位數據總線(ARM11,Cortex-R4)的ARM處理器編寫C程序,然后再執行一些仿真(Verilog)。到目前為止,我僅使用具有32位寬AHB數據總線(ARM9)的處理器。當我從

2022-09-30 10:50:58

嗨,我將使用axi tpg和axi vdma在zedboard上的ddr3中編寫幀數據,但我不知道,如何在vivado 2014.4和我的項目的sdk c應用程序代碼中設計vivado塊設計,請幫幫我是zedboard的新用戶。

2020-04-06 17:25:15

的AXI數據總線實際上是64位寬的呢!那么我如何在64位數據總線上進行讀/寫操作呢?謝謝,--Rudy以上來自于谷歌翻譯以下為原文Hi, In the SDK environment, if I am

2019-04-19 09:11:39

0->定標器 - > VDMA1 - > Axi至視頻輸出 - > HDMI輸出|| | | ||VTC0DDR3 DDR3 VTC1我想知道如何將兩個VDMA的同步鎖相模式和Axi的定時

2019-11-08 06:02:55

你好最近,我遇到了關于axi vdma fsync設置的問題。在我的項目中,我想使用一個AXI VDMA和AXI Pcore來加速Zedboard上的算法。我的數據流是DDR-> VDMA

2019-02-27 11:36:34

采用具有24位∑-△型A/D轉換器的系統級單片機MSC1210結合低成本的供電解決方案與CAN控制器SJA1000以及CAN總線收發器82C250,設計一種具有CAN總線接口的24位稱重數據采集系統,可應用于組合稱重設備、選別設備。

2021-04-14 06:15:25

axi接口分配的地址(e203中把axi當做外設來用,10041地址已經給定,剩下12位即4K地址空間留給axi),寫數據時候由于gpio定義1位寬,所以只需給0x1,如果gpio定義為32位寬,則會

2025-10-29 06:08:12

您好,我計劃將 X-Nucleo-cca02m2 板與 nucleo-f401re 一起用于音頻流。我找到了 en.x-cube-memsmic1_v5.5.0 示例代碼,其中發現 USB 音頻流的位分辨率為 16 位。但我的要求是 24 位分辨率。更改給定源代碼中的位分辨率是否有效?

2022-12-16 06:59:46

大家好。我目前正在使用GTH收發器實現更復雜的設計,這些收發器工作在2.8 GHz(5.6GB),我想知道我是否可以使用AXI4流以某種方式從收發器中提取輸入數據。有沒有辦法將數據寫入內存并

2019-05-05 13:14:10

● 基于特定地址進行的突發傳輸●通過獨立的讀和寫通道實現低成本直接內存訪問(DMA)●支持無序數據傳輸●提供多級寄存器鎖存的支持,實現更好的時序收斂 1.1 AXI版本介紹AXI協議是Xilinx從6系列

2019-05-06 16:55:32

,ar)共用一組信號的接口(arw,w,b,r)。關于總線互聯的設計凡是設計中用到Axi4總線的設計總離不開總線互聯。在Xilinx FPGA使用中,VIvado針對Axi4總線提供了豐富的IP,對于

2022-08-02 14:28:46

的發送引擎。#1。根據“表2-2:AXI4-流接口端口 - 發送”&在美國的其他相關部分,我看到這個AXI-4流接口沒有可用的地址線。我錯過了什么嗎?我想知道為什么在這個接口上沒有地址線的原因

2020-04-28 10:00:42

為了減少VDMA調用的數量,我需要一個更大的幀緩沖32.我想擴展它,但我沒有找到任何源文檔或驗證測試平臺。有人可以推薦一種方法嗎?我還考慮過使用AXI DMA。使用分辨率,我可以緩沖超過32幀,但仍然不夠。感謝您的支持!

2020-04-27 08:05:13

大家好,我開發了一個基于VDMA的系統,可以將圖像從DDR輸出到視頻輸出。流是1280x720 @ 60fps。然后,我復制VDMA有兩個視頻輸出流,它工作正常。需要擴展此系統以達到4個視頻流,我

2019-07-11 13:24:17

UCT62726 是一款專用于LED 顯示的16位 恒流驅動器 ,它擁有極低的輸入輸出壓差,單個通道90mA 的輸出電流時僅為300mV。恒流輸出電流可由一個外接電阻設定,可調范圍寬,可從4mA 到 90mA

2011-06-14 18:12:13 150

150 目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實現基于AXI總線的雙核嵌入式系統設計以及共享實現LED燈的時控.

2012-03-09 14:17:01 91

91 AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 12

12 Northwest Logic? 的 ?DMA? 內核現已支持 ?Vivado? 設計套件中的 ?IP? 集成器工具流。 IP? 集成器流可為客戶簡化將基于 ?AMBA? AXI4? 接口的 ?IP

2017-02-09 08:12:36 466

466

1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數據通道( W): write data

2018-01-05 08:13:47 11271

11271

了解如何使用Xilinx AXI驗證IP有效驗證和調試AXI接口。

該視頻回顧了使用的好處,以及如何使用示例設計進行模擬。

2018-11-20 06:38:00 4660

4660 XDMA是Xilinx封裝好的PCIE DMA傳輸IP,可以很方便的把PCIE總線上的數據傳輸事務映射到AXI總線上面,實現上位機直接對AXI總線進行讀寫而對PCIE本身TLP的組包和解包無感。

2020-12-28 10:17:23 4192

4192 通道 AXI-HP----AXI-Stream 的轉換,只不過這次是完全由 PL 控制的, PS 是完全被動的。 AXI-VDMA:實現從 PS 內存

2020-10-09 18:05:57 8938

8938

ZYNQ中DMA與AXI4總線 為什么在ZYNQ中DMA和AXI聯系這么密切?通過上面的介紹我們知道ZYNQ中基本是以AXI總線完成相關功能的: 圖4?34連接 PS 和 PL 的 AXI 互聯

2020-11-02 11:27:51 5032

5032

在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2022-02-08 11:44:02 18239

18239 在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2021-02-23 06:57:00 45

45 AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 7245

7245

位流檢測器(用于S/PDIF)下載產生碼

2021-04-12 20:42:14 0

0 位流檢測器(用于SPDIF)下載產生碼

2021-06-17 13:55:21 11

11 32位單片機,64位win7,其實就是在說它的地址總線是32位的,地址總線是64位的,也就是32位的單片機最大支持的內存(也就是尋址范圍)是4G,所以可以推出32位win7最多只能裝4G內存條。拍自《C語言內核深度解析》...

2021-11-18 19:51:04 5

5 差分形式并保持與輸出串行數據流的同步關系。LVDS 輸出有 2 個鏈路,每個鏈路包括 4 對 LVDS 差分數據輸出和 1 對并行的 LVDS 差分時鐘。 24 位 LVDS 發送器1 、產品概述本產品為一款多通道 LVDS 串行發送器,實現將 27 位 CMOS/TTL 信號(24 位 RGB

2021-11-30 21:06:05 15

15 ,那么在正常工作時,單片機將依次接收到24bit的數據。ADC的數據是24位的,但是沒有24位的數據類型。在單片機中,int類型的數據一般是32位的。所以需要一個函數來完成兩者的轉換。首先我...

2022-01-13 13:08:19 1

1 本文主要介紹關于AXI4-Stream Video 協議和AXI_VDMA的IP核相關內容。為后文完成使用帶有HDMI接口的顯示器構建圖像視頻顯示的測試工程做準備。

2022-07-03 16:11:05 10565

10565 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數據流。從字面意思去理解

2022-07-04 09:40:14 10523

10523 關于AXI總線協議的一些簡單知識,通過閱讀Xilinx的使用指導手冊(UG1037),結合正點原子的ZYNQ視頻進行梳理總結。

2022-07-15 09:16:29 3977

3977 AXI (高性能擴展總線接口,Advanced eXtensible Interface)是ARM AMBA 單片機總線系列中的一個協議,是計劃用于高性能、高主頻的系統設計的。AXI協議是被優化

2022-10-10 09:22:22 11273

11273 Xilinx vivado下通常的視頻流設計,都采用Vid In to axi4 stream --> VDMA write --> MM --> VDMA read -->

2022-10-11 14:26:03 7574

7574 具有 4 位輸出使能的 8 位總線開關-74CBTLV3244_Q100

2023-02-07 20:10:16 0

0 具有 4 位輸出使能的 8 位總線開關-74CBTLV3244

2023-02-07 20:10:30 0

0 如果 STRIDE 等于 HSIZE,那么 AXI VDMA IP 會在沒有任何跳轉的情況下讀取幀緩存。但是,由于輸入大小大于輸出大小,我們需要在地址之間跳轉以便能夠正確地對齊下一行的開頭。

2023-02-15 11:25:24 2041

2041 具有 5 位輸出使能功能的 10 位電平轉換總線開關-CBTD3384

2023-02-16 21:11:01 0

0 具有 5 位輸出使能的 10 位總線開關-74CBTLV3384

2023-02-16 21:24:07 0

0 具有 5 位輸出使能的 10 位總線開關-CBT3384

2023-02-20 20:08:42 0

0 24位總線開關-74CBTLV16211

2023-03-03 19:57:09 1

1 C++的輸入流和輸出流是C++標準庫中的兩個重要的流類,分別用于輸入和輸出數據。在本篇博客中,我們將詳細介紹C++的輸入流和輸出流,包括流的概念、流的類型、流的操作和流的應用等方面。

2023-04-30 17:58:00 2754

2754 從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 3091

3091

外部存儲器接口( EMIF )通信常用于FPGA和DSP之間的數據傳輸,即將FPGA作為DSP的外部SRAM、或者協同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 11848

11848

AXI-Stream,其中AXI-Lite和AXI-Full都是基于memory map的形式實現數據傳輸(即包括地址總線),而AXI-Stream是以數據流的形式傳輸,無地址。 ?其中

2023-10-31 15:37:08 2142

2142

電子發燒友網站提供《16位恒流LED接收器驅動器MBI5026數據手冊.pdf》資料免費下載

2024-03-11 17:08:57 3

3 電子發燒友網站提供《16位恒流LED接收驅動器MBI5026數據手冊.pdf》資料免費下載

2024-04-18 17:13:41 5

5 電子發燒友網站提供《具有可配置電壓轉換和三態輸出的 24位雙電源總線收發器數據表.pdf》資料免費下載

2024-05-13 10:34:41 0

0 電子發燒友網站提供《具有3態輸出的12位至24位多路復用總線交換機SN74ALVCH16271數據表.pdf》資料免費下載

2024-05-24 09:59:35 0

0 電子發燒友網站提供《具有3態輸出的12位至24位注冊總線交換機SN74ALVCH16270數據表.pdf》資料免費下載

2024-05-30 11:30:58 0

0 電子發燒友網站提供《具有3態輸出的12位至24位注冊總線交換機SN74ALVCH162268數據表.pdf》資料免費下載

2024-05-30 11:33:07 0

0 電子發燒友網站提供《具有可配置電壓轉換和三態輸出的 24 位雙電源總線收發器數據表.pdf》資料免費下載

2024-05-31 11:05:39 0

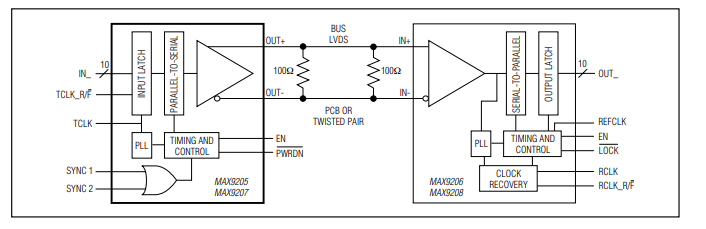

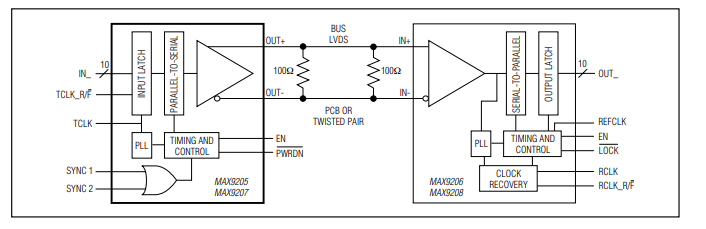

0 MAX9205/MAX9207串行器將10位寬度并行LVCMOS/LVTTL數據轉換為串行高速總線LVDS數據流。串行器與解串器配對使用,如MAX9206/MAX9208解串器,完成將串行輸出再轉換為10位寬度的并行數據。

2025-05-29 09:23:21 704

704

Semiconductors PCA9958 24位63mA電流LED驅動器(帶SPI).pdf 一、產品概述 PCA9958采用4線串行總線控制,具備24個恒流LED輸出通道。每個輸出通道都有獨立

2025-12-24 15:05:03 176

176

電子發燒友App

電子發燒友App

評論