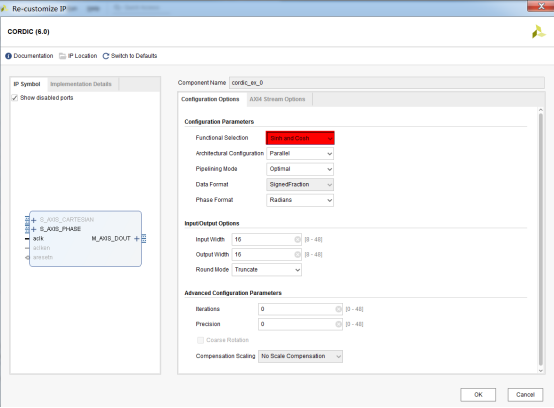

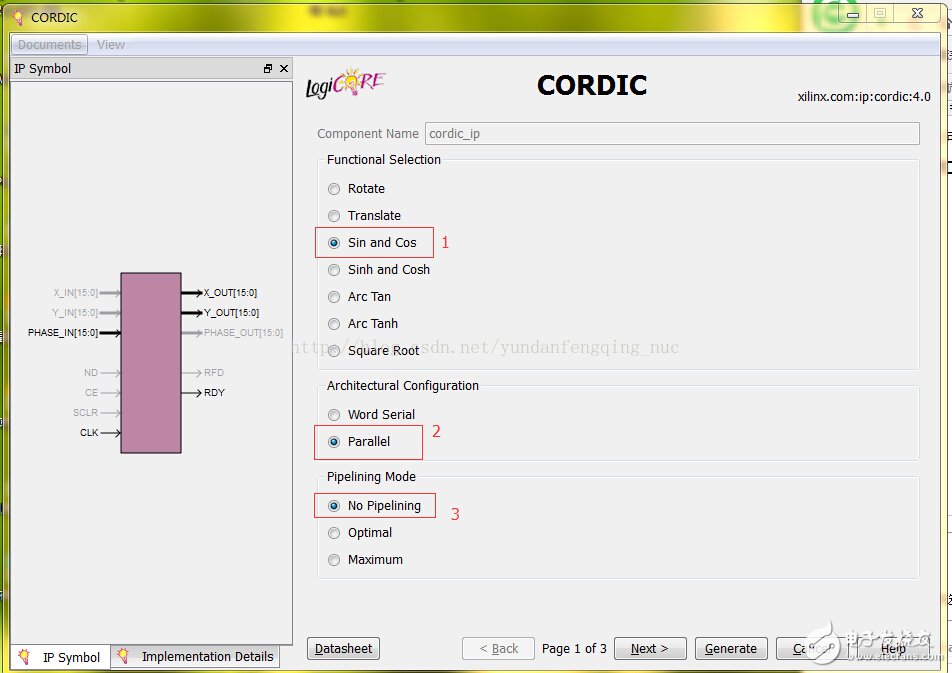

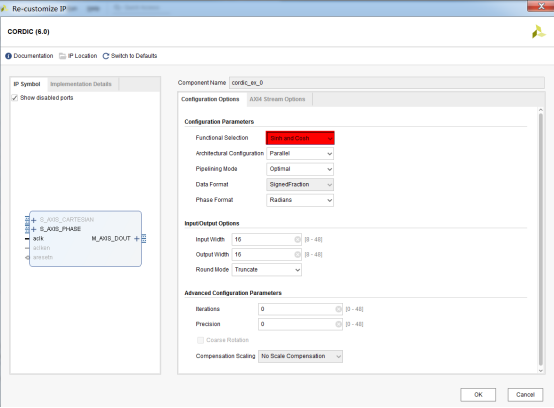

Architectural Configuration選擇為并行模式,具有單周期數據吞吐量和較大的硅面積。具有并行結構配置的CORDIC核使用移位相加子級數組并行實現這些移位相加操作。該并形電路的實現規模與(內部精度 * 迭代次數)成正比。

2025-05-03 18:16:00 1393

1393

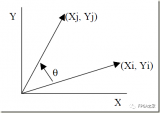

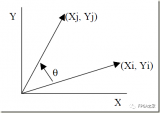

在進行坐標變換的時候,需要計算角度的正余弦值,而在FPGA中是不能直接進行求解的,需要采用其它的方式進行求解。

2025-06-19 09:54:37 1272

1272

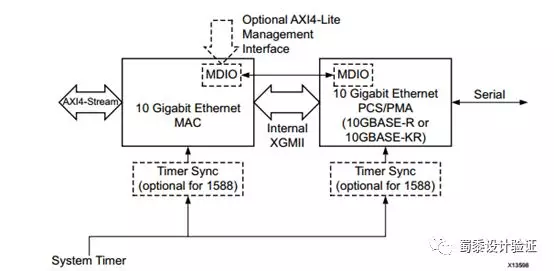

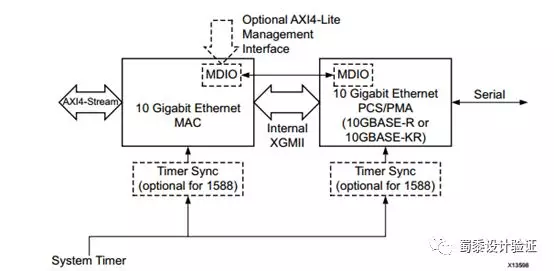

IP核描述 10 Giga Ethernet Sub System , 參考文檔PG157: https://www.xilinx.com/support/documentation

2020-12-30 12:56:30 5312

5312

IP CORE CORDIC ALGO EC/ECP CONF

2023-03-30 12:01:20

IP CORE CORDIC ALGO ECP3 CONF

2023-03-30 12:01:21

IP CORE CORDIC ALGO ECP2 CONF

2023-03-30 12:01:21

IP CORE CORDIC ALGO XP2 CONF

2023-03-30 12:01:21

使用Xilinx ISE 13.1的IP核CORDIC 4.0以下是提示信息:ERROR:coreutil - Exception caught when running XST synthesis

2013-09-01 20:09:00

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

`Xilinx FPGA入門連載73:波形發生器之IP核CORDIC(正弦波)配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-24 18:57:15

`Xilinx FPGA入門連載74:波形發生器之IP核CORDIC(正弦波)功能仿真特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1

2016-04-25 08:33:11

`Xilinx系列FPGA芯片IP核詳解(完整高清書簽版)`

2017-06-06 13:15:16

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

用的xilinx的FFT 9.1版本的ip核 , 仿真出來的結果和我MATLAB算出來的結果差的很多,也沒有倍數關系,scaled因數改了好幾次,沒有溢出,波形大致相同,但是數值上差的太多,已經弄了快兩周了,求做過這個的講講經驗。

2018-07-10 16:16:31

有沒有大神可以提供xilinx FPGA的FFT IP核的調用的verilog 的參考程序,最近在學習FFT的IP核的使用,但是仿真結果有問題,所以想找些參考設計,謝謝

2016-12-25 17:05:38

xilinx dds IP核輸出能不能改為無符號數,因為一般DA轉化器只能轉化正數

2015-09-29 18:30:23

用vivado2019.2建立工程,工程中調用cordic IP核進行atan求解,功能仿真時正常且滿足要求;綜合時正常;實現時報錯提示多重驅動。

如果經cordic計算后的輸出值不用于后續的操作

2023-06-06 17:17:37

AD9788正交變頻中如何調整NCO的正余弦波形?

2018-11-15 11:34:21

BRAM IP核包括哪幾種類型?Vivado中xilinx_BRAM IP核怎么使用?

2021-03-08 07:11:54

的情況時,總會遇到一些以前未曾接觸過的新內容,這些新內容會讓我們感到陌生和恐懼,不知道該如何下手。

那么今天以xilinx vivado 為例分享學習FPGA 新IP核的正確打開方式。

一、常規

2023-11-17 11:09:22

我有個需求,要輸出頻率可調的正玄波,因此想到了FPGA。但是兄弟以前沒試用過FPGA,初學。網上看到說可以用DDS或CORDIC算法來實現,但是小弟不知道這些算法對FPGA芯片有沒有要求,是否一般

2015-01-14 14:24:38

本次發布 Gowin CORDIC IP 參考設計及用戶指南。Gowin CORDIC IP 的用戶指南及參考設計可在高云官網下載,其中參考設計已配置一例特定參數,可用于仿真,實例化加插用戶設計后的總綜合,總布局布線。

2022-10-08 08:11:00

Gowin CORDIC IP用戶指南主要內容包括功能特征、端口描述、時序說明、配置調用、參考設計等。主要用于幫助用戶快速了解 Gowin CORDIC IP的產品特性、特點及使用方法。

2022-10-08 08:07:55

本帖最后由 elecfans跑堂 于 2015-9-7 13:54 編輯

一個項目里有IP核rom,想改其中的參數重新生成,結果打開失敗,然后我把它移除了,在項目里邊新添加不了,提示如下錯誤

2015-09-07 12:21:59

使用LabVIEW FPGA模塊中的CORDIC IP核,配置arctan(X/Y)算法,配置完成之后,IP核只有一個輸入。我參考網上VHDL CORDIC IP核,說是將XY合并了,高位X低位Y。不知道在LabVIEW中如何將兩個值X、Y合并成一個(X、Y均為定點數)。具體情況如下圖:

2019-09-10 20:07:07

最近在做FFT IP核,,走了好多彎路,LISENCE激活過了0034的IP核,通過修改LISENCE.DAT的方法。后來生成FFT的時候卡住,又嘗試了關閉quartus_map進程和重裝jre

2019-04-03 16:16:21

請問一下,我使用QuartusII 13.0 生成不了Rapid IO IP核,iP核已破解,其他諸如FIR、CIC、NCO等都能正常生成,到底是怎么回事呢?是Quartus版本的問題嗎?

2017-07-17 16:23:29

TCORDIC算法,由低延遲CORDIC算法和Taylor展開組成。Taylor展開計算作為CORDIC算法的補充,能夠結合CORDIC算法和Taylor展開方式來計算浮點正余弦函數,實現基于統一

2025-10-29 06:30:48

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

請教各位大神,小弟剛學FPGA,現在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

本帖最后由 liu1032042013 于 2017-5-3 22:16 編輯

使用quartus 12.1生成NCO IP 核失敗,進度條一直卡著不動,經百度得網友分享的方法,成功解決問題

2017-05-02 21:39:22

quartus 編譯顯示沒有ip核權限,生成的pof文件是time-limited,然后我在網上找了一個全ip權限的licsense文件,HOSTID也替換好了,可是編譯又顯示該lic文件沒有我要用

2017-01-16 20:16:27

除了在Xilinx官網上在哪里能下載到Xilinx IP Core 及license? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

為什么例化CORDIC IP核求復數模輸出為高阻 不知道是不是IP核參數設置錯誤?求指導

2013-09-27 11:04:34

各位大佬,xilinx ip核的各個參數的含義從哪里看啊

2021-05-30 10:37:27

大家好,這是一個UDP實現的16位定點CORDIC,用于計算給定角度的正弦和余弦。它在PSoC 3上被支持,并且可能(忽略警告)運行到33 MHz。我已經附上了一個演示項目與項目庫,所以嘗試運行它在

2019-05-24 10:03:12

如何使用這個用IP核生成的xdc文件?是否有任何標準的方法來使用它們擺脫crtical警告?非常感謝。以上來自于谷歌翻譯以下為原文When we create some IP cores

2019-03-26 12:29:31

一個DDS應用,我想使用Xilinx DDS IP內核生成任意波形,但我看到的是DDS只能生成正弦或余弦波形數據。你知道如何用其他數據替換正弦波形LUT嗎?如果可以修改該LUT,它可以生成任意波形

2019-02-12 08:07:21

我正在嘗試將Xilinx MIG IP Core從1.7版升級到1.9版。 Coregen UI左側有一個方便的“升級IP核”按鈕,但它顯示為灰色。我需要做什么才能進行IP核升級?我在Kintex

2019-11-04 09:26:19

的經驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現在有一些經驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

嗨,我想創建一個設計,我需要2Mhz clk,我想用16Mhz輸入時鐘的vivado套裝中的“時鐘向導”IP核生成它。根據Xilinx手冊(下面的鏈接),這可以通過CLKOUT4_CASCADE選項

2020-07-27 06:32:48

我想問一下蜂鳥內核怎么算正余弦函數

2023-08-12 07:52:32

請教大家誰用過 Xilinx PCIe IP 核啊?

2014-01-15 14:38:28

請教問題:我設計了一個ADAU1701的板子,時鐘是12.288MHZ,f0為48KHZ,我想生成一個40KHZ的正玄波,sine tone最大只能生成20KHZ的正玄波,不知道怎么才能生成40KHZ的正玄波。非常感謝

2018-08-09 06:37:57

Hii,我需要對Cordic i / p進行一些澄清。這里的問題是,由于ADC的輸出是標量,所以可以直接將它們傳遞給Cordic ip核心......?或者我們是否需要將i / p發送給Cordic

2019-02-27 11:57:52

IP核生成器生成ip后有兩個文件對我們比較有用,假設生成了一個asyn_fifo的核,則asyn_fifo.veo給出了例化該核方式(或者在Edit->Language Template->COREGEN中找到verilog/VHDL的例化方式)

2009-07-21 16:42:12 0

0

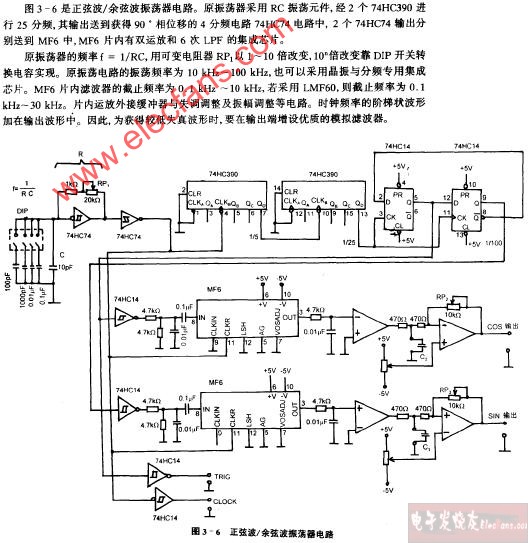

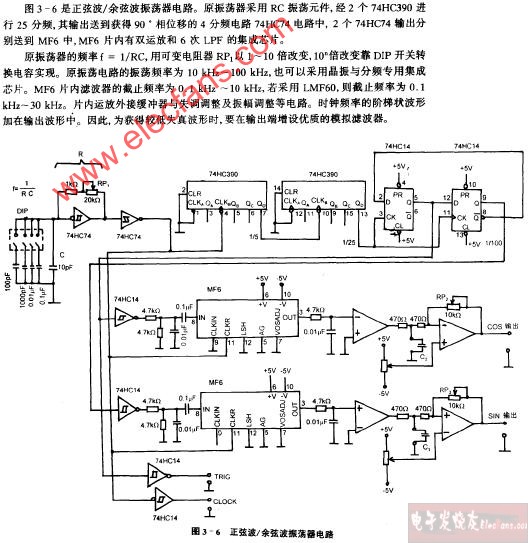

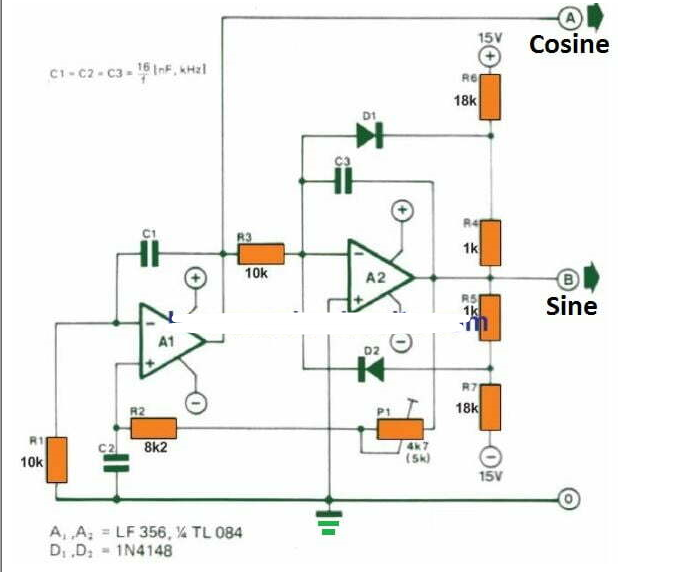

正弦波、余弦波振蕩器電路圖

2009-07-14 17:20:30 3067

3067

在研究CORDIC算法的數學基礎上,采用流水線的硬件結構實現了該算法,并在Altera公司的FPGA芯片上進行了驗證,使正余弦函數的計算達到了實時性、高精度的要求。

2011-12-16 14:30:00 33

33 IP核生成文件:(Xilinx/Altera 同) IP核生成器生成 ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則asyn_fifo.veo 給出了例化該核方式(或者在 Edit-》Language Template-》C

2012-08-15 15:57:09 35

35 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 Xilinx FPGA工程例子源碼:FFT變換的IP核的源代碼

2016-06-07 11:44:14 10

10 Xilinx FPGA工程例子源碼:PCI Express IP核應用參考設計

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB2.0 IP核源代碼

2016-06-07 14:13:43 35

35 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 Xilinx FPGA工程例子源碼:PCI總線IP核(華為的商用)

2016-06-07 14:54:57 32

32 Xilinx FPGA工程例子源碼:VGA顯示IP核(包括驅動)

2016-06-07 14:54:57 18

18 Xilinx FPGA工程例子源碼:攝像頭的硬件函數(IP核)

2016-06-07 15:07:45 14

14 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

Xilinx針對不同類型的調試IP核,提供了不同的核生成器。本節重點介紹Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro調試IP核ICON、ILA、VIO和ATC2及其屬性

2017-02-11 07:14:11 1113

1113

以ISE10.1軟件為例,其集成的CORDIC算法IP為V3.0版本,具體步驟如下:

2017-02-11 11:16:49 3358

3358

。 使用Xilinx內核生成器IP函數實現FPGA VI中不同的Xilinx內核生成器IP。LabVIEW使用IP集成節點實現上述函數。函數名稱和說明來自于Xilinx數據表。單擊Xilinx內核生成器配置對話框的數據表按鈕,了解IP內核的詳細信息。 選板隨終端變化且僅顯示FPGA設備系列支持的IP。

2017-11-18 05:54:05 1780

1780 本頁包含通過LabVIEW FPGA模塊可用的Xilinx CORE生成器IP的列表。LabVIEW通過Xilinx IP節點實現該IP。 下列IP名稱和說明來自于Xilinx數據表。LabVIEW

2017-11-18 05:55:51 5498

5498 LabVIEW使用IP集成節點方便的整合Xilinx內核生成IP至FPGA VI。按照下列步驟添加Xilinx內核生成器IP至FPGA VI。 1、在支持的FPGA終端下新建一個空白VI,并顯示VI

2017-11-18 05:56:22 2433

2433 DMA 控制器具有三條獨立的通道。每條通道在配置后都可以用于將數值在任何地址之間進行轉移。因此,一個數據表可以同時用于正弦波與余弦波,而兩條 DMA 通道只需存取數據表的不同部分,以便形成正弦與余弦輸出。

2018-04-30 22:40:00 2840

2840

在生成濾波器IP核之前需要產生抽頭系數,這個抽頭系數的階數是自己設定的,階數越高代表濾波器乘累加運算越多,但是階數大小的選擇要看是否滿足自己的設計要求(例如衰減db是否滿足要求)。同時,生成的濾波器

2018-07-06 10:00:00 3990

3990 本文檔的主要內容詳細介紹的是如何使用RAM IP生成可變頻的正弦波。

2020-03-26 08:00:00 19

19 DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 10426

10426

Xilinx LogiCORE IP塊內存生成器(BMG)內核是一種高級內存構造函數,它使用XilinxFPGAs中的嵌入式塊RAM資源生成區域和性能優化的內存。

2020-12-09 15:31:00 22

22 由于Verilog/Vhdl沒有計算exp指數函數的庫函數,所以在開發過程中可利用cordic IP核做exp函數即e^x值;但前提要保證輸入范圍在(-pi/4—pi/4)。在cordic核中e^x = sinh + cosh所以在配置cordic時點選sinh and cosh即可 如下圖

2022-07-25 16:51:14 5458

5458

由于Verilog/Vhdl沒有計算exp指數函數的庫函數,所以在開發過程中可利用cordic IP核做exp函數即e^x值;但前提要保證輸入范圍在(-pi/4—pi/4)。在cordic核中e^x = sinh + cosh所以在配置cordic時點選sinh and cosh即可 如下圖

2021-01-27 07:21:04 9

9 vivado提供了DDS IP核可以輸出正余弦波形,配置方法如下

2021-04-27 15:52:10 12327

12327

本次項目我們主要是為了講解DDS,所以我們使用了混頻這個小項目來講解。DDS自己手寫是比較簡單且靈活,但是Xilinx給我們提供了相應的IP核,那么這次我們將直接講解使用IP來產生不同頻率的正弦波。

2021-04-27 16:00:05 7980

7980

高精度正余弦函數的FPGA實現(打印)實現。

2021-04-27 14:14:31 5

5 本文以一個案例的形式來介紹lattice DDR3 IP核的生成及調用過程,同時介紹各個接口信號的功能作用

2022-03-16 14:14:19 2713

2713

電子發燒友網站提供《Gowin CORDIC IP用戶指南.pdf》資料免費下載

2022-09-15 14:35:31 1

1 整個仿真結構如圖1所示,由相位累加控制器和sin波形存儲器組成。仿真生成采樣率為44.1KHZ @1KHZ正玄波和余弦波(相位相差90度)。

2023-01-03 11:50:05 999

999 一步步來嘛,首先肯定要產生兩個頻率不同的余弦波cos(w0t),cos(wct)。立馬想到調用系統自帶的DDS IP核來實現嘛,這是最簡單的方法。我在網上還看到一個自己通過導coe文件來模擬DDS然后來產生余弦波的,這里就不說了。

2023-01-10 11:02:25 3903

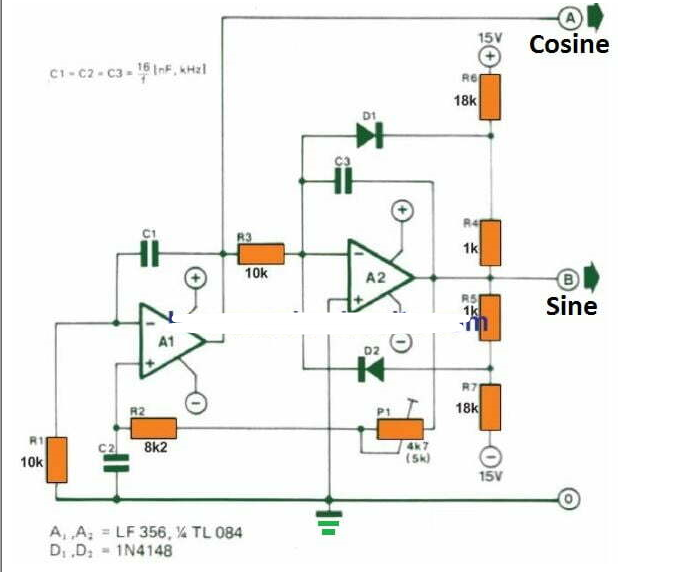

3903 下面討論的電路設計用于生成精密正弦和余弦波形,這些波形與其尺寸完全相同,但異相90°。

2023-05-17 18:14:12 3112

3112

筆者在校的科研任務,需要用FPGA搭建OFDM通信系統,而OFDM的核心即是IFFT和FFT運算,因此本文通過Xilinx FFT IP核的使用總結給大家開個頭,詳細內容可查看官方文檔PG109。

2023-07-10 10:43:18 2064

2064

DDS(Direct Digital Frequency Synthesizer) 直接數字頻率合成器,本文主要介紹如何調用Xilinx的DDS IP核生成某一頻率的Sin和Cos信號。

2023-07-24 11:23:29 8502

8502

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

CORDIC(Coordinate Rotation Digital Computer)算法即坐標旋轉數字計算方法,是J.D.Volder1于1959年首次提出,主要用于三角函數、雙曲線、指數、對數的計算。

2023-08-31 14:54:21 4356

4356

在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5640

5640

正余弦信號編碼器(Sin/Cos編碼器)是一種特殊的增量式編碼器,其核心特點是輸出?高質量的正弦波和余弦波模擬信號?。區別于傳統增量編碼器的數字方波輸出,正余弦編碼器通過模擬信號特性及其后續處理技術,實現了更高的分辨率和精度。

2025-07-29 11:40:38 1088

1088

電子發燒友App

電子發燒友App

評論