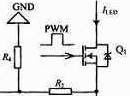

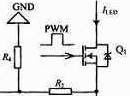

對LED串電流的取樣可用 LED串電流 反饋控制電路來實現。取樣輸出值與串電流的比例關系如圖中等式所示。

2011-11-10 16:27:32 3054

3054

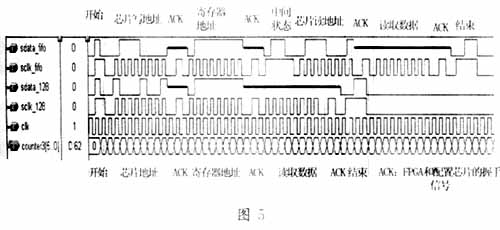

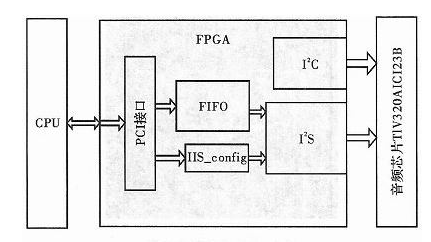

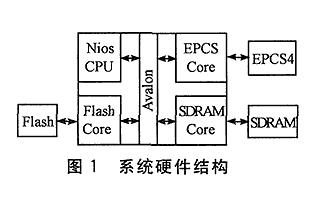

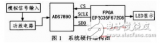

現場可編程門陣列(FPGA)作為專用集成電路(ASIC)領域的一種半定制電路,可以根據設計的需要靈活實現各種接口或者總線的輸出,在設備端的通信產品中已得到越來越廣泛的使用。##在設備端通信產品中,基于CPLD 的FPGA 從并加載框如圖2 所示。

2015-01-30 16:54:39 3717

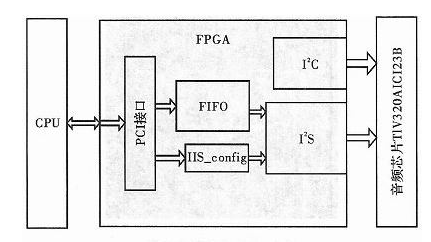

3717 如今大部分處理器并沒有集成I2S接口,但在嵌入式系統中CPU經常使用PCI總線與外圍設備進行交互,故需設計一種PCI—I2S 接口轉換電路,從而實現CPU與外圍音頻設備進行通信。目前實現此種接口轉換

2016-01-18 09:58:33 11956

11956

在FPGA中實現在應用編程(In Application Pro—gramming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數據,在被動串行(PS)模式下由

2020-07-22 16:41:32 2951

2951

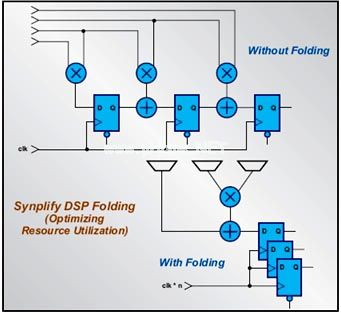

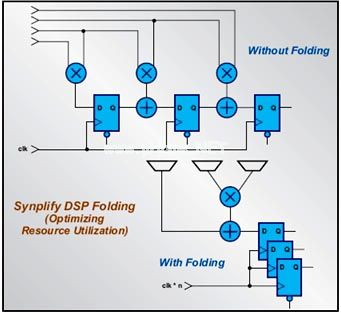

通用處理器(GPP)和專用集成電路(ASIC)之間提供了很好的折中方案。GPP 是完全可編程的,但在功率和性能方面效率較低;ASIC 可實現專用的功能,并展現出最佳的功率和性能特性,但需要極其昂貴

2020-11-08 10:36:00 5820

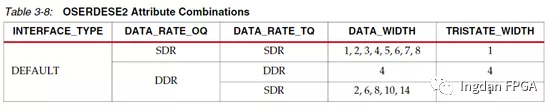

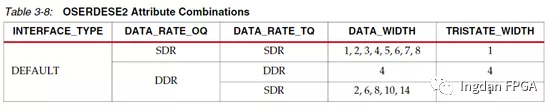

5820 在SelectIO簡介連載一中介紹了其架構,本章會繼續介紹如何使用其gearbox功能來實現不同的比率的串并轉換功能。7 Series FPGA中LVDS使用了ISERDESE2,SDR Rate可設為2,3,4,5,6,7,8。DDR Rate可設為4,6,8,10,14。

2022-08-02 08:03:21 4457

4457

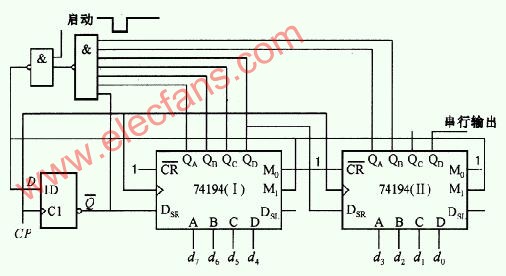

串并轉換與并串轉換是高速數據流處理的重要技巧之一。其實現方法多種多樣,根據數據的順序和數量的不同要求,可以選用移位寄存器、雙口RAM(Dual RAM)、SRAM、SDRAM或者FIFO 等實現。

2023-11-05 11:11:58 3871

3871

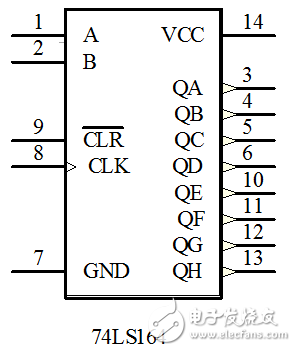

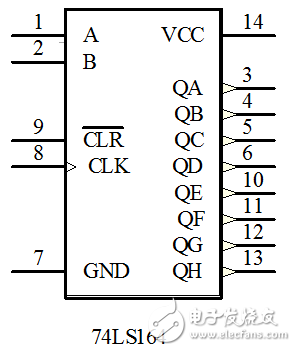

74LS165如何接可以實現并串轉換?如何接電路?

2015-03-06 17:35:28

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-10-23 07:16:35

(18)FPGA串/并轉換的思想1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA串/并轉換的思想5)結語1.2 FPGA簡介FPGA(Field

2022-02-23 07:38:28

各位大神是否能用400個以上I/O口的FPGA芯片,實現串并轉換,一個串行RS232輸入,將輸入的50個字節的數據轉換控制 50個8位并行輸出。具體大概應該怎么做

2015-07-08 17:19:33

現場可編程門陣列(FPGA)作為專用集成電路(ASIC)領域的一種半定制電路,可以根據設計的需要靈活實現各種接口或者總線的輸出,在設備端的通信產品中已得到越來越廣泛的使用。1 FPGA 常用配置方式

2019-07-12 07:00:09

現場可編程門陣列(FPGA)作為專用集成電路(ASIC)領域的一種半定制電路,可以根據設計的需要靈活實現各種接口或者總線的輸出,在設備端的通信產品中已得到越來越廣泛的使用。FPGA

2019-06-14 06:00:00

本帖最后由 jiuri1989 于 2012-2-10 11:42 編輯

本系列討論的四種常用FPGA/CPLD設計思想與技巧:乒乓操作、串并轉換、流水線操作、數據接口同步化,都是FPGA

2012-02-10 11:40:52

代碼的優劣的最終標準是:其描述并實現的硬件電路的性能,包括面積和速度兩個方面。評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件想HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在

2021-11-22 10:04:03

代碼的優劣的最終標準是:其描述并實現的硬件電路的性能,包括面積和速度兩個方面。評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件想HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在更大

2021-07-25 11:09:06

代碼的優劣的最終標準是:其描述并實現的硬件電路的性能,包括面積和速度兩個方面。評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件想HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在更大

2021-07-26 14:47:48

代碼的優劣的最終標準是:其描述并實現的硬件電路的性能,包括面積和速度兩個方面。評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件想HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在

2021-08-10 14:51:33

代碼的優劣的最終標準是:其描述并實現的硬件電路的性能,包括面積和速度兩個方面。評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件想HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在更大

2021-07-09 14:34:18

代碼的優劣的最終標準是:其描述并實現的硬件電路的性能,包括面積和速度兩個方面。評價一個設計的代碼水平較高,僅僅是說這個設計是由硬件想HDL代碼這種表現形式的轉換更加流暢、合理。而一個設計最終性能,在

2020-08-02 10:45:07

的VHDL程序,并對程序進行編譯并仿真,同時對程序的錯誤進行修改,直到完全通過編譯和仿真。3、要求對整體電路進行仿真,提供仿真波形圖,并分析結果用quartus來做,并行接口,電腦外接實驗箱求VHDL程序和FPGA芯片引腳分配(value)

2016-05-07 12:28:16

并串轉換74hc165{:9:}

2013-10-12 14:39:19

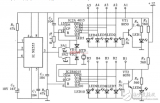

用兩塊單片機來實現按鍵控制燈亮,里面要用到并串轉換,求解

2015-05-14 15:09:56

自制FPGA數據采集板,通過txtfrm和txtclk采集輸出LVDS數據,怎么有錯,因為輸出時鐘是個假320MHz(INCLK=40MHz),每個點只有7個時鐘,差一個,到底按照什么時序采集才能正確實現串轉并?

2024-12-25 07:38:53

` 本帖最后由 jingzhaojun1986 于 2020-6-12 13:58 編輯

,這個庫多用于協議解析,主要實現了16進制字符串到正常字符串的顯示正常字符串轉換為16進制字符串`

2020-05-19 11:50:05

單元可以產生不同頻率的移位時鐘,從而測量精度可以根據具體需要進行適當調整。5結束語本基于 FPGA的時間數字轉換電路設計在占用較少芯片資源的前提下,實現了很高的測量精度,工作時數據轉換速度也在納秒級

2015-02-02 14:04:52

的實現方法我們用一個臺PC去解碼MP3,然后把信號發送到用1位數模轉換(DAC)設置成的FPGA傷。音頻輸出 我們需要一個DAC(數字-模擬轉換器)FPGA(數字)連接到揚聲器(模擬)。傳統的做法

2012-03-15 09:55:03

能準確的驅動芯片ADS8320,轉換為12位的二進制數。并實現串并轉換的基本功能。

2013-06-28 08:51:56

ADC,用戶可以直接通過JTAG下載調試接口讀取電壓和溫度值。但這些單元物理位置固定,靈活性受限,僅限于特定的應用。而采用FPGA的LVDS接收器來實現ADC,邏輯電路完全在FPGA內部實現,可重新配置,擴展性好,需要的外圍器件少,使FPGA能直接進行混合信號處理。

2019-07-04 07:08:30

基于CPLD/FPGA視頻顏色空間轉換電路的設計

2013-05-02 12:21:53

本文研究設計了一種基于高速隔離芯片的高速串行隔離型ADC。該數字隔離型ADC頻帶寬,延時小,穩定性高并且電路結構簡單。利用FPGA作為控制器,很好地實現了模數轉換和隔離傳輸。

2021-05-06 06:38:57

數/模轉換(D/A)電路,是數字系統中常用的電路之一,其主要作用是把數字信號轉換成模擬信號,通常是利用專用的數/模轉換(D/A)芯片來實現的。AD7543是Analog Device公司生產的的12

2019-08-01 06:19:16

基于ARM的嵌入式系統從串配置FPGA的實現

2021-03-03 06:16:30

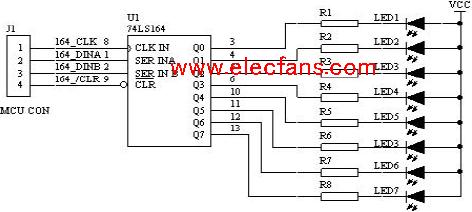

怎么用labview編程來實現74HC595電路(看附圖)串轉并輸出。如果我想讓0.0輸出為1,其他(0.1,0.2等)輸出為0。

2014-02-09 23:07:49

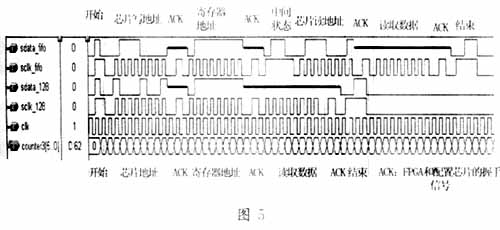

如何用EEPROM對大容量FPGA芯片數據實現串行加載?如何設計并-串轉換時序?

2021-04-29 07:13:12

現在有個課題需要要用FPGA或者DSP處理DICOM文件但是需要將DICOM轉換為數據流的形式才可在板子里操作并且是將DICOM的所有信息全部讀取包括圖像信息和病患信息等最后還需要將數據還原成

2015-04-16 23:27:25

每塊板子都可以進行并串和串并的轉換,但是在串并轉換時候,2塊板子的時鐘相位不同步,怎么解決?

2014-03-30 20:48:24

本文推導出一種適合在FPGA上實現從RGB到YCbCr。顏色空間變換的新算法,采用單片FPGA完成電路設計,利用FPGA內嵌DSP核實現乘法運算,提高了轉換算法的運行速度。

2021-04-29 06:57:57

,數字控制信號經過 DA轉換后輸出模擬控制電壓到后端控制電路,實現對七路溫度的閉環控制。 4.FPGA與外圍電路之間的通信接口 FPGA與外圍電路之間的通信接口主要包括與溫度傳感器,DSP,232接口

2020-08-19 09:29:48

比較流行的大規模集成電路Verilog開發語言。系統軟件功能實現了A/D控制模塊、語音編碼控制模塊、并串轉換控制模塊、串并轉換控制模塊、D/A控制模塊、語音解碼控制模塊和反向數據的收發控制模塊。

2019-07-17 07:43:08

LED先并后串和先串后并的區別,可能還要串電阻的這個兩個電路有啥區別呢,在什么情況下可以通用呢

2018-03-22 09:15:18

串并轉換 通過多通道串-并轉換器將多個同步串行數據流轉換為并行數據(源代碼)

** Filenames and Descriptions: **

2009-06-14 09:24:23 50

50 本文從DDS 基本原理出發,利用FPGA 來實現DDS 調頻信號的產生,重點介紹了其原理和電路設計,并給出了FPGA 設計的仿真和實驗,實驗結果表明該設計是行之有效的。直接數字頻率

2009-06-26 17:29:09 72

72 數模轉換器可以將一個二進制數字量轉換成與該數字量成正比的電壓值,可應用于可編程電壓源、波形發生器等。本文采用數字化技術,用FPGA 實現了一個簡單的一階8 位Σ-Δ 型DAC,

2009-08-21 11:18:34 27

27 高速串并轉換器的設計是FPGA 設計的一個重要方面,傳統設計方法由于采用FPGA 的內部邏輯資源來實現,從而限制了串并轉換的速度。該研究以網絡交換調度系統的FGPA 驗證平臺中多路高

2010-09-22 08:29:41 81

81 為了滿足某測控平臺的設計要求,設計并實現了基于FPGA的六通道HDLC并行通信系統。該系統以FPGA為核心,包括FPGA、DSP、485轉換接口等部分。給出了系統的電路設計、關鍵模塊及軟件

2010-09-30 16:49:30 43

43 新式降壓轉換設計并實現PWM升壓轉換器

Christian Schimpfl

2006-04-21 00:09:53 2727

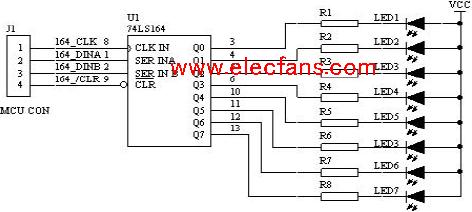

2727 串轉并的I/O 口實驗

一. 實驗目的熟悉并掌握串轉并的I/O 口擴展方法。二. 實驗設備及器件IBM PC 機 一臺DP-51PROC 單片機

2008-09-22 10:52:52 9746

9746

分析了視頻轉換中的關鍵技術,即,視頻掃描轉換和視頻圖像處理的基本原理,并給出了一種實際的實現方案,構建了以FPGA為控制核心的視頻轉換硬件系統。利用FPGA對整個系統進行

2009-05-05 20:37:16 1186

1186

基于AD7543和FPGA的數/模轉換電路設計

引 言

數/模轉換(D/A)電路,是數字系統中常用的電路之一,其主要作用是把數字信號轉換成模擬信

2009-11-17 09:57:19 2523

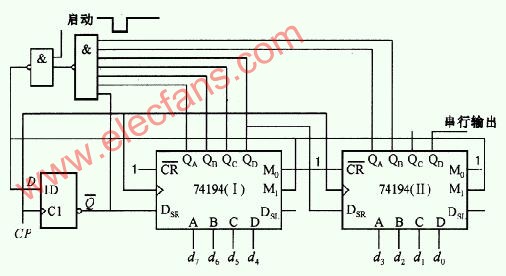

2523 8位串-并變換器電路

串-并變換器是把若干位串行二進制編碼變成并行二進制編碼的電路。并-串變換器則剛剛相反。

2010-01-12 14:09:07 3844

3844

8位并-串變換器

2010-01-12 14:10:04 1847

1847

用FPGA實現音頻采樣率的轉換

如今,即使低成本FPGA也能提供遠遠大于DSP的計算能力。目前的FPGA包含專用乘法器甚至DSP乘法/累加(MAC)模塊,能以550MHz以上的時鐘速度處理

2010-03-01 10:50:05 5021

5021

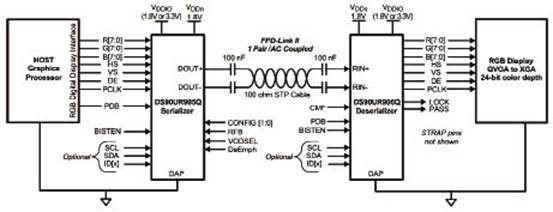

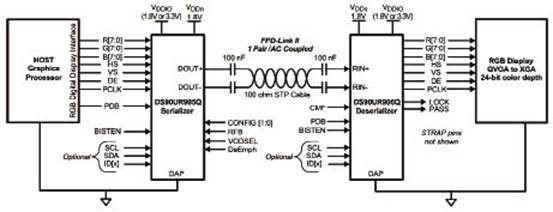

基于DS90UR905Q/906Q設計的24位FPD串并-并串轉換方案

NS公司的DS90UR905Q/906Q芯片組是5MHz-65MHz24位彩色FPD-LinkII串行化器和串并轉換器,能把并行RGB視頻接口

2010-05-13 16:49:50 2784

2784

摘要:為了實現高速HDLC通訊協議,設計了DSP+FPGA結構的485通訊接口,接口包括DSP、FPGA、485轉換等硬件電路,以及DSP與FPGA之間的數據交換程序和FPGA內部狀態機;其中DSP用于實現數據控制,FPGA用于實現HDLC通訊協議,DSP與FPGA之間采用XINTF方式,通過雙FI

2011-02-25 17:24:34 98

98 利用FPGA控制模塊,設計了OLED真彩色動態圖像驅動控制電路。介紹采用FPGA實現OLED外圍控制電路和256級灰度的方法,并分析電路中模塊的作用及整個電路的工作過程。

2012-05-24 15:32:01 43

43 為實現某專用接口裝置的接口功能檢測,文中詳細地介紹了一種34位串行碼的編碼方式,并基于FPGA芯片設計了該類型編碼的接收、發送電路。重點分析了電路各模塊的設計思路。電路采

2012-06-18 12:37:09 41

41 6合1串口轉換器電路,包括USB232,485等常用接口,使用方便

2015-11-09 18:04:22 34

34 基于FPGA的串并集合排序在雷達系統中的應用

2016-01-04 14:59:05 0

0 基于FPGA的光電系統同步自適應電路設計與實現

2016-01-04 17:03:55 11

11 并串轉換和串并轉換,有興趣的同學可以下載學習

2016-04-27 16:18:12 63

63 在雷達設計中,需要對接收到的信號首先進行模數轉換,其轉換速度和準確性直接決定了之后FFT等運算的準確性,最終影響雷達測量精度。介紹了一種基于FPGA,利用芯片ADS7890實現一種快速14位串

2016-09-01 15:44:10 0

0 基于并串結合機制的數據競爭消除系統設計與實現_沙晗

2017-01-07 18:39:17 0

0 在雷達設計中,需要對接收到的信號首先進行模數轉換,其轉換速度和準確性直接決定了之后FFT等運算的準確性,最終影響雷達測量精度。介紹了一種基于FPGA,利用芯片ADS7890實現一種快速14位串

2017-05-17 10:56:06 12655

12655

和底層工具Planahead實現高速串并轉換中數據建立時間和保持時間的要求,實現并行數據的正確輸出。最后通過功能測試和時序測試,驗證了設計的正確性。此方法可適用于高端和低端FPGA,提高了系統設計的靈活性,降低了系統的成本。

2017-11-17 12:27:01 7352

7352

塊的連接方式。編譯VI時編譯工具將FPGA VI轉換為FPGA電路。 注: 本主題包含底層FPGA的實現概述。理解上述概念并非為入門LabVIEW FPGA模塊的必需要求,但對于用戶創建更為有效的FPGA VI可能有所幫助。 下圖為邏輯塊、I/O塊和FPGA上可編程連線間的關系示意圖。

2017-11-18 05:57:01 1138

1138

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2018-04-26 11:53:00 1765

1765

/A、A/D芯片取代,有利于系統溫度穩定性的提到。FPGA內的數字邏輯實現了磁通門信號解算、激勵正弦信號發生、D/A、A/D輸入/輸出串并轉換的功能,首先用硬件描述語言(HDL)設計并仿真,然后下載、配置到FPGA中,調試完成后進行實驗,通過實時

2018-01-19 22:24:56 2185

2185 本文主要介紹了74ls164與單片機的串并轉換(串轉并\串進并出)。選用89C51單片機最小應用系統模塊,用八位數據線連接74LS164的并行輸出JD5G與十六位邏輯電平顯示模塊JD2I,將

2018-05-08 15:02:36 33234

33234

本文主要介紹了cd4015應用電路圖大全(電子開關/閃爍燈/串并數據轉換電路)。由CD4015組成的LED動感閃爍燈電路。主要采用一只雙四位串入/并出移位寄存器CD4015組成。該電路由移位寄存器

2018-05-10 10:33:39 19612

19612

FPGA 的配置數據通常存放在系統中的存儲器件中,上電后控制器讀取存儲器中的bit 文件并加載到FPGA 中,配置方式有JTAG、從并、從串、主從4 種,不同廠家叫法不同,但實現方式基本都是一樣的。

2018-10-30 08:58:00 9336

9336

FPGA芯片卻沒有這個特點,所以使用FPGA作為處理器可以有兩個選擇,第一個選擇是使用UART芯片進行串并轉換,第二個選擇是在FPGA內部實現UART功能。

2019-10-18 07:54:00 3397

3397

介紹了一種用FPGA實現對高速A/D轉換芯片的控制電路,討論了這一控制電路設計思想,提出了更好地解決高速A/D采樣與較慢速的單片機數據處理間矛盾的鏈接方法。

2018-09-21 17:00:29 27

27 介紹了采用CPLD和Flash器件對FPGA 實現快速并行配置,并給出了具體的硬件電路設計和關鍵模塊的內部編程思路。

2018-10-24 15:15:49 9

9 本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:08:00 3476

3476

本文檔的主要內容詳細介紹的是單片機串并轉換實驗的仿真電路圖和程序合集免費下載。

2020-05-15 17:08:00 11

11 應用能夠有更高的性能,您需要熟悉如下介紹的硬件。另外,將會介紹編譯優化選項,有助于將您的 OpenCL 應用更好的實現 RTL 的轉換和映射,并部署到 FPGA 上執行。

2020-07-16 17:58:28 7215

7215

本文檔的做作業內容詳細介紹的是八位串行和并行轉換電路的仿真電路圖免費下載。

2020-07-17 16:31:18 24

24 利用日本夏普公司的TFT-LCD模塊LQ080V3DG01,設計并制作了由可編程邏輯門陣列(FPGA)控制驅動的顯示系統。根據LQ080V3DG01的接口方式,用FPGA設計了液晶的驅動時序電路。用

2020-08-03 17:58:57 35

35 利用FPGA處理數據量大、處理速度快,結合CMOS圖像傳感器MT9M001和BayerCFA格式圖像的特點,設計一種基于FPGA的圖像數據轉換處理系統,提出用硬件實現Bayer格式到RGB格式轉換

2021-01-25 16:04:13 6

6 本文檔的主要內容詳細介紹的是使用單片機實現并串轉換器74HC165應用的仿真電路圖免費下載。

2021-03-04 17:08:32 24

24 本文檔的主要內容詳細介紹的是使用單片機實現串轉并數字芯片測試的C語言實例免費下載。

2021-03-29 11:48:26 3

3 雙鋰電串放并充電路圖下載

2021-12-30 09:17:34 8

8 (18)FPGA串/并轉換的思想1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA串/并轉換的思想5)結語1.2 FPGA簡介FPGA(Field

2021-12-29 19:40:56 2

2 同編程語言將字符串轉換為日期類型。 正文: 一、Python中的字符串轉日期轉換 在Python中,使用datetime模塊可以方便地將字符串轉換為日期類型。具體的方法是首先導入datetime模塊,然后使用datetime.strptime()方法指定日期字符串的格式,并

2023-11-17 16:27:28 11284

11284 在LabVIEW中,將字符串轉換為16進制字符串是一個常見的需求,尤其是在處理數據通信和硬件接口時。LabVIEW提供了多種方法來實現這一轉換,包括使用內置函數、編寫VI(Virtual

2024-09-04 15:54:44 7534

7534

電子發燒友App

電子發燒友App

評論