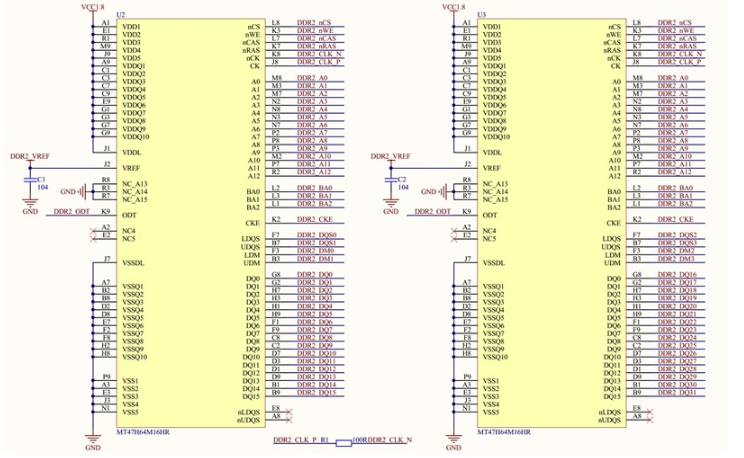

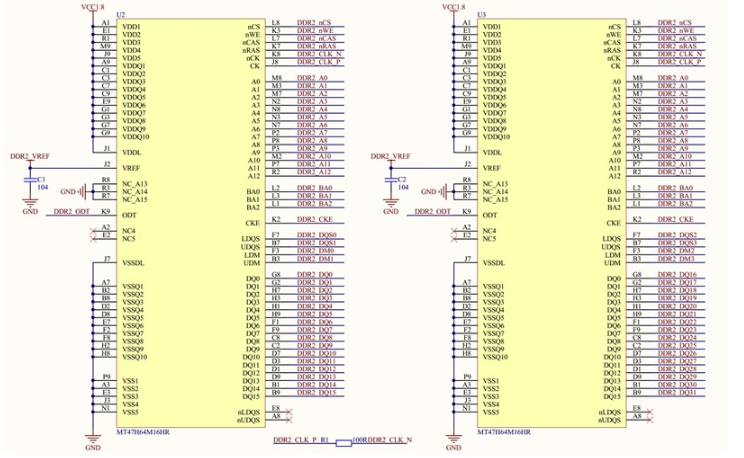

每片DDR2存儲(chǔ)器的容量為1Gb,兩片DDR2芯片組合,得到總?cè)萘繛?b class="flag-6" style="color: red">2Gb。單DDR2存儲(chǔ)器為16bit,兩片存儲(chǔ)器共用控制線和地址線,數(shù)據(jù)線并列,即組成了32位的2Gb存儲(chǔ)模組。

2020-08-21 15:09:00 7428

7428

本文首先列出了DDR2布線中面臨的困難,接著系統(tǒng)的講述了DDR2電路板設(shè)計(jì)的具體方法,最后給出個(gè)人對(duì)本次電路設(shè)計(jì)的一些思考。

2020-11-20 10:28:35 8529

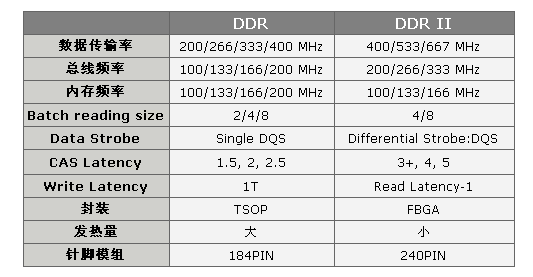

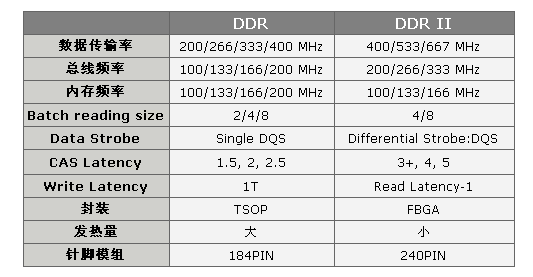

8529 DDR內(nèi)存1代已經(jīng)淡出市場(chǎng),直接學(xué)習(xí)DDR3 SDRAM感覺(jué)有點(diǎn)跳躍;如下是DDR1、DDR2以及DDR3之間的對(duì)比。

2023-04-04 17:08:47 5108

5108

從上表可以看出,在同等核心頻率下,DDR2的實(shí)際工作頻率是DDR的兩倍。這得益于DDR2內(nèi)存擁有兩倍于標(biāo)準(zhǔn)DDR內(nèi)存的4BIT預(yù)讀取能力。

2019-08-08 07:11:44

本次設(shè)計(jì)中CPU的封裝為BGA844-SOC-Y,DDR2的封裝為FBGA84,DDR2的控制總線采用星形連接,使用的PCB軟件為AltiumDesigner10

2019-07-30 06:29:28

DDR2設(shè)計(jì)原理 DDR2 designBasic knowledge? Source Sync Bus Analysis? On-Die Terminations (ODT)? Slew Rate

2009-11-19 09:59:04

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

最近在做ddr2方面的東西,需要仿真ddr2,可是一直沒(méi)有頭緒。xx_example_top_tb仿真不知道是對(duì)是錯(cuò),網(wǎng)上說(shuō)的外掛美光ddr2 模型的仿真方法,沒(méi)有具體講解。哪位大蝦能夠指點(diǎn)一二哇,不甚感激!

2016-06-29 15:50:28

實(shí)現(xiàn)特權(quán)同學(xué)的例程 特權(quán)FPGA VIP視頻圖像開(kāi)發(fā)套件例程詳解2——DDR2控制器讀寫(xiě)測(cè)試 時(shí),進(jìn)行IP核配置時(shí),進(jìn)入下一步配置參數(shù)時(shí),變成黑屏重裝軟件也不行

2018-01-24 08:23:17

在DDR2 MIG的使用時(shí),想把DDR2封裝成一個(gè)FIFO使用,但是有些問(wèn)題不是太明白。在MIG的User Interface接口中,提供給控制器的數(shù)據(jù)是上升沿和下降沿的拼接,一個(gè)周期提供兩個(gè)數(shù)據(jù)到

2015-03-29 18:41:43

本文和設(shè)計(jì)代碼由FPGA愛(ài)好者小梅哥編寫(xiě),未經(jīng)作者許可,本文僅允許網(wǎng)絡(luò)論壇復(fù)制轉(zhuǎn)載,且轉(zhuǎn)載時(shí)請(qǐng)標(biāo)明原作者。Altera DDR2控制器使用IP的方式實(shí)現(xiàn),一般很少自己寫(xiě)控制器代碼。ddr

2020-02-25 18:33:00

、DDR2與DDR3內(nèi)存的特性區(qū)別: 1、邏輯Bank數(shù)量 DDR2 SDRAM中有4Bank和8Bank的設(shè)計(jì),目的就是為了應(yīng)對(duì)未來(lái)大容量芯片的需求。而DDR3很可能將從2Gb容量起步,因此起始

2011-12-13 11:29:47

`例說(shuō)FPGA連載41:DDR控制器集成與讀寫(xiě)測(cè)試之DDR2 IP核接口描述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 如圖

2016-10-27 16:36:58

最近在設(shè)計(jì)一個(gè)需要連接DDR2 SDRAM的FPGA小系統(tǒng),由于是第一次在使用SDRAM,在硬件連接時(shí)就遇到一個(gè)很糾結(jié)的問(wèn)題——引腳的連接。看了幾種參考設(shè)計(jì),發(fā)現(xiàn)有兩種說(shuō)法:1、DDR2的數(shù)據(jù)(DQ

2017-09-25 17:51:50

這是我自己寫(xiě)ddr2控制器的寫(xiě)操作,但為什么寫(xiě)的地址不按順序?qū)懀姓l(shuí)做過(guò)嗎?

2017-03-20 16:36:20

Cyclone III系列型號(hào)為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產(chǎn)的型號(hào)為MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM為存儲(chǔ)器。用一個(gè)IP核完成

2011-05-03 11:31:09

基于Xilinx FPGA的DDR2 SDRAM存儲(chǔ)器接口

2012-08-20 18:55:15

嗨!我正在尋找Spartan-3A / 3ANFPGA入門(mén)KitBoard用戶指南(UG334)。具體來(lái)說(shuō)第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因?yàn)槔邕@個(gè)內(nèi)存

2019-07-31 06:18:10

你好使用Xilinx的任何一個(gè)端口MIG DDR2 SDRAM控制器都是我遇到了問(wèn)題我有vhdl頂級(jí)系統(tǒng),其中我實(shí)例化ddr2控制器我的ddr2包裝器與testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

的工作時(shí)鐘頻率。然而,設(shè)計(jì)至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實(shí)現(xiàn)高速、高效率的DDR3控制器是一項(xiàng)艱巨的任務(wù)。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲(chǔ)器可靠接口的塊

2019-08-09 07:42:01

嗨,我即將使用Virtex-4QV設(shè)備(XQR4VFX140)開(kāi)始一個(gè)新項(xiàng)目。雖然我對(duì)使用DDR2 / DDR3 SDRAM的Xilinx MIG有一些經(jīng)驗(yàn),但我發(fā)現(xiàn)MIG IP不支持VIRTEX-4QV器件。那可能是另類?如何將DDR2 SDRAM與此FPGA連接?彌敦道

2020-04-02 06:08:46

我生成了DDR2設(shè)計(jì)但是當(dāng)我在硬件上運(yùn)行它時(shí),led_error輸出總是很高,表明讀回失敗。為了縮小問(wèn)題范圍,我需要查看接口中的總線傳輸,但是當(dāng)我嘗試將chipcope信號(hào)掛鉤到DDR2總線實(shí)現(xiàn)失敗

2019-05-10 14:25:23

DDR2控制和FPGA實(shí)現(xiàn)

2015-07-21 19:28:14

下降的缺陷(甚至于DDR/DDR2又有著不支持單一地址訪問(wèn)的限制,分別至少2/4個(gè)地址同時(shí)訪問(wèn))。但是,速度是王道,容量也是它的優(yōu)勢(shì),這些特點(diǎn)是其它任何易失存儲(chǔ)器無(wú)法媲美的,也是它存在的唯一理由

2014-12-30 15:22:49

我們知道ddr2有速度等級(jí)和存儲(chǔ)量大小之分。在用altera FPGA設(shè)計(jì)的時(shí)候調(diào)用IP核到底該怎樣選擇ddr2呢?比如說(shuō)640*480*8bit@60hz的視頻信號(hào),該選擇什么ddr2呢?怎么計(jì)算

2018-01-31 11:00:13

FPGA與DDR2存儲(chǔ)器接口DDR2控制器的設(shè)計(jì)原理是什么?DDR2控制器的應(yīng)用有哪些?

2021-04-30 06:28:13

×16bit)的DDR2 SDRAM為存儲(chǔ)器。用一個(gè)IP核完成對(duì)4片DDR2的控制(帶寬為64bit),且DDR2的最高速率可達(dá)200MHz,以此完成對(duì)數(shù)據(jù)的高速大容量存儲(chǔ)。由于采用一個(gè)DDR2的IP核進(jìn)行控制

2019-05-31 05:00:05

DDR SDRAM is a 2n prefetch architecture with two data transfers perclock cycle. In the 2n prefetch

2009-03-28 14:43:47 56

56 DDR2 SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設(shè)計(jì)方法!詳述了其基本結(jié)構(gòu)和設(shè)計(jì)思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 FeaturesThe Agilent W2630 Series DDR2 BGA probes for logic analyzers and oscilloscopes enable

2010-08-01 12:14:42 6

6 DDR2 SDRAM 和 FB-DIMM的電氣檢驗(yàn):

隨著DDR2 SDRAM時(shí)鐘頻率和信號(hào)邊沿速率不斷提高,檢查電路板結(jié)構(gòu)、電氣系統(tǒng)和信令正變得越來(lái)越重要。本應(yīng)用指南介紹了電路板、電源系統(tǒng)、

2010-08-06 08:29:01 39

39 不只計(jì)算機(jī)存儲(chǔ)器系統(tǒng)一直需要更大、更快、功率更低、物理尺寸更小的存儲(chǔ)器,嵌入式系統(tǒng)應(yīng)用也有類似的要求。本應(yīng)用指南介紹了邏輯分析儀在檢驗(yàn)DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 81

81 我采用XC4VSX35或XC4VLX25 FPGA來(lái)連接DDR2 SODIMM和元件。SODIMM內(nèi)存條選用MT16HTS51264HY-667(4GB),分立器件選用8片MT47H512M8。設(shè)計(jì)目標(biāo):當(dāng)客戶使用內(nèi)存條時(shí),8片分立器件不焊接;當(dāng)使用直接貼

2010-10-07 11:06:37 157

157 在高速、大容量存儲(chǔ)的系統(tǒng)設(shè)計(jì)中,DDR2 SDRAM為設(shè)計(jì)者提供了高性價(jià)比解決方案。在FPGA中實(shí)現(xiàn)DDR2 SDRAM控制器,降低了系統(tǒng)功耗并節(jié)省空間, 縮短開(kāi)發(fā)周期,降低系統(tǒng)開(kāi)發(fā)成本

2010-12-13 17:10:35 49

49 DDR2名詞解釋

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))進(jìn)行開(kāi)發(fā)的新生代內(nèi)存技術(shù)標(biāo)準(zhǔn),它與上一代DDR內(nèi)

2009-04-26 18:02:22 1572

1572

DDR2內(nèi)存?zhèn)鬏敇?biāo)準(zhǔn) DDR2可以看作是DDR技術(shù)標(biāo)準(zhǔn)的一種升級(jí)和擴(kuò)展:DDR的核心頻率與時(shí)鐘頻率相等,但數(shù)據(jù)頻率為時(shí)鐘頻率的兩倍,也

2009-04-26 18:05:40 1127

1127

什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))進(jìn)行開(kāi)發(fā)的新生代內(nèi)存技

2009-12-17 11:17:59 935

935 DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))進(jìn)行開(kāi)發(fā)的新生代內(nèi)存技術(shù)標(biāo)準(zhǔn),它與上一代DDR內(nèi)存技術(shù)標(biāo)準(zhǔn)最大的不

2009-12-17 16:26:19 1134

1134 DDR2內(nèi)存?zhèn)鬏敇?biāo)準(zhǔn)

DDR2可以看作是DDR技術(shù)標(biāo)準(zhǔn)的一種升級(jí)和擴(kuò)展:DDR的核心頻率與時(shí)鐘頻率相等,但數(shù)據(jù)頻率為時(shí)鐘頻率的兩倍,也就是說(shuō)在一個(gè)時(shí)鐘周期內(nèi)必須傳輸

2009-12-24 14:53:28 883

883 DDR2傳輸標(biāo)準(zhǔn)

DDR2可以看作是DDR技術(shù)標(biāo)準(zhǔn)的一種升級(jí)和擴(kuò)展:DDR的核心頻率與時(shí)鐘頻率相等,但數(shù)據(jù)頻率為時(shí)鐘頻率的兩倍,也就是說(shuō)在一個(gè)時(shí)鐘周期內(nèi)必須傳輸兩次

2009-12-25 14:12:57 563

563 DDR2乏人問(wèn)津 DRAM廠搶轉(zhuǎn)產(chǎn)能

DDR2和DDR3 1月上旬合約價(jià)走勢(shì)迥異,DDR2合約價(jià)大跌,DDR3卻大漲,凸顯世代交替已提前來(lái)臨,將加速DDR2需求急速降溫,快速轉(zhuǎn)移到DDR3身上,

2010-01-18 16:04:44 1316

1316 廠商采取搭售策略 挽回DDR2銷售頹勢(shì)

全球DRAM市場(chǎng)正加速進(jìn)行世代交替,DDR3芯片因缺貨使得價(jià)格持續(xù)上漲,DDR2價(jià)格卻嚴(yán)重下跌,且累積庫(kù)存越來(lái)越多,近期韓系DRAM大

2010-01-20 09:24:18 912

912 DDR2芯片價(jià)格有望在下半年超過(guò)DDR3

報(bào)道,威剛主席Simon Chen今天表示,隨著DRAM制造商把重點(diǎn)放在DDR3芯片生產(chǎn)上,DDR2芯片的出貨量將開(kāi)始減少,其價(jià)格有望在今年下半

2010-02-05 09:56:18 1177

1177 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))進(jìn)行開(kāi)發(fā)的新生代內(nèi)存技術(shù)標(biāo)準(zhǔn),它與上一代DDR內(nèi)

2010-03-24 16:06:36 1644

1644 金士頓:DDR2/DDR3價(jià)格可能會(huì)繼續(xù)上漲

據(jù)報(bào)道,存儲(chǔ)大廠金士頓亞太地區(qū)副總裁Scott Chen近日表示,雖然1Gb DDR2/DDR3的芯片價(jià)格已經(jīng)超過(guò)了3美元大關(guān),

2010-04-09 09:11:05 904

904 DDR2內(nèi)存瘋狂演繹 2G版沖破350元近一年間,市場(chǎng)主流的DDR2內(nèi)存一直演繹著瘋狂,在200元與300元之間幾經(jīng)反復(fù)。近日,DDR2內(nèi)存的瘋狂更進(jìn)一步,2G的DDR2內(nèi)存的售價(jià)最高竟然已達(dá)35

2010-04-13 09:29:35 604

604 MAX17000A脈寬調(diào)制(PWM)控制器為筆記本電腦的DDR、DDR2、DDR3存儲(chǔ)器提供完整的電源方案。該器件集成了一路降壓控制器、一路可

2010-11-25 09:26:24 909

909

摘要:介紹了一種基于現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA) 和第二代雙倍數(shù)據(jù)率同步動(dòng)態(tài)隨機(jī)存取記憶體(DDR2) 的高速模 數(shù)轉(zhuǎn)換(ADC) 采樣數(shù)據(jù)緩沖器設(shè)計(jì)方法,論述了在Xilinx V5 FPGA 中如何實(shí)現(xiàn)高速同步

2011-03-31 16:38:08 140

140 從那時(shí)起,采用DDR2、甚至最新的DDR3 SDRAM的新設(shè)計(jì)讓DDR SDRAM技術(shù)黯然失色。DDR內(nèi)存主要以IC或模塊的形式出現(xiàn)。如今,DDR4雛形初現(xiàn)。但是在我們利用這些新技術(shù)前,設(shè)計(jì)人員必須了解如何

2011-07-11 11:17:14 6408

6408

This document defines the DDR2 SDRAM specification, including features, functionalities, ACand DC

2011-07-12 09:53:15 203

203 文中在介紹DDR2的工作原理的基礎(chǔ)上,給出了一個(gè)用VHDL語(yǔ)言設(shè)計(jì)的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統(tǒng)中DDR2 SDRAM的應(yīng)用方案,同時(shí)在Virtex-5系列的FPGA上得到了實(shí)現(xiàn)

2011-07-23 10:03:16 5829

5829 文章對(duì)適用DDR2 SDRAM控制器的結(jié)構(gòu)、接口和時(shí)序進(jìn)行了深入研究與分析,總結(jié)出一些控制器的關(guān)鍵技術(shù)特性,然后采用了自頂向下(TOP-IX)WN)的設(shè)計(jì)方法,用Verilog硬件描述語(yǔ)言實(shí)現(xiàn)控制器,

2011-09-01 16:36:29 174

174 SDRAM, DDR, DDR2, DDR3 是RAM 技術(shù)發(fā)展的不同階段, 對(duì)于嵌入式系統(tǒng)來(lái)說(shuō), SDRAM 常用在低端, 對(duì)速率要求不高的場(chǎng)合, 而在DDR/DDR2/DDR3 中,目前基本上已經(jīng)以DDR2 為主導(dǎo),相信不久DDR3 將全面取代

2012-01-16 14:53:01 0

0 使用功能強(qiáng)大的FPGA來(lái)實(shí)現(xiàn)一種DDR2 SDRAM存儲(chǔ)器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲(chǔ)控制器,由于該公司出產(chǎn)的這種存儲(chǔ)控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 239

239 基于Xilinx的DDR2 SDRAM存儲(chǔ)控制器的用戶接口設(shè)計(jì)與仿真,本設(shè)計(jì)通過(guò)采用多路高速率數(shù)據(jù)讀寫(xiě)操作仿真驗(yàn)證,可知其完全可以滿足時(shí)序要求,由綜合結(jié)果可知其使用邏輯資源很少,運(yùn)行速

2013-01-10 14:12:45 4252

4252 ddr2_sdram 操作時(shí)序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 21

21 ISS 的DDR2 的設(shè)計(jì)指導(dǎo),雖是英文,但很有用。

2015-10-29 10:53:38 0

0 用FPGA設(shè)計(jì)DDR2控制器講解DDR2時(shí)序原理用戶接口設(shè)計(jì)幫助用戶快速掌握DDR2的控制技術(shù)新手上路的非常有幫助的資料。

2015-11-10 10:54:14 3

3 總結(jié)了DDR和DDR2,DDR3三者的區(qū)別,對(duì)于初學(xué)者有很大的幫助

2015-11-10 17:05:37 36

36 DDR2 SDRAM操作時(shí)序規(guī)范,中文版規(guī)范

2015-11-10 17:42:44 0

0 帶自測(cè)功能的DDR2控制器設(shè)計(jì),感興趣的可以看看。

2016-01-04 15:23:32 0

0 Xilinx FPGA工程例子源碼:DDR2 Controller

2016-06-07 11:44:14 24

24 Xilinx FPGA工程例子源碼:Xilinx DDR2存儲(chǔ)器接口調(diào)試代碼

2016-06-07 14:54:57 27

27 DDR2SDRAM控制器IP功能測(cè)試與FPGA驗(yàn)證_陳平

2017-01-07 21:45:57 3

3 本文首先列出了DDR2布線中面臨的困難,接著系統(tǒng)的講述了DDR2電路板設(shè)計(jì)的具體方法,最后給出個(gè)人對(duì)本次電路設(shè)計(jì)的一些思考。

2017-09-19 11:27:21 22

22 SDRAM):DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達(dá)2133~3200 MT/s。

2017-11-17 13:15:49 28010

28010 提出一種便于用戶操作并能快速運(yùn)用到產(chǎn)品的DDR2控制器IP核的FPGA實(shí)現(xiàn),使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過(guò)IP核控制DDR2。簡(jiǎn)單介紹了DDR2的特點(diǎn)和操作原理,并

2017-11-22 07:20:50 5930

5930

本應(yīng)用報(bào)告包含對(duì)包含DDR2接口的實(shí)現(xiàn)說(shuō)明tms320c6472 / tms320tci6486 DSP器件。為指定的DDR2接口時(shí)序的方法接口與以前的設(shè)備有很大的不同。

2018-04-16 15:37:42 7

7 本文檔提供了對(duì)c6474 DSP包含DDR2接口的實(shí)現(xiàn)說(shuō)明。

2018-04-16 16:03:37 7

7 本文檔介紹了在tms320c6474數(shù)字信號(hào)處理器的DDR2內(nèi)存控制器(DSPs)。

2018-04-16 16:16:04 8

8 本文檔介紹了DDR2內(nèi)存控制器在tms320dm646x數(shù)字媒體片上系統(tǒng)(dmsoc)的DDR2內(nèi)存控制器。

DDR2內(nèi)存控制器是用來(lái)與jesd79d-2a標(biāo)準(zhǔn)兼容的DDR2 SDRAM接口

2018-04-18 10:45:10 4

4 突發(fā)長(zhǎng)度,由于DDR3的預(yù)期為8bit,所以突發(fā)傳輸周期(BL,Burst Length)也固定位8,而對(duì)于DDR2和早期的DDR架構(gòu)的系統(tǒng),BL=4也是常用的,DDR3為此增加了一個(gè)

2018-06-21 09:20:54 16119

16119

采用DDR2 SDRAM作為被采集數(shù)據(jù)的緩存技術(shù), 給出了USB2.0與DDR2相結(jié)合的實(shí)時(shí)、高速數(shù)據(jù)采集系統(tǒng)的解決方案, 同時(shí)提出了對(duì)數(shù)據(jù)采集系統(tǒng)的改進(jìn)思路以及在Xilinx的Virtex5 LX30 FPGA上的實(shí)現(xiàn)方法。

2018-12-07 16:12:39 21

21 DDR2 設(shè)備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標(biāo)準(zhǔn),該電氣標(biāo)準(zhǔn)具有較低的功耗。與TSOP比起來(lái),DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 3987

3987

DDR2 SDRAM采用雙數(shù)據(jù)速率結(jié)構(gòu)實(shí)現(xiàn)高速運(yùn)行。雙數(shù)據(jù)速率體系結(jié)構(gòu)本質(zhì)上是4n預(yù)取體系結(jié)構(gòu),其接口設(shè)計(jì)為在I/O球處每個(gè)時(shí)鐘周期傳輸兩個(gè)數(shù)據(jù)字。DDR2 SDRAM的單次讀寫(xiě)操作有效地包括在內(nèi)部

2020-05-21 08:00:00 2

2 DDR2 SDRAM采用雙數(shù)據(jù)速率結(jié)構(gòu)實(shí)現(xiàn)高速運(yùn)行。雙數(shù)據(jù)速率體系結(jié)構(gòu)本質(zhì)上是4n預(yù)取體系結(jié)構(gòu),其接口設(shè)計(jì)為在I/O球處每個(gè)時(shí)鐘周期傳輸兩個(gè)數(shù)據(jù)字。DDR2 SDRAM的單次讀寫(xiě)操作有效地包括在內(nèi)部

2020-05-21 08:00:00 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是DDR和DDR2與DDR3的設(shè)計(jì)資料總結(jié)包括了:一、DDR的布線分析與設(shè)計(jì),二、DDR電路的信號(hào)完整性,三、DDR Layout Guide,四、DDR設(shè)計(jì)建議,六、DDR design checklist,七、DDR信號(hào)完整性

2020-05-29 08:00:00 0

0 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)(嵌入式開(kāi)發(fā)式入門(mén))-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 13:07:09 37

37 DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別作者:AirCity 2019.12.17Aircity007@sina.com 本文所有權(quán)歸作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 163

163 DDR2總線的仿真方法,基于Agree公司最新的網(wǎng)絡(luò)處理器APP300和HY的

DDR2 SDRAM HY5PS121621。

2022-10-21 16:09:58 0

0 電子發(fā)燒友網(wǎng)站提供《具有最大1Gb DDR2 SDRAM的SAMA5D2 SIP MPU.pdf》資料免費(fèi)下載

2023-09-25 10:11:12 0

0 5片DDR2設(shè)計(jì)分享

2022-12-30 09:19:26 5

5 電子發(fā)燒友網(wǎng)站提供《DDR2與DDR的區(qū)別.doc》資料免費(fèi)下載

2024-03-07 14:58:52 0

0 電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 10:16:45 1

1 電子發(fā)燒友網(wǎng)站提供《完整的DDR2、DDR3和DDR3L內(nèi)存電源解決方案同步降壓控制器TPS51216數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-03-13 13:58:12 0

0 電子發(fā)燒友網(wǎng)站提供《全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-04-09 09:51:21 9

9 電子發(fā)燒友網(wǎng)站提供《完整DDR,DDR2,DDR3 和LPDDR3 存儲(chǔ)器電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-04-09 09:49:32 0

0 電子發(fā)燒友網(wǎng)站提供《在DSP上實(shí)現(xiàn)DDR2 PCB布局布線.pdf》資料免費(fèi)下載

2024-10-15 09:16:49 3

3 電子發(fā)燒友網(wǎng)站提供《TMS320DM644x DMSoC DDR2內(nèi)存控制器用戶指南.pdf》資料免費(fèi)下載

2024-12-16 10:27:15 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論