本例程詳細(xì)介紹了如何在FPGA上實(shí)現(xiàn)Serial RapidIO(SRIO)通信協(xié)議,并通過Verilog語言進(jìn)行編程設(shè)計。SRIO作為一種高速、低延遲的串行互連技術(shù),在高性能計算和嵌入式系統(tǒng)中廣

2025-11-12 14:38:17 5408

5408

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-12-12 09:19:08 3688

3688

Keystone_SRIO_Init(&srio_cfg);之后,接收即終止了,之后也沒辦法繼續(xù)接收FPGA傳輸?shù)?b class="flag-6" style="color: red">數(shù)據(jù)。而此時DSP可以正常向FPGA傳輸數(shù)據(jù)。

??????? 不知道是不是因為沒有添加

2018-06-21 13:16:48

? ? ? ? 我已經(jīng)研究過K1_STK中的SRIO例程,對SRIO的工作方式也很熟悉。現(xiàn)在將DSP板與FPGA板兩板通過SRIO 4x進(jìn)行背板連接,因為FPGA有專門的工具可以通過發(fā)送PRBS

2018-06-21 06:25:29

\device_srio.cport mode(port模式)SRIO通道有自回環(huán)(loopback)模式和普通模式(Normal),要使用SRIO實(shí)現(xiàn)FPGA和DSP的通信,必須將各port調(diào)至Normal模式,即

2020-09-23 11:08:36

CCS5.5DSP 6657

FPGA XC7Z030

FPGA 與

FPGA 之間

SRIO傳輸成功;DSP 與 DSP 之間

SRIO傳輸成功;問題 :

FPGA 與 DSP 之間 ,PORT OK 可以通過,可是就是無法正確傳輸成功。 這會是什么問題呢?會是什么原因?qū)е碌哪兀啃枰⒁馐裁吹胤侥兀?/div>

2019-01-10 11:17:28

FPGA的SRIO(Serial RapidIO)接口使用時,需要注意以下幾個方面以確保數(shù)據(jù)交換和通信的順利進(jìn)行:

接口連接與配置 :

確保FPGA和與其通信的設(shè)備(如DSP)上都配備了SRIO接口

2024-06-27 08:33:13

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02:57

SITE LICENSE SRIO 2.1 ECP3

2023-03-30 12:03:00

各位好!

? ? ? ?參考Ti給的例程,發(fā)現(xiàn)SRIO中斷是直接配置寄存器,然后再SRIO_vector.asm文件中完成中斷服務(wù)函數(shù)入口的映射,而主機(jī)PC和DSP的交互是通過利用CSL庫函數(shù)來完成中斷配置,我想問一下:兩種中斷配置方式能同時寫在同一個函數(shù)里面嗎?

謝謝!

2018-06-21 08:43:37

本人使用virtex 5 與dsp c6678 srio通信,fpga是從模式,一直使用的1x。現(xiàn)在調(diào)試4x的時候遇到問題,4x會自動變成1x通信,或者:dsp成4x,fpga也訓(xùn)練成4x,但是此時

2018-06-21 00:10:20

我用fpga nwrite方式向6678寫數(shù)然后看ddr3內(nèi)存 點(diǎn)內(nèi)存界面的持續(xù)刷新時 內(nèi)存數(shù)據(jù)不變 點(diǎn)刷新時內(nèi)存數(shù)據(jù)變化 有的時候只有srio初始化的時候內(nèi)存數(shù)據(jù)變一下 請問問題可能出在哪

2018-08-03 06:51:53

嗨, 我想通過srio協(xié)議將數(shù)據(jù)從我的模塊(fpga)發(fā)送到其他模塊(tc6678texas處理器)。我想知道是否有任何中斷來啟動轉(zhuǎn)移?感謝致敬M LOKESWARA REDDYBEL

2020-04-30 09:31:47

數(shù)據(jù)、萬兆以太網(wǎng)數(shù)據(jù)、SRIO協(xié)議等數(shù)據(jù)的采集。采-存-傳系統(tǒng)——存儲高帶寬大容量的存儲能力是本系統(tǒng)的靈魂我們的系統(tǒng)采用高性能NVME SSD為存儲介質(zhì),NVME SSD硬盤通過PCIe Gen3x4

2021-12-16 11:33:22

? ? ?各位好,我正準(zhǔn)備投板FPGA+DSP(c6657+kintex7)的一塊板子,兩者是通過SRIO口做數(shù)據(jù)的交互。目前,整個板子剩下SRIO口的電路還不是很確定,雖然在論壇也看過一些帖子,但

2018-06-19 01:47:15

請教SRIO通信問題,6672和FPGA的SRIO通信,2個lane連接,現(xiàn)象如下:

?(1)兩端都配置成2x,3.125G,FPGA顯示port initial成功,link initial失敗。

(2)把6672配置成2個1x,FPGA顯示初始化成功,但無法進(jìn)行數(shù)據(jù)通信。

請教是什么問題,謝謝。

2018-06-21 13:52:27

目前在使用DSP和FPGA之間通過SRIO的SWRITE事務(wù)完成雙向數(shù)據(jù)通信,大多數(shù)情況下都正常,但是在我不停的給DSP進(jìn)行燒寫程序時,會偶爾出錯,FPGA無法收到DSP下發(fā)的數(shù)據(jù)。偶爾故障情況下buf_lcl_phy_buf_stat_out始終是5\'b10000,且buf_lcl_response_only_out一直是1

2025-11-15 16:22:36

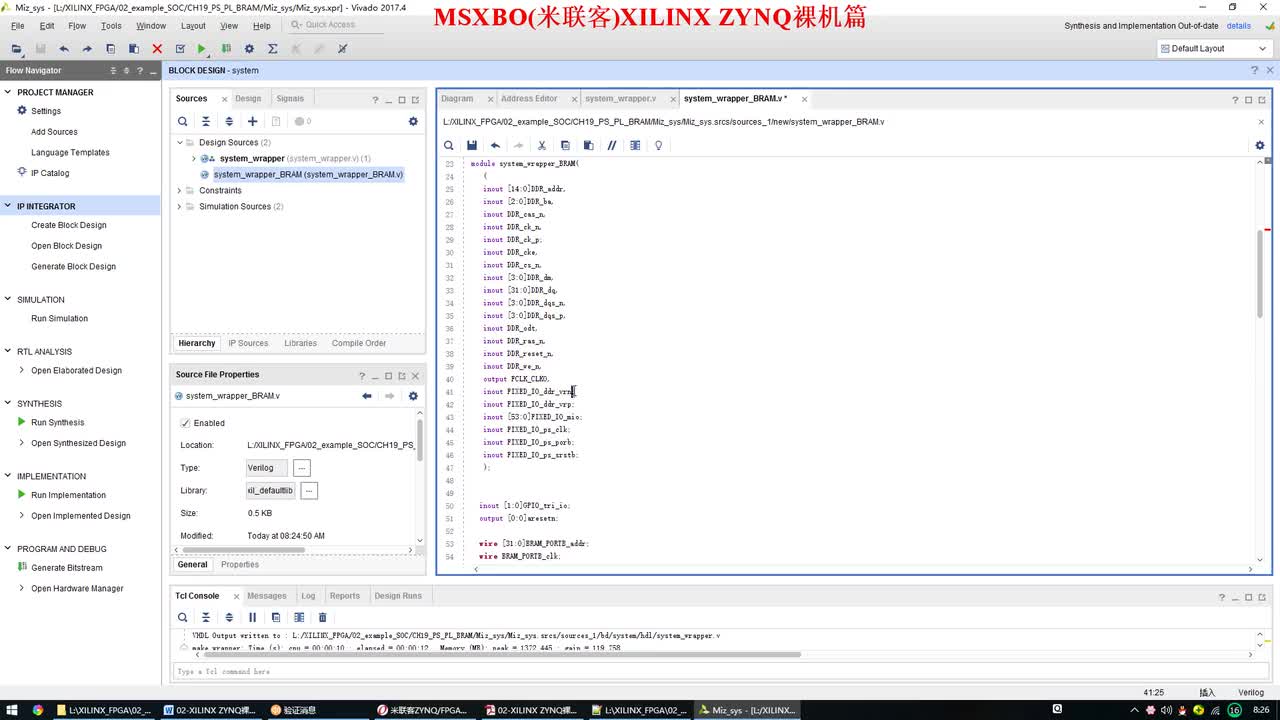

寫數(shù)據(jù)進(jìn)行比對,以檢測SRIO傳輸是否有數(shù)據(jù)錯誤。1.1.3例程使用特別提示:例程使用,請參考下面章節(jié)順序執(zhí)行。確保ZYNQ PL程序要先運(yùn)行,然后才能運(yùn)行DSP程序。1.1.3.1 加載運(yùn)行ZYNQ程序

2023-02-21 14:51:50

進(jìn)行比對,以檢測SRIO傳輸是否有數(shù)據(jù)錯誤。1.1.3 例程使用特別提示:例程使用,請參考下面章節(jié)順序執(zhí)行。確保ZYNQ PL程序要先運(yùn)行,然后才能運(yùn)行DSP程序。1.1.3.1 加載運(yùn)行ZYNQ程序

2023-02-02 21:43:20

目前已調(diào)試完成兩片DSP之間的SRIO通信,在進(jìn)行DSP與FPGA之間的SRIO。現(xiàn)在遇到了如下幾個問題。希望TI的工程師們有時間的時候給點(diǎn)幫助,不勝感激。1.DSP之間傳輸時一切正常,但是

2018-12-27 11:16:03

目前在調(diào)試多片6678與fpga通過cps1848交換芯片通信,使用的是論壇中keystone_srio例程調(diào)試過程中有幾個問題。1.dap向dpga發(fā)數(shù)時而成功時而失敗,失敗時查看error

2019-06-04 11:03:34

你好!我現(xiàn)在嘗試實(shí)現(xiàn)FPGA通過SRIO接口向DSP TMS320C6670發(fā)送數(shù)據(jù),代碼基于CCS5.0下的SRIO_Loopbacktestproject,但發(fā)現(xiàn)在sriodevice_init

2018-08-06 06:38:43

6678、FPGA,程序基于STK例程修改。流程:FPGA通過srio傳輸數(shù)據(jù)后,將傳輸完成標(biāo)志置1。該傳輸完成標(biāo)志位于DSP的SL2中。DSP查詢該標(biāo)志的狀態(tài)。如果為1,則去讀取數(shù)據(jù)。讀取數(shù)據(jù)后

2018-08-03 09:20:22

進(jìn)行修改,實(shí)現(xiàn)了c6678與FPGA之間的數(shù)據(jù)通信(數(shù)據(jù)通信功能已測試完成)。現(xiàn)在的問題是,原代碼中可以正常接收到doorbell中斷(即FPGA向C6778發(fā)送doorbell,在c6678一側(cè)會成

2018-08-03 06:19:00

你好,

? ? ? 我想將FPGA上的數(shù)據(jù) , 位寬 32bit, 速率500MHz 左右 實(shí)時傳到 DSP上去,應(yīng)該如何設(shè)計接口,不使用RAPID IO/SRIO 等接口。

2018-06-21 07:51:58

基于ZigBee網(wǎng)與以太網(wǎng)間數(shù)據(jù)傳輸系統(tǒng)該怎樣去設(shè)計?

2021-05-19 06:20:59

在現(xiàn)代各類儀器的開發(fā)中,人機(jī)交互功能正起著無可替代的作用。人機(jī)交互界面友好的儀器將更容易操作和使用,從而提高工作效率。液晶顯示器(LCD)具有功耗低、價格低、壽命長、接口控制方便等特點(diǎn),在科研

2019-10-21 07:48:41

如題,怎么將保存的的txt文件中的時間數(shù)據(jù)讀出啊,用表格顯示的話,時間數(shù)據(jù)總是顯示0啊,怎么回事啊

2013-07-23 11:05:40

在現(xiàn)代各類儀器的開發(fā)中,人機(jī)交互功能正起著無可替代的作用。人機(jī)交互界面友好的儀器將更容易操作和使用,從而提高工作效率。液晶顯示器(LCD)具有功耗低、價格低、壽命長、接口控制方便等特點(diǎn),在科研

2019-08-22 07:50:27

大家好,我想請教一個問題,我需要把一段離散的時間數(shù)據(jù)轉(zhuǎn)換成連續(xù)的時間數(shù)據(jù),如圖左邊,第1秒到第10秒的數(shù)據(jù)都是100,第10秒到第20秒的數(shù)據(jù)都是200,第20秒到第30秒的數(shù)據(jù)都是300,想轉(zhuǎn)換成

2020-04-09 09:16:49

大家好,5396的手冊網(wǎng)上只要簡版的2頁說明,想問下把5396的數(shù)據(jù)接口直接連到FPGA的GTX,能進(jìn)行5396與FPGA的數(shù)據(jù)交互嗎,還是需要相關(guān)的配置來完成5396余FPGA的交互呢?還有把數(shù)據(jù)

2018-01-07 23:02:05

本文介紹一種基于FPGA高精度時間數(shù)字轉(zhuǎn)換電路的設(shè)計方法,利用片內(nèi)鎖相環(huán)(PLL)和環(huán)形移位寄存器,采用不高的系統(tǒng)時鐘便可得到很高的時間分辨率,且占用較少邏輯資源。可作為功能電路獨(dú)立使用,也可作為 IP核方便地移植到其他片上系統(tǒng)(SOC)中。

2021-05-07 06:10:43

程序如圖,但是運(yùn)行后顯示兩列時間數(shù)據(jù) ,如何才能只顯示一列時間數(shù)據(jù)

2019-03-27 13:19:32

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠?qū)崿F(xiàn)端口0的外部回環(huán)測試。fpga端的協(xié)議還沒做通,我想用dsp直接給fpga發(fā)包,fpga根據(jù)收到

2018-06-21 10:45:13

通過全局地址搬移,如從0x10800000搬移到0x13800000,那么請問如果是多核交互的話,是否其他核就是從MSMC,共享DDR,或者0x13800000對應(yīng)的本地內(nèi)存空間去取數(shù)據(jù)就可以了,還是

2019-01-02 15:23:29

現(xiàn)在用6678的SRIO從FPGA接收數(shù)據(jù),FPGA做主!現(xiàn)在遇到一個問題,就是怎么判斷FPGA發(fā)送過來的數(shù)據(jù)已經(jīng)到達(dá)DSP指定的空間,比如我想把數(shù)據(jù)發(fā)送到6678的SL2,待數(shù)據(jù)完全到達(dá)我才能對數(shù)據(jù)

2019-01-03 11:36:07

本帖最后由 一只耳朵怪 于 2018-6-19 15:39 編輯

因為項目需求,一片C6670需要連接到兩片FPGA,但是又覺得沒必要使用SRIO SWITCH。所以我的問題是:C6670

2018-06-19 00:53:24

本帖最后由 一只耳朵怪 于 2018-6-19 14:49 編輯

本人使用的是6678芯片,現(xiàn)在需要編寫6678核間數(shù)據(jù)交互部分的程序。看了資料,qmss,CPPI都可以用來進(jìn)行核間數(shù)據(jù)

2018-06-19 02:42:49

你好我對DSP和SRIO之間的通信感興趣。有人知道virtex-6 FPGA是否有srio引腳,以及如何配置?

2020-06-14 14:22:51

收不到數(shù)據(jù),serdes loopback收到數(shù)據(jù)正確。采用的是6678平臺,目前external loopback 硬件連接是:通過外部用線連RX,TX。SRIO external loopback

2018-06-19 06:26:42

怎樣去設(shè)計數(shù)據(jù)采集與交互系統(tǒng)的軟件部分?怎樣去設(shè)計數(shù)據(jù)采集與交互系統(tǒng)的硬件部分?

2021-05-24 06:55:36

在論壇下載到SRIO的官方例程,移植到開發(fā)板后,使DSP與FPGA通訊,DSP向FPGA發(fā)送1K數(shù)據(jù)成功,更改傳輸數(shù)據(jù)的大小為1024*1024后編譯成功,但是還是傳輸?shù)?K數(shù)據(jù),查看地址以及配置

2018-07-23 10:49:17

Hi,Ti guys,我在使用自己板上的c6678,利用論壇上keystone_srio程序調(diào)試dsp和fpga端的通信。同事從fpga(v6,srio核)看來收發(fā)地址都是34衛(wèi)的,但我調(diào)DSP互聯(lián)

2018-12-28 11:08:14

收發(fā)接口來說,驅(qū)動初始化完畢之后,是不是FPGA可以通過一個接口向DSP發(fā)送數(shù)據(jù),而DSP也可以通過另一個反向接口發(fā)送數(shù)據(jù),就是說對于一對SRIO接口來說,兩邊是不是都能通過這個接口主動發(fā)起數(shù)據(jù)讀寫操作啊?謝謝!

2018-06-19 03:02:21

本帖最后由 一只耳朵怪 于 2018-5-25 15:56 編輯

我們設(shè)計的系統(tǒng)是6678和Altera的FPGA利用SRIO進(jìn)行通訊,FPGA利用SRIO 1X接口,對6678進(jìn)行SRIO

2018-05-25 10:16:06

分析空間數(shù)據(jù)的特點(diǎn)和用常規(guī)方法進(jìn)行空間數(shù)據(jù)聚類分析的難點(diǎn)與不足,提出一種基于改進(jìn)的演化算法空間數(shù)據(jù)聚類方法——SDCEA。解決用傳統(tǒng)方法進(jìn)行空間數(shù)據(jù)聚類分析時存在的問

2009-04-10 09:29:24 28

28 利用數(shù)據(jù)庫技術(shù)來管理海量的空間數(shù)據(jù),有兩種方法:一種是在數(shù)據(jù)庫和用戶應(yīng)用系統(tǒng)間建立中間層,稱為空間數(shù)據(jù)引擎SDE,利用SDE作為中間接口使數(shù)據(jù)庫操作系統(tǒng)能存儲和管理空

2009-08-07 09:56:31 9

9 本文在介紹空間數(shù)據(jù)挖掘、Agent 技術(shù)的概念和特點(diǎn)的基礎(chǔ)上,提出一個基于Agent的分布式空間數(shù)據(jù)挖掘系統(tǒng),描述了其實(shí)現(xiàn)過程。由于在實(shí)現(xiàn)過程中只傳送執(zhí)行挖掘功能的移動Agent

2009-12-25 13:38:56 14

14 什么是空間數(shù)據(jù)轉(zhuǎn)換格式

空間數(shù)據(jù)轉(zhuǎn)換格式是實(shí)施空間數(shù)據(jù)轉(zhuǎn)換的標(biāo)準(zhǔn)中介格式。為實(shí)現(xiàn)轉(zhuǎn)換,需要制訂并遵循統(tǒng)一 的空間數(shù)據(jù)轉(zhuǎn)換標(biāo)準(zhǔn),包括現(xiàn)實(shí)世

2009-06-17 07:35:45 1900

1900 什么是空間數(shù)據(jù)庫無縫連接

空間數(shù)據(jù)庫的無縫連接是一個建立在用戶與空間數(shù)據(jù)庫接口基礎(chǔ)上的概念,它是空間數(shù)據(jù)庫 中空間數(shù)據(jù)集

2009-06-17 07:36:28 1523

1523 什么是空間數(shù)據(jù)交換中心

空間數(shù)據(jù)交換中心是指對不同范圍、領(lǐng)域的空間信息及其元數(shù)據(jù)進(jìn)行有效管理、給信息需求 者提供空間數(shù)據(jù)

2009-06-17 07:40:05 1205

1205 :根據(jù)現(xiàn)行文獻(xiàn)中反復(fù)提到的空間數(shù)據(jù)處理內(nèi)涵的理解,將空間數(shù)據(jù)處理分為空間數(shù)據(jù)處理技術(shù)和空間數(shù)據(jù)處理理論,簡要論述了各自的主要內(nèi)容,討論了空間數(shù)據(jù)挖掘的現(xiàn)狀和今后研究的重

2011-06-24 11:12:43 0

0 針對GML 空間數(shù)據(jù) 冗余較大且存儲和傳輸代價高的問題,提出一種GML 空間數(shù)據(jù)壓縮方法,采用VTD-XML 解析GML 文檔,設(shè)計將樹形結(jié)構(gòu)的GML 空間數(shù)據(jù)轉(zhuǎn)換為2 個線性結(jié)構(gòu)數(shù)據(jù)的GBW 變換,利用

2011-07-27 15:46:23 0

0 本文介紹了這種基于SRIO互聯(lián)技術(shù)的高速實(shí)時數(shù)據(jù)處理硬件平臺,并在該平臺上研究了多DSP之間、DSP與FPGA之間的SRIO通信技術(shù)。

2012-01-10 15:07:55 4573

4573

基于FPGA的高精度時間數(shù)字轉(zhuǎn)換 方法研究

2015-10-30 10:59:13 4

4 一種基于FPGA的時鐘相移時間數(shù)字轉(zhuǎn)換器_王巍

2017-01-07 22:23:13 3

3 基于Linux及Qt_Embedded的壓鑄車間數(shù)據(jù)采集系統(tǒng)設(shè)計_魯遙遙

2017-02-07 18:11:35 0

0 空間數(shù)據(jù)系統(tǒng)咨詢委員會(CCSDS)-直致力于空間任務(wù)安全性方面的工作,并成立了一個工作小組,旨在數(shù)據(jù)鏈路層為遙控遙測通信制定安全協(xié)議,即空間數(shù)據(jù)鏈路安全(SDLS)協(xié)議。該協(xié)議為已存在的空間數(shù)據(jù)

2017-11-07 15:29:37 19

19 難度大,實(shí)現(xiàn)復(fù)雜算法也比較困難。因此,結(jié)合多核DSP和FPGA的優(yōu)勢,構(gòu)建基于異構(gòu)處理器的信號處理系統(tǒng)成為當(dāng)前一種發(fā)展趨勢。異構(gòu)處理器間的高速通信成為高速信號處理系統(tǒng)[1]的關(guān)鍵問題之一,本文基于SRIO協(xié)議設(shè)計和實(shí)現(xiàn)了DSP與FPGA之間的高速數(shù)據(jù)通信。

2017-11-17 03:11:01 32633

32633

為了滿足2ynq-7000系列芯片的SRIO數(shù)據(jù)傳輸要求,提出了一種基于FPGA控制DMA傳輸進(jìn)行SRIO通信的設(shè)計方案,并完成了ARM與FPGA核間高吞吐率的數(shù)據(jù)交互操作。系統(tǒng)的FPGA部分主要

2017-12-21 11:37:03 31

31 ,基于這兩方面,本文簡要介紹了如何利用Xilinx公司的MicroBlaze微處理器軟核,以及相應(yīng)的嵌入式操作系統(tǒng)Xilkernel和Lwip協(xié)議功能函數(shù),采用片上系統(tǒng)設(shè)計理念,來設(shè)計完成基于FPGA的嵌入式以太網(wǎng)與Matlab通信平臺的數(shù)據(jù)傳送交互系統(tǒng)。

2018-10-12 16:14:46 9

9 SRIO是面向嵌入式系統(tǒng)開發(fā)提出的高可靠、高性能、基于包交換的新一代高速互聯(lián)技術(shù),已于2004年被國際標(biāo)準(zhǔn)化組織(ISO)和國際電工協(xié)會(IEC)批準(zhǔn)為ISO/IECDIS 18372標(biāo)準(zhǔn)。SRIO則是面向串行背板、DSP和相關(guān)串行數(shù)據(jù)平面連接應(yīng)用的串行RapidIO接口。

2020-06-17 11:48:12 3520

3520 本文為您分享基于C66x+FPGA的SRIO開發(fā)視頻教程,適用于創(chuàng)龍TMS320C6678、TMS320C665x、Kintex-7、Artix-7平臺。

2020-07-01 10:47:39 2375

2375 近年來,隨著面向?qū)ο?b class="flag-6" style="color: red">數(shù)據(jù)庫技術(shù)成熟,使用大型的RDBMS管理海量空間數(shù)據(jù)成為可能,企業(yè)化GIS數(shù)據(jù)組織和處理就顯得非常必要。空間數(shù)據(jù)共享是當(dāng)前地理信息系統(tǒng)建設(shè)的重要課題,而空間數(shù)據(jù)轉(zhuǎn)換是實(shí)現(xiàn)信息共享

2020-09-17 16:07:00 13

13 基于Oracle-Spatial空間數(shù)據(jù)共享系統(tǒng)設(shè)計(肇慶理士電源技術(shù)有限公司圖片)-該文檔為基于Oracle-Spatial空間數(shù)據(jù)共享系統(tǒng)設(shè)計總結(jié)文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 13:59:08 1

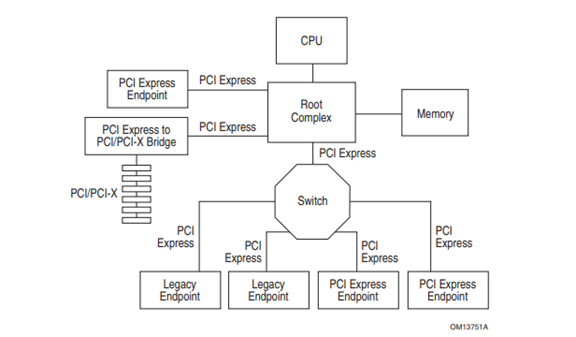

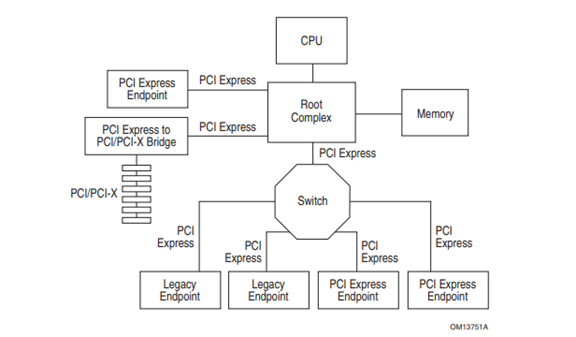

1 隨著PCIe接口、以太網(wǎng)接口的飛速發(fā)展,以及SOC芯片的層出不窮,芯片間的數(shù)據(jù)交互帶寬大大提升并且正在向片內(nèi)交互轉(zhuǎn)變;SRIO接口的應(yīng)用市場在縮小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用場景中仍然占有一席之地。

2022-08-02 10:00:26 5994

5994

目前具備SRIO接口的硬件不多,推薦廣州星嵌電子科技有限公司開發(fā)的DSP+FPGA+RAM開發(fā)板XQ6657Z35-EVM。

2022-11-08 17:22:21 2762

2762

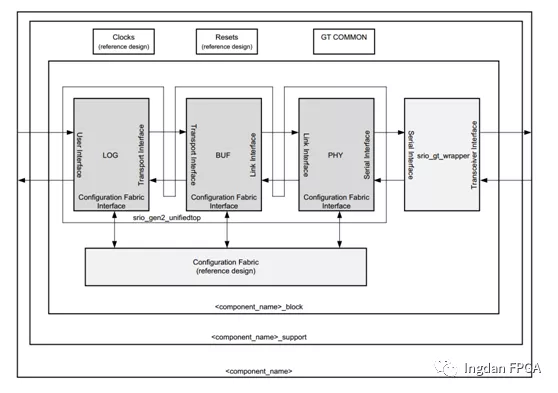

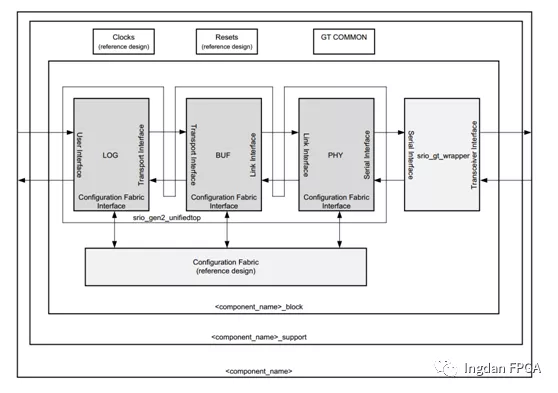

數(shù)據(jù)從遠(yuǎn)程設(shè)備(假設(shè)為DSP的SRIO端)傳輸過來,FPGA端(假設(shè)我們這端為FPGA的SRIO端口)通過RX接收到串行數(shù)據(jù),先到達(dá)物理層進(jìn)行時鐘恢復(fù),串并轉(zhuǎn)換,之后進(jìn)行8b/10b解碼操作、CRC校驗,這一系列的操作都在物理層完成,之后進(jìn)入傳輸層

2023-03-03 10:19:53 1638

1638 摘要: 現(xiàn)代 信號 處理系統(tǒng)通常需要在不同處理器之間實(shí)現(xiàn)高速數(shù)據(jù) 通信 ,SRIO協(xié)議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實(shí)現(xiàn)SRIO協(xié)議的方法,并

2023-03-20 15:00:01 3755

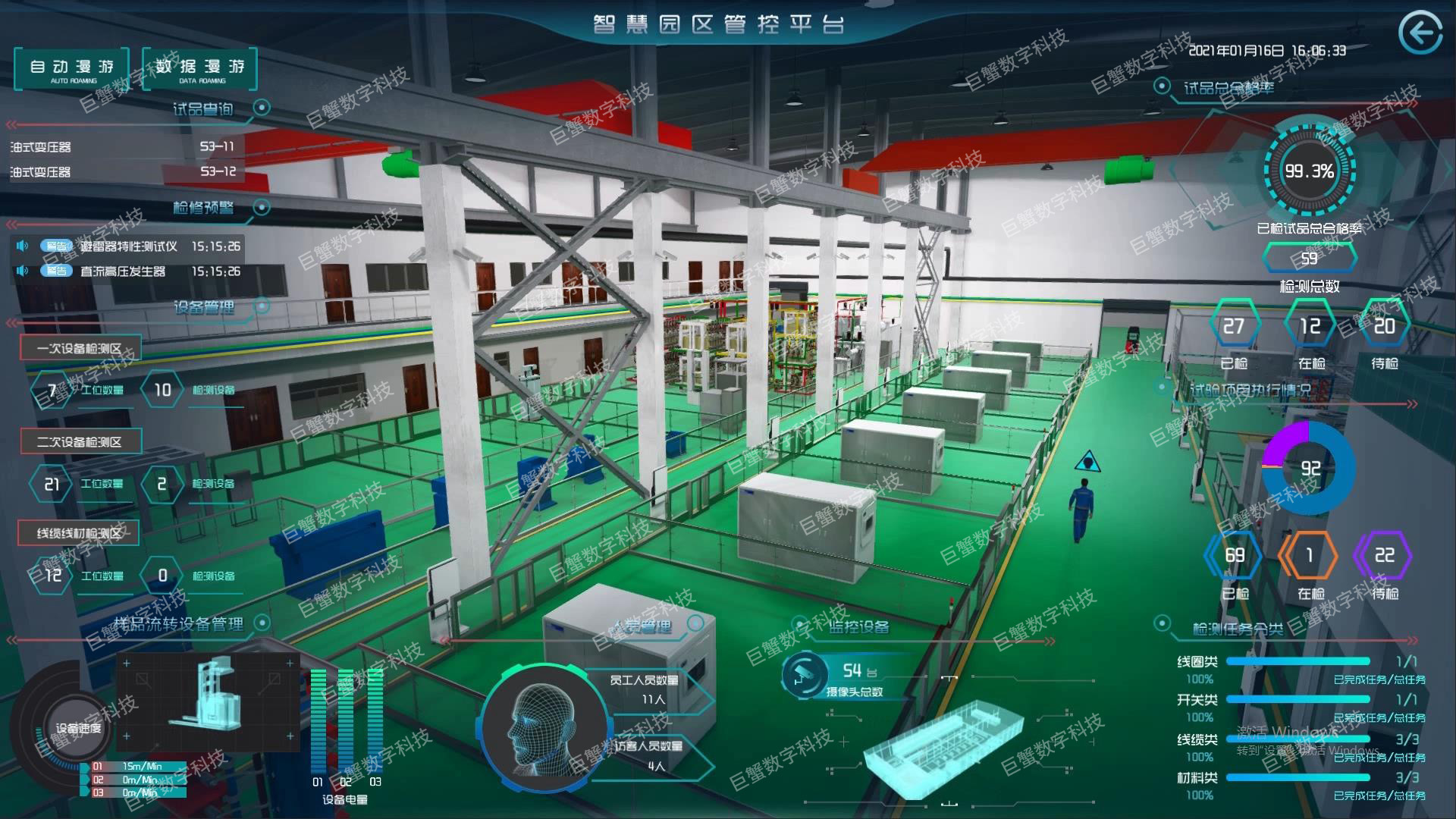

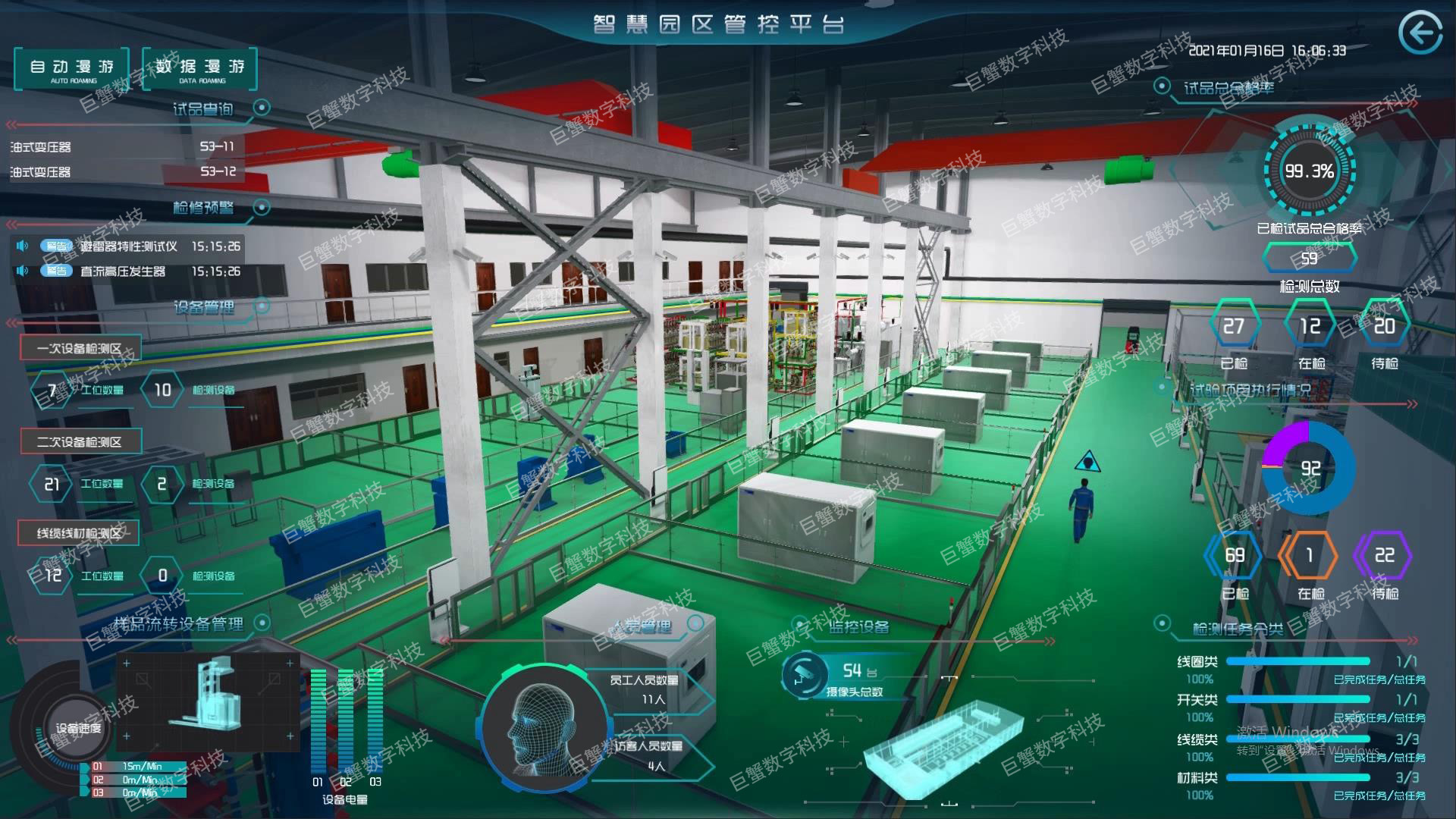

3755 河南鄭州洛陽數(shù)字孿生智慧工廠,工廠車間數(shù)字化三維仿真交互,3d可視化數(shù)據(jù)大屏展示系統(tǒng)。在推動制造業(yè)邁向智能化的諸多技術(shù)之中,數(shù)字孿生備受關(guān)注,也被寄予厚望。巨蟹數(shù)字科技通過虛實(shí)融合,不僅可以實(shí)現(xiàn)可視化展示,還可以實(shí)現(xiàn)精準(zhǔn)預(yù)警以及運(yùn)營優(yōu)化,成為傳統(tǒng)工廠數(shù)智化建設(shè)轉(zhuǎn)型的熱門技術(shù)。

2023-03-31 14:18:42 1355

1355

SRIO這種高速串口復(fù)雜就復(fù)雜在它的協(xié)議上,三層協(xié)議:邏輯層,傳輸層以及物理層。

數(shù)據(jù)手冊會說這三層協(xié)議是干什么的呢?也就是分工(【FPGA】SRIO IP核系統(tǒng)總覽以及端口介紹(一)(User Interfaces 之 I/O Port))

2023-04-25 11:20:55 2541

2541

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-09-04 18:19:18 2358

2358

GIS(地理信息系統(tǒng))主要用于處理和分析地理空間數(shù)據(jù),但它也可以處理非地理空間數(shù)據(jù)。在現(xiàn)實(shí)世界中,許多數(shù)據(jù)也不是直接與地理位置相關(guān)聯(lián)的,這些數(shù)據(jù)可能來自不同的領(lǐng)域,例如經(jīng)濟(jì)、社會、環(huán)境和健康等。將

2024-02-25 13:53:57 1206

1206 等領(lǐng)域,以實(shí)現(xiàn)設(shè)備之間的高速、低延遲數(shù)據(jù)交互。SRIO交換芯片的出現(xiàn),極大地提升了數(shù)據(jù)傳輸效率和系統(tǒng)性能。

2024-03-16 16:40:42 5525

5525 FPGA(現(xiàn)場可編程門陣列)和DSP(數(shù)字信號處理器)之間通過SRIO接口進(jìn)行調(diào)試通常需要以下步驟。

2024-04-19 11:48:46 2569

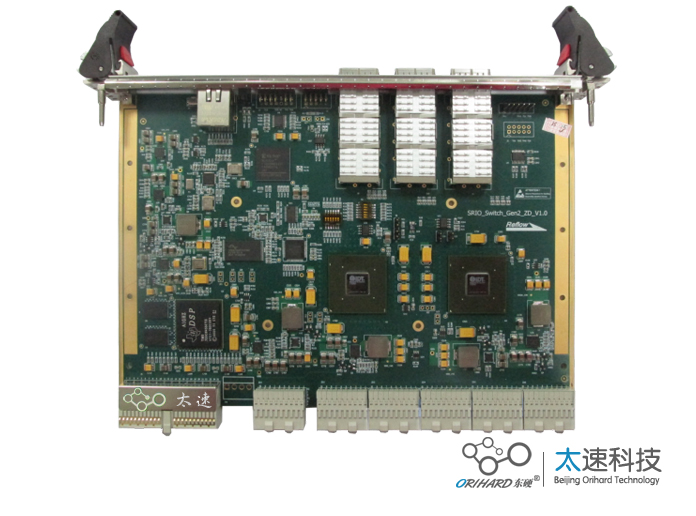

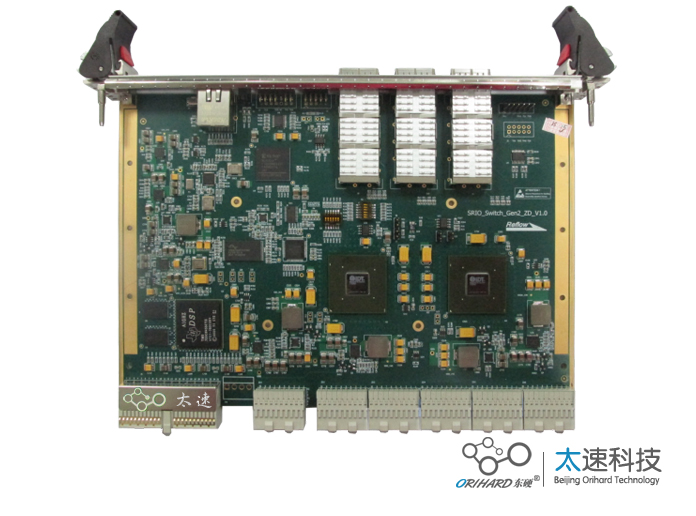

2569 SRIO_Switch_Gen2_ZD交換板卡為基于IDT?SRIO?Gen2系列SRIO交換芯片,采用CPCI-ZD平臺架構(gòu)的數(shù)據(jù)交換板。可以為高速實(shí)時信號處理任務(wù)提供可靠保障。

2024-05-13 11:40:57 1879

1879

三維地圖可視化 交互系統(tǒng)是一種基于三維地圖技術(shù)的交互式應(yīng)用程序,可以呈現(xiàn)地理信息和空間數(shù)據(jù)的立體化展示,并提供用戶友好的交互功能。以下是古河云科技關(guān)于三維地圖可視化交互系統(tǒng)的主要特點(diǎn)和應(yīng)用價值

2024-07-19 18:20:46 2629

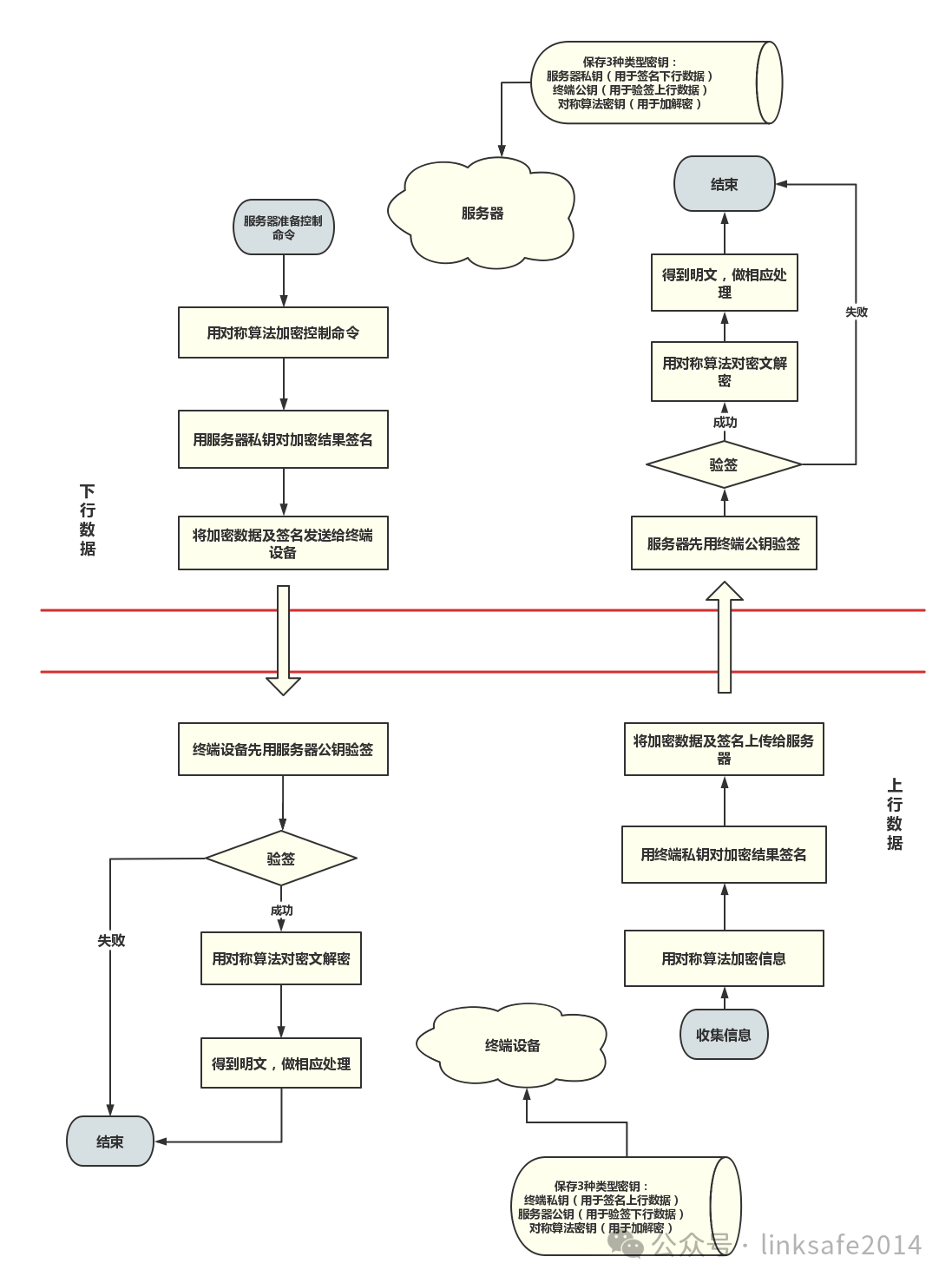

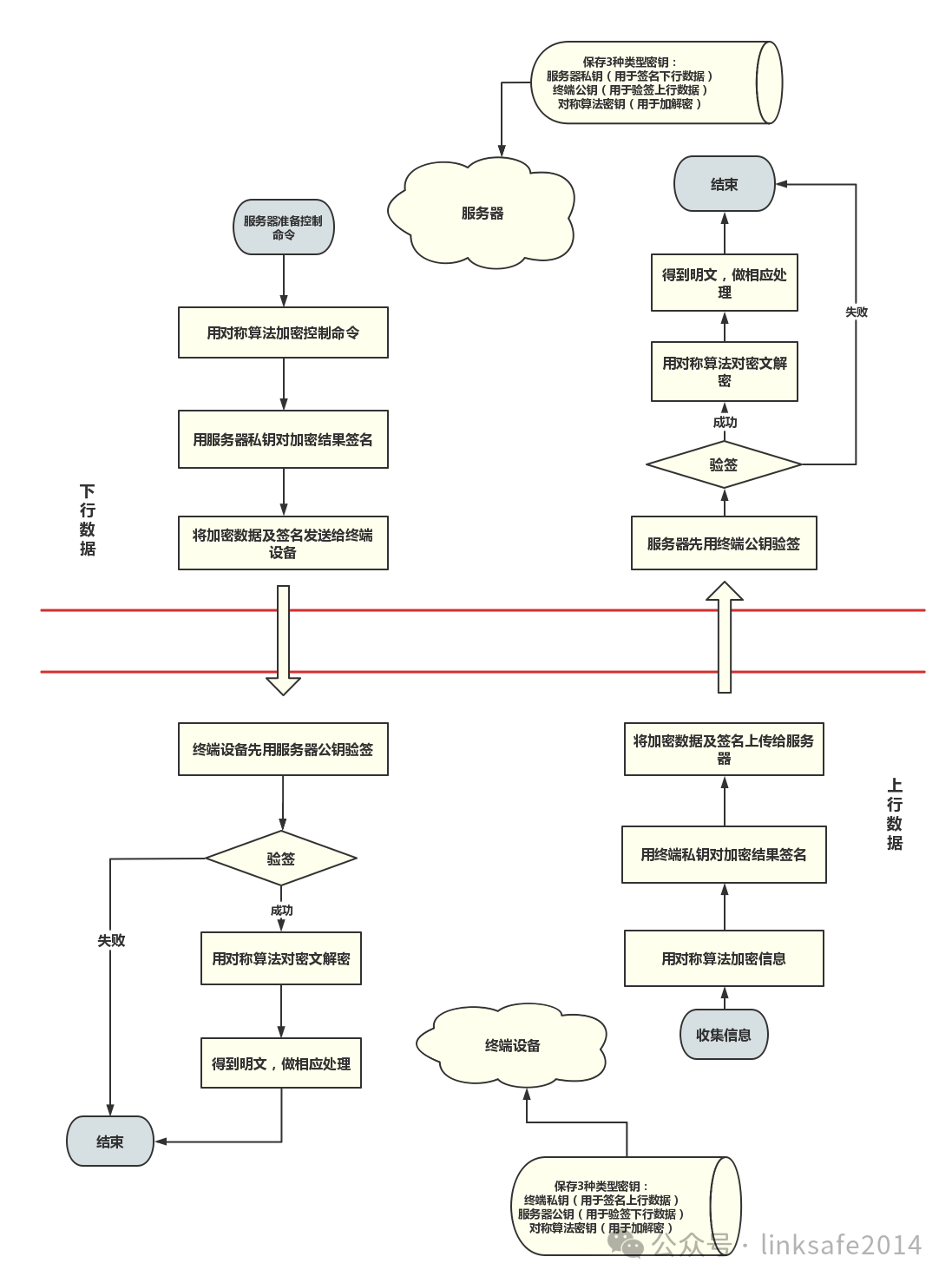

2629 隨著互聯(lián)網(wǎng)、智能終端等相關(guān)行業(yè)的飛速發(fā)展,對終端產(chǎn)品遠(yuǎn)程控制的需求在人們生活中越來越普遍。如何保障后臺與終端產(chǎn)品之間數(shù)據(jù)安全交互、不被篡改、不被盜取成為產(chǎn)品安全性的主要問題。

2024-08-26 17:20:28 962

962

介紹 本處將從SRIO的數(shù)據(jù)流,數(shù)據(jù)協(xié)議,常用FPGA支持模式,以及IP例程中的時鐘大小計算等部分介紹SRIO的情況。 3.1 SRIO的數(shù)據(jù)流 SRIO通過生成IP后,通常情況下主要使用的接口為四組

2024-12-10 16:24:43 4651

4651

電子發(fā)燒友App

電子發(fā)燒友App

評論