)、鎖相環頻率合成技術(PLL)、直接數字頻率合成技術(DDS)、混合頻率合成技術四種實現方式,其中鎖相環頻率合成器是射頻電路中最常使用的一種結構,相比于其他幾種結構,PLL結構能夠在有限的功耗限制下合成高性能的載波信號。

2015-10-17 11:24:00 2785

2785

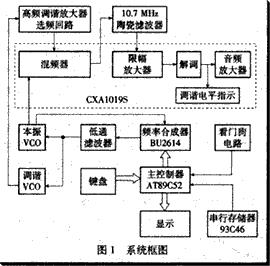

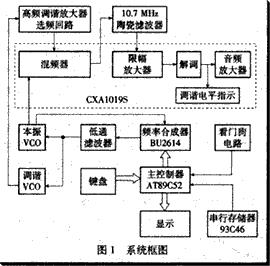

作為收音機重要組成部分的調諧電路和本振電路一直采用傳統的電容、電感手動調臺方式。近年來,隨著無線電通信技術的迅速發展,鎖相環和頻率合成技術在各個領域得到了廣泛的應用。由于鎖相環具有跟蹤特性、窄帶濾波特性和鎖定狀態無剩余頻差存在,因此在頻率合成技術中采用鎖相環路可以產生頻率準確度很高的振蕩信號源。

2018-12-21 08:50:00 8441

8441

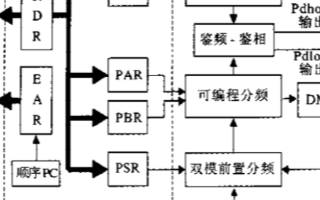

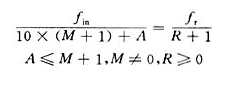

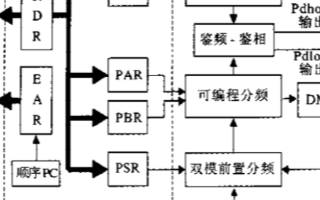

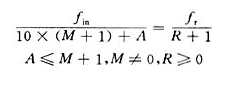

數字鎖相環頻率合成系統的工作原理是:鎖相環對高穩定度的基準頻率(通常由晶體振蕩器直接或經分頻后提供)進行精確鎖定,環內串接可編程的分頻器,通過編程改變分頻器的分頻比,使環路總的分頻比為N(可通過編程改變),從而環路穩定的輸出 N倍的基準頻率,而整個程序和系統的控制是要由CPU來完成的。

2020-07-23 16:47:49 2086

2086

我用ADF4351做一個整數分頻的鎖相環輸出,控制器是51單片機,程序能下載進單片機,時序是參考網上寫寄存器的程序,但是寄存器賦值LD引腳高低電平變化時,在LD引腳檢測不到高低電平,感覺寄存器值沒寫

2019-01-04 10:16:12

我ADF4351不能正常控制它的輸出頻率,控制板調整輸出頻率數值增加一定范圍的數值,ADF輸出端輸出頻率才發生變化,并且輸出頻率錯誤。比如驅動板控制ADF輸出70MHZ,但是ADF輸出端只有

2017-07-15 17:35:36

專家們好,最近項目用ADF4351做AD/DA的采樣時鐘源,時鐘頻率為100MHz,結果寄存器寫進去了,鎖定指示LD管腳連接的指示燈也亮了,但用示波器看輸出卻沒有信號,不知為何,同樣的程序,把時鐘

2018-10-25 09:12:45

本人新手,最近再學習ADF4351的使用,在制作PCB時發現官網中所給出的ADF4351BCPZ的封裝里的輸出引腳(11,12)與ADF4351的用戶手冊里的輸出引腳(12,13)對應不上,而且還有

2018-09-04 11:35:32

求一ADF5355_鎖相環相關資料,最好中文版,詳細點

2017-03-06 23:32:13

想用adf4351做一個鎖相環提取載波,但是每次鎖定后輸出都和參考有一個隨機的相位差,請問如何才能消除這個相位差,使輸出與參考輸入同頻同相。寄存器配置如下:

2018-08-09 06:48:18

頻率合成器的主要性能指標鎖相環頻率合成器原理鎖相環頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

我用msp430和adf4106加一個vco 和環路濾波做了一個鎖相環,但頻率漂到其他地方了!請大神解決

2016-01-20 15:07:57

ADI是高性能模擬器件供應商,在鎖相環領域已有十多的的設計經驗。到目前為止,ADI的ADF系列鎖相環產品所能綜合的頻率可達8GHz,幾乎能夠涵蓋目前所有無線通信系統的頻段。ADF系列PLL頻率合成

2018-10-31 15:08:45

ADI是高性能模擬器件供應商,在鎖相環領域已有十多的的設計經驗。到目前為止,ADI的ADF系列鎖相環產品所能綜合的頻率可達8GHz,幾乎能夠涵蓋目前所有無線通信系統的頻段。ADF系列PLL頻率合成

2018-11-06 09:03:16

EVAL-ADF4351EB1Z,該板設計用于允許用戶評估ADF4351頻率合成器的性能,以實現鎖相環(PLL)。它顯示了該板,其中包含ADF4351集成合成器和VCO,用于輸出信號的SMA連接器

2019-03-01 08:03:03

FPGA怎么驅動ADF4351去產生一個正弦波

2016-06-04 14:57:29

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。 關鍵詞:ADF4106,鎖相環,頻率合成器,環路濾波器

2019-07-04 07:01:10

我有一塊ADF4351的開發板,但是我現在想用相位噪聲測試儀測量ADF4351的VCO開環相位噪聲,但是卻不知道怎樣設置,如果僅僅只是將振蕩器移除,測量得到的相位噪聲是VCO的閉環相位噪聲,有沒有大神知道怎么設置才能測量VCO的開環相位噪聲, 希望能夠指點一二 謝謝

2018-08-02 07:46:23

圖一圖一中U2是ADF4351,U6和U8是兩個串聯的射頻開關HMC347,兩個開關中心距是6mm,一個HMC347在2.4GHz隔離度大概50多dB,C44這邊是ADF4351頻率源的輸出,是個

2019-01-10 14:27:42

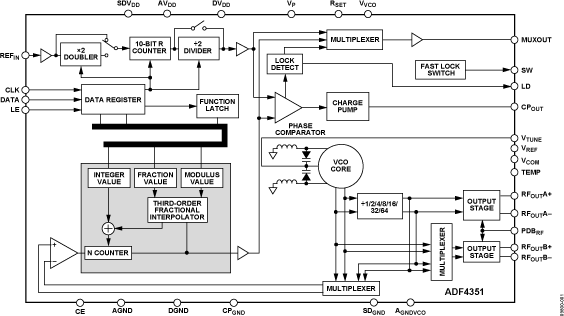

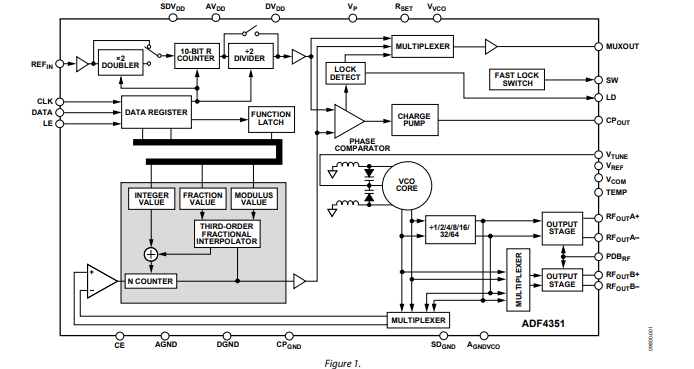

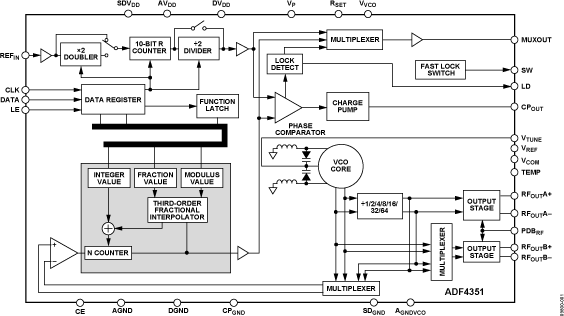

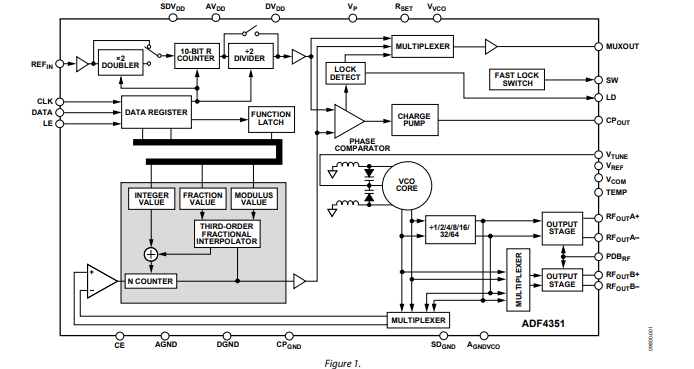

ADF4351鎖相環介紹及相關硬件設計ADF4351是ADI公司推出的一款集成VCO的鎖相環芯片。其輸出頻率范圍可配置為35MHZ到4400MHZ,這取決于參考頻率和寄存器配置。其內部包括整數N

2022-01-11 07:28:51

下合成高性能的載波信號。本文基于鎖相環芯片ADF4106設計了一種數字鎖相環頻率合成器,具有超寬的帶寬、較好的噪聲特性、快速鎖定時間,以及功耗低和體積小等特點,從而被廣泛應用于無線通信系統中。一

2018-09-06 14:32:13

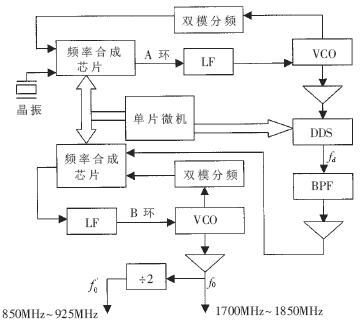

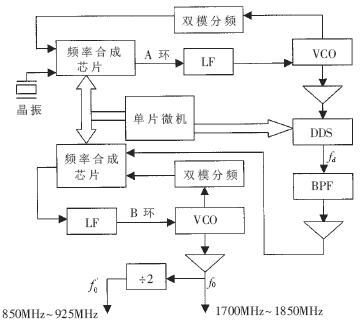

本文設計了一種多環鎖相頻率合成器。多環鎖相環路有直接數字頻率合成(DDS)環路和鎖相頻率合成環路(PLL)組成。充分利用兩個不同環路的優點,既保證了高的輸出頻率,又得到了較高的頻率分辨率。【關鍵詞

2010-05-13 09:09:53

鎖相環是什么工作原理?如何采用FPGA與頻率綜合器ADF4111相結合的方法實現數字鎖相式頻率源的設計?

2021-04-14 07:00:20

鎖相環頻率合成器是什么原理?基于CD4046的鎖相環頻率合成器的設計

2021-04-12 06:28:35

數字鎖相環頻率合成系統的工作原理CPU控制數字鎖相環頻率合成系統FPGA實現

2021-04-09 06:20:37

評估板EVAL-ADF4152HVEB1Z旨在讓用戶評估ADF4152HV頻率合成器的性能,以實現鎖相環(PLL)。該板包含ADF4152HV合成器,環路濾波器,1GHz至2GHz倍頻程的壓控振蕩器

2019-03-01 10:17:42

使用ADF4351設計了一個頻率源,頻率范圍1200M-2500M,步進1M,要求跳頻時間控制在50us內,通過實際測試只能到100us。現在想知道ADF4351最快的頻率鎖定時間是多少啊?如果可以達到的話,應如何設置寄存器?參考頻率100M,鑒相頻率25M,環路帶寬為250K。

2018-10-11 09:21:28

問題描述:使用ADF4351評估板自帶的25 MHz參考頻率,輸出頻率為1422 MHz,參數設計如下圖所示: 使用頻譜儀輸出頻率,Span設置為100 Hz,VBW和RBW自動設置,發現頻率在

2018-09-12 11:08:59

ADF4351移相時禁用頻段選擇,設置相位值,并不能實現移相操作?

2019-01-03 21:35:40

工程師您好:ADF4351內部集成VCO振蕩器,如果結合外部環路濾波器和外部參考時鐘頻率能構成數字鎖相環嗎?如果不能是不是因為ADF4351內部沒有鑒相器,如果我想做數字鎖相環還要和ADF4002合用嗎?能實現位同步嗎?期待您們的答復!

2018-09-14 14:23:29

采用ADF4351輸出頻率,發現設置輸出頻率時,其3、5、7、2、4、6等倍頻的位置幅值很大,特別是基波600M頻率以下時,3倍頻諧波輸出幅度超過了基波,請教如何能將高次諧波大幅度減小?

2018-09-25 11:29:24

請教老師,我想用一個PLL(ADF4351)給兩個DAC(AD9119)提供時鐘,DAC時鐘頻率最高為1.5GHz。我的ADF4351輸出可以直接接到兩個DAC的CLK輸入端嗎(也就是兩個DAC并聯

2018-12-03 09:26:26

您好!請問頻率合成器ADF4351數據手冊中提到的“通道步進分辨率”是什么意思?它有什么作用?下圖是ADF4351的評估板軟件,我想要配置1425.42MHz的輸出,請問Channel

2018-10-26 09:07:07

我近日在學習鎖相環時使用STM32控制ADF4351產生264.3MHz的LO。在使用ADIsimPLL設計工具時,根據填入參數,生成的配置中Prescaler P選項默認設置成8,但是我覺得根據

2018-07-27 09:25:30

請問一些關于ADF4351的問題1.ADF4351能在40~4.4GHz都單端輸出2dBm的功率嗎?功率波動為2dBm2.輔助輸出B也能在單端輸出時輸出2dBm的功率嗎?功率博能能到2dBm嗎?3.

2018-07-30 06:06:13

`具體要求是這樣的,要利用ADF4351產生多路同頻并具有特定相位差(如相差為0)的信號。目前我利用同一個外部時鐘和STM32f103RCT6控制板實現了4路同頻信號(我這里是151MHz)的產生

2018-11-18 18:06:50

最近在調試adf4351,出現數字檢測是高電平,LD也輸出高電平,但沒輸出信號,請問是什么問題?

2018-09-25 14:14:51

各位前輩們好,請問,用頻譜儀測量ADF4351輸出,為什么1.7GHz-2.3GHz的頻率段沒鎖住,而35MHz-2.5GHz的其他任何頻率鎖的頻譜都非常好?環路濾波器我是仿的50MHz到2.5GHz的。

2018-09-04 11:35:39

驅動高壓鎖相環頻率合成器電路的VCO

2021-01-11 06:02:04

用ad9850激勵的鎖相環頻率合成器山東省濟南市M0P44 部隊Q04::00R 司朝良摘要! 提出了一種ad9850和ad9850相結合的頻率合成方案! 介紹了ad9850芯片ad9850的基本工作原理" 性能特點及

2008-07-17 22:44:22 4

4 文中在簡要敘述鎖相環的基本原理的基礎上,介紹了 ADF4218L 的主要特點及基于ADF4218L 鎖相頻率合成器硬件電路的設計和實現。在此基礎上討論了實際電路調試中應該注意的問

2009-08-13 09:59:45 41

41 ADF4351結合外部環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。 ADF4351具有一個集成電壓控制振蕩器(VCO),其基波輸出頻率范圍為

2023-02-16 15:13:11

ADF4351結合外部環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。 ADF4351具有一個集成電壓控制振蕩器(VCO),其基波輸出頻率范圍為

2023-02-16 15:18:14

鎖相環的研究和頻率合成一、實驗目的:1. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環基本特性的研究3. 利用鎖相環實現頻率合成二、鎖相環原理:

2009-03-06 20:02:52 2529

2529

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。???

2009-05-05 19:57:57 3047

3047

單環鎖相頻率合成器,單環鎖相頻率合成器是什么意思

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統的“心臟”。現代戰爭是

2010-03-23 11:36:28 1266

1266 集成鎖相環頻率合成器,什么是集成鎖相環頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統

2010-03-23 11:45:44 956

956 數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

背景知識:

隨著數字電路技術的發展,數字鎖相環在調制解調、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 6110

6110 頻率合成器可以提供大量精確、穩定的頻率作為無線通信設備的本振信號。簡要介紹了鎖相環頻率合成器的基本原理,并利用整數N鎖相芯片ADF4112設計了一個寬波段的頻率合成器。討論

2011-05-03 18:20:24 102

102 全球領先的高性能信號處理解決方案和 RF IC供應商,最近推出一款用于無線通信系統的 PLL(鎖相環)頻率合成器ADF4351。

2011-06-21 16:50:02 2847

2847 本文鑒于 數字鎖相環 在實際應用中對信號頻率的準確度和穩定度有較為嚴格的要求,設計一種應用于數字鎖相環的數控振蕩器(NCO,Number Controlled Oscillator)。基于直接數字頻率合成(

2011-08-05 14:51:05 79

79 鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

為得到性能優良、符合實際工程的鎖相環頻率合成器,提出了一種以ADI的仿真工具ADIsimPLL為基礎,運用ADS(Advanced Design System 2009)軟件的快速設計方法。采用此方法設計了頻率輸出為

2013-01-10 16:50:36 81

81 一、設計目標 基于鎖相環的理論,以載波恢復環為依托搭建數字鎖相環平臺,并在FPGA中實現鎖相環的基本功能。 在FPGA中實現鎖相環的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統計計算,多普勒頻偏

2017-10-16 11:36:45 19

19 業界領先的射頻、微波及毫米波產品供應商美國Pasternack公司推出一系列新型USB控制鎖相環(PLL)頻率合成器。在將信號完整性作為首要目標的射頻和微波通信系統中,鎖相環頻率合成器可提供高頻率

2018-04-26 11:16:00 1104

1104 電子發燒友網為你提供ADI(ti)ADF4351相關產品參數、數據手冊,更有ADF4351的引腳圖、接線圖、封裝手冊、中文資料、英文資料,ADF4351真值表,ADF4351管腳等資料,希望可以幫助到廣大的電子工程師們。

2019-02-22 15:16:34

本文檔的主要內容詳細介紹的是基于MSP430F5438A的ADF4351鎖相環頻率鎖定程序的詳細資料免費下載。

2019-03-18 08:00:00 56

56 本視頻將介紹如何搭建ADF4351評估板

2019-07-08 06:15:00 3913

3913 數字鎖相環頻率合成器已經廣泛的運用在軍事和民用無線通信領域,而用CPU控制的可編程大規模數字鎖相環頻率合成器則是其中的關鍵技術。當前,可編程邏輯電路在數字系統設計中飛速發展,很多中規模,甚至

2020-03-11 10:30:58 1590

1590

ADF4351 Gerber Files

2021-02-03 15:49:30 10

10 ADF4351 Gerber Files

2021-03-06 08:25:27 5

5 ADF4350/ADF4351 Evaluation Board Software

2021-03-10 14:40:42 9

9 CN-0369:低相位噪聲的轉換鎖相環頻率合成器

2021-03-20 13:21:15 7

7 UG-369:ADF4151鎖相環頻率合成器評估板

2021-04-19 20:14:47 6

6 UG-802:用于鎖相環的ADF5355頻率合成器評估

2021-04-25 12:23:05 4

4 UG-873:評估ADF4355-3小數/整數N鎖相環頻率合成器

2021-04-28 14:35:35 5

5 UG-804:評估ADF4355-2小數/整數N鎖相環頻率合成器

2021-05-10 08:26:33 9

9 UG-383:用于鎖相環的ADF4159頻率合成器評估

2021-05-10 13:26:06 2

2 UG-485:ADF4153A小數N鎖相環頻率合成器評估板

2021-05-16 13:22:43 9

9 UG-1087:用于鎖相環的ADF5356頻率合成器評估

2021-05-17 09:38:07 10

10 ADF4217:雙射頻鎖相環頻率合成器過時數據表

2021-05-17 11:55:55 2

2 UG-389:ADF4xxx鎖相環頻率合成器的USB轉并行轉接板

2021-05-24 11:46:02 6

6 UG-686:ADF4155鎖相環頻率合成器評估板

2021-05-25 16:46:51 4

4 所設計的頻率合成器,要求相位噪聲低,輸出頻率800~1 000 MHz,共88個波道,通過單片機發送的頻率控制字進行波道選擇。在對比各種大規模集成頻率合成芯片性能的基礎上,選用了單片大規模集成鎖相環頻率合成芯片PE3236作為核心電路,構成鎖相式頻率合成器。

2021-05-28 10:30:08 5925

5925

ADF4150HV鎖相環頻率合成器UG-406評估板

2021-06-03 11:16:33 10

10 該評估板旨在幫助用戶評估支持鎖相環(PLL)的頻率合成器ADF4351的性能。它包含ADF4351集成式頻率合成器和VCO、用于輸出信號的SMA連接器、電源、參考振蕩器和USB連接器。片上還集成

2021-06-04 13:54:55 4

4 數字調諧系統是現代收發信機的核心,其性能直接影響通信質量的好壞,其主要部分是集成鎖相式頻率合成器。集成鎖相環與微處理器結合,可由微機控制完成頻率合成器的全部功能。

2021-06-14 17:29:00 5078

5078

ADF4351腔體完整帶控制器V1.0文件資料分享

2022-10-08 11:24:05 6

6 鎖相環的鎖定是指鎖相環的輸出頻率等于輸入頻率,而輸出信號的相位跟隨輸入信號的變化而變化。

2023-01-31 16:31:12 4097

4097 模擬鎖相環和數字鎖相環的主要區別在于它們的控制方式不同。模擬鎖相環是通過模擬電路來控制頻率和相位,而數字鎖相環是通過數字信號處理技術來控制頻率和相位。此外,模擬鎖相環的精度較低,而數字鎖相環的精度較高。

2023-02-15 13:47:53 6625

6625 鎖相環頻率合成器的優缺點? 鎖相環頻率合成器,又稱為PLL(Phase Locked Loop),是一種廣泛應用的電路,能夠將輸入信號的頻率合成為電路所需要的頻率,并且能夠實現對信號的相位和頻率

2023-09-02 14:59:33 3701

3701 如何調試鎖相環頻率合成器?? 鎖相環頻率合成器(PLL)是電路中常見的一個模塊,用于生成穩定的高精度頻率信號。PLL的核心部分是相位檢測器和環路濾波器,其主要工作原理是通過不斷調整反饋回來的參考信號

2023-09-02 15:06:37 1899

1899 基本PLL鎖相環、整數型頻率合成器和分數型頻率合成器。下面將詳細介紹這三種模式的作用和特點。 第一種:基本PLL鎖相環 基本PLL鎖相環是PLLf工作的最基本形式,它主要由比較器、低通濾波器、VCO和分頻器組成。其基本工作原理是將輸入信號和VCO輸出的信號進行

2023-10-13 17:39:48 5284

5284 電子發燒友網站提供《基于ADF4111的鎖相環頻率合成器設計.pdf》資料免費下載

2023-10-20 14:45:29 4

4 的實時處理能力。數字鎖相環廣泛應用于物理和工程領域,包括用于測量和跟蹤信號頻率、提取原始信號的給定頻率分量并在同時消除噪聲和雜散分量,或者基于輸入信號合成新信號。此外,數字鎖相環在調制解調、頻率合成、FM立體聲解碼、彩色副載波同步、圖像處理等各個方面得到了廣泛的應用,已成為鎖相技術發展的方向。

2024-01-02 17:20:25 3358

3358

頻率合成器和鎖相環是兩種常見的電子設備,用于生成穩定的頻率信號。盡管它們的功能都是產生特定頻率的信號,但它們在工作原理和應用方面有著明顯的區別。

2024-02-27 18:22:59 2092

2092 鎖相環頻率合成器(Phase-Locked Loop Frequency Synthesizer, PLLFS)是一種利用鎖相環(Phase-Locked Loop, PLL)技術實現頻率合成的裝置。其基本原理基于相位負反饋控制系統,通過調整輸出信號的相位和頻率,使其與參考信號的相位和頻率保持同步。

2024-08-05 15:01:43 2292

2292 ADF4351結合外部環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。

ADF4351具有一個集成電壓控制振蕩器(VCO),其基波輸出頻率范圍為2200

2025-04-25 15:43:14 1099

1099

電子發燒友App

電子發燒友App

評論