1 引言

作為收音機重要組成部分的調(diào)諧電路和本振電路一直采用傳統(tǒng)的電容、電感手動調(diào)臺方式。近年來,隨著無線電通信技術(shù)的迅速發(fā)展,鎖相環(huán)和頻率合成技術(shù)在各個領(lǐng)域得到了廣泛的應(yīng)用。由于鎖相環(huán)具有跟蹤特性、窄帶濾波特性和鎖定狀態(tài)無剩余頻差存在,因此在頻率合成技術(shù)中采用鎖相環(huán)路可以產(chǎn)生頻率準(zhǔn)確度很高的振蕩信號源。利用這種振蕩信號源產(chǎn)生的頻率作為收音機電路的調(diào)諧頻率和本振頻率可以實現(xiàn)數(shù)字化收音。利用單片機控制鎖相環(huán)路中的分頻數(shù)就可以改變振蕩信號源的輸出頻率,以達到調(diào)臺的目的。設(shè)計要求主要有:

(1)接收FM信號的頻率范圍為88-108MHz;

(2)調(diào)制信號的頻率范圍為100-15000Hz,最大頻偏75kHz;

(3)最大不失真輸出功率)100mW(負載阻抗8n);

(4)接收機靈敏度≤1mW;

(5)鏡像抑制性能優(yōu)于20dB;

(6)能實現(xiàn)數(shù)字化的自動搜臺、手動調(diào)臺、存臺和頻率顯示等功能。

2 設(shè)計方案

采用專用的芯片可以使整個系統(tǒng)體積小、重量輕、可靠性好、靈敏度高、功耗低。

2.1整機電路方案

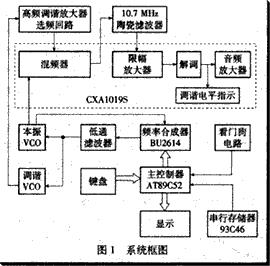

設(shè)計中高放、混頻、中放、解調(diào)等電路采用CXA1019S;自動調(diào)諧、程控搜索、電臺載頻顯示等功能由鎖相頻率合成器芯片BU2614,MCS-51系列單片機及相應(yīng)的外圍電路配合完成。通過BU2614的串行口與單片機通信來改變分頻比,用BU2614內(nèi)部的分頻器和鑒頻鑒相器,與CXAl019S的本振VCO構(gòu)成數(shù)控鎖相環(huán),通過改變分頻比改變接收的頻點。選臺和頻率顯示、存臺等由單片機AT89C52和MAX7219,93C46芯片配合完成,系統(tǒng)框圖如圖所示1。

2.2各部分電路的設(shè)計

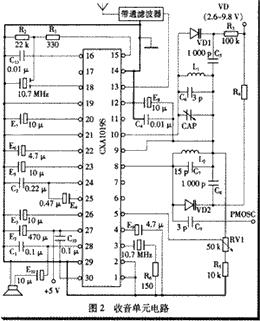

(1)收音單元。目前市場上收音機的集成芯片很多,CXAl019S用于便攜式收音機及頭盔式收音機,其接收靈敏度高、鏡像抑制性能好、外圍元件少且輸出功率大。FM時Vcc:5V,工作電流為5.3mA;在Vcc=6V、RL-8Ω時,輸出功率為500mW。收音單元電路如圖2。

(2)鎖相頻率合成單元。這一部分既是設(shè)計的重點也是難點,F(xiàn)M調(diào)頻收音機的接收頻率范圍是88-108MHz,因此所選用的頻率合成器芯片最高頻率須達到110MHz才能滿足要求。ROHM公司生產(chǎn)的鎖相頻率合成調(diào)諧集成芯片BU2614最高頻率可達到130MHz,完全滿足要求,另外該芯片內(nèi)帶有高靈敏度的RF放大器,支持IP計數(shù)功能。利用鎖相環(huán)路法構(gòu)成數(shù)字式頻率合成器,應(yīng)用BU2614內(nèi)部的數(shù)字邏輯電路把壓控振蕩器VCO頻率一次或多次降頻至鑒相器頻率上,再與參考頻率在鑒相電路中進行比較,所產(chǎn)生的誤差信號用來控制VCO的頻率,使之鎖定在芯片內(nèi)參考頻率的穩(wěn)定度上。BU2614應(yīng)用電路如圖3所示。

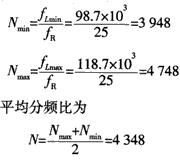

為了按要求保證搜索到所有電臺,標(biāo)準(zhǔn)頻率fr設(shè)定為25kHz,本振輸出頻率fo為98.7-118.7MHz,可采用分頻方式,環(huán)路的可編程分頻器的分頻比N為

N=fo\fr

BU2614分頻比變化范圍為

VCO為本振壓控振蕩器,實際測得的VCO增益為

BU2614的外圍電路工作原理:⑤腳接收單片機的串行數(shù)據(jù),該數(shù)據(jù)為12腳反饋頻率FMOSC提供分頻系數(shù)N,內(nèi)部標(biāo)準(zhǔn)頻率由串行數(shù)據(jù)位中的R0,R1,R2的取值確定。該設(shè)計選擇R0,R1,R2均為“1”,標(biāo)準(zhǔn)頻率為25kHz與頻率FMOSC/N比較,在PD輸出相位比較信號,根據(jù)PD輸出端的不同狀態(tài),從低通濾波器得到相應(yīng)的直流電壓,該電壓加在CX-A1019S收音機回路的調(diào)諧和本振回路中的變?nèi)?a target="_blank">二極管上,使得調(diào)諧頻率和本振頻率的改變與天線BPF輸出的載波信號諧振收到電臺,實現(xiàn)電調(diào)諧功能。而本振頻率通過電容耦合反饋到BU2614中使得頻率鎖定。

(3)顯示單元。常用的顯示接口電路多由8155,8279等芯片構(gòu)成,由于這些芯片與單片機連接時需占用P0,P2口,且動態(tài)掃描方式占用單片機內(nèi)部系統(tǒng)資源比較大。為簡化單片機的外圍電路,用MAX7219構(gòu)成一個6位靜態(tài)顯示模塊,它只需占用AT89C52的3個口線,即可完成顯示功能。

(4)鍵盤電路。由于本設(shè)計中使用的按鍵較多,因而采用了功能鍵與數(shù)字鍵分開識別的方式,即功能鍵采用查詢方式,數(shù)字鍵采用編碼動態(tài)掃描方式,這樣既可減少掃描占用的時間,又可以簡化程序。

(5)關(guān)機數(shù)據(jù)存儲單元。根據(jù)設(shè)計要求,該機具有掉電后能夠保存所存儲電臺的功能。目前市場上并行EEPROM類型很多如2764A,2864A等,體積大且無關(guān)電保存數(shù)據(jù)功能。而串行EEPROM體積小、價廉、電路連接簡單,如93C46是電擦除可編程只讀存儲器,具有在線擦除和改寫數(shù)據(jù)功能,能滿足關(guān)電保存數(shù)據(jù)的要求。另外采用串行的形式,能節(jié)省單片機的口資源。

(6)程序運行監(jiān)視單元。為加強程序運行的可靠行,需要對程序的運行狀況進行監(jiān)視,以防止程序彈飛到一個臨時構(gòu)成的死循環(huán)中,導(dǎo)致整個系統(tǒng)完全癱瘓。因此有必要在電路中設(shè)置看門狗電路(WATCHDOG電路)。現(xiàn)在常用的看門狗電路既有硬件構(gòu)成的,也有純軟件構(gòu)成的,但純軟件的WATCHDOG系統(tǒng)需要設(shè)置高級中斷子程序,占用較多的單片機內(nèi)部資源,必將影響整機的運行速度。硬件構(gòu)成的WATCHDOG系統(tǒng)的硬件部分完全獨立于CPU,可靠性大大提高。

(7)電源單元。由于BU2614,CXAl019S以及單片機系統(tǒng)需要5V電源電壓,而變?nèi)荻O管需要9V以上的電壓,若采用單電源+5V供電,則必須采用DC-DC模塊升壓得到+12V電壓。

3 軟件系統(tǒng)設(shè)計

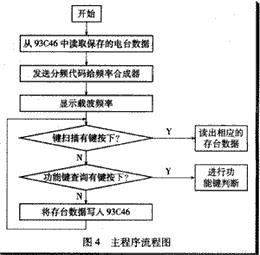

在收音機開機后,首先把上次關(guān)機時的電臺調(diào)出來,并把上次關(guān)機前的各個臺號存儲的電臺頻率數(shù)據(jù)還原。然后開始動態(tài)掃描各個數(shù)字鍵,判斷是否直接調(diào)用已存好的電臺。如果有數(shù)字鍵按下,則調(diào)用已存在該鍵下的電臺,并顯示該電臺頻率。如果沒有數(shù)字鍵按下則轉(zhuǎn)入判斷功能鍵。當(dāng)有功能鍵按下時,則執(zhí)行相應(yīng)的功能。若沒有功能鍵按下,則存儲當(dāng)前電臺數(shù)據(jù)后再返回繼續(xù)進行循環(huán)掃描。主程序流程圖如圖4所示。

4測試結(jié)果分析改進措施

設(shè)計制作完成后,對整機進行了測試,結(jié)果完全達到了預(yù)想的要求,可實現(xiàn)全頻段范圍搜索、選擇存儲電臺,在特定范圍搜索選擇存儲電臺,調(diào)用已存儲的任意電臺,載波頻率顯示等功能,接收機鏡像抑制比極高,但也存在著各頻點靈敏度略有不同的問題,經(jīng)調(diào)整天線輸入端的帶通濾波器及相關(guān)電路,效果有較大改善。

從本調(diào)頻收音機所采用的器件來實現(xiàn)的功能上看,還有可以改進和完善的地方,如顯示采用LCD液晶顯示可提供漢字信息、增加時間顯示,功能鍵采用復(fù)合鍵以減少按鍵的數(shù)量;從整機供電、攜帶方便等角度考慮,整機應(yīng)采用更低的電源供電。

總的來看,該設(shè)計的接收性能達到了要求,有的已遠超過設(shè)計要求,控制功能基本完善。

-

單片機

+關(guān)注

關(guān)注

6078文章

45552瀏覽量

672848 -

收音機

+關(guān)注

關(guān)注

64文章

612瀏覽量

80093 -

無線電

+關(guān)注

關(guān)注

63文章

2213瀏覽量

119806

發(fā)布評論請先 登錄

Altera公司鎖相環(huán)IP核介紹

CDC509:高性能3.3V鎖相環(huán)時鐘驅(qū)動器

CDCVF2505 3.3 - V 時鐘鎖相環(huán)時鐘驅(qū)動器:設(shè)計與應(yīng)用指南

TLC2932A高性能鎖相環(huán)芯片詳解:設(shè)計與應(yīng)用指南

探索TLC2933A高性能鎖相環(huán):特性、應(yīng)用與設(shè)計要點

?CDCVF2510 3.3V鎖相環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

全品類的收音機竟然都支持定制了?#收音機工廠 #收音機設(shè)計 #戶外收音機 #應(yīng)急收音機 #收音機廠家

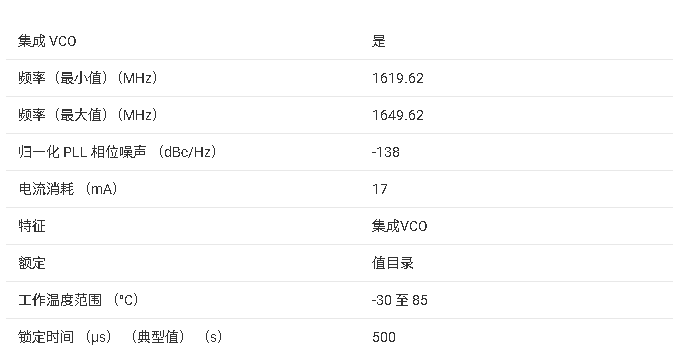

LMX2502 集成VCO的頻率合成器系統(tǒng)技術(shù)手冊

基于鎖相環(huán)的無軸承同步磁阻電機無速度傳感器檢測技術(shù)

高壓放大器在鎖相環(huán)穩(wěn)定重復(fù)頻率研究中的應(yīng)用

ADF4155整數(shù)N/小數(shù)N分頻PLL頻率合成器技術(shù)手冊

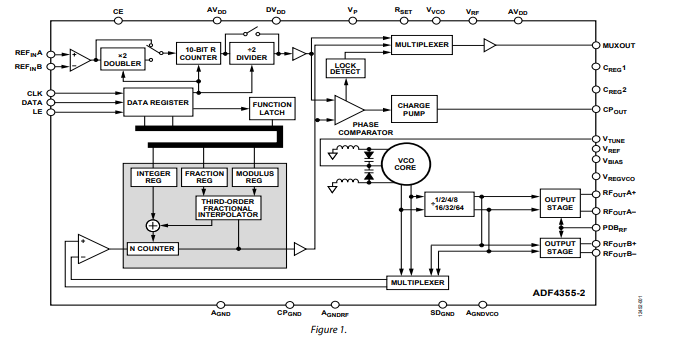

ADF4355-2集成VCO的寬帶頻率合成器技術(shù)手冊

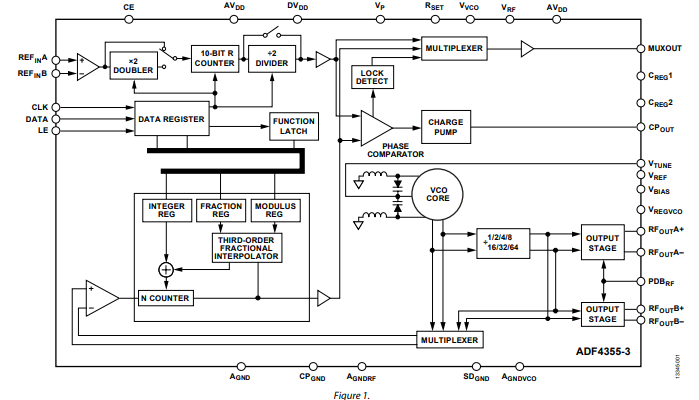

ADF4355-3集成VCO的微波寬帶頻率合成器技術(shù)手冊

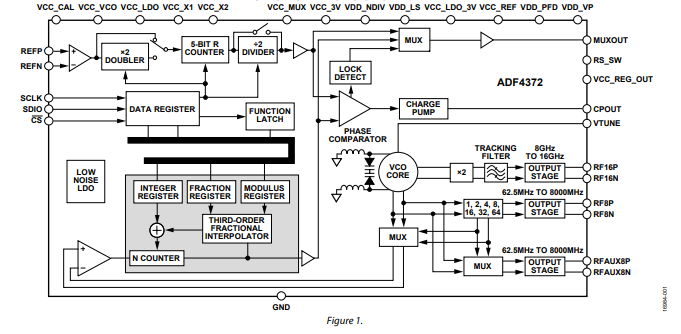

ADF4372帶集成VCO的微波寬帶頻率合成器技術(shù)手冊

鎖相環(huán)和頻率合成技術(shù)在數(shù)字式收音機中設(shè)計應(yīng)用

鎖相環(huán)和頻率合成技術(shù)在數(shù)字式收音機中設(shè)計應(yīng)用

評論