)、鎖相環頻率合成技術(PLL)、直接數字頻率合成技術(DDS)、混合頻率合成技術四種實現方式,其中鎖相環頻率合成器是射頻電路中最常使用的一種結構,相比于其他幾種結構,PLL結構能夠在有限的功耗限制下合成高性能的載波信號。

2015-10-17 11:24:00 2785

2785

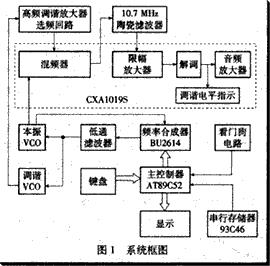

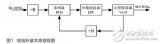

作為收音機重要組成部分的調諧電路和本振電路一直采用傳統的電容、電感手動調臺方式。近年來,隨著無線電通信技術的迅速發展,鎖相環和頻率合成技術在各個領域得到了廣泛的應用。由于鎖相環具有跟蹤特性、窄帶濾波特性和鎖定狀態無剩余頻差存在,因此在頻率合成技術中采用鎖相環路可以產生頻率準確度很高的振蕩信號源。

2018-12-21 08:50:00 8441

8441

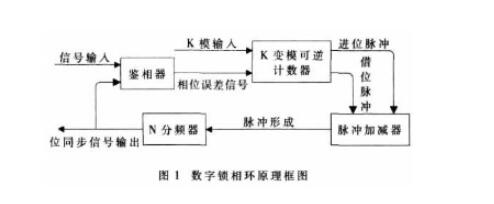

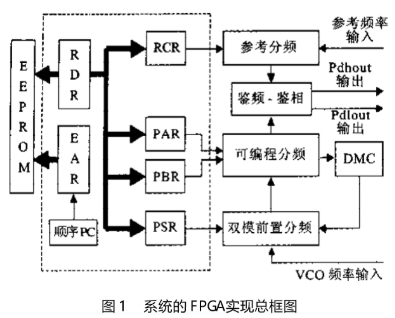

的問題進行了討論。 引言 鎖相環(PLL)技術在眾多領域得到了廣泛的應用。如信號處理,調制解調,時鐘同步,倍頻,頻率綜合等都應用到了鎖相環技術。傳統的鎖相環由模擬電路實現,而全數字鎖相環(DPLL)與傳統的模擬電路實現的PLL相比,具有精度高

2018-10-25 09:17:13 9370

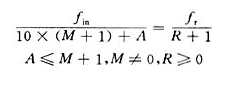

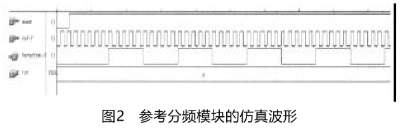

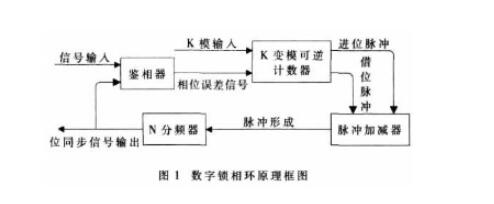

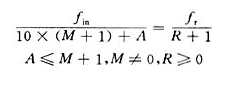

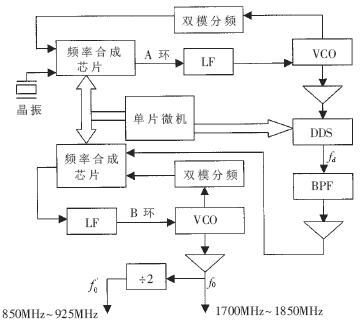

9370 數字鎖相環頻率合成系統的工作原理是:鎖相環對高穩定度的基準頻率(通常由晶體振蕩器直接或經分頻后提供)進行精確鎖定,環內串接可編程的分頻器,通過編程改變分頻器的分頻比,使環路總的分頻比為N(可通過編程改變),從而環路穩定的輸出 N倍的基準頻率,而整個程序和系統的控制是要由CPU來完成的。

2020-07-23 16:47:49 2086

2086

大家都知道鎖相環很重要,它是基石,鎖相環決定了收發系統的基礎指標,那么如此重要的鎖相環選型原則有哪些呢?

2023-08-01 09:37:05 7303

7303

該文章是完全原創,用最簡潔的語言講清楚FPGA實現負反饋的精要。震撼!FPGA實現負反饋控制純數字鎖相環!.zip (225.26 KB )

2019-04-30 04:50:41

堆疊著鑒相、同相積分、中相積分、濾波等專用名詞。這些概念距離硬件設計實現數字鎖相環較遠。Div20PLL Port(clock : in std_logic; --80M local clkflow

2012-01-12 15:29:12

數字鎖相環設計源程序PLL是數字鎖相環設計源程序, 其中, Fi是輸入頻率(接收數據), Fo(Q5)是本地輸出頻率.目的是從輸入數據中提取時鐘信號(Q5), 其頻率與數據速率一致, 時鐘上升沿鎖定在數據的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

保證環路所要求的性能, 增加系統的穩定性。壓控振蕩器受濾波器輸出的電壓控制, 使得壓控振蕩器的頻率向輸入信號的頻率靠攏, 也就是使差拍頻率越來越低, 直至消除頻率差而鎖定。鎖相環在開始工作時, 通常輸入

2022-06-22 19:16:46

頻率合成器的主要性能指標鎖相環頻率合成器原理鎖相環頻率合成器捕捉過程的分析與仿真

2021-04-22 06:27:35

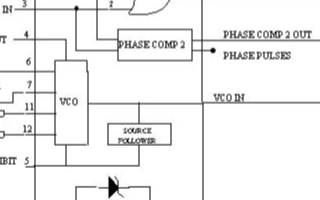

及可編程分頻器三部分組成。其中可編程分頻器是單片微機與鎖相環之間的接口,同時也是組成數字鎖相頻率合成器的關鍵部件,在移動通信陸地電臺等領域有著廣泛的應用。</p><

2010-03-16 10:59:24

硬件鎖相環和軟件鎖相環,這個很好理解,很多東西原來都是直接用硬件電路搞出來,現在有可編程器件了,再利用軟件來實現。傳統的硬件鎖相環在如諧波、頻率突變、相位突變等電壓畸變以及三相電壓不平衡情況下,很難

2015-01-04 22:57:15

ADI是高性能模擬器件供應商,在鎖相環領域已有十多的的設計經驗。到目前為止,ADI的ADF系列鎖相環產品所能綜合的頻率可達8GHz,幾乎能夠涵蓋目前所有無線通信系統的頻段。ADF系列PLL頻率合成

2018-11-06 09:03:16

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。 關鍵詞:ADF4106,鎖相環,頻率合成器,環路濾波器

2019-07-04 07:01:10

全數字鎖相環的設計及分析 1 引 言 鎖相環是一種能使輸出信號在頻率和相位上與輸入信號同步的電路,即系統進入鎖定狀態(或同步狀態)后,震蕩器的輸出信號與系統輸入信號之間相差為零,或者保持為常數

2010-03-16 10:56:10

HDL硬件描述語言對優化前后的算法進行了編碼實現。仿真和實驗結果表明,優化后的數字三相鎖相環大大節省了FPGA的資源,并能快速、準確地鎖定相位,具有良好的性能。關鍵詞:FPGA;三相鎖相環;乘法復用;CORDIC

2019-06-27 07:02:23

(DS)、鎖相環頻率合成技術(PLL)、直接數字頻率合成技術(DDS)、混合頻率合成技術四種實現方式,其中鎖相環頻率合成器是射頻電路中最常使用的一種結構,相比于其他幾種結構,PLL結構能夠在有限的功耗限制

2018-09-06 14:32:13

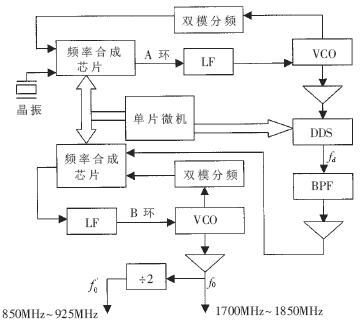

本文設計了一種多環鎖相頻率合成器。多環鎖相環路有直接數字頻率合成(DDS)環路和鎖相頻率合成環路(PLL)組成。充分利用兩個不同環路的優點,既保證了高的輸出頻率,又得到了較高的頻率分辨率。【關鍵詞

2010-05-13 09:09:53

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2019-10-10 06:12:52

。本文結合FPGA技術、鎖相環技術、頻率合成技術,設計出了一個整數/半整數頻率合成器,能夠方便地應用于鎖相環教學中,有一定的實用價值。那么有誰知道具體該如何利用FPGA設計PLL頻率合成器嗎?

2019-07-30 07:55:22

鎖相環頻率合成器是什么原理?基于CD4046的鎖相環頻率合成器的設計

2021-04-12 06:28:35

全數字鎖相環由那幾部分組成?數字鎖相環的原理是什么?如何采用VHDL實現全數字鎖相環電路的設計?

2021-05-07 06:14:44

控制用微處理器的主要性能有哪些?處理器在調頻(FM)調諧器中的應用是什么?數字調諧系統有哪些性質?怎樣去設計一種基于PLL(鎖相環)合成器的數字調諧系統?

2021-08-17 07:03:36

fpga中的用鎖相環產生時鐘信號相比于用計數器進行分頻有哪些優點,看fpga中鎖相環的結構,其前期的輸入信號和后期的輸出信號不也是通過計數器進行分頻實現的嗎

2014-10-06 10:46:05

數字鎖相環頻率合成系統的工作原理CPU控制數字鎖相環頻率合成系統FPGA實現

2021-04-09 06:20:37

大家好,我的課題是要用FPGA做一個高精度鎖相環。這個數字鎖相環的工作原理為:正弦模擬信號通過低通濾波器后,經過模數轉換器(ADC)轉化為數字信號,與NCO(數控振蕩器) 的輸出信號相乘后濾波,從而

2016-08-15 11:31:56

驅動高壓鎖相環頻率合成器電路的VCO

2021-01-11 06:02:04

用ad9850激勵的鎖相環頻率合成器山東省濟南市M0P44 部隊Q04::00R 司朝良摘要! 提出了一種ad9850和ad9850相結合的頻率合成方案! 介紹了ad9850芯片ad9850的基本工作原理" 性能特點及

2008-07-17 22:44:22 4

4 智能全數字鎖相環的設計

摘要: 在FPGA片內實現全數字

2008-08-14 22:12:51 56

56 以TRAC020LH 完全可重配置模擬器件和TRAC 開發軟件為基礎,設計模擬鎖相環;給出仿真結果和利用PIC 單片機對器件進行配置的應用電路。該鎖相環成功應用于逆變器的頻率跟蹤,性能

2009-04-15 11:42:39 11

11 智能全數字鎖相環的設計:在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智能配

2009-06-25 23:32:57 72

72 基于FPGA的全數字鎖相環設計:

2009-06-26 17:30:59 145

145

鎖相環頻率合成器:相位噪聲問題和寬帶循環:

In this chapter we locate the context of this thesis by introducing

2009-07-25 17:18:33 0

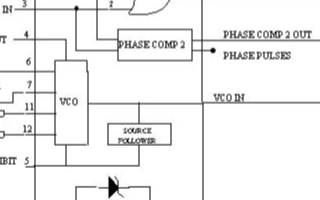

0 鎖相環頻率合成器(Motorola集成電路應用技術叢書):鎖相環路設計基礎,鑒相器,壓控振蕩器,程序分頻器,前置分頻器,單片集成鎖相環路等內容。

2009-09-05 08:20:52 0

0 鎖相環被廣泛應用于電力系統的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數字鎖相環。通過對其數學模型的分析,闡述了該鎖相環的各項性能指標與設計參數的

2010-07-02 16:54:10 30

30 本文介紹鎖相環及其頻率跟蹤的基本原理,給出二階鎖相環和四階鎖相環的設計依據。在此基礎上,對四階鎖相環實現頻率跟蹤的轉換時間進行了仿真,就如何減小頻率跟蹤的轉換時間

2010-07-29 16:28:14 44

44 鎖相環的研究和頻率合成一、實驗目的:1. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環基本特性的研究3. 利用鎖相環實現頻率合成二、鎖相環原理:

2009-03-06 20:02:52 2529

2529

實驗五? 數字鎖相環與位同步

一、?實驗目的

??? 1. 掌握數字鎖相環工作原理以及觸發式數字鎖

2009-04-01 09:27:45 6242

6242

介紹了鎖相環路的基本原理,分析了集成鎖相環芯片ADF4106的工作特性,給出了集成鎖相環芯片ADF4106的一個應用實例,為高頻頻率合成器的設計提供了很好的思路。???

2009-05-05 19:57:57 3047

3047

摘要: 在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智

2009-06-20 12:39:32 1760

1760

寬頻帶數字鎖相環的設計及基于FPGA的實現數字鎖相環(DPLL)技術在數字通信、無線電電子學等眾多領域得到了極為廣泛的應用。與傳統的模擬電路實現的

2009-11-23 21:00:58 1713

1713

單環鎖相頻率合成器,單環鎖相頻率合成器是什么意思

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統的“心臟”。現代戰爭是

2010-03-23 11:36:28 1266

1266 集成鎖相環頻率合成器,什么是集成鎖相環頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統

2010-03-23 11:45:44 956

956 數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

背景知識:

隨著數字電路技術的發展,數字鎖相環在調制解調、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 6110

6110 模擬鎖相環,模擬鎖相環原理解析

背景知識:

鎖相技術是一種相位負反饋控制技術,它利用環路的反饋原理來產生新的頻率點。它的主要

2010-03-23 15:08:20 6264

6264 鎖相環路由于具有高穩定性、優越的跟蹤性能及良好的抗干擾性,在頻率合成中得到了廣泛應用。但簡單的鎖相環路對輸出頻率、頻率分辨率等指標往往不能滿足要求,所以要對簡單鎖相環

2011-05-28 13:42:13 1355

1355

本文鑒于 數字鎖相環 在實際應用中對信號頻率的準確度和穩定度有較為嚴格的要求,設計一種應用于數字鎖相環的數控振蕩器(NCO,Number Controlled Oscillator)。基于直接數字頻率合成(

2011-08-05 14:51:05 79

79 針對擴頻通信系統的載波同步,提出一套完善的數字鎖相環設計方案. 該方案利用新穎的可控根法完成1~3階模擬鎖相環(APLL)環路參數設計,并實現從模擬域到數字域的轉換,得到的數字鎖相

2011-08-26 16:10:38 122

122 敘述了MC14046 芯片的主要特點和功能,分析了用鎖相環構成頻率合成器的工作原理,介紹了一種用MC14046 構成的新型頻率合成器。

2011-09-14 17:58:15 170

170 鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

為得到性能優良、符合實際工程的鎖相環頻率合成器,提出了一種以ADI的仿真工具ADIsimPLL為基礎,運用ADS(Advanced Design System 2009)軟件的快速設計方法。采用此方法設計了頻率輸出為

2013-01-10 16:50:36 81

81 基于FPGA的數字鎖相環設計與實現技術論文

2015-10-30 10:38:35 9

9 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 38

38 隨著數字電路技術的發展,數字鎖相環在調制解調、頻率合成、FM 立體聲解碼、彩色副載波同步、圖象處理等各個方面得到了廣泛的應用。數字鎖相環不僅吸收了數字電路可靠性高、體積小、價格低等優點,還解決了模擬

2017-09-12 16:54:55 0

0 一、設計目標 基于鎖相環的理論,以載波恢復環為依托搭建數字鎖相環平臺,并在FPGA中實現鎖相環的基本功能。 在FPGA中實現鎖相環的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統計計算,多普勒頻偏

2017-10-16 11:36:45 19

19 業界領先的射頻、微波及毫米波產品供應商美國Pasternack公司推出一系列新型USB控制鎖相環(PLL)頻率合成器。在將信號完整性作為首要目標的射頻和微波通信系統中,鎖相環頻率合成器可提供高頻率

2018-04-26 11:16:00 1104

1104 鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。

2019-09-20 07:05:00 4322

4322

隨著集成電路技術的不斷進步,數字化應用逐漸普及,在數字通信、電力系統自動化等方面越來越多地運用了數字鎖相環。它的好處在于免去了模擬器件的繁瑣,而且成本低、易實現、省資源。本文綜合以上考慮,在一片FPGA中以Quartus II為平臺用VHDL實現了一個全數字鎖相環功能模塊,構成了片內鎖相環。

2020-07-16 09:16:08 3429

3429

鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環通常

2020-08-06 17:58:25 26

26 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 66

66 本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 20

20 CN-0369:低相位噪聲的轉換鎖相環頻率合成器

2021-03-20 13:21:15 7

7 鎖相環路誕生于20世紀30年代。近年來,鎖相技術在通信、航天、測量、電視、原子能、電機控制等領域,能夠高性能地完成信號的提取、信號的跟蹤與同步,模擬和數字通信的調制與解調、頻率合成、濾波等功能

2021-03-31 11:59:11 6328

6328

UG-369:ADF4151鎖相環頻率合成器評估板

2021-04-19 20:14:47 6

6 UG-802:用于鎖相環的ADF5355頻率合成器評估

2021-04-25 12:23:05 4

4 UG-383:用于鎖相環的ADF4159頻率合成器評估

2021-05-10 13:26:06 2

2 UG-1087:用于鎖相環的ADF5356頻率合成器評估

2021-05-17 09:38:07 10

10 用鎖相環實現超快頻率切換

2021-05-18 20:29:01 9

9 UG-686:ADF4155鎖相環頻率合成器評估板

2021-05-25 16:46:51 4

4 所設計的頻率合成器,要求相位噪聲低,輸出頻率800~1 000 MHz,共88個波道,通過單片機發送的頻率控制字進行波道選擇。在對比各種大規模集成頻率合成芯片性能的基礎上,選用了單片大規模集成鎖相環頻率合成芯片PE3236作為核心電路,構成鎖相式頻率合成器。

2021-05-28 10:30:08 5925

5925

基于FPGA的寬頻帶數字鎖相環的設計與實現簡介說明。

2021-06-01 09:41:14 26

26 ADF4150HV鎖相環頻率合成器UG-406評估板

2021-06-03 11:16:33 10

10 基于FPGA的高性能全數字鎖相環

2021-06-08 11:09:01 46

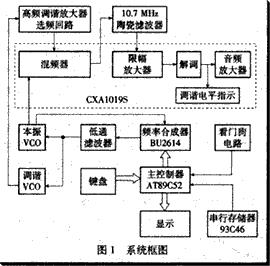

46 數字調諧系統是現代收發信機的核心,其性能直接影響通信質量的好壞,其主要部分是集成鎖相式頻率合成器。集成鎖相環與微處理器結合,可由微機控制完成頻率合成器的全部功能。

2021-06-14 17:29:00 5078

5078

鎖相環(PLL)電路是由壓控振蕩器(VCO)和鑒相器組成的反饋系統,振蕩器信號跟蹤施加的頻率或相位調制信號是否具有正確的頻率和相位。需要從固定低頻率信號生成穩定的高輸出頻率時,或者需要頻率快速變化時,都可以使用PLL。典型應用包括采用高頻率、電信和測量技術實現濾波、調制和解調,以及實現頻率合成。

2022-06-13 16:14:35 5580

5580 鎖相環的鎖定是指鎖相環的輸出頻率等于輸入頻率,而輸出信號的相位跟隨輸入信號的變化而變化。

2023-01-31 16:31:12 4097

4097 模擬鎖相環和數字鎖相環的主要區別在于它們的控制方式不同。模擬鎖相環是通過模擬電路來控制頻率和相位,而數字鎖相環是通過數字信號處理技術來控制頻率和相位。此外,模擬鎖相環的精度較低,而數字鎖相環的精度較高。

2023-02-15 13:47:53 6625

6625 鎖相環頻率合成器的優缺點? 鎖相環頻率合成器,又稱為PLL(Phase Locked Loop),是一種廣泛應用的電路,能夠將輸入信號的頻率合成為電路所需要的頻率,并且能夠實現對信號的相位和頻率

2023-09-02 14:59:33 3701

3701 鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 5114

5114 如何調試鎖相環頻率合成器?? 鎖相環頻率合成器(PLL)是電路中常見的一個模塊,用于生成穩定的高精度頻率信號。PLL的核心部分是相位檢測器和環路濾波器,其主要工作原理是通過不斷調整反饋回來的參考信號

2023-09-02 15:06:37 1899

1899 鎖相環(Phase Locked Loop, PLL)是一種廣泛應用于通信系統、頻率合成、數字信號處理等領域的關鍵電路。本文將介紹鎖相環的基本原理、分類及應用,以期幫助讀者更好地理解和掌握這一技術。

2023-09-14 17:29:12 12300

12300 基本PLL鎖相環、整數型頻率合成器和分數型頻率合成器。下面將詳細介紹這三種模式的作用和特點。 第一種:基本PLL鎖相環 基本PLL鎖相環是PLLf工作的最基本形式,它主要由比較器、低通濾波器、VCO和分頻器組成。其基本工作原理是將輸入信號和VCO輸出的信號進行

2023-10-13 17:39:48 5281

5281 比較,通過不斷調整內部振蕩器的頻率,使得輸出信號的相位與參考信號的相位保持一致,從而實現同步。鎖相環廣泛應用于數字通信、音頻解碼、數字信號處理等領域。 在鎖相環的基本結構中,包含一個相位檢測器、一個積分環節、一個低通濾波器和一個控制振蕩器。參考

2023-10-13 17:39:53 3088

3088 軟件鎖相環在頻率突變時鎖不住 鎖相環無法鎖定怎么辦?? 鎖相環(PLL)是一種用于在電路中生成穩定頻率的技術。它是在1960年代開發的,并被廣泛應用于通信、雷達、衛星技術等領域中。鎖相環的主要作用

2023-10-13 17:39:58 3085

3085 電子發燒友網站提供《基于ADF4111的鎖相環頻率合成器設計.pdf》資料免費下載

2023-10-20 14:45:29 4

4 數字鎖相環(DigitalPhase-LockedLoop,簡稱DPLL)是一種基于反饋控制的技術,用于實現精確的時序控制和相位同步。通過相位比較、頻率差計算、頻率控制、濾波和循環控制,它能夠完成

2024-01-02 17:20:25 3358

3358

頻率合成器和鎖相環是兩種常見的電子設備,用于生成穩定的頻率信號。盡管它們的功能都是產生特定頻率的信號,但它們在工作原理和應用方面有著明顯的區別。

2024-02-27 18:22:59 2092

2092 鎖相環頻率合成器(Phase-Locked Loop Frequency Synthesizer, PLLFS)是一種利用鎖相環(Phase-Locked Loop, PLL)技術實現頻率合成的裝置。其基本原理基于相位負反饋控制系統,通過調整輸出信號的相位和頻率,使其與參考信號的相位和頻率保持同步。

2024-08-05 15:01:43 2292

2292 在現代電子系統中,頻率控制和信號生成是至關重要的。鎖相環(PLL)和頻率合成器是實現這些功能的兩種關鍵技術。盡管它們在某些應用中可以互換使用,但它們在設計、工作原理和應用領域上存在顯著差異。 一

2024-11-06 10:46:53 1812

1812 鎖相環(Phase-Locked Loop,簡稱PLL)是一種廣泛應用于電子系統中的反饋控制系統,主要用于頻率合成和相位同步。本文將從鎖相環的工作原理、基本組成、應用案例以及設計考慮等方面進行詳細闡述,以幫助讀者全面理解這一重要技術。

2025-02-03 17:48:00 2319

2319

電子發燒友App

電子發燒友App

評論