FPGA的功耗由4部分組成:上電功耗、配置功耗、靜態(tài)功耗和動(dòng)態(tài)功耗。一般的FPGA都具有這4種功耗,但是Actel Flash FPGA由于掉電數(shù)據(jù)不丟失,無(wú)需配置芯片,所以上電后不需要一個(gè)很大的啟動(dòng)電流,也不需要配置過(guò)程,只有靜態(tài)功耗和動(dòng)態(tài)功耗,沒有上電功耗和配置功耗。

2024-07-18 11:11:00 3195

3195

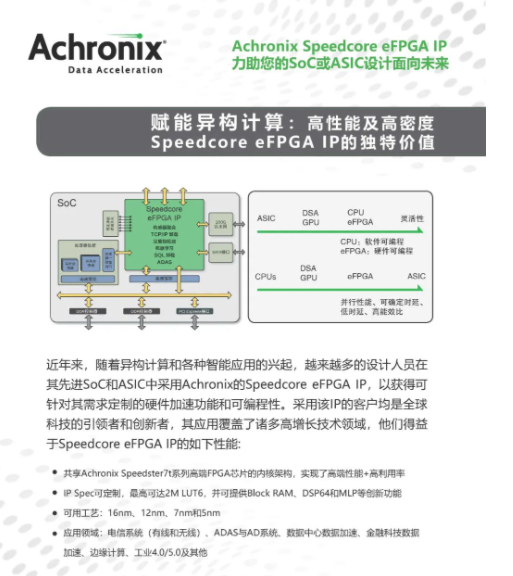

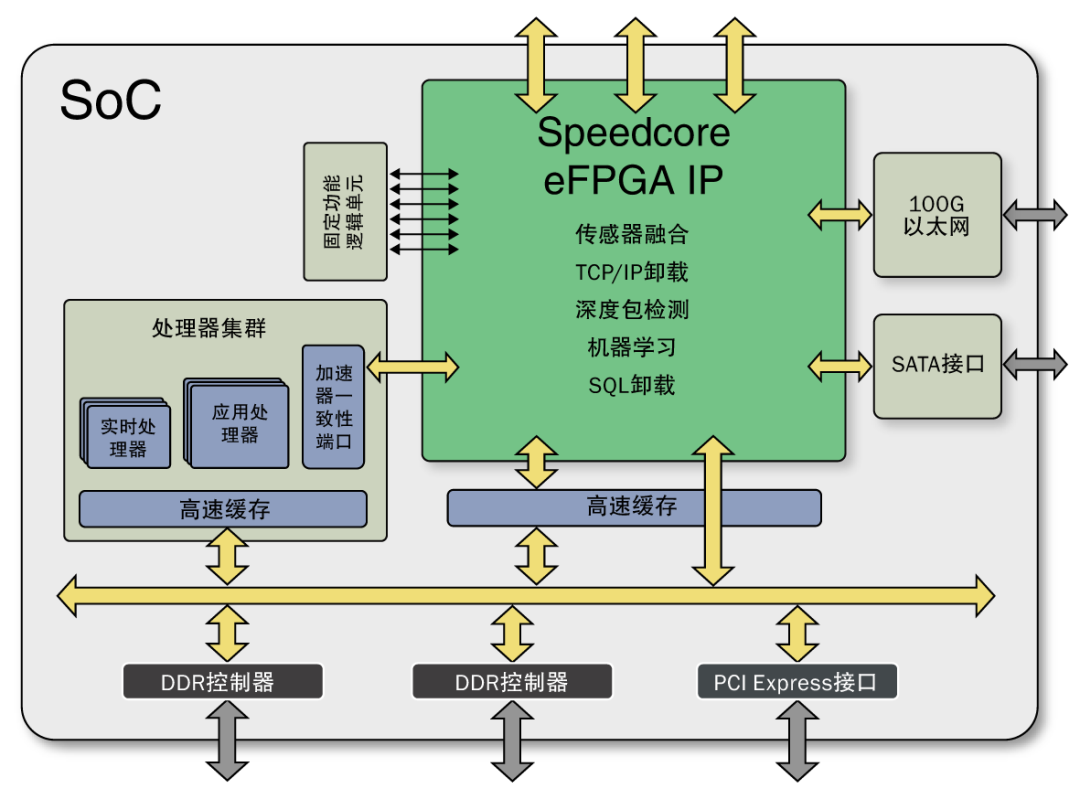

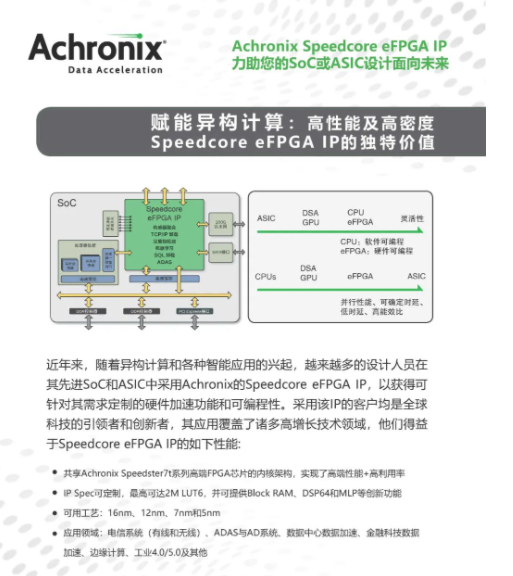

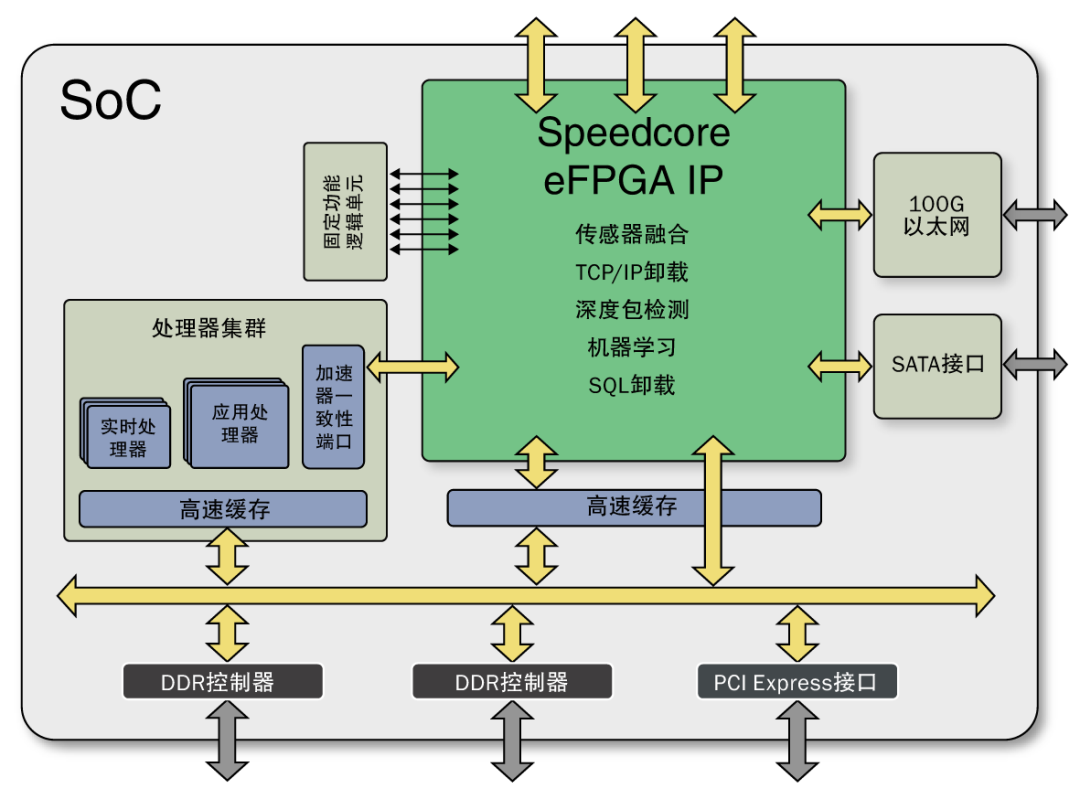

【導(dǎo)讀】為了滿足人工智能、機(jī)器學(xué)習(xí)、無(wú)人駕駛、ADAS等應(yīng)用提出的越來(lái)越高的特殊計(jì)算需求,Achronix宣布為其eFPGA IP解決方案推出Speedcore定制單元塊,這是一種可以將功耗和面積降至最低、同時(shí)將數(shù)據(jù)流通量最大化的解決方案。

2017-10-19 11:28:32 1378

1378 待機(jī)功耗、高效率、動(dòng)態(tài)紋波小優(yōu)異線性調(diào)整率和負(fù)載調(diào)整率內(nèi)置抖頻電路抗干擾能力強(qiáng)內(nèi)置150V MOSESOP8封裝【帶抖頻電路,抗干擾能力強(qiáng),有效解決EMC問(wèn)題,外圍簡(jiǎn)潔,有效縮減外圍布板體積】【帶線損補(bǔ)償,空載帶載電壓一致性高,高低壓輸入情況輸出電壓穩(wěn)定,恒壓精度高】

2021-03-18 16:04:00

面積縮減了50%,賽靈思FPGA芯片在升級(jí)中,功耗和性能平衡得非常好。 (2)Kintex-7 FPGA 系列——業(yè)界最佳性價(jià)比 堪稱“業(yè)界性價(jià)比之王”的Kintex-7 FPGA 系列,能以不到

2012-09-21 13:46:16

FPGA功耗的基本概念,如何降低

FPGA功耗?IGLOO能夠做到如此低的

功耗是因?yàn)槭裁矗?/div>

2021-04-30 06:08:49

`FPGA面積優(yōu)化1.對(duì)于速度要求不是很高的情況下,我們可以把流水線設(shè)計(jì)成迭代的形式,從而重復(fù)利用FPGA功能相同的資源。2.對(duì)于控制邏輯小于共享邏輯時(shí),控制邏輯資源可以用來(lái)復(fù)用,例如FIR濾波器

2014-12-04 13:52:40

FPGA已經(jīng)被廣泛用于實(shí)現(xiàn)大規(guī)模的數(shù)字電路和系統(tǒng),隨著CMOS工藝發(fā)展到深亞微米,芯片的靜態(tài)功耗已成為關(guān)鍵挑戰(zhàn)之一。文章首先對(duì)FPGA的結(jié)構(gòu)和靜態(tài)功耗在FPGA中的分布進(jìn)行了介紹。接下來(lái)提出了晶體管

2020-04-28 08:00:00

FPGA提供了更加高效的功能。總體上看,采用這些模塊節(jié)約了常規(guī)邏輯資源并增加了系統(tǒng)執(zhí)行的速度,同時(shí)可以減少系統(tǒng)功耗。因此更高的邏輯效率也意味著能夠?qū)崿F(xiàn)更小的器件設(shè)計(jì),并進(jìn)一步降低靜態(tài)功耗和系統(tǒng)成本

2015-02-09 14:58:01

。可編程功能支持靈活的通信標(biāo)準(zhǔn)和網(wǎng)絡(luò)協(xié)議。圖3應(yīng)用實(shí)例:下一代驅(qū)動(dòng)單芯片方法明顯增強(qiáng)了性能,降低了功耗。在驅(qū)動(dòng)系統(tǒng)中,控制環(huán)速率是最關(guān)鍵的性能參數(shù)。SoCFPGA控制環(huán)速率是多芯片解決方案的20倍,從100

2021-07-14 08:00:00

滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。作為矛盾的兩個(gè)組成部分,面積

2021-07-25 11:09:06

滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。作為矛盾的兩個(gè)組成部分,面積

2021-07-26 14:47:48

滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。作為矛盾的兩個(gè)組成部分,面積

2021-11-22 10:04:03

滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。作為矛盾的兩個(gè)組成部分,面積

2021-07-09 14:34:18

滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。作為矛盾的兩個(gè)組成部分,面積

2021-08-10 14:51:33

滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。作為矛盾的兩個(gè)組成部分,面積

2020-08-02 10:45:07

。

極簡(jiǎn)外圍電路設(shè)計(jì),大幅縮減 PCB 面積與 BOM 成本,同時(shí)兼顧寬輸入、高效率、靈活配置與全面保護(hù),Hi8001/Hi8002 系列芯片廣泛適用于工業(yè)控制、消費(fèi)電子、物聯(lián)網(wǎng)設(shè)備等升壓恒壓電源場(chǎng)景,助力工程師快速實(shí)現(xiàn)高可靠性、高性價(jià)比的電源方案落地。

2025-12-05 17:42:29

LED屏幕點(diǎn)白平是,芯片比別的模組溫度更高些,是什么原因啊,請(qǐng)大俠指點(diǎn)指點(diǎn)。

2011-12-04 19:26:52

你好。我正在寫一篇技術(shù)論文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的資源。資源可以是晶體管數(shù)量,柵極數(shù),芯片面積大小等等。我在一個(gè)網(wǎng)站上聽說(shuō)LUT需要2.5倍的“FPGA門”,但

2019-02-27 13:49:58

請(qǐng)教各位,LabVIEW 2010為什么可以實(shí)現(xiàn)更高效的測(cè)量?

2021-04-26 07:15:49

,獲得的縱向電場(chǎng)分布幾乎是恒定的,而給定擊穿電壓所需的漂移區(qū)長(zhǎng)度大幅降低。與此同時(shí),漂移區(qū)的雜質(zhì)濃度提高。這兩種技術(shù)都可導(dǎo)致通態(tài)電阻的大幅降低。擴(kuò)展器件系列,實(shí)現(xiàn)更高阻斷能力占板空間更小的全新高效邊緣終端

2018-12-07 10:21:41

小弟剛學(xué)FPGA ,在看Veriolg ,遇到縮減運(yùn)算符,對(duì)于縮減與 縮減或能理解,那個(gè)非本身就是單目運(yùn)算,縮減非是怎么回事呢?

2013-10-07 10:13:36

存儲(chǔ)器訪問(wèn)次數(shù)減少,降低 Flash 讀取功耗(Flash 訪問(wèn)是系統(tǒng)功耗的重要來(lái)源)。

更小代碼量還可選用容量更小的 Flash,進(jìn)一步降低芯片整體功耗。

6. 物理設(shè)計(jì)優(yōu)化

芯片面積更小:M0+

2025-11-19 08:15:55

從Xilinx公司推出FPGA二十多年來(lái),研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實(shí)現(xiàn)數(shù)字電路的優(yōu)選平臺(tái)。今天,功耗日益成為FPGA供應(yīng)商及其

2019-09-20 06:33:32

,工業(yè)界對(duì)芯片設(shè)計(jì)的要求已從單純追求高性能、小面積轉(zhuǎn)為對(duì)性能、面積、功耗的綜合要求。而微處理器作為數(shù)字系統(tǒng)的核心部件,其低功耗設(shè)計(jì)對(duì)降低整個(gè)系統(tǒng)的功耗具有重要的意義。

2019-10-14 07:48:14

,更高效的處理視頻; e. 通過(guò)CODEC和1080p視頻工作臺(tái)IP內(nèi)核提供全面的解決方案。 2 Arria V系列:中端市場(chǎng)最佳性價(jià)比之王 2.1 Arria V系列 FPGA芯片基本描述

2012-09-21 13:49:05

在微功耗場(chǎng)景下,使用RCC是否比低功耗芯片的效率更高?設(shè)計(jì)例子:?jiǎn)位鹑‰婍?xiàng)目,從AC線取電取電,交流220V轉(zhuǎn)直流12V,再通過(guò)DC-DC方案,將12V轉(zhuǎn)為3.3V供Zigbee工作,該Zigbee

2016-06-17 13:50:42

。可編程功能支持靈活的通信標(biāo)準(zhǔn)和網(wǎng)絡(luò)協(xié)議。圖3應(yīng)用實(shí)例:下一代驅(qū)動(dòng)單芯片方法明顯增強(qiáng)了性能,降低了功耗。在驅(qū)動(dòng)系統(tǒng)中,控制環(huán)速率是最關(guān)鍵的性能參數(shù)。SoCFPGA控制環(huán)速率是多芯片解決方案的20倍,從100

2021-07-12 08:00:00

方面滿足DSP應(yīng)用的需要。然而在應(yīng)用FPGA進(jìn)行系統(tǒng)設(shè)計(jì)綜合過(guò)程中,選擇芯片的運(yùn)行速度優(yōu)化和資源利用優(yōu)化常常是相互矛盾的,對(duì)速度指標(biāo)要求高的設(shè)計(jì)優(yōu)化常常要占用較大的芯片資源,而減小芯片面積的設(shè)計(jì)又需要

2019-08-02 06:03:48

STM32定時(shí)器的功能包括哪些呢?如何更高效的去實(shí)現(xiàn)STM32按鍵和延時(shí)功能呢?

2021-11-23 07:59:06

的提高,光收發(fā)器模塊的功耗勢(shì)必增大,同時(shí)其外形尺寸需要保持不變。這就給模塊設(shè)計(jì)工程師帶來(lái)巨大壓力,要求其使用低功耗、高度集成的芯片。那么如何在狹小空間內(nèi)提供更多功能的同時(shí)實(shí)現(xiàn)更高效地供電?本設(shè)計(jì)方案提出一種創(chuàng)新的電源管理系統(tǒng),能夠以較小的空間高效供電,且滿足下一代光收發(fā)器的需求。

2021-02-24 06:22:34

和寬厚比公式做為一名 SMT 工藝工程師,即使已知“面積比和寬厚比的最佳條件”,但面對(duì)成千上萬(wàn)的開口,在沒有專業(yè)工具軟件的前提下,要想實(shí)現(xiàn)“驗(yàn)證每一個(gè)開口是否符合 IPC7525 標(biāo)準(zhǔn)”是極其不現(xiàn)實(shí)

2021-07-01 13:46:58

器件的功耗更低,能以更高的速度工作,有更高的性能(2倍的帶寬),并有更大的密度。與DDR2相比,DDR3器件的功耗降低了30%,主要是由于小的芯片尺寸和更低的電源電壓(DDR3 1.5V而DDR2

2019-08-09 07:42:01

MCU和電源的選擇讓您的嵌入式電路設(shè)計(jì)更高效

2021-04-02 07:16:43

同時(shí)具備設(shè)計(jì)面積最小、運(yùn)行頻率最高是不現(xiàn)實(shí)的。更科學(xué)的設(shè)計(jì)目標(biāo)應(yīng)該是在滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高

2020-09-18 10:32:44

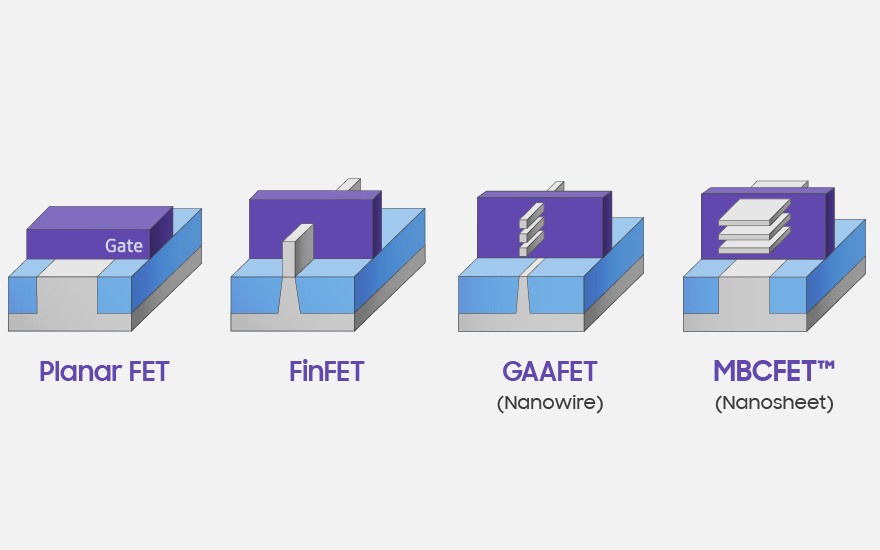

1.工藝節(jié)點(diǎn) 首先不管選擇什么廠家的產(chǎn)品,都建議在其主流產(chǎn)品中選擇合適的芯片。 以上是目前 Xilinx 主流的也是常用的幾個(gè) FPGA 產(chǎn)品系列,這里不談傳說(shuō)中的后兩個(gè)系列

2020-12-23 17:21:03

ADAU1850相比上款產(chǎn)品擁有極小的芯片面積,超強(qiáng)音質(zhì)ANC codec,以更低的成本提供更精確降噪的可能。ADAU1850詳細(xì)參數(shù)特征:1、28pin,0.4 mm pitch, 3.0 mm

2021-08-23 11:12:42

的小型化,從而大大縮減安裝面積。(*截至2016年11月18日ROHM調(diào)查數(shù)據(jù))通過(guò)輸出電壓的線性控制,使電機(jī)旋轉(zhuǎn)速度的精度更高以往的分立結(jié)構(gòu)存在相對(duì)于外部MCU生成的PWM信號(hào)來(lái)說(shuō)輸出電壓的線性度較低

2018-12-04 10:18:47

請(qǐng)教下,誰(shuí)能夠推薦一款比 cc1100 功耗更低的芯片 ?

2020-08-20 08:00:30

芯片靜態(tài)功耗;2. 設(shè)計(jì)靜態(tài)功耗;3. 設(shè)計(jì)動(dòng)態(tài)功耗。l芯片靜態(tài)功耗:FPGA在上電后還未配置時(shí),主要由晶體管的泄露電流所消耗的功耗l設(shè)計(jì)靜態(tài)功耗:當(dāng)FPGA配置完成后,當(dāng)設(shè)計(jì)還未啟動(dòng)時(shí),需要維持I

2014-08-21 15:31:23

和期望輸出電壓的規(guī)范,并且需要選擇一些 FET。另外,如果您是一名 IC 設(shè)計(jì)人員,則您還會(huì)有一定的預(yù)算,其規(guī)定了 FET 成本或者封裝尺寸。這兩種輸入會(huì)幫助您選擇總 MOSFET 芯片面積。之后

2018-09-26 10:24:59

管殼到環(huán)境的熱阻隨芯片面積只有很小的變化。●但是,TO220和TO247具有不同的管殼到環(huán)境的熱阻(水平線)。由于TO220與環(huán)境相連的引線架的面積大了許多,因此TO220的值(1.4K/W)幾乎比

2018-12-03 13:46:13

在汽車電子系統(tǒng)中,功耗管理是一個(gè)關(guān)鍵問(wèn)題。如何優(yōu)化芯源車規(guī)級(jí)CW32A030C8T7芯片的功耗管理,實(shí)現(xiàn)更高效的能源利用,延長(zhǎng)汽車電池壽命?

2025-12-16 07:15:10

請(qǐng)問(wèn)圖中字樣的三極管芯片面積是多大?謝謝

2014-05-08 17:07:35

成本 通過(guò)表1我們不難得出以下結(jié)論: 與上一代 FPGA相比,其功耗降低了50%,成本削減了35%,性能提高30%,占用面積縮減了50%,賽靈思FPGA芯片在升級(jí)中,功耗和性能平衡得非常好。 (2

2012-09-06 16:24:35

高度集成的單芯片射頻收發(fā)器解決方案 (例如,ADI 推出的 ADRV9008/ADRV9009 產(chǎn)品系列) 的面市促成了此項(xiàng)成就。在此類系統(tǒng)的 RF 前端部分仍然需要實(shí)現(xiàn)類似的集成,意在降低功耗 (以改善熱管理) 和縮減尺寸(以降低成本),從而容納更多的 MIMO 通道。

2019-07-31 07:05:44

自從Xilinx推出FPGA二十多年來(lái),研發(fā)工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實(shí)現(xiàn)數(shù)字電路的優(yōu)選平臺(tái)。今天,功耗日益成為FPGA供應(yīng)商及其客戶關(guān)注的問(wèn)題。降低FPGA功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移

2011-03-15 14:58:34 31

31 意法半導(dǎo)體(STMicroelectronics, ST) 日前發(fā)布全新微型封裝技術(shù) SMBflat ,據(jù)稱比 SOT-223 封裝薄40%,能有效縮減50%的印刷電路板占板面積

2011-03-28 11:39:30 1590

1590 Virtex-5 器件包括基于第二代高級(jí)硅片組合模塊 (ASMBL) 列架構(gòu)的多平臺(tái) FPGA 系列。集成了為獲得最佳性能、更高集成度和更低功耗設(shè)計(jì)的若干新型架構(gòu)元件,Virtex-5 器件達(dá)到了比以往更高

2012-02-17 14:39:56 51

51 集成電路晶圓代工企業(yè)中芯國(guó)際集成電路制造有限公司(“中芯國(guó)際”)日前宣布,其0.11微米后段銅制程(Cu-BEoL)超高密度IP庫(kù)解決方案可為客戶平均節(jié)省31%芯片面積。

2012-03-12 09:14:40 1490

1490 白皮書 :采用低成本FPGA實(shí)現(xiàn)高效的低功耗PCIe接口 了解一個(gè)基于DDR3存儲(chǔ)器控制器的真實(shí)PCI Express (PCIe) Gen1x4參考設(shè)計(jì)演示高效的Cyclone V FPGA怎樣降低系統(tǒng)總成本,同時(shí)實(shí)現(xiàn)性能和功耗

2013-02-26 10:04:25 73

73 基于ARM? 微控制器單元(MCU)的功耗大幅降低了50%。Silicon Labs表示,搭載了ARM Cortex?-M4核心的新款EFM32 Wonder Gecko,比競(jìng)爭(zhēng)對(duì)手MCU要少消耗50%的功耗,即使運(yùn)行在更高的溫度,也能延長(zhǎng)電池使用時(shí)間。

2013-09-25 09:59:51 1221

1221 Achronix Semiconductor公司今日宣布:推出可集成至客戶系統(tǒng)級(jí)芯片(SoC)中的Speedcore? 嵌入式FPGA(embedded FPGA ,eFPGA)知識(shí)產(chǎn)權(quán)(IP)產(chǎn)品,并即刻開始向客戶供貨。

2016-10-11 18:12:01 3091

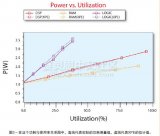

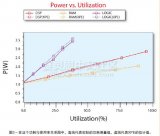

3091 有一種新方法可用于測(cè)量真實(shí)FPGA器件的功耗估計(jì)值 現(xiàn)代的FPGA 芯片能夠開發(fā)高性能應(yīng)用,但在這些設(shè)計(jì)中電源管理通常是一大限制因素。FPGA 器件的資源使用最能決定設(shè)計(jì)的容量和處理速度,但是增加

2017-11-18 01:14:02 8016

8016

的數(shù)量,可以用消耗的觸發(fā)器和查找表的個(gè)數(shù)或者是等效邏輯門數(shù)來(lái)衡量;速度是指一個(gè)設(shè)計(jì)在FPGA上穩(wěn)定運(yùn)行時(shí)所能 達(dá)到的最高頻率,由設(shè)計(jì)時(shí)序狀態(tài)決定。 關(guān)于面積和速度的折衷,應(yīng)在滿足設(shè)計(jì)時(shí)序和工作頻率要求的前提下,占用最小的芯片面積;或者在所規(guī)定

2017-11-25 03:57:01 1471

1471

要點(diǎn):

術(shù)量產(chǎn)級(jí)測(cè)試芯片的驗(yàn)證

Speedcore驗(yàn)證芯片通過(guò)了嚴(yán)格的整套測(cè)試,同時(shí)所有功能已獲驗(yàn)證

在所有的運(yùn)行條件下,復(fù)雜的設(shè)計(jì)均可運(yùn)行在500MHz速率

2018-01-19 15:02:33 8524

8524

隨著芯片集成度越來(lái)越高,隨機(jī)存儲(chǔ)器(random access memory,RAM)在片上系統(tǒng)(system on chip,SoC)中的占比也越來(lái)越高,因此RAM對(duì)SoC的面積及功耗的貢獻(xiàn)也

2018-01-19 15:27:13 1

1 工智能(AI)/機(jī)器學(xué)習(xí)、5G移動(dòng)通信、汽車先進(jìn)駕駛員輔助系統(tǒng)(ADAS)、數(shù)據(jù)中心和網(wǎng)絡(luò)應(yīng)用; Speedcore custom blocks定制單元塊可以大幅度地提升性能、功耗和面積效率,并支持以前在FPGA獨(dú)立芯片上無(wú)法實(shí)現(xiàn)的功能。

2018-01-22 16:42:01 1116

1116 由于FPGA具有可編程專用性,高性能及低功耗的特點(diǎn),浪潮推出基于FPGA的深度學(xué)習(xí)加速解決方案,希望通過(guò)更高配置的硬件板卡設(shè)計(jì)和內(nèi)置更高效已編譯算法,來(lái)加速FPGA在人工智能領(lǐng)域的應(yīng)用。

2018-02-19 05:02:00 933

933 芯片面積估計(jì)就是通過(guò)目標(biāo)工藝的庫(kù)信息,設(shè)計(jì)的spec、以往設(shè)計(jì)的信息及,部分IP的綜合報(bào)告來(lái)統(tǒng)計(jì)這主要部分的總面積的過(guò)程。

2018-04-25 15:36:59 11936

11936 不過(guò)在聯(lián)發(fā)科副總經(jīng)理暨智能設(shè)備事業(yè)群總經(jīng)理游人杰看來(lái),雖然CPU、GPU等通用型芯片以及FPGA可以適應(yīng)相對(duì)更多種的算法,但是特定算法下ASIC的性能和效能要更高。另外,雖然FPGA的便定制特性比ASIC芯片更加靈活,但部署FPGA所付出的成本也要比ASIC更高。

2018-05-04 15:39:03 255520

255520

Imagination公司日前基于其神經(jīng)網(wǎng)絡(luò)加速器(NNA)架構(gòu)PowerVR 2NX推出了兩款全新的神經(jīng)網(wǎng)絡(luò)內(nèi)核AX2185和AX2145,其設(shè)計(jì)目的是在極小芯片面積上以極低功耗實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)高性能計(jì)算。

2018-06-20 10:50:04 4522

4522

美高森美公司(Microsemi) 宣布為其主流SERDES-based SmartFusion 2 系統(tǒng)級(jí)芯片(SoC) FPGA和IGLOO 2 FPGA器件提供全新小尺寸解決方案。這兩款

2018-09-19 16:14:00 1785

1785 該組項(xiàng)目將使研究機(jī)構(gòu)和公司能夠使用Achronix高性能Speedcore eFPGA技術(shù)快速構(gòu)建低成本測(cè)試芯片

2018-12-01 08:25:37 3637

3637 %、功耗降低了50%、芯片面積減少65%,同時(shí)保留了原有的Speedcore eFPGA IP的功能,即可將可編程硬件加速功能引入廣泛的計(jì)算、網(wǎng)絡(luò)和存儲(chǔ)應(yīng)用,實(shí)現(xiàn)接口協(xié)議橋接/轉(zhuǎn)換、算法加速和數(shù)據(jù)包處理。

2018-12-10 17:28:00 990

990 2016年,Achronix推出的Speedcore成為首款向客戶出貨的嵌入式FPGA(eFPGA)IP,使客戶將FPGA功能集成到他們的SoC中成為可能。由于Speedcore IP是專為計(jì)算

2018-12-23 16:29:40 5164

5164 和公司能夠全面對(duì)接Achronix領(lǐng)先Speedcore eFPGA技術(shù)。 eFPGA技術(shù)正在迅速地成為基于系統(tǒng)級(jí)芯片(SoC)的CPU卸載功能中可編程硬件加速單元的必備硅知識(shí)產(chǎn)權(quán)(IP),已被廣泛用于包括人工智能/機(jī)器學(xué)習(xí)(AI / ML)、區(qū)塊鏈、網(wǎng)絡(luò)加速、智能網(wǎng)卡和智能物聯(lián)網(wǎng)等各種應(yīng)用。這些被

2018-12-24 14:47:29 1459

1459 2019 年 12 月 10 日——萊迪思半導(dǎo)體公司(NASDAQ:LSCC),低功耗可編程器件的領(lǐng)先供應(yīng)商,今日宣布推出全新低功耗 FPGA 技術(shù)平臺(tái)——Lattice Nexus?。該技術(shù)平臺(tái)

2019-12-11 15:05:51 1298

1298 英國(guó)格拉斯哥大學(xué)稱,該校科學(xué)家通過(guò)使用現(xiàn)場(chǎng)可編程邏輯門陣列(FPGA)芯片系統(tǒng),能夠以高出目前標(biāo)準(zhǔn)處理器20倍的速度完成文檔檢索,可大幅降低使用網(wǎng)絡(luò)搜索的碳排放量,從而向構(gòu)建“綠色節(jié)能網(wǎng)絡(luò)”又邁進(jìn)一步。

2020-07-20 18:04:56 878

878 降低了50%,芯片面積減少了65%,同時(shí)保留了Speedcore eFPGA IP的原有功能,將可編程硬件加速功能帶到廣泛的高性能計(jì)算、網(wǎng)絡(luò)和存儲(chǔ)應(yīng)用中。Achronix將于9月26日參加在圣克拉拉市

2020-08-07 15:41:06 937

937 要求一個(gè)同時(shí)具備設(shè)計(jì)面積最小、運(yùn)行頻率最高是不現(xiàn)實(shí)的。更科學(xué)的設(shè)計(jì)目標(biāo)應(yīng)該是在滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率的要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,是設(shè)計(jì)的時(shí)序余量更大、頻率跑的更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡的思想。

2020-11-29 10:58:59 2097

2097 Achronix Speedcore eFPGA IP使客戶公司能夠?qū)?b class="flag-6" style="color: red">FPGA功能集成到其ASIC或SoC器件中。 Speedcore eFPGA具有可變換的架構(gòu),它可讓客戶根據(jù)需求去定義eFPGA IP的FPGA邏輯陣列、存儲(chǔ)器和DSP處理能力。

2021-03-26 10:18:54 2333

2333 葉片是植物進(jìn)行光合作用合成有機(jī)物的重要器官,它的面積大小對(duì)農(nóng)作物產(chǎn)量具有重要影響。 另外,在農(nóng)業(yè)科研中,許多生理指標(biāo)的測(cè)定和研究也都會(huì)涉及到葉面積。早期測(cè)定植物葉片面積,往往需要通過(guò)畫格子、稱重

2021-08-02 18:08:50 1697

1697 托普云農(nóng)設(shè)計(jì)研發(fā)生產(chǎn)的YMJ-B植物葉面積儀,該儀器更適合狹長(zhǎng)葉片的活體測(cè)量,能夠獲得葉片面積、長(zhǎng)度、寬度、長(zhǎng)寬比、葉片周長(zhǎng)及形狀因子參數(shù)。

2021-11-10 17:32:44 805

805 要求同時(shí)具備設(shè)計(jì)面積最小、運(yùn)行頻率最高是不現(xiàn)實(shí)的。更科學(xué)的設(shè)計(jì)目標(biāo)應(yīng)該是在滿足設(shè)計(jì)時(shí)序要求(包括對(duì)設(shè)計(jì)頻率要求)的前提下,占用最小的芯片面積。或者在所規(guī)定的面積下,使設(shè)計(jì)的時(shí)序余量更大、頻率跑得更高。這兩種目標(biāo)充分體現(xiàn)了面積和速度的平衡思想。

2022-04-15 16:59:15 2534

2534 在查看芯片面積時(shí),智能手機(jī)和可穿戴設(shè)備中的小尺寸設(shè)計(jì)將明顯受益于基于軟件的基帶實(shí)現(xiàn)所實(shí)現(xiàn)的芯片面積減少。

2022-06-29 10:23:38 1489

1489 芯片版圖設(shè)計(jì)是一項(xiàng)精密的工作,設(shè)計(jì)時(shí)需要綜合考慮芯片面積、性能和功耗。版圖設(shè)計(jì)人員試圖在最小化芯片區(qū)域的同時(shí),盡可能縮短布線長(zhǎng)度,避免走線擁擠,并滿足時(shí)間要求和其他設(shè)計(jì)標(biāo)準(zhǔn)。總體目標(biāo)是實(shí)現(xiàn)芯片性能、功耗和成本的最優(yōu)組合。

2022-09-07 17:05:15 1493

1493 卻越來(lái)越大。為了減少芯片面積、降低芯片成本、減少芯片功耗,逐漸地提升了芯片的工藝,從而降低了功耗,提升了能耗比。光靠工藝的提升來(lái)減少功耗,還不夠。為了更好地功耗管理,ARM提出了功耗控制系統(tǒng)架構(gòu)

2022-11-30 09:05:00 3317

3317 相對(duì)于FPGA+SoC的方案,集成了eFPGA的SoC或者ASIC將在功耗、單位成本、延遲和連接帶寬方面獲得巨大收益,其價(jià)值已經(jīng)得到全球數(shù)十家頂級(jí)創(chuàng)新公司驗(yàn)證。

2022-12-23 10:21:14 820

820

(Flip-Flop)和查找表(Look Up Table)等資源。在FPGA設(shè)計(jì)過(guò)程中,速度的提高通常以面積擴(kuò)增為代價(jià),面積的縮減通常以速度的降低為代價(jià)。如何權(quán)衡二者的性能要求,在滿足時(shí)序(速度)要求的前提下盡可能節(jié)約邏輯資源(面積),是FPGA設(shè)計(jì)過(guò)程中需要考慮的重點(diǎn)。

2023-06-09 09:36:37 2711

2711

在人工智能的不斷發(fā)展的時(shí)代,永遠(yuǎn)需要性能更高、功耗更低、成本更低的芯片面世。

2022-03-21 09:23:45 2553

2553

尋求最高集成度的設(shè)計(jì)人員可以選擇去開發(fā)一款包含Speedcore eFPGA IP的單芯片ASIC。然而,在某些應(yīng)用中,單芯片集成無(wú)法實(shí)現(xiàn)某些產(chǎn)品靈活性,而這在使用基于chiplet的方案中就有更多靈活性。

2023-09-06 15:12:11 930

930 超低功耗SPAD Array(60mW),采用先進(jìn)3D堆疊式結(jié)構(gòu),極大的縮小了芯片面積,從而改善性能、節(jié)省功耗,為終端用戶創(chuàng)造更大價(jià)值。

2023-10-08 09:53:23 2290

2290

。體積要比QFP和BGA小數(shù)倍,因此能在電路板上實(shí)現(xiàn)更高的元器件安裝密度。CSP還比QFP和PGA封裝有著更高的硅占比(硅與封裝面積的比例)。QFP的硅占比大約在10–60%,而CSP的單個(gè)芯片硅占比高達(dá)60–100%。

2023-12-22 09:08:31 4183

4183

Navi 48采用自主研發(fā)的設(shè)計(jì)方案,包含有64個(gè)計(jì)算單元,采用256位顯存位寬,顯存帶寬達(dá)到693 GB/s,總帶寬高達(dá)2770GB/s,而其GPU芯片面積也達(dá)到了240mm2。

2024-04-10 16:22:18 1904

1904 Speedcore嵌入式FPGA(embedded FPGA,eFPGA)知識(shí)產(chǎn)權(quán)(IP)產(chǎn)品是Achronix公司于2016年推出的顛覆性技術(shù),并于當(dāng)年開始向最終客戶交付,目前出貨量已經(jīng)超過(guò)2500萬(wàn)。

2024-11-15 14:28:10 1634

1634

在部署全閃存儲(chǔ)陣列時(shí),數(shù)據(jù)縮減能力一直是客戶關(guān)注的一大重點(diǎn)。最近聽到有朋友調(diào)侃:“宣傳里寫著5:1,怎么我看到的縮減比只有2:1 ?”

2025-06-18 14:58:57 944

944 連接標(biāo)準(zhǔn)聯(lián)盟最新發(fā)布的Zigbee 4.0標(biāo)準(zhǔn),為低功耗物聯(lián)網(wǎng)連接帶來(lái)了全新升級(jí)!泰凌微電子迅速響應(yīng),旗下TLSR9、TL3、TL7系列SoC已率先實(shí)現(xiàn)對(duì)該標(biāo)準(zhǔn)的支持,以硬核技術(shù)助力智能家居、工業(yè)物

2025-11-24 14:31:02 2774

2774

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論