由于某整車廠混合動力汽車在前期設計階段沒有考慮 EMC 方面的設計,同時各個零部件廠家自身設計能力的不足,單個部件也不能夠滿足要求,因此整車在進行 EMC 測試階段,也遇到不能夠滿足標準 GB 18655 和 GB/T 18387 要求。

2018-05-07 08:42:23 7288

7288

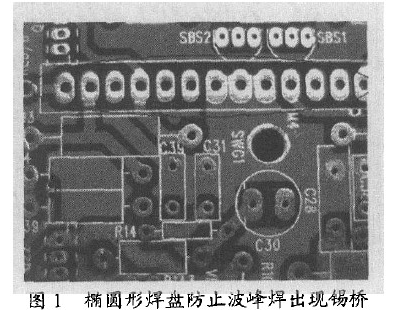

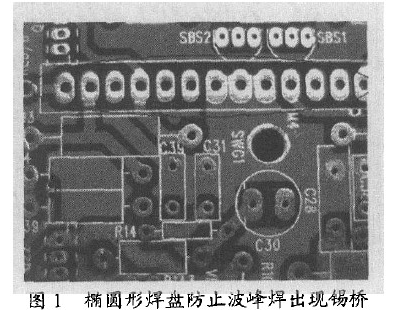

在設計階段排版得當可避免很多制造過程中的麻煩,并將焊接缺陷降低到最低。

2011-11-28 10:59:22 898

898

由于 SAR ADC 的功耗隨著每一代新器件的推出而不斷降低,放大器成了功耗敏感型應用的制約因素。那么我們如何才能進一步降低功耗?在尋找可能的解決方案之前,讓我們先考慮一下 ADC 功耗降低的原因。

2016-08-12 16:04:09 3056

3056

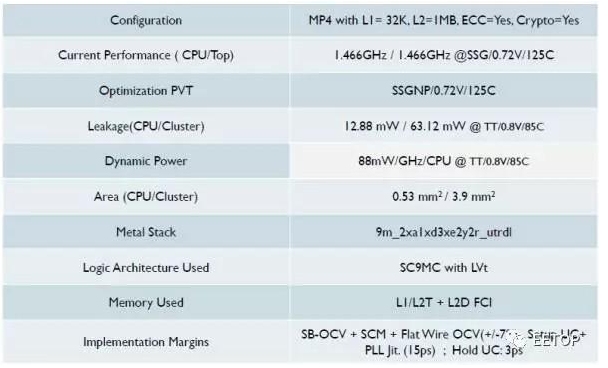

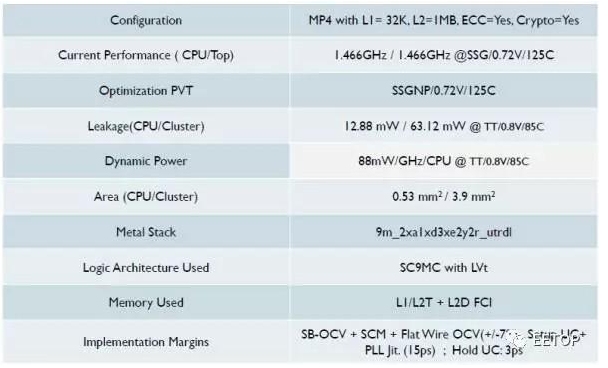

概念: Power/Ground Gating是集成電路中通過關掉那些不使用的模塊的電源或者地來降低電路漏電功耗的低功耗設計方法。該方法能降低電路在空閑狀態下的靜態功耗,還能測試Iddq。 理論

2020-09-16 16:04:15 12899

12899

本文中,我們以15秒的間隔將LM35溫度傳感器數據上傳到ThingSpeak云,在這15秒內,ESP8266將處于深度睡眠(Deep Sleep)模式以降低功耗。

2020-11-06 15:59:57 9476

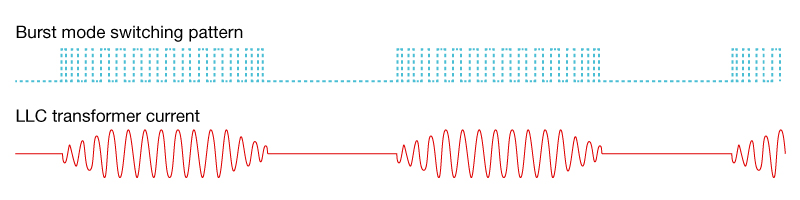

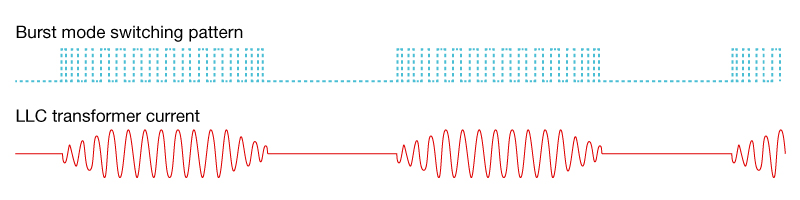

9476 為了滿足不斷變化的能源法規,這些法規要求更低的待機功率和更高的效率,工程師正在設計使用輕負載模式(如突發模式操作)的電源。雖然輕負載模式有助于最大限度地降低待機功耗,但它們帶來了新的挑戰:電源磁性

2023-04-10 11:09:00 9431

9431

大家都知道在設計階段解決問題的成本是最低,同樣道理在原理圖設計階段做好關鍵信號、敏感電路的防護設計可以達到事半功倍的效果,本期將與大家探討在原理圖的設計階段如何考慮靜電防護設計。

2024-01-03 09:32:54 2444

2444

設計技巧為什么能夠節省功耗?降低FPGA功耗的設計技巧有哪些?

2021-04-30 06:04:19

降低一個MCU的主頻就能降低運行的功耗嗎

2023-10-11 08:15:48

考慮到我們今天所生活的時代,嵌入式系統的便攜性是十分關鍵的設計考慮因素。便攜式系統通常用電池供電,而電池使用壽命取決于系統的功耗。

2019-10-30 07:19:27

串聯電阻大概是線圈電阻的兩倍。繼電器閉合可靠性稍微有所降低。但功耗僅有原來不串電阻的1/3,繼電器線圈發熱減少許多,延長使用壽命

2019-01-08 16:11:58

設計、PCB布局布線和軟件設計的各種技巧,并且幫助用戶在設計階段考慮系統的抗ESD和EFT性能。典型故障章節幫助用戶在出現類似問題時提供分析思路。

2023-10-25 07:54:01

CC2530芯片 ZED 和ZC,在組網正常的情況下,ZED可以進入低功耗模式,電流在uA級別。當關閉ZC后,ZED會持續的進行網絡發現,無法進入低功耗模式。電流達28mA;求教,如何降低ZC發現網絡的頻次以降低功耗?或者有其他什么方法來降低功耗?

2016-04-07 14:19:54

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能夠做到如此低的功耗是因為什么?

2021-04-30 06:08:49

支配開關功耗,就像在前幾個工藝節點支配時序一樣。右圖表明了互連對總動態功耗的相對影響。今天,設計師有能力通過布線優化來減少功耗。 在物理設計階段,設計師也可以發現更多自動降耗的機會。在物理設計過程中

2017-10-08 22:06:50

:一是可以通過優化布線減少功耗,互連正在開始支配開關功耗,就像在前幾個工藝節點支配時序一樣。今天,設計師有能力通過布線優化來減少功耗。二是可以在物理設計階段,抓住自動降耗的機會,將是對設計流程早期以及邏輯

2017-06-29 16:46:52

概述NI 提供了高速、靈活、精確的RF硬件,并搭配功能強大的NI LabVIEW軟件,以適應無線通信領域日新月異的需求,并且貫穿了從設計、驗證到生產的所有工程設計階段。為了能滿足不斷發展的通訊標準

2019-06-04 08:19:03

解決方案:僅包含球面或方案中具有不同數量的光學元件的透鏡的選擇,或具有非球面的透鏡。在設計階段,選擇是困難的。在這種情況下,決定是考慮到鏡頭的生產工藝過程。

主要的結果:進行了最佳透鏡光學方案的選擇

2025-05-09 08:51:45

現在wifi 的smartconfig 時候功耗比較大,現在達不到要求,需要在配網時降低10mA。

1,如何通過編程的手段進行降低?

2,這個需要考慮配網時跟路由器之間的距離嗎?

2024-07-10 08:09:41

本帖最后由 一只耳朵怪 于 2018-5-25 17:32 編輯

電子產品的低功耗問題經常讓產品設計者頭痛而又不得不面對。以單片機(MCU)為核心的系統,其功耗主要由單片機功耗和單片機外圍電路功耗組成。要降低單片機系統的功耗,需要從哪方面考慮?

2018-05-25 01:03:12

硬件上設計階段完成,接下來就是我們的軟件層次了。一:端口引腳的配置1 未使用的引腳:不用連接,配置為輸出模式并驅動到任一狀態(高電平或低電平);配置為輸入模式并使用外部電阻(約10 k)拉至VDD

2021-11-11 08:45:36

恒定功耗可以得到控制。 盡早考慮功耗 您在設計的早期階段做出的功耗決定影響最大。決定采用什么元件對功耗具有重大意義,而在時鐘上插入一個 BUFGMUX 則影響甚微。對功耗的考慮越早越好。 恰當

2012-01-11 11:59:44

如何在 Linux 階段進行 OTA 更新

2025-08-20 08:27:11

您好,我被要求執行序列生成器。我已經用紙做過一切,但我不知道如何在Xilinx上正確創建它。我完成了轉換表和輸出表。我的輸出函數已經用karnaugh等進行了簡化。但是當我實現它時,我認為它在

2019-01-10 10:39:50

我們如何在xilinx中制作RPM?使用PlanAhead還是使用FPGA編輯器?我發現有一些指南指向了floorplanner中的一些選項,但我在我的xilinx版本中看不到那些選項(將RPM寫入

2018-10-17 14:23:35

今天給大俠帶來在FPGA設計應用中如何在ModelSim中添加Xilinx仿真庫,話不多說,上貨。

注意:ModelSim一定要安裝在不帶空格的目錄下,即不要安裝在“Program

2024-07-03 18:16:38

如何在PCB設計階段處理好EMC及其EMI的問題呢?有什么解決辦法嗎?

2023-04-06 15:52:59

在使用PIC24系列開發自己的數據記錄器時,我遇到了問題。我使用I2C RTC和SPI串行閃存進行數據存儲。閑置狀態,消耗15mA。如何降低功耗?請向我推薦。

2019-08-27 14:43:22

每輛汽車中都有一個包含傳感器、電機和開關的龐大車載網絡。這些網絡不斷發展以適應車輛上日益增加的連通性,總功耗也隨之增加,因此可能會對車輛的排放產生負面影響。 根據所使用的網絡協議,有幾種方法可以降低功耗

2022-11-04 07:07:38

易失性FPGA的電源特性是什么?如何在進行板級設計時,降低系統的靜態與動態功耗?

2021-04-08 06:47:53

FPGA的功耗高度依賴于用戶的設計,沒有哪種單一的方法能夠實現這種功耗的降低,如同其它多數事物一樣,降低功耗的設計就是一種協調和平衡藝術,在進行低功耗器件的設計時,人們必須仔細權衡性能、易用性、成本、密度以及功率等諸多指標。

2019-08-15 08:28:42

我正在開發一個使用 LoRa模塊的物聯網項目, 但我發現 LoRa 模塊的功耗比較高, 這可能會導致電池消耗得很快.我正在尋找一些建議來幫助我降低 LoRa 模塊的功耗以延長電池壽命.我已經考慮了

2024-03-01 07:38:34

低功耗mcu的選擇方法如何降低mcu的功耗

2021-02-24 06:11:07

如何降低可重構系統的整體功耗?有什么方法能使可重構系統的性能和功耗需求之間達到平衡?

2021-04-08 07:09:23

降低蜂窩手機功耗并且延長其電池壽命是每一位手機設計工程師的目標。設計工程師正在不斷將MP3播放器、照相機以及全運動視頻等功能加入到現代手機中,從而需要不斷地將功耗降到最低。

2019-08-23 08:26:40

請問如何使ADS1247功耗降低,我用CC2530控制1247,現在整體功耗在休眠時候是5V0.45mA,但是1247說明上有一句說是:在睡眠模式下功耗只有0.1-0.5uA,我已經把CC2530

2025-01-10 07:58:04

如何才能實現降低FPGA設計的功耗?

2021-04-29 06:47:38

如何滿足工程過電壓與絕緣配合設計階段的建模需要?

2021-11-05 06:18:36

可以做哪些措施來降低功耗

2023-10-23 07:51:09

自己做了一個電路板,因為功耗除了點問題,怎么降低電路板功耗呢

2019-08-07 22:21:34

從事便攜式或手持產品設計的工程師都明白對于如今的設計,最大限度地降低功耗是必不可少的要求。但是,只有經驗豐富的工程師理解盡可能地延長系統的電池壽命的那些微妙但又重要的細節。本文中我們的重點是,如何使用超低功耗的復雜可編程邏輯器件(CPLD)?如何在嵌入式設計中降低CPLD的功耗?

2019-08-01 08:19:42

降低功耗的最重要的途徑是使用MSP430的時鐘系統來最大限度地提高MSP430處于低功耗模式的時間。怎樣降低msp430的功耗?

2014-11-09 23:10:18

如果忽略了容差積累的影響,你就會在完成原型之后遇到種種麻煩。 制造可靠的硬件要求你在設計階段就應考慮所有的容差。許多參考文獻討論了由于參數偏差引起的有源器件誤差,說明如何計算運算放大器失調電壓、輸入電流以及類似...

2021-04-20 06:15:37

在產品設計時,除考慮降低成本、增加功能之外,還越來越重視其環保性能。選擇低功耗及采用無鉛/符合RoHS標準的封裝的IC器件是設計環保系統的關鍵。設計MAX9509低功耗視頻濾波放大器時,需要考慮一些特殊

2020-12-17 09:52:10

電源門控可以降低泄漏功耗嗎?有哪幾種情況采用PG能顯著減小泄漏功耗呢?

2022-02-11 06:34:36

什么是TICKLESS?怎么能實現功耗的降低呢?TICKLESS是如何去實現功耗降低的呢?

2022-02-24 08:02:02

stm32進入低功耗模式,必須用中斷來喚醒,現在就是不用這種模式,如何通過程序來降低功耗啊

2019-05-06 18:43:22

如何利用FPGA設計技術降低功耗?

2021-04-13 06:16:21

考慮到我們今天所生活的時代,嵌入式系統的便攜性是十分關鍵的設計考慮因素。便攜式系統通常用電池供電,而電池使用壽命取決于系統的功耗。在提倡“綠色環保”計劃的今天,即便是市電供電的應用也要把功耗作為一項

2020-08-20 12:30:00

長期以來,人們往往注重對項目后期竣工結算,決算階段的造價控制,而忽視了對設計階段的造價控制。事實上,設計費用一般只占建設成本的1%-2%,而其卻往往能影響70%-90%左右的

2009-12-28 15:39:27 5

5 輸變電工程設計階段的

2008-11-20 15:47:42 760

760 在絕大部分使用電池供電和插座供電的系統中,功耗成為需要考慮的第一設計要素。Xilinx決定使用20nm工藝的UltraScale器件來直面功耗設計的挑戰,本文描述了在未來的系統設計中,使用Xilinx 20nm工藝的UltraScale FPGA來降低功耗的19種途徑。

2018-07-14 07:21:00 6608

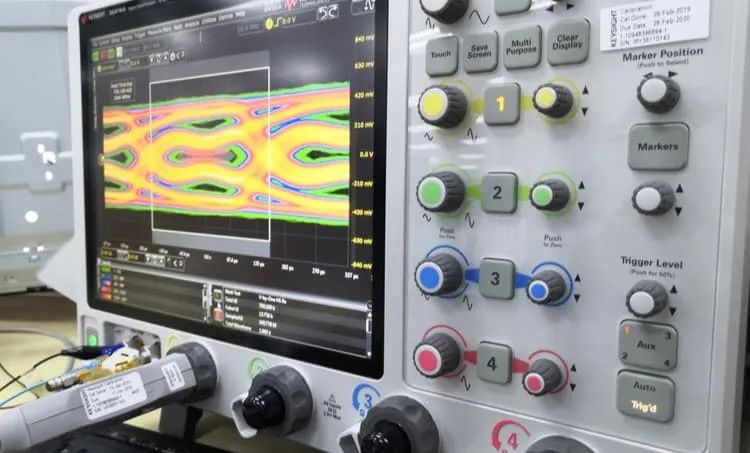

6608 電源測量小貼士 10 個設計階段

2017-10-16 15:44:48 6

6 電源測量的小貼士 10 個設計階段

2017-10-19 09:03:49 4

4 當PCB設計人員所設計的產品投入生產時,幾乎都會遇到一些問題。這些問題通常與生產制程和產量有關,或是PCB組裝中出現了問題,導致產品報廢或大量的返工。當出現上述情況時,產品需重回設計階段進行必要的設計改版,以便其能符合預定的生產制程。

2018-02-14 07:43:00 1100

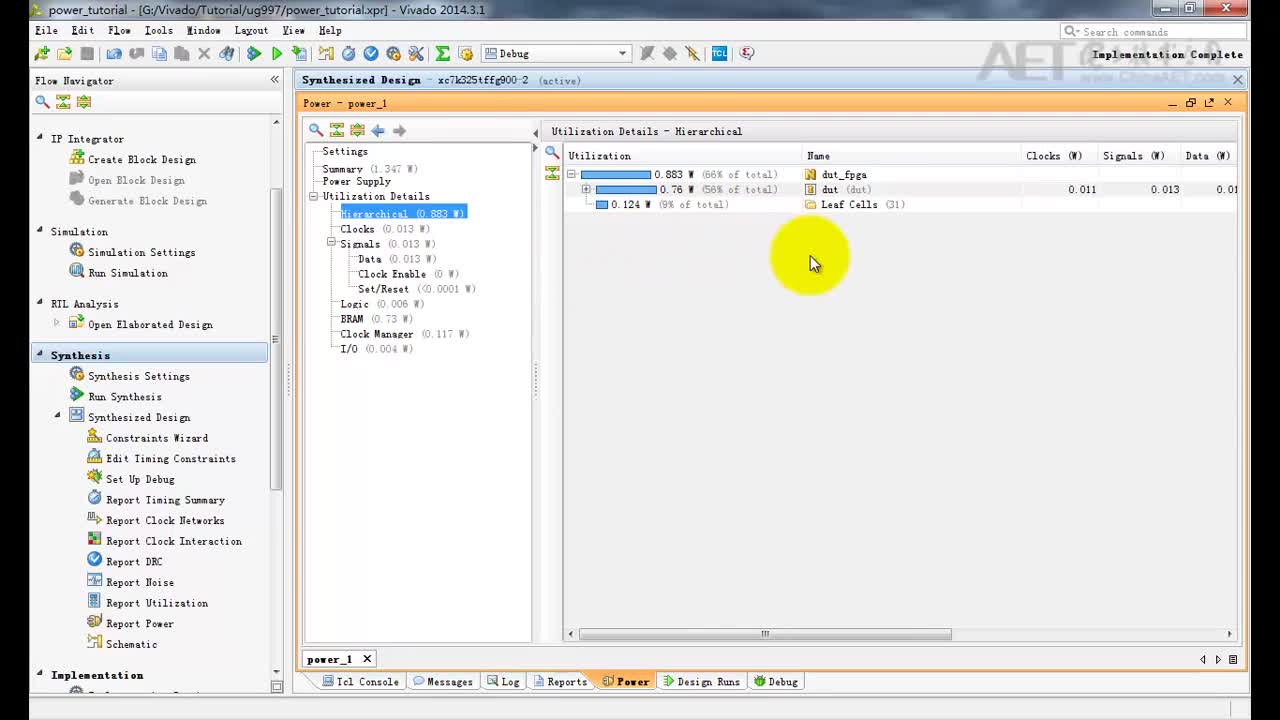

1100 本視頻演示了 Xilinx 功耗估計器電子數據表工具

2018-06-05 13:45:00 8589

8589

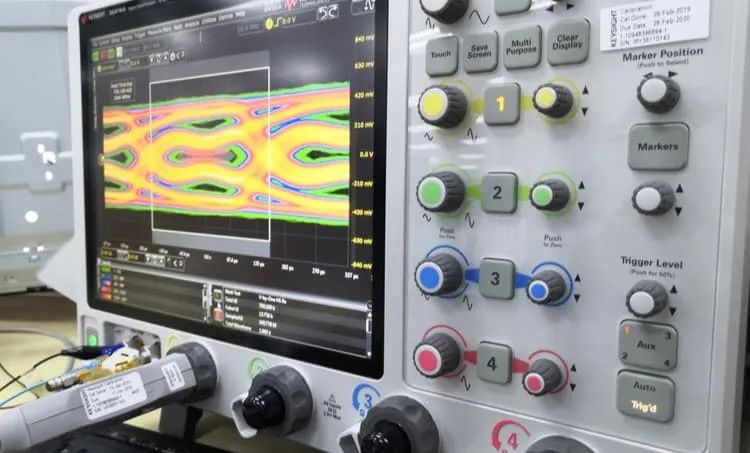

該視頻演示了兩種在設計原型設計階段以及終端系統設計和集成階段監控功耗的方法。

該演示將Maxim解決方案作為電源的一部分進行了比較并利用了......

2018-11-26 07:08:00 2556

2556 亞馬遜網絡服務公司的Gadi Hutt于2018年1月9日在法蘭克福舉行了Xilinx開發者論壇的開幕主題演講.Gadi解釋了Amazon EC2 F1實例的基礎知識,如何在AWS云中加速Xilinx FPGA

2018-11-23 06:15:00 3155

3155 Xilinx FPGA是支持OpenStack的第一個(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺上運行每個演示,并使用OpenStack進行配置和管理。

2018-11-23 06:14:00 4240

4240 了解如何使用可用工具在UltraScale器件上執行功耗分析,以及如何估算從7系列FPGA遷移的設計的功耗。

還要了解如何操作Xilinx功耗估算器。

2018-11-23 06:08:00 4834

4834 本次研討會視頻討論了數據采集系統中降低功耗的解決方案。討論的主題包括使用低功耗器件(如ADC驅動器、穩壓器等)的局限性和權衡考慮因素。

2019-06-10 06:02:00 3966

3966

在設計階段排版得當可避免很多制造過程中的麻煩,并將焊接缺陷降低到最低。

2019-09-02 11:55:51 624

624

在PCB設計階段,關于元件封裝選擇時需要考慮的以下六件事。本文中的所有例子都是用Multisim設計環境開發的,不過即使使用不同的EDA工具,同樣的概念仍然適用。

2019-09-20 10:52:53 9360

9360 AMD在SC19大會上做了一次演講。AMD在開發以及IPC增長方面對ZEN 3和Epyc發表了一些有趣的評論。首先,AMD提到ZEN 3架構設計階段已經完成。如今可以將AMD的設計和發布階段視為發布時間表。在這里,您可能會期望ZEN2的迭代更新。

2019-11-26 14:58:01 3045

3045 在一個應用中,印刷電路板的成本對產品的整體價格有著巨大的影響。因此,重要的是納入有助于減少此支出的所有步驟。下面列出了一些步驟,通過在 PCB 設計階段進行簡單的更改,您就可以降低總體應用程序成本

2020-11-18 19:19:54 3564

3564 為了盡早地在產品設計階段解決電磁兼容問題,設計師需要進行基于理論分析和協作設計的EMC仿真。

2020-11-24 16:32:24 1251

1251 單粒子翻轉(Single-Event Upsets,SEU)指的是元器件受輻照影響引起電位狀態的跳變,“0”變成“1”,或者“1”變成“0”,但一般不會造成器件的物理性損傷。正因為“單粒子翻轉”頻繁出現,因此在芯片設計階段需要重點關注。這也是這篇文章的重點。

2020-11-29 11:07:10 8377

8377 談到芯片,首先想到的一定是性能,功耗,價格,成熟度,生態圈兼容性等。但是只針對芯片本身的話,是看芯片內部有什么運算能力,比如處理器,浮點器,編解碼器,數字信號處理器,圖形加速器,網絡加速器等,還要

2021-02-20 15:42:21 14664

14664

景嘉微:下一代圖形處理芯片處于后端設計階段 景嘉微在接受投資機構調研時對外表示,公司下一代圖形處理芯片目前處于后端設計階段,后續的研發進展將在定期報告中進行披露。景嘉微表示,“公司一直高度重視員工

2021-01-13 11:38:00 2997

2997 Xilinx功耗估算器用戶指南免費下載。

2021-04-21 10:26:30 25

25 硬件上設計階段完成,接下來就是我們的軟件層次了。一:端口引腳的配置1 未使用的引腳:不用連接,配置為輸出模式并驅動到任一狀態(高電平或低電平);配置為輸入模式并使用外部電阻(約10 k)拉至VDD

2021-11-05 20:06:02 11

11 在需求分析階段,硬件電路的設計已經較為全面的進行了說明。接下來我們將細化硬件設計部分。一.低功耗外圍器件的選型1.電容:所有電容在電流通過電介質時都會產生少量電荷損失,即使完全充電后也是如此,稱為

2021-11-05 20:21:02 13

13 優化功耗是電池壽命的關鍵,也是操作設備的關鍵。我們將通過參考物聯網設備的典型功耗配置,介紹在降低功耗方面需要考慮的挑戰和因素。為了能夠優化睡眠模式、固件更新或天線匹配等因素,您會學習到如何測量功耗和電池模型。我們還會用一個簡短的電源概述引導您選擇合適的測量方案。

2022-04-22 08:58:39 2069

2069 選擇性喚醒的控制器局域網收發器如何在汽車設計中降低功耗

2022-10-28 12:00:17 0

0 在印制電路板設計階段對電磁兼容考慮將減少電路在樣機中發生電磁干擾。問題的種類包括公共阻抗耦合、串擾、高頻載流導線產生的輻射和通過由互連布線和印制線形成的回路拾取噪聲等。

2023-04-07 09:15:06 1108

1108 課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:北京4月21日-22日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2023-04-07 17:05:08 728

728

課程名稱:《產品EMC正向設計與分析》講師:吳老師時間地點:深圳5月19日-20日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2023-04-19 09:37:50 740

740

課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:北京6月16日-17日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2023-05-12 10:07:01 697

697

電源管理在RTC中至關重要,因為高功耗會縮短電池壽命,導致設計人員增加電池容量。另一方面,低功耗將允許更小的電池(從而降低成本并實現更小的設計),并且還有助于延長電池壽命。

2023-06-28 15:40:17 1459

1459 的設計概念,它們關注的是PCB設計的可制造性和可組裝性。 DFF(Design for Fabrication)是指在PCB設計階段考慮到PCB制造的要求和限制,以確保設計的可實施性和可制造性。DFF

2023-06-29 09:43:54 1791

1791 1、如何降低功耗? 一般的簡單應用中處理器大量的時間都在處理空閑任務,所以我們就可以考慮當處理器處理空閑任務的時候就進入低功耗模式,當需要處理應用層代碼的時候就將處理器從低功耗模式喚醒

2023-07-30 11:18:36 1726

1726 電子發燒友網站提供《Xilinx功耗估算用戶指南.pdf》資料免費下載

2023-09-13 09:18:55 1

1 如何降低設備功耗,降低采集設備功耗的幾種方法 工程監測傳感器 以下是降低數采設備功耗的一些方法: 優化硬件設計:通過選擇低功耗的芯片、使用更高效的轉換器、減少功率損耗等方式來優化硬件設計,從而降低功耗

2023-10-11 09:29:00 2750

2750 如何在高速信號中降低符號間干擾

2023-11-27 15:29:49 1341

1341

課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:武漢4月19-20日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2024-03-16 08:16:23 619

619

? 融入“制造意識”(Manufacturing Awareness)的設計是一種設計哲學,它強調在產品設計和開發過程中對制造過程的理解和考慮。這種設計方法的目的是減少設計階段到生產階段的轉換時間

2024-06-18 16:51:16 1828

1828

課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:上海6月20-21日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2025-05-15 15:38:11 383

383

課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:成都9月19-20日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2025-07-10 11:54:18 376

376

課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:北京8月8-9日&成都9月12-13日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品

2025-08-01 11:24:07 454

454

課程名稱:《產品EMC正向設計與檢視》講師:吳老師時間地點:深圳11月21-22日主辦單位:賽盛技術課程背景在產品系統設計階段,如何在結構方面考慮電磁兼容設計?在產品PCB設計階段,哪些地方要進行

2025-10-15 14:44:57 256

256

電子發燒友App

電子發燒友App

評論