談到芯片,首先想到的一定是性能,功耗,價格,成熟度,生態圈兼容性等。但是只針對芯片本身的話,是看芯片內部有什么運算能力,比如處理器,浮點器,編解碼器,數字信號處理器,圖形加速器,網絡加速器等,還要看提供了什么接口,比如閃存,內存,PCIe,USB,SATA,以太網等,還有看里面自帶了多少內存可供使用,以及功耗如何。

性能,對CPU來說就是基準測試程序能跑多少分,比如Dhrystone,Coremark,SPEC2000/2006等。針對不同的應用,比如手機,還會看圖形處理器的跑分,而對網絡處理器,會看包轉發率。當然,還需要跑一些特定的應用程序,來得到更準確的性能評估。

功耗,從high level來看,也分動態功耗和靜態功耗。動態功耗,就是在跑某個程序的時候,芯片的功率是多少瓦。通常,這時候處理器會跑在最高頻率,但這并不意味著所有的晶體管都在工作,由于power gating和clock gating的存在,有些沒有被用到的邏輯和片上內存塊并沒在耗電。芯片公司給出的處理器功耗,通常都是在跑Dhrystone。這個程序有個特點,它只在一級緩存之上運行,不會訪問二級緩存,更不會訪問內存。這樣得出的功耗,其實并不是包含了內存訪問的真實功耗,也不是最大功耗。為得到處理器最大功耗,需要運行于一級緩存之上的向量和浮點指令,其結果通常是Dhrystone功耗的2-3倍。但是從實際經驗看,普通的應用程序并不能讓處理器消耗更高的能量,所以用Dhrysone測量也沒什么問題。當然,要準確衡量整體的芯片功耗,還得考慮各種加速器,總線和接口,并不僅僅是處理器。

在芯片設計階段,最重要的就是PPA,它轉化為設計,就是功能,性能,功耗,直接影響價格。其中,性能有兩層含義。在前端設計上,它表示的是每赫茲能夠跑多少標準測試程序分。通常來說,流水線級數越多,芯片能跑到的最高頻率越高。可是并不是頻率越高,性能就越高。這和處理器構架有很大關系。典型的反例就是Intel的奔騰4,30多級流水,最高頻率高達3G赫茲,可是由于流水線太長,一旦指令預測錯誤,重新抓取的指令要重走這幾十級流水線,代價是很大的。而它的指令又非常依賴于編譯器來優化,當時編譯器又沒跟上,導致總體性能低下。而MIPS或者PowerPC的處理器頻率都不高,但是每赫茲性能相對來說還不錯,總體性能就會提高一些。所以性能要看總體跑分,而不是每赫茲跑分。

性能的另外一個含義就是指最高頻率,這是從Backend設計角度來說的。Backend的人只看芯片能跑到多少頻率,頻率越高,對實現的時候的timing, noise等要求不一樣。頻率越高,在每赫茲跑分一定的情況下,總體性能就越高。請注意對于那些跑在一級緩存的程序,處理器每赫茲跑分不會隨著頻率的變化而變化。而如果考慮到多級緩存,總線和外圍接口,那肯定就不是隨處理器頻率線性增加了。

從后端角度考慮,影響頻率的因素有很多,比如:

首先,受工藝的影響。每一種制程(例如14nm)下面還有很多小的工藝節點,例如LP,HP等。他們之間的最高頻率,漏電,成本等會有一些區別,適合不同的芯片,比如手機芯片喜歡漏電低,成本低的,服務器喜歡頻率高的,不一而足。

其次,受后端庫的影響。Foundry會把工藝中晶體管的參數抽象出來,做成一個物理層開發包(可以認為叫DK),提供給工具廠商,IP廠商和芯片廠商。而這些廠商的后端工程師,就會拿著這個物理層開發包,做自己的物理庫。物理庫一般包含邏輯和內存兩大塊。根據晶體管參數的不同,會有不同特性,適合于不同的用途。而怎么把這些不同特性的的庫,合理的用到各個前端設計模塊,就是一門大學問。一般來說,源極和漏極通道越短,電子漂移距離越短,能跑的頻率就越高。可是,頻率越高,動態功耗就越大,并且可能是按指數級上升。除此之外,還會有Track這種說法,指的是的標準單元的寬度。常見的有6.75T,9T等。寬度越大,電流越大,越容易做到高頻,面積也越大。還有一個可調的參數就是閾值電壓,決定了柵極的電壓門限,門限越低,頻率能沖的越高,靜態功耗也越大,按對數級上升。比如需要低功耗(更多使用HVT的晶體管)或者高性能(更多使用LVT,ULVT)的晶體管。

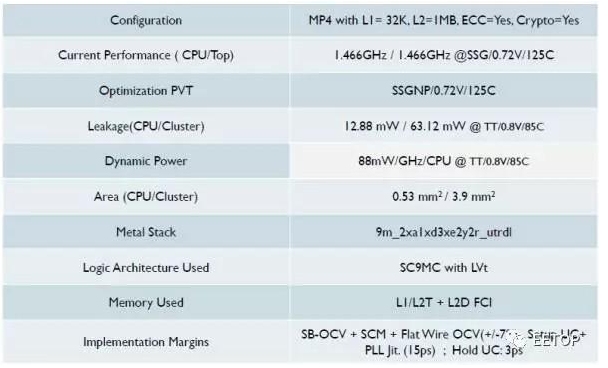

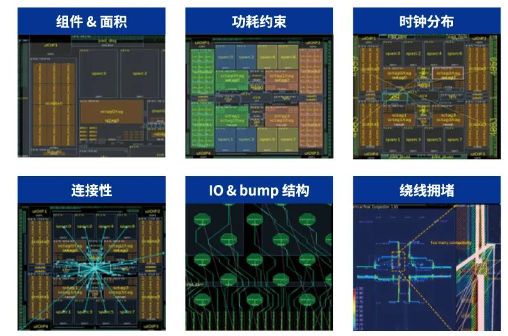

接下來,受布局和布線的影響。芯片里面和主板一樣,也是需要多層布線的,每一層都有個利用率。總體面積越小,利用率越高,布線就越困難。而層數越多,利用率越低,成本就越高。在給出一些初始和限制條件后,EDA軟件會自己去不停的計算,最后給出一個可行的頻率和面積。就好像下圖,Metal Stack表明,整個芯片是9層Stack。

再次,受前后端協同設計的影響。處理器的關鍵路徑直接決定了最高頻率。這一部分,還沒體會,先放著,不懂。

從功耗角度,同樣是前后端協同設計,某個訪問片上內存的操作,如果知道處理器會花多少時間,用哪些資源,就可以讓內存的空閑塊關閉,從而達到省電的目的。比如Clock Gating,Power Gating等都是用來干這事的。

對于移動產品,靜態功耗也是很有用的一個指標。靜態就是晶體管漏電造成的,大小和芯片工藝,晶體管數,電壓相關。控制靜態功耗的方法是power gating,關掉電源,那么靜態和動態功耗都沒了。

另外,就是動態功耗。動態是開關切換造成的,所以和晶體管數,頻率,電壓相關。動態調頻調壓(DVFS)的控制方法是clock gating,頻率變小,自然動態功耗就小,降低電壓,那么動態功耗和靜態功耗自然都小。可是電壓不能無限降低,否則電子沒法漂移,晶體管就不工作了。并且,晶體管跑在不同的頻率,所需要的電壓是不一樣的,拿16納米來說,往下可以從0.9V變成0.72V,往上可以變成1V或者更高。別小看了這一點點的電壓變化,動態功耗的變化,是和電壓成2次方關系,和頻率成線性關系的。而頻率的上升,同樣是依賴于電壓提升的。所以,1.05V和0.72V,電壓差了45%,動態功耗可以差3倍。

再往上,就是軟件電源管理了,也就是芯片的Low Power管理策略。把每個大模塊的clock gating和power gating進行組合,形成不同的休眠狀態,軟件可以根據溫度和運行的任務,動態的告訴處理器每個模塊進入不同的休眠狀態,從而在任務不忙的時候降低功耗。這里就需要PVT Sensor。在每個芯片里面都有很多PVT Sensor。

頻率和面積其實也是互相影響的。給定一個目標頻率,選用了不同的物理庫,不同的track(也就是不同的溝道寬度),不同的利用率,形成的芯片面積就會不一樣。通常來說,越是需要跑高頻的芯片,所需的面積越大。頻率差一倍,面積可能有百分之幾十的差別。對晶體管來說,面積就是成本,晶圓的總面積一定,價錢一定,那單顆芯片的面積越小,成本越低,并且此時良率也越高。

從上面我們看到,設計芯片很大程度上就是在平衡。影響因素,或者說坑,來自于方方面面,IP提供商,工廠,市場定義,工程團隊。水很深,坑很大,沒有完美的芯片,只有完美的平衡。在這點上,蘋果是一個很典型的例子。蘋果A10的CPU頻率不很高,但是Geekbench單核跑分卻比 A73高了整整75%,接近Intel桌面處理器的性能。為什么?因為蘋果用了大量的面積換取性能和功耗。首先,它使用了六發射,而A73只有雙發射,流水線寬了整整三倍。當然,三倍的發射寬度并不表示性能就是三倍,由于數據相關性的存在,發射寬度的效益是遞減的。再一點,蘋果使用了整整6MB的緩存,而這個數字在別的手機芯片上通常是2MB。對一些標準跑分,比如SpecInt2000/2006,128KB到256KB二級緩存帶來的性能提升僅僅是7%左右,而256KB到1MB帶來的提升更小,緩存面積卻是4倍。第三,除了一二三級緩存之外,蘋果大量增加處理器在各個環節的緩沖,比如指令預測器等。當然,面積的提升同樣帶來了靜態功耗的增加,不過相對于提升頻率,造成動態功耗增加來說,還是小的。再次,蘋果引入的復雜的電源,電壓和時鐘控制,雖然增加了面積,但由于系統軟件都是自己的,可以從軟件層面就進行很精細的優化,將整體功耗控制的非常好。舉個例子,Wiki上面可以得知,A10上的大核Hurricane面積在TSMC的16nm上是4.18平方毫米,而ARM的Enyo去掉二級緩存差不多是2.4平方毫米,在2.4Ghz時,SPECINT2000跑分接近,面積差了70%。

但是,也只有蘋果能這么做,一般芯片公司絕對不會走蘋果這樣用大量面積換性能和功耗的路線,那樣的話毛利就太低了。這也是為什么現在越來越多的整機廠家,愿意來自研芯片或者定制芯片的一個主要原因。

編輯:hfy

-

處理器

+關注

關注

68文章

20250瀏覽量

252208 -

電源管理

+關注

關注

117文章

7176瀏覽量

147998 -

cpu

+關注

關注

68文章

11277瀏覽量

224944 -

PowerPC

+關注

關注

2文章

39瀏覽量

30600 -

網絡處理器

+關注

關注

1文章

49瀏覽量

14473

發布評論請先 登錄

芯片測試覆蓋率99%就夠了嗎?給DFT設計提個醒

從設計階段排查預防PCB短路

為什么要進行芯片測試以及分別在什么階段進行

“點沙成金”的科技奇跡:深入解讀芯片制造三大階段與五大步驟

深圳 11月21-22日《產品EMC正向設計與檢視》公開課火熱報名中!

北京 8月8-9日 成都 9月12-13日《產品EMC正向設計與檢視》公開課火熱報名中!

北京 8月9-10日 成都 9月19-20日《產品EMC正向設計與檢視》公開課火熱報名中!

成都 9月19-20日《產品EMC正向設計與檢視》公開課火熱報名中!

上海 6月20日-21日《產品EMC正向設計與檢視》公開課火熱報名中!

PanDao:光學設計階段透鏡系統的可生產性分析

PanDao:光學加工評估

概倫電子層次化SoC設計規劃方案NavisPro介紹

芯片設計階段時關于PPA的考慮

芯片設計階段時關于PPA的考慮

評論