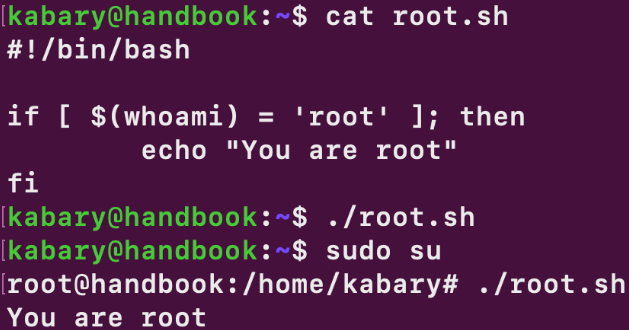

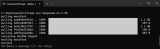

今天我們介紹一下如何在 bash 中使用條件語句。

2022-12-09 17:27:19 2830

2830

在這篇文章中,我們將學(xué)習(xí)如何在OpenCV中使用基于深度學(xué)習(xí)的邊緣檢測,它比目前流行的canny邊緣檢測器更精確。

2023-05-19 09:52:29 2813

2813

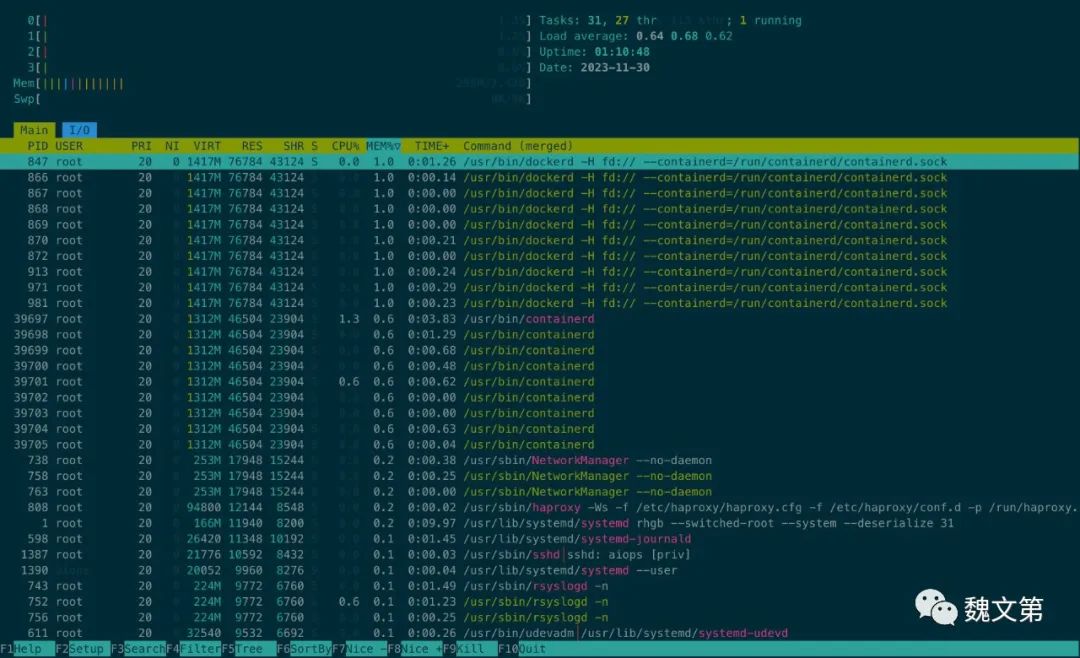

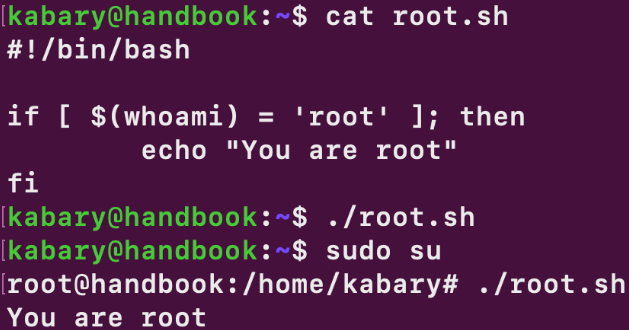

本文介紹如何在 Linux 中使用 htop 命令。

2023-12-04 14:45:28 4132

4132

是一個(gè)IP核,這個(gè)IP核對外總線接口有PLB(包括一個(gè)DPLB和一個(gè)IPLB)、LMB(包括一個(gè)DLMB和一個(gè)ILMB)、FSL(8個(gè)FSL主、8個(gè)FSL從接口)、XCL(包括一個(gè)DXCL和一個(gè)

2013-05-04 17:51:46

我在EDK中使用MCB,我正在對它進(jìn)行一些修改。但我發(fā)現(xiàn)了以下結(jié)果。我的寫作和閱讀工作正在爆發(fā)4.我在哪里可以改變它?對于那些從事AXI接口工作的人來說,MCB使用寫通道和讀通道在有效信號和就緒信號

2020-05-04 14:41:06

你好,我已經(jīng)在micrlaze中建立了用于SPI ip核心的EDK平臺。我正在使用Spartan6 FPGA以及如何使用Isim模擬edk中的SPI ip core以及如何驗(yàn)證spi ipcore。謝謝&問候Madhu B

2020-04-03 09:57:48

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數(shù)字電路中常用但比較復(fù)雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設(shè)計(jì)成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數(shù)字電路中常用但比較復(fù)雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設(shè)計(jì)成可修改參數(shù)的模塊,讓其它用戶可以直接調(diào)用這些模塊,以避免重復(fù)勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調(diào)用IP核和在qsys中用IP核有什么區(qū)別?自個(gè)有點(diǎn)迷糊了

2017-08-07 10:09:03

我調(diào)用了一個(gè)ip核 在下載到芯片中 有一個(gè)time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個(gè)解決方法就是把ip核生成的v文件加到主項(xiàng)目文件中就是上面

2016-05-17 10:28:47

用Quartus II 調(diào)用IP核時(shí),在哪可以查看IP核的例程

2014-07-27 20:28:04

CAN控制器IP核(可直接在Nios II中使用)

2016-08-24 16:54:21

的只是IP核的功能,那么這個(gè)微型電池(或powerpc)的最簡單的系統(tǒng)是什么。謝謝。以上來自于谷歌翻譯以下為原文Hi all. Can EDK IP Core be directly used

2019-01-23 10:21:55

FPGA的IP軟核使用技巧主要包括以下幾個(gè)方面:

理解IP軟核的概念和特性 :

IP軟核是指用硬件描述語言(如VHDL或Verilog)描述的功能塊,但并不涉及具體的電路實(shí)現(xiàn)細(xì)節(jié)。它通常只經(jīng)過功能

2024-05-27 16:13:24

嗨,有什么例子vor Vivado 14.1如何在塊設(shè)計(jì)中使用以太網(wǎng)ip核心?我想將幀傳輸?shù)絇L進(jìn)行數(shù)據(jù)包檢查。 (1GBit etho)謝謝HS

2020-03-16 09:54:01

我在EDK中使用xps_tft完成后我將它下載到頂點(diǎn)4 ML403 fx系列FPGA,我的vga能夠同步,但fpga會被加熱得非常快(在幾秒鐘內(nèi)),這有什么問題?... ..謝謝。以上來自于谷歌翻譯

2019-03-01 13:38:21

通過Quartus II 軟件創(chuàng)建PLL IP核。首先,要新建一個(gè)工程,這個(gè)方法在之前的帖子中已經(jīng)發(fā)過,不會的可以查看前面的相關(guān)帖子。創(chuàng)建好自己的工程:打開如下的菜單

2016-09-23 21:44:10

在較大工程中由于其局限性使用的越來越少,不推薦再學(xué)習(xí);Verilog HDL為當(dāng)今主流的設(shè)計(jì)方式;用IP核代替用戶自己設(shè)計(jì)的邏輯,可以大大縮短開發(fā)周期,提供更加有效的邏輯綜合和實(shí)現(xiàn)。Altera IP

2019-03-04 06:35:13

你好,我已經(jīng)在micrlaze中建立了用于SPI ip核心的EDK平臺。我正在使用Spartan6 FPGA以及如何使用Isim模擬edk中的SPI ip core以及如何驗(yàn)證spi ipcore。謝謝&問候Madhu B

2020-04-03 09:54:09

嗨, 如果您在位于此處的ML507板上下載帶有XPS 11.5的標(biāo)準(zhǔn)IP附加示例的EDK BSB設(shè)計(jì)http://www.xilinx.com/products/boards/ml507

2019-08-20 09:51:47

請問我修改完MIG IP核以后,該如何進(jìn)行更新呢?搗鼓了半天,要么更新為源代碼,要么就是提示我自己添加的端口不存在

2018-11-12 19:46:15

對于深入學(xué)習(xí)使用FPGA的小伙伴們,特別是一些復(fù)雜的、大規(guī)模的設(shè)計(jì)應(yīng)用,適宜的IP核對開發(fā)能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調(diào)用這些模塊

2024-04-29 21:01:16

你好,我正在EDK中使用axi4stream。有人可以幫助我如何使用通過Vivado高級綜合(HLS)生成的ap_fifo / axi4stream接口可以在EDK中使用嗎?我正在使用Export

2019-02-28 13:47:30

嗨,我想在EDK中使用ISE中提供的PCI Express IP核,這意味著我應(yīng)該將所有ISE IP核的verilog模塊導(dǎo)入EDK。這是可能的,如果可能的話請發(fā)送相關(guān)文件。謝謝&問候,Madhu.B

2020-03-24 08:14:50

我在Kintex-7設(shè)計(jì)中使用PCIE IP核。從IP示例中,模擬在MMCM user2輸出處顯示125Mhz。我使用相同的核心,但在我的設(shè)計(jì)中它顯示62.5Mhz。兩個(gè)設(shè)計(jì)之間的輸入在100Mhz

2020-08-28 13:41:38

核的分類和特點(diǎn)是什么?基于IP核的FPGA設(shè)計(jì)方法是什么?

2021-05-08 07:07:01

信息,所以我必須vhd包裝器文件中的實(shí)例化然后它可以通過合成流程。如何在IP Intergrator中使用此vhd文件?hdmi_i2c_sender.vhd 8 KB以上來自于谷歌翻譯以下為原文

2019-03-07 11:05:26

失敗。1)如何在ISE和EDK項(xiàng)目中共享ML605差分clk(即CLK_P和CLK_N)?2)此外,我可以使用Xilinx時(shí)鐘模塊IP制作差分clk嗎?謝謝。以上來自于谷歌翻譯以下為原文Hi, I

2019-02-21 10:56:58

如何在Libero的開發(fā)環(huán)境下封裝通用的自定義的IP核?請各位大俠指點(diǎn)!

2019-11-13 23:09:18

通用的IP核,使得用戶可輕松集成屬于自己的專用功能;但對于一些特定的外設(shè),沒有現(xiàn)成可用的IP核,如液晶模塊CBGl28064等。用戶可通過自定義邏輯的方法在SOPC設(shè)計(jì)中添加自定義IP核。在實(shí)際應(yīng)用中

2019-08-05 07:56:59

作為我項(xiàng)目的一部分,我需要將ADC與7系列FPGA接口,我有一個(gè)SelectIO?接口向?qū)У?b class="flag-6" style="color: red">IP核。但是,我的整個(gè)項(xiàng)目都在VHDL中,IPi得到的是Verilog。請指出我如何在我的VHDL頂級模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

嗨,我正在嘗試學(xué)習(xí)如何使用System Generator來創(chuàng)建自己的IP核。首先,我在DocNav中找到了一個(gè)ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“examples”文件夾中找不到完全相同的示例。提前致謝馬丁

2020-05-22 07:22:09

本帖最后由 machairodus 于 2014-5-29 00:10 編輯

小弟我最近用EDK做一個(gè)視頻采集系統(tǒng),做了一個(gè)視頻采集的IP核,希望將采集到的視頻數(shù)據(jù)傳到DDR2 中緩存。制作

2014-05-28 19:57:05

,找到拷貝好的IP核所在文件夾。完成添加好如圖所示,點(diǎn)擊Finish。如圖所示,在IP文件夾下,移植的IP已經(jīng)呈現(xiàn)出來。接下去可以例化這個(gè)IP到目標(biāo)工程中使用。`

2019-09-04 10:06:45

設(shè)計(jì)。本人剛剛接觸FPGA,對IP核的理解也是一知半解,是說比如我在verilog中,不能使用+,-,*,/,而必須自己親自設(shè)計(jì),只可以用& ,|,!,^這些運(yùn)算是么?當(dāng)然我知道IP核遠(yuǎn)遠(yuǎn)不止我提到的這些,但是最基本的+,-,/,*肯定都不可以使用是吧。謝謝大家了!

2018-04-06 20:46:11

你好我對在設(shè)計(jì)中使用IP并嘗試學(xué)習(xí)一些基本內(nèi)容感到困惑。目前我正在嘗試使用ZYBO板讀取模擬信號,并從示例設(shè)計(jì)開始。https://github.com/Digilent/Zybo-XADC問題是

2020-08-14 09:25:30

各位大家好,我找到了xilinx zynq單板電腦板,但我發(fā)現(xiàn)它有顯示限制,我問他們的工程師,他們告訴我這塊板子使用xylon試用版IP而且只能在啟動后30分鐘內(nèi)工作,我需要購買IP核的許可證,但我認(rèn)為許可證價(jià)格非常高,是否有可能自己開發(fā)IP核?有什么好建議嗎?

2019-10-21 09:50:42

EDK 原理、工具和技巧指南

EDK Concepts, Tools, andTechniques

A Hands-On Guide to EffectiveEmbedded System Design

EDK 9.2i

2007-12-23 21:39:59 62

62 如何在VxWorks系統(tǒng)中使用TrueType字庫

2009-03-29 12:25:18 19

19 USB設(shè)備接口IP核的設(shè)計(jì):討論了用Verilog硬件描述語言來實(shí)現(xiàn)USB設(shè)備接口IP核的方法,并進(jìn)行了FPGA的驗(yàn)證。簡要介紹USB系統(tǒng)的體系結(jié)構(gòu),重點(diǎn)描述USB設(shè)備接口IP核的結(jié)構(gòu)劃分和各模塊的

2010-01-08 18:15:38 22

22 提出了一種采用基于NiosII處理器的通用AD IP核來實(shí)現(xiàn)嵌入式數(shù)據(jù)采集系統(tǒng)的新方案。它能將市面上任意一款A(yù)D芯片制作成IP核并集成到NiosII系統(tǒng)中使用,且整個(gè)IP核的控制與運(yùn)算邏輯由

2010-07-30 11:39:16 50

50 文章采用TOP-DOWN 的方法設(shè)計(jì)了 AMBA 總線IP 核!它包括AHB 和APB兩個(gè)子IP 核 所有AMBA結(jié)構(gòu)模塊均實(shí)現(xiàn)了RTL級建模

2011-07-25 18:10:52 93

93 本書介紹Xilinx公司的嵌入式集成開發(fā)平臺EDK工具組的使用方法,F(xiàn)PGA內(nèi)嵌CPU核軟核Microblaze和硬核PowerFC405,以及使用這些CPU核與Xilinx提供的多種外設(shè)IP核進(jìn)行嵌入式設(shè)計(jì)的流程與方法。引

2011-11-23 10:47:01 102

102 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實(shí)用挺不錯(cuò)的資料

2015-11-30 17:36:15 12

12 Xilinx FPGA工程例子源碼:EDK中PS2自定義IP

2016-06-07 11:44:14 4

4 Xilinx FPGA工程例子源碼:PCI Express IP核應(yīng)用參考設(shè)計(jì)

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

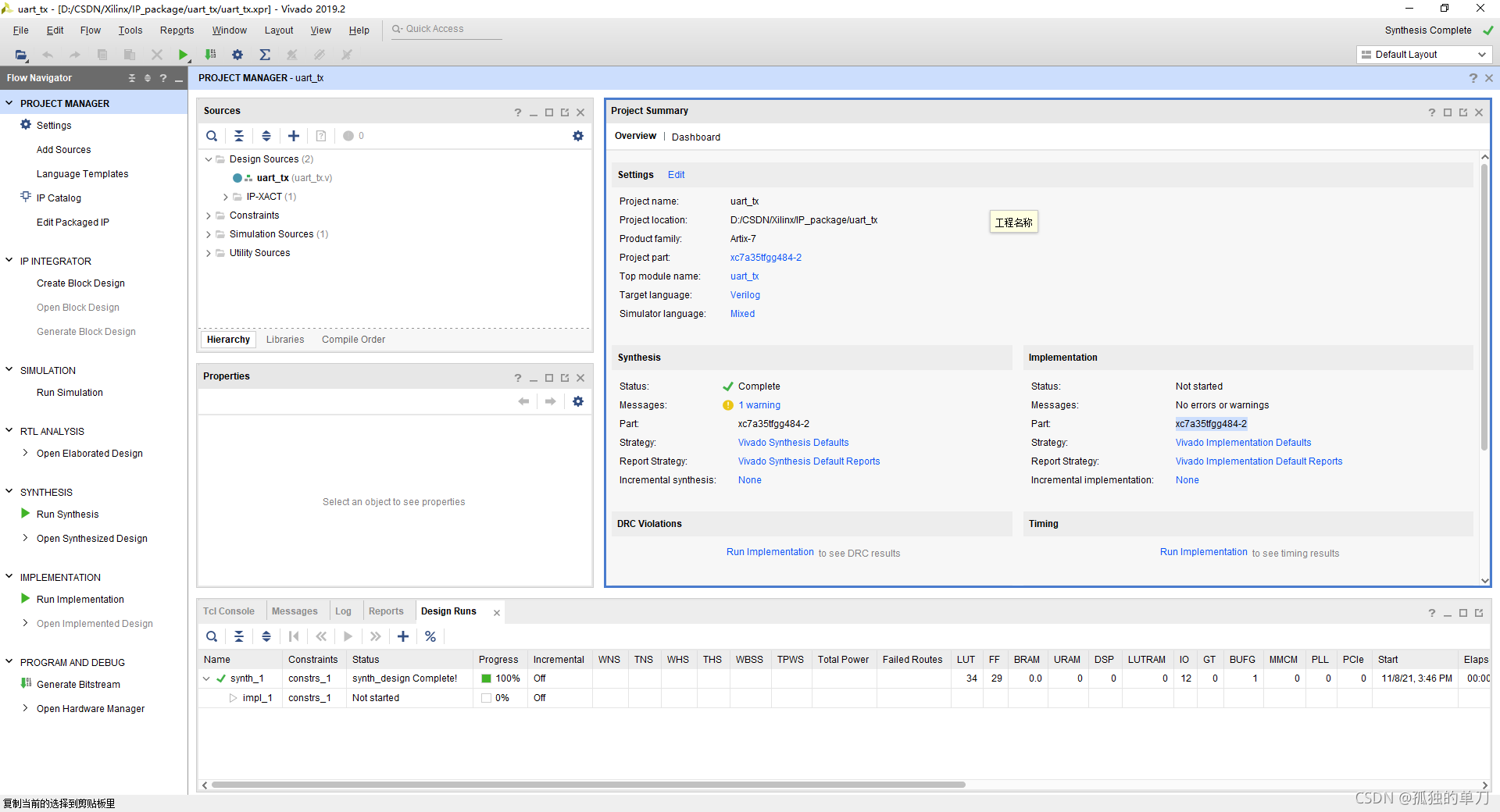

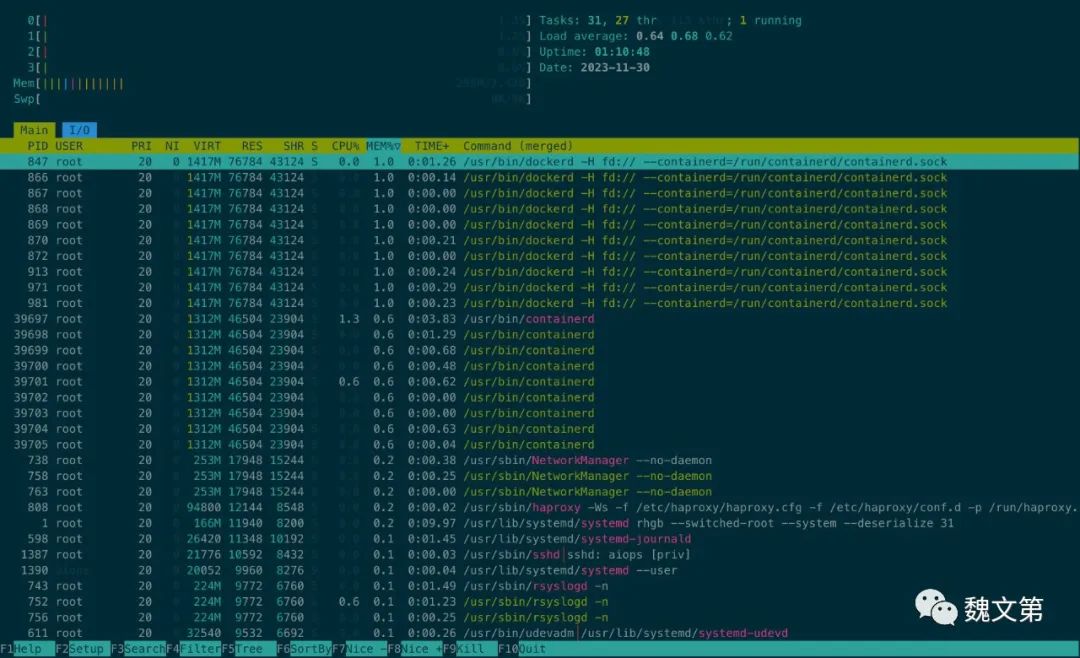

13 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言

2017-02-08 13:08:11 3085

3085

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言

2017-11-15 11:19:14 10744

10744 DMA控制器是常見的總線設(shè)備之一,很多廠商都有自己的DMA控制器IP核。比如嵌入式處理器的龍頭ARM公司就有自己的DMA控制器解決方案提供給客戶,另外像Freescale,F(xiàn)ujitsu等芯片

2017-12-06 13:41:59 4363

4363

本文檔內(nèi)容介紹了建立用戶自己的IP核的操作步驟,供參考

2018-04-03 11:26:51 4

4 在EDK環(huán)境中針對在xilinx sp605 PCIe開發(fā)板,舉一個(gè)簡單的例子,介紹如何使用PCIE核與PC進(jìn)行數(shù)據(jù)通訊。

2018-06-07 02:46:00 6649

6649 大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來聊一聊vivado 調(diào)用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 對于IP核輸出數(shù)據(jù)的解析最好的工具就是其自帶的仿真文件,里面既將接收的數(shù)據(jù)進(jìn)行了解析,又將發(fā)送給IP核的數(shù)據(jù)進(jìn)行了封裝,這對于了解數(shù)據(jù)結(jié)構(gòu)和協(xié)議是十分有幫助的,以太網(wǎng)如此,pcie、ram、fifo等其它IP也如此,我們只需將ip自帶的仿真文件改為我們自己的邏輯即可,接口連接并不變。

2018-07-09 14:07:00 4234

4234 AD的IP核哪里有?

2018-10-06 15:37:29 469

469 了解如何在UltraScale +設(shè)計(jì)中包含新的UltraRAM模塊。

該視頻演示了如何在UltraScale + FPGA和MPSoC中使用UltraRAM,包括新的Xilinx參數(shù)化宏(XPM)工具。

2018-11-22 05:50:00 8790

8790 在本教程中,我們將來聊一聊有關(guān)如何在 Vitis HLS 中使用 AXI4-Lite 接口創(chuàng)建定制 IP 的基礎(chǔ)知識。

2020-09-13 10:04:19 7395

7395

? Xilinx公司的FPGA中有著很多的有用且對整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運(yùn)行工程。 本篇博文將分為 3 個(gè)部分: 1. 從 Vitis HLS 導(dǎo)出 IP。 2.

2021-04-26 17:32:26 5439

5439

IP核目前的IP設(shè)計(jì)已成為目前FPGA設(shè)計(jì)的主流方法之一,應(yīng)用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數(shù)據(jù)塊。IP核在SoC中的集成方式及應(yīng)用場景,芯片設(shè)計(jì)中的IP核具有特定功能的可復(fù)用的標(biāo)準(zhǔn)性和可交易性,已經(jīng)成為集成電路設(shè)計(jì)技術(shù)的核心與精華。

2021-10-01 09:08:00 3100

3100 模塊復(fù)用是邏輯設(shè)計(jì)人員必須掌握的一個(gè)基本功,通過將成熟模塊打包成IP核,可實(shí)現(xiàn)重復(fù)利用,避免重復(fù)造輪子,大幅提高我們的開發(fā)效率。

2022-02-16 16:21:28 3653

3653

在本篇博文中,我們將學(xué)習(xí)如何導(dǎo)出 IP 以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運(yùn)行工程。

2022-07-08 09:34:00 4213

4213 您是否想創(chuàng)建自己帶有 AXI4-Lite 接口的 IP 卻感覺無從著手?本文將為您講解有關(guān)如何在 Vitis HLS 中使用 C 語言代碼創(chuàng)建 AXI4-Lite 接口的基礎(chǔ)知識。

2022-07-08 09:40:43 2808

2808 如何在java代碼中使用HTTP代理IP。

2022-08-04 15:38:49 2843

2843 如何在python代碼中使用HTTP代理IP。

2022-08-04 15:46:27 1801

1801 如何在PHP代碼中使用HTTP代理IP。

2022-08-04 16:08:51 2994

2994 如何在go語言代碼中使用HTTP代理IP。

2022-08-04 16:13:14 3791

3791 如何在易e語言代碼中使用HTTP代理IP,示例代碼demo直接可用(步驟注釋清晰)

2022-08-05 16:29:51 7706

7706 如何在c語言代碼中使用HTTP代理IP,示例代碼demo直接可用(步驟注釋清晰)

2022-08-05 16:31:38 2906

2906 如何在c#語言代碼中使用HTTP代理IP,示例代碼demo直接可用(步驟注釋清晰)

2022-08-05 16:33:07 3424

3424 如何再python代碼中使用HTTP代理IP。

2022-09-13 09:25:52 1544

1544 電子發(fā)燒友網(wǎng)站提供《如何在Arduino中使用伺服電機(jī).zip》資料免費(fèi)下載

2022-10-24 09:46:03 3

3 電子發(fā)燒友網(wǎng)站提供《如何在Arduino中使用LDR.zip》資料免費(fèi)下載

2022-10-31 09:50:41 0

0 電子發(fā)燒友網(wǎng)站提供《如何在Arduino中使用Modbus.zip》資料免費(fèi)下載

2022-11-22 11:21:30 14

14 電子發(fā)燒友網(wǎng)站提供《如何在Arduino中使用微型伺服.zip》資料免費(fèi)下載

2022-11-28 09:50:24 1

1 在仿真Vivado IP核時(shí)分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

的不同模塊進(jìn)行實(shí)體/塊的仿真。前文回顧如何測試與驗(yàn)證復(fù)雜的FPGA設(shè)計(jì)(1)——面向?qū)嶓w或塊的仿真在本篇文章中,我們將介紹如何在虹科IP核中執(zhí)行面向全局的仿真,而這也是測

2022-06-15 17:31:20 1373

1373

來源:AI公園,作者:TraptiKalra編譯:ronghuaiyang導(dǎo)讀這是前一篇文章的繼續(xù),在這篇文章中,我們將討論紋理分析在圖像分類中的重要性,以及如何在深度學(xué)習(xí)中使用紋理分析。在這

2022-10-10 09:15:41 1708

1708

本文主要介紹如何在 Python 項(xiàng)目中使用?paho-mqtt?客戶端庫 ,實(shí)現(xiàn)客戶端與?MQTT?服務(wù)器的連接、訂閱、取消訂閱、收發(fā)消息等功能。

2022-12-22 10:41:54 11494

11494

FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,F(xiàn)PGA)中使用的可復(fù)用的設(shè)計(jì)模塊或功能片段。它們是預(yù)先編寫好的硬件設(shè)計(jì)代碼,可以在FPGA芯片上實(shí)現(xiàn)特定的功能。

2023-07-03 17:13:28 8969

8969 Vivado IP核提供了強(qiáng)大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

Xilinx公司的FPGA中有著很多的有用且對整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 Dimitar Panayotov 在 2023 年 QA Challenge Accepted 大會 上分享了他如何在測試中使用 ChatGPT。

2024-02-20 13:57:01 1390

1390 在使用FPGA的時(shí)候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

本文介紹了Vidado中FFT IP核的使用,具體內(nèi)容為:調(diào)用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數(shù)據(jù)>>測試verilogHDL>>TestBench仿真>>結(jié)果驗(yàn)證>>FFT運(yùn)算。

2024-11-06 09:51:43 5640

5640

在 DeepSeek-R1(https://github.com/deepseek-ai/DeepSeek-R1) AI 模型橫空出世后,人們幾乎就立馬開始詢問如何在 MATLAB 中使用這些模型

2025-02-13 09:20:03 4220

4220

電子發(fā)燒友App

電子發(fā)燒友App

評論