多道脈沖幅度分析器不僅能自動獲取能譜數(shù)據(jù),而且一次測量就能得到整個能譜,因此可大大減少數(shù)據(jù)采集時間,與此同時,其測量精度也顯著提高。自從20世紀(jì)50年代以來,

2010-09-25 09:26:13 2658

2658

數(shù)字濾波器的濾波效果良好。通過SignalCompiler把模型轉(zhuǎn)換成VHDL語言加入到FPGA的硬件設(shè)計中,從QuartusⅡ軟件中的虛擬邏輯分析工具SignalTapⅡ中得到數(shù)字濾波器實時的結(jié)果波形圖,結(jié)果符合預(yù)期。

2013-10-08 13:39:06 10636

10636

本方案利用FPGA實現(xiàn)了巴特沃茲IIR數(shù)字帶通濾波器,并給出較為詳細(xì)的方案設(shè)計過程。實驗結(jié)果證明了所設(shè)計的濾波器完全滿足預(yù)定設(shè)計要求,從而也證實了本方案的有效性、可行性。

2014-02-13 10:58:32 7689

7689 多道脈沖幅度分析儀和射線能譜儀是核監(jiān)測與和技術(shù)應(yīng)用中常用的儀器。##FPGA

2014-06-09 10:42:39 1950

1950

本文簡要介紹了FIR數(shù)字濾波器的結(jié)構(gòu)特點和基本原理,提出基于FPGA和DSP Builder的FIR數(shù)字濾波器的基本設(shè)計流程和實現(xiàn)方案。##FIR 數(shù)字濾波器的詳細(xì)設(shè)計。

2014-07-24 15:30:05 9476

9476

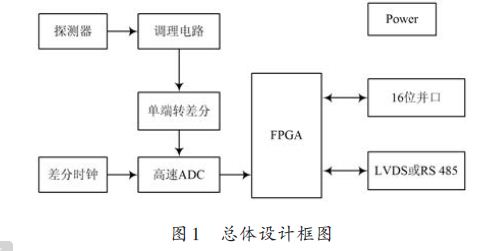

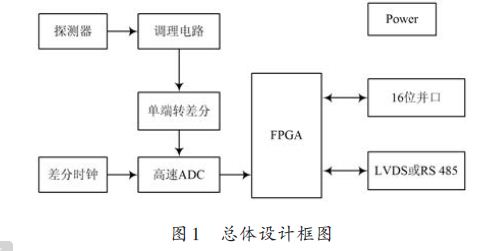

基于FPGA 的數(shù)字核脈沖分析器硬件設(shè)計方案,該方案采用現(xiàn)場可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設(shè)計。

2015-02-03 09:55:05 2373

2373

本文選用TI公司的雙核 DSP OMAP-L138作為本設(shè)計的微處理器,并實現(xiàn)了一種數(shù)字示波器微處理器硬件設(shè)計。

2015-04-20 10:28:57 4250

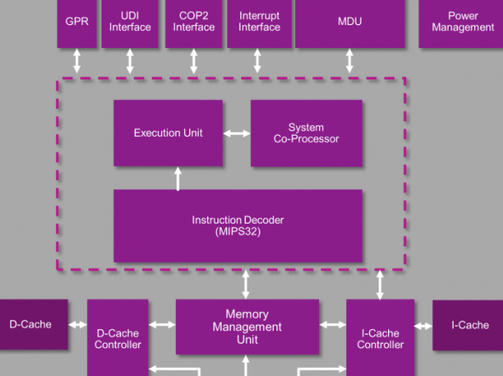

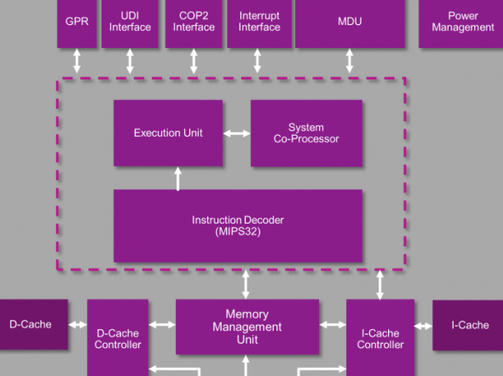

4250 課程的地方在于首次采用了一款純粹的商用軟核CPU用于研究目的,用戶可以在此課程的系統(tǒng)集成環(huán)境下詳細(xì)、深入的探索計算機架構(gòu)。 MIPSfpga使用一款MIPS系列軟核IP具體來講是microAptiv核,PIC32MK處理器采用的既是此款軟核。該核面向的是可編程邏

2018-05-21 10:17:01 8273

8273

本帖最后由 王棟春 于 2019-2-22 22:21 編輯

600W數(shù)字電源設(shè)計方案資料(硬件設(shè)計資料,軟件例程)

2019-02-22 22:20:23

工業(yè)自動化程度的不斷提高,變頻器也得到了非常廣泛的應(yīng)用。本文為大家介紹幾種變頻器的設(shè)計方案,包含完整軟硬件方案。基于Simulink的數(shù)字下變頻器設(shè)計及其FPGA實現(xiàn)本文利用MATLAB

2015-12-14 11:39:27

FPGA典型設(shè)計方案精華匯總

2012-08-16 16:29:32

各位FPGA設(shè)計大賽參賽者注意了:小編這里幫大家解釋一下設(shè)計方案提交規(guī)則和活動時間安排

自4月23日比賽開始,參賽者報名之后即可提交設(shè)計方案。設(shè)計方案提交的截止日期是活動結(jié)束,暨設(shè)計方案評選的最后

2012-05-04 10:27:46

本帖最后由 eehome 于 2013-1-5 10:02 編輯

數(shù)字語音解碼器的低功耗設(shè)計方案

2012-08-20 12:50:40

專家好,

CCS調(diào)試程序過程中,需要分析下各函數(shù)的執(zhí)行時間,CCS中提供了性能分析器profile

Q1:性能分析器profile是否只能在Simulator下才能使用,Emulator下沒有這個功能?

Q2:性能分析器profile的使用方法是否有相應(yīng)的教程參考?

謝謝

NanShan

2018-06-21 19:20:12

,系統(tǒng)建模分析器。本文檔介紹該工具的使用方法。

系統(tǒng)建模分析器

如何運行建模分析器

系統(tǒng)建模分析器

例1:光束清理濾波器

示例 – 光束清理濾波器

光束清理濾波器 – 光源

光束清理濾波器

2024-12-19 12:36:57

,系統(tǒng)建模分析器。本文檔介紹該工具的使用方法。

系統(tǒng)建模分析器

如何運行建模分析器

系統(tǒng)建模分析器

例1:光束清理濾波器

示例 – 光束清理濾波器

光束清理濾波器 – 光源

光束清理濾波器

2025-01-14 09:45:39

技術(shù)10.4.2 基于FPGA的千兆以太網(wǎng)MAC控制器實現(xiàn)方案10.4.3 Xilinx 千兆以太網(wǎng)MAC IP Core10.5 本章小結(jié)第11章時序分析原理以及時序分析器的使用11.1 時序分析的作用

2012-04-24 09:23:33

國內(nèi)譜儀技術(shù)多年來一直停留在模擬技術(shù)水平上,數(shù)字化能譜測量技術(shù)仍處于方法研究階段。為了滿足不斷增長的高性能能譜儀需求,迫切需要研制一種數(shù)字化γ能譜儀。通過核脈沖分析儀顯示在顯示器上的核能譜幫助人們了解核物質(zhì)的放射性的程度。

2019-07-03 07:35:52

發(fā)揮;(3)影像處理的解決方案可在數(shù)分鐘內(nèi)完成;(4)達(dá)成硬件階層的快速開發(fā)。使用Visual Applets,不必?fù)碛休^深的硬件知識,如數(shù)字電路、時間分析、FPGA硬件設(shè)計語言。使用VisuaI

2019-05-05 08:30:00

摘要

線柵偏振器,可以使透射光產(chǎn)生線性偏振狀態(tài),是眾多應(yīng)用中常見的一種光學(xué)元件。由于它們的結(jié)構(gòu)在亞波長范圍內(nèi),因此必須對光的傳播進行嚴(yán)格的處理。VirtualLab的偏振分析器及其內(nèi)置的RCWA

2025-01-13 08:59:04

一種基于FPGA的簡易頻譜分析儀設(shè)計方案,其優(yōu)點是成本低,性能指標(biāo)滿足教學(xué)實驗所要求的檢測信號范圍。

2021-04-30 06:43:21

了非常廣泛的應(yīng)用。本文為大家介紹幾種變頻器的設(shè)計方案,包含完整軟硬件方案。基于Simulink的數(shù)字下變頻器設(shè)計及其FPGA實現(xiàn)

2019-08-28 07:42:25

描述圖形音頻分析器 16x32

2022-08-24 06:38:03

基于FPGA的16位數(shù)據(jù)路徑的AESIP核提出一種基于FPGA 的16位數(shù)據(jù)路徑的高級加密標(biāo)準(zhǔn)AES IP核設(shè)計方案。該方案采用有限狀態(tài)機實現(xiàn),支持密鑰擴展、加密和解密。密鑰擴展采用非并行密鑰擴展

2012-08-11 11:53:10

基于FPGA的數(shù)字脈沖壓縮技術(shù)1.數(shù)字脈沖壓縮實現(xiàn)原理2.電路設(shè)計2.1APEX2OKE系列FPGA 簡介2.2 基于FPGA 的算法研究及實現(xiàn) 2.3 脈沖壓縮在FPGA 上的實現(xiàn)

2011-03-02 09:41:50

使用。 本文基于快速傅里葉IP核可復(fù)用和重配置的特點,實現(xiàn)一種頻域的FPGA數(shù)字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設(shè)計靈活,調(diào)試方便,可擴展性強的特點。 1 系統(tǒng)功能硬件

2018-11-09 15:53:22

上學(xué)時做的變頻器設(shè)計方案,利用simulink仿真,基于FPGA的變頻器設(shè)計方案。

2014-09-10 10:40:12

基于FPGA的數(shù)據(jù)無阻塞交換設(shè)計方案,不看肯定后悔

2021-04-29 06:48:07

此提供了新的解決方案。IP核(IP Core)是具有特定電路功能的硬件描述語言程序,可較方便地進行修改和定制,以提高設(shè)計效率[3]。本文研究了基于FPGA的數(shù)據(jù)采集控制器IP 核的設(shè)計方案和實現(xiàn)方法,該IP核既可以應(yīng)用在獨立IC芯片上,還可作為合成系統(tǒng)的子模塊直接調(diào)用,實現(xiàn)IP核的復(fù)用。

2019-07-09 07:23:09

多種EDA工具的FPGA設(shè)計方案

2012-08-17 10:36:17

如何用FPGA實現(xiàn)DVB碼流分析功能的嵌入式設(shè)計方案?

2021-04-28 06:19:10

多道脈沖幅度分析器結(jié)構(gòu)由那幾部組成基于LPC2134的多道脈沖幅度分析器設(shè)計

2021-04-09 06:44:29

本文是基于FPGA的數(shù)字示波器圖文顯示系統(tǒng)的硬件/軟件的設(shè)計思路和設(shè)計方案。

2021-05-08 07:24:13

本文的創(chuàng)新點是提出了一種基于FPGA的高速數(shù)據(jù)中繼器設(shè)計方案,并綜合分析了ASIC和NP等方法設(shè)計的高速網(wǎng)絡(luò)中繼器設(shè)計方法,在設(shè)計的功能和靈活性兩方面做了很好的權(quán)衡。

2021-04-29 06:45:51

求一種基于FPGA的HDLC協(xié)議控制器設(shè)計方案

2021-04-30 06:53:06

求一種基于FPGA的永磁同步電機控制器的設(shè)計方案。

2021-05-08 07:02:07

求一種基于RK3288 Cortex-A17四核處理器的政務(wù)服務(wù)一體機硬件設(shè)計方案

2022-03-03 12:59:57

摘要:本文介紹了虛擬頻譜分析儀的設(shè)計方案,設(shè)計了該系統(tǒng)的硬件部分與軟件部分。該系統(tǒng)以數(shù)據(jù)采集卡,PC機為硬件開發(fā)平臺,以圖形化編程語言LabVIEW為軟件開發(fā)平臺,將虛擬儀器技術(shù)運用到頻譜分析中來,增強了儀器的功能,節(jié)省了儀器的開發(fā)時間。

2019-06-11 06:43:23

dimond抓取內(nèi)部信號工具有:插入器,分析器。插入器生產(chǎn)后綴文件為rvl,分析器后綴為rva。FPGA每次斷電后,需要重拔插USB 口才可燒寫(軟件bug)。FPGA每次斷電后,需要找到對應(yīng)文件夾

2018-12-03 09:00:37

獵頭職位:硬件研發(fā)工程師(FPGA)【北京】崗位職責(zé):1、基于FPGA技術(shù)實現(xiàn)計算機體系結(jié)構(gòu)設(shè)計; 2、利用可編程邏輯設(shè)計技術(shù)進行產(chǎn)品設(shè)計與實現(xiàn); 3、分析確認(rèn)設(shè)計需求,評估芯片選型,制定設(shè)計方案

2016-11-14 15:33:13

多道脈沖幅度分析器的結(jié)構(gòu)是怎樣設(shè)計的?多道脈沖幅度分析器的硬件是如何設(shè)計的?怎樣去設(shè)計多道脈沖幅度分析器的相關(guān)軟件?怎樣對多道脈沖幅度分析器的硬件電路進行仿真測試?

2021-04-14 06:31:11

提出了采用Verilog HDL 設(shè)計I2C 總線分析器的方法,該I2C 總線分析器支持三種不同的工作模式:被動、主機和從機模式,并提供了嵌入式系統(tǒng)設(shè)計接口。通過硬件總體框架分析,分

2009-08-10 15:32:18 40

40 VPGE(Visual Parser Generation Environment)是一個可視化語法分析器集成開發(fā)環(huán)境,除了具有良好的界面和強大的調(diào)試功能,其LALR(1)分析器的生成速度達(dá)到并超過公認(rèn)的分析器生成速度最快

2009-08-29 10:04:13 16

16 轉(zhuǎn)換到TimeQuest時序分析器教程(電子書)

2010-03-23 16:49:43 0

0 本文介紹一種采用電池供電的ADc和袖珍計算機Pc一1500通過接口電路組成的256道脈沖幅度分析器。其分析范圍為0.1—5V,微分非線性好于±2.5%,耗電約180mw,連續(xù)工作24小時道位漂移不

2010-05-19 09:12:18 30

30 摘要:通過對高精度脈沖幅度分析器的電路分析,得出了在使用過程中,采用高精度和低溫系數(shù)的電壓基準(zhǔn)集成塊,可保證該脈沖幅度分析器比傳統(tǒng)脈沖幅度分析器靈敏度高、穩(wěn)定

2010-05-25 08:39:59 29

29 本文提出了基于FPGA技術(shù)實現(xiàn)數(shù)字復(fù)接系統(tǒng)的設(shè)計方案,并介紹了有代表性的較簡單的四路同步復(fù)接器系統(tǒng)總體設(shè)計。硬件電路調(diào)試證明,該方案是行之有效的。

2010-08-06 16:33:16 30

30 摘要:提出一種基于FPGA技術(shù)的多路模擬量、數(shù)字量采集與處理系統(tǒng)的設(shè)計方案,分析整個系統(tǒng)的結(jié)構(gòu),并討論FPGA內(nèi)部硬件資源的劃分和軟件的設(shè)計方案等。本設(shè)計

2009-06-20 15:05:11 1956

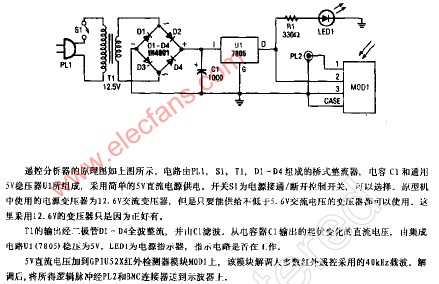

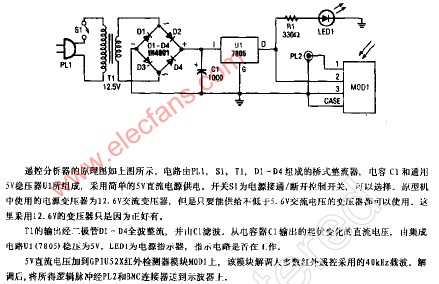

1956 遙控分析器

2009-09-18 14:14:38 683

683

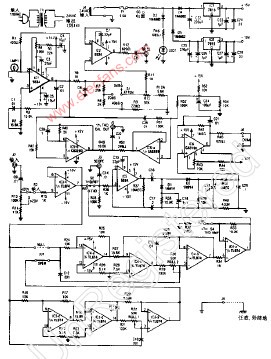

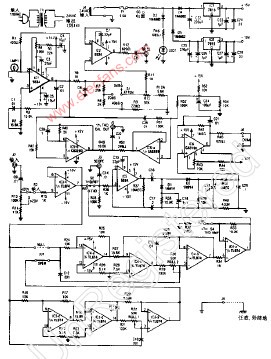

諧波失真分析器

電路包括一個1KHZ的低失真

2009-09-23 14:34:24 944

944

基于PCI IP核的碼流接收卡的設(shè)計

本文介紹了一種基于Altera公司的PCI接口IP核的DVB碼流接收系統(tǒng)的硬件設(shè)計方案及設(shè)計要點的分析。該設(shè)計采用Altera公司的新一代FPGA

2009-09-26 18:02:08 912

912

基于ADC和FPGA脈沖信號測量的設(shè)計方案

0引言

測頻和測脈寬現(xiàn)在有多種方法。通常基于MCU的信號參數(shù)測量,由于其MCU工作頻率很低,所以能夠達(dá)到的精度也

2009-12-21 09:13:23 2199

2199

基于FPGA的高速定點FFT算法的設(shè)計方案

引 言 快速傅里葉變換(FFT)作為計算和分析工具,在眾多學(xué)科領(lǐng)域(如信號處理、圖像處理、生物信息學(xué)、計算物理

2010-02-09 10:47:50 1345

1345

網(wǎng)絡(luò)分析器,網(wǎng)絡(luò)分析器原理是什么?

網(wǎng)絡(luò)分析器

具有發(fā)現(xiàn)并解決各種故障特性的硬件或軟件設(shè)備

2010-03-22 11:25:21 1261

1261 協(xié)議分析器在WLAN中的應(yīng)用

協(xié)議分析器廣泛應(yīng)用于有線網(wǎng)絡(luò),成為一類極有用的測試和維護工具。然而,在WLAN領(lǐng)域,這個問題很有可

2010-03-29 17:11:30 634

634 多種EDA工具的FPGA設(shè)計方案

概述:介紹了利用多種EDA工具進行FPGA設(shè)計的實現(xiàn)原理及方法,其中包括設(shè)計輸入、綜合、功能仿真、實現(xiàn)、時序仿真、配

2010-05-25 17:56:59 895

895

虛擬聲譜分析器軟件詳細(xì)介紹 此軟件操作方便快捷

2011-02-11 15:53:54 99

99 摘要:介紹一種以數(shù)字信號處理器(DSP)為核心的多道脈沖幅度分析器,它能夠進行核信號的采集\處理以及傳輸,然后經(jīng)過上位機的處理實現(xiàn)對射線的能量和強度的分析.DSP的采用保證了信號處理的實時性. 關(guān)鍵詞:DSP MCA A/D轉(zhuǎn)換 D/A轉(zhuǎn)換 探測器 高壓

2011-02-27 13:33:23 34

34 Fortify的靜態(tài)代碼分析器(Static Code Analyzer,SCA)是組成Fortify 360的三個分析器之一。SCA工作在開發(fā)階段,以用于分析應(yīng)用程序的源代碼是否存在安全漏洞。這種類型的分析與程序跟蹤分析

2011-04-07 20:32:46 22

22 多道脈沖幅度分析器不僅能自動獲取能譜數(shù)據(jù),而且一次測量就能得到整個能譜,因此可大大減少數(shù)據(jù)采集時間,與此同時,其測量精度也顯著提高。

2011-10-13 12:01:13 5567

5567

本文將重點介紹“交換端口分析器(SPAN)”的工作原理及配置方法。

2012-02-03 14:09:03 1166

1166 以Altera公司的Quartus Ⅱ 7.2作為開發(fā)工具,研究了基于FPGA的DDS IP核設(shè)計,并給出基于Signal Tap II嵌入式邏輯分析儀的仿真測試結(jié)果。將設(shè)計的DDS IP核封裝成為SOPC Builder自定義的組件,結(jié)合

2012-04-05 16:04:34 85

85 電子發(fā)燒友網(wǎng): 本文主要分析了多道脈沖幅度分析器忙時間的形成特點,設(shè)計出來一套能減小系統(tǒng)忙時間的方案,從而大大地減少由于忙時間造成的脈沖漏計數(shù)。同時分析了改進后系統(tǒng)

2012-06-11 08:47:26 37

37 基于FPGA的OLED真彩色顯示設(shè)計方案

2017-01-18 20:35:09 25

25 數(shù)字電路設(shè)計方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 基于LPC1764的多道脈沖幅度分析器的電路設(shè)計

2017-09-25 11:45:51 4

4 基于CPLD_ARM的多道脈沖幅度分析器設(shè)計

2017-09-25 12:55:06 8

8 核能譜輻射測量技術(shù)是一種綜合性很強的技術(shù),是核探測技術(shù)、電子技術(shù)、計算機技術(shù)等多學(xué)科相互交叉滲透的產(chǎn)物。具有現(xiàn)場、多元素快速分析等特點。核能譜輻射測量技術(shù)已經(jīng)不僅用于核研究,也在地質(zhì)學(xué)、醫(yī)學(xué)、環(huán)境學(xué)

2018-01-23 09:45:01 4916

4916

基于FPGA三相正弦波pwm控制器的設(shè)計方案

2018-04-08 17:33:39 30

30 核分析能譜測量所用的多道脈沖幅度分析器,在進行模數(shù)轉(zhuǎn)換時需要一定的時間,會使分析器產(chǎn)生漏計數(shù),給測量分析帶來誤差,需要對死時間進行修正。針對這種情況,探討了兩種有效的死時間修正方法。核分析能譜測量

2018-04-09 11:11:45 12

12 本文介紹一種采用電池供電的ADC和袖珍計算機PC-1500通過接口電路組成的256道脈沖幅度分析器。

2018-04-09 11:19:24 9

9 針對當(dāng)前對多道脈沖幅度分析器的高處理速度、高集成度、友好人機交互的要求,采用三星公司生產(chǎn)的S3C2410芯片設(shè)計并實現(xiàn)了一種便攜式的核數(shù)據(jù)采集系統(tǒng)設(shè)計方案。對傳統(tǒng)的多道脈沖幅度分析器進行改進和簡化

2018-04-09 11:51:32 6

6 基于FPGA的調(diào)焦電路設(shè)計方案資料下載

2018-05-07 15:53:08 10

10 Seth為DirectX提供了圖形幀分析器。

了解這款功能強大的分析儀的基本特性和功能。

2018-11-12 06:35:00 2700

2700 Seth提供圖形監(jiān)視器,系統(tǒng)分析器和HUD。

這些組件構(gòu)成了英特爾圖形性能分析器中的實時分析工具。

2018-11-07 06:53:00 6201

6201 基于CPLD/FPGA的半整數(shù)分頻器設(shè)計方案

2021-06-17 09:37:02 21

21 基于FPGA的偽隨機數(shù)發(fā)生器設(shè)計方案

2021-06-28 14:36:49 4

4 開源網(wǎng)絡(luò)協(xié)議分析器WireShark軟件下載

2021-07-23 09:22:08 15

15 在前文中,我們了解到兩種 FPGA 嵌入式處理器核方案:軟核與硬核。本文將展開討論軟核在一個基于 FPGA 通信系統(tǒng)中的應(yīng)用。軟核,由 FPGA...

2022-02-07 10:07:43 4

4 電子發(fā)燒友網(wǎng)站提供《圖形音頻分析器開源設(shè)計.zip》資料免費下載

2022-08-02 15:18:04 0

0 LogAnalyzer(日志分析器)是HostMonitor的一個輔助應(yīng)用程序,它包含在高級主機監(jiān)視器軟件包中。

2022-10-13 15:42:31 2904

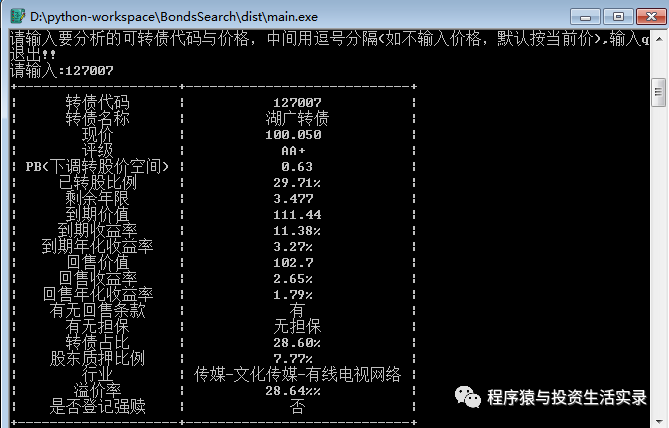

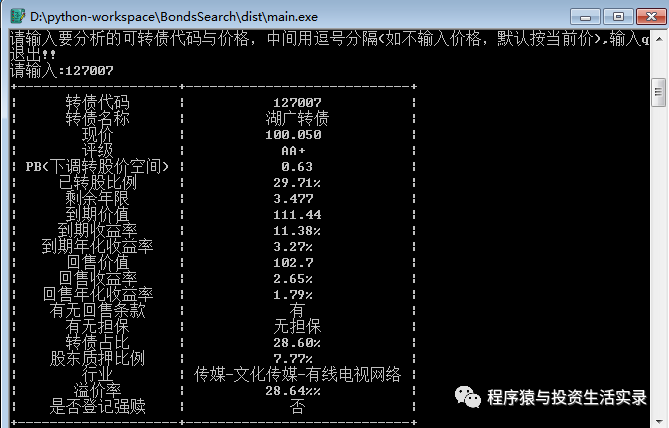

2904 用Python寫個可轉(zhuǎn)債分析器

2023-02-16 15:13:00 2314

2314

轉(zhuǎn)換器分析器用戶指南

2023-04-27 18:48:01 0

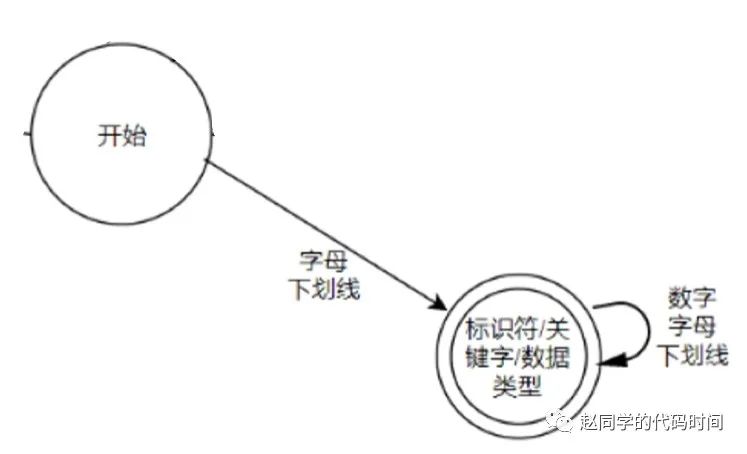

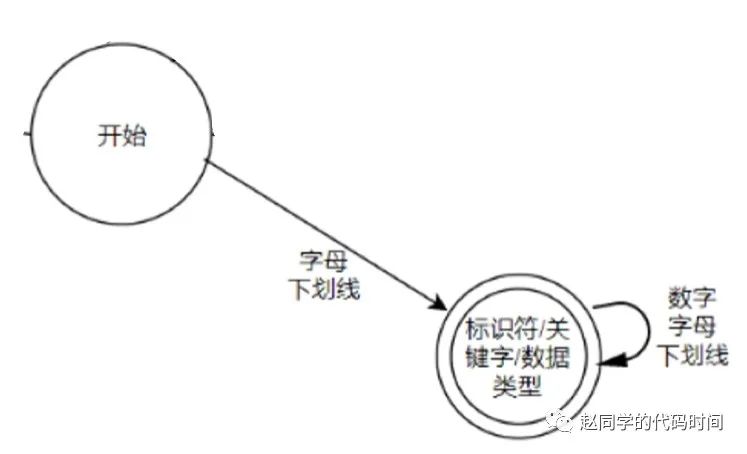

0 在開始手寫詞法分析器之前呢,我們得先準(zhǔn)備好一些零件,規(guī)劃好將要使用哪些函數(shù),如果函數(shù)沒有現(xiàn)成的,那還得自己寫。

2023-05-23 11:20:58 1182

1182

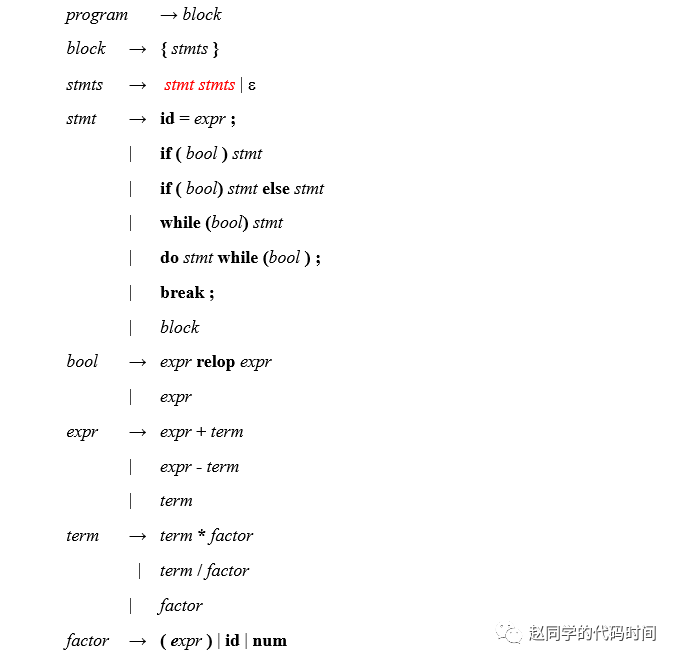

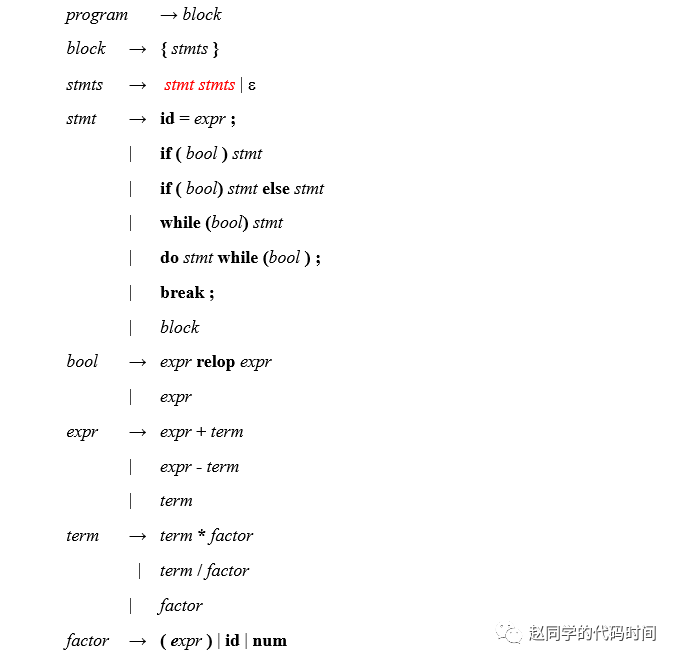

在之前已經(jīng)通過手寫的方式實現(xiàn)了一個詞法分析器,現(xiàn)在,我將利用之前手寫的詞法分析器,使用遞歸下降的方式,實現(xiàn)一個簡單的語法分析器。

2023-05-23 11:24:02 2733

2733

電子發(fā)燒友網(wǎng)站提供《基于ARM核的雙芯片GPs接收機的硬件設(shè)計方案.pdf》資料免費下載

2023-10-18 09:25:19 0

0 電子發(fā)燒友網(wǎng)站提供《基于FPGA的PCI硬件加解密卡的設(shè)計方案.pdf》資料免費下載

2023-10-18 11:18:03 1

1 電子發(fā)燒友網(wǎng)站提供《基于CPLD/FPGA的多串口擴展設(shè)計方案.pdf》資料免費下載

2023-10-27 09:45:17 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評論