為了實現激光-水聲淺海地形遙感探測中水聲信號的實時解調與處理,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統的設計方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結合

2013-10-29 10:10:02 3060

3060

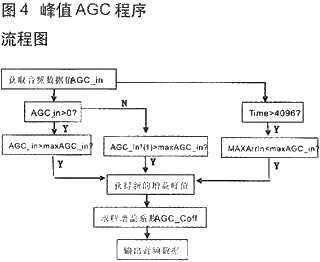

為了研究數字化γ能譜儀,本文提出一種基于FPGA的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。用QuartusⅡ軟件在FPGA平臺上完成了數字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 2545

2545

本文介紹了一種基于555定時器和單片機的數顯式電阻和電容測量系統設計方案。該系統利用555和待測電阻或電容組成多諧振蕩器,通過單片機測量555輸出信號的周期,根據周期與待測電阻或電容的數學關系計算出

2013-12-02 14:16:49 4338

4338

本文以FPGA作為核心處理器,提出了一種基于FPGA多路機載冗余圖像處理系統的設計方案。##整個系統顯示的分辨率為1600×1200@60 Hz,信號位為真彩色24b,則一幀圖像所需需要存儲的容量C≈47 Mb。##讀寫操作交替進行仿真圖如圖5所示。圖5中包含了兩個寫入操作,一個讀取操作。

2014-01-07 10:28:32 3905

3905

本文以X射線透射衰減規律為基礎,提出了一種基于DSP的X射線能譜數據采集系統的設計方案。##經過前置放大和帶通濾波處理后的信號仍然比較微弱,因此脈沖信號在送入ADC電路之前還需進一步放大。

2014-01-08 11:56:49 4911

4911

為解決現場測試系統中微弱信號的高速實時采集處理和及時可靠存儲的問題,本文提出了基于PCI總線的數據采集電路的設計方案,該方案將模擬信號通過高速A/D芯片有效采樣,在FPGA的控制下將數據上傳到PC機

2014-01-24 09:45:29 4027

4027

本文以標準的I2C 總線協議為基礎,提出了一種基于FPGA的I2C SLAVE 模式總線的設計方案。方案主要介紹了SLAVE 模式的特點。給出了設計的原理框圖和modelsim 下的行為仿真時序圖

2014-02-26 11:39:13 19994

19994 基于FPGA 的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。

2015-02-03 09:55:05 2373

2373

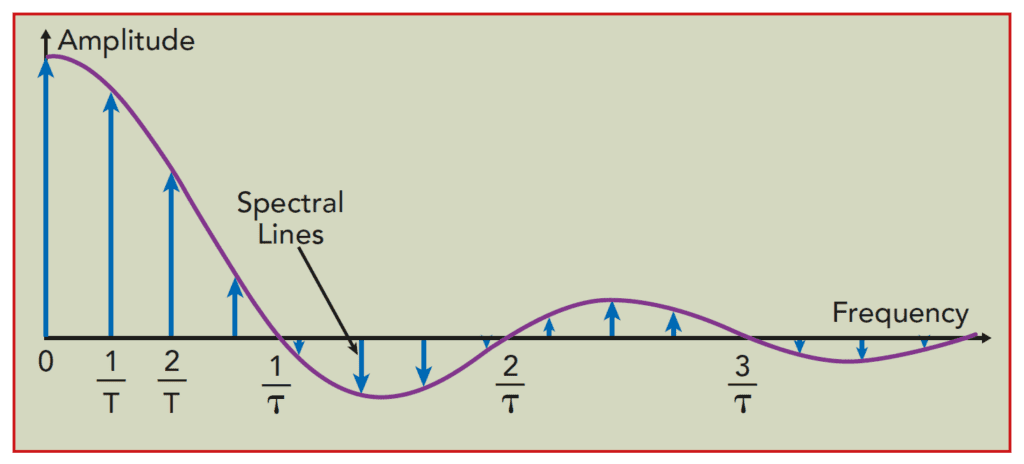

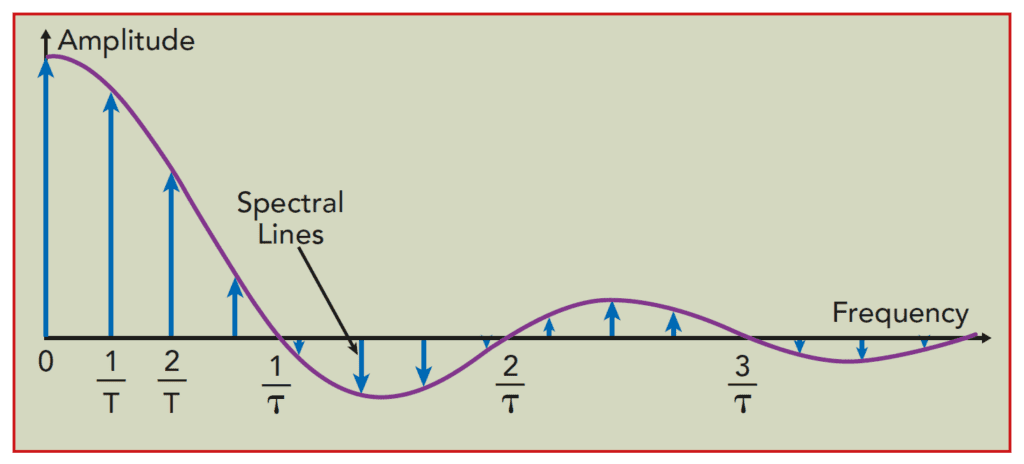

相位噪聲是雷達系統性能的重要參數。大多數雷達采用脈沖調制,目標的速度是通過檢測雷達反射信號相對于發射器頻率的多普勒頻移得出的。發射器自身的相位噪聲會強烈影響該測量的分辨率和精度,限制了雷達的檢測閾值和精度。因此,脈沖信號的相位噪聲已成為越來越重要的測量內容。

2022-09-23 16:40:10 7844

7844

FPGA典型設計方案精華匯總

2012-08-16 16:29:32

本帖最后由 csuly 于 2011-6-16 22:44 編輯

大俠你好! 菜鳥求助了。我需要檢測一個50Hz脈寬為20us的脈沖信號與一個15KHz脈寬為5us的脈沖信號。附件中的程序,我

2011-06-16 22:37:12

各位FPGA設計大賽參賽者注意了:小編這里幫大家解釋一下設計方案提交規則和活動時間安排

自4月23日比賽開始,參賽者報名之后即可提交設計方案。設計方案提交的截止日期是活動結束,暨設計方案評選的最后

2012-05-04 10:27:46

本人想做一個陣列接收模塊,初步想法是FPGA+adc芯片,采集16Khz左右正弦信號,得到其相位與幅度信息。如果要做64路,adc采用并行ad,這樣需要的IO口會很多,但如果不用一片fpga就不能同時采集信號。想問一下有沒有什么好的解決方案呢?求大佬關注一下!!!謝謝!!!

2019-03-06 19:01:51

基于PCIE總線的脈沖采集方案-坤馳科技一、概述:為采集高速脈沖輸入信號,并能實施將采集數據傳入PC主內存,系統方案規格如下:1.采用12bit1Gsps高速ADC。2.50歐姆阻抗輸入。直流藕合

2016-08-15 14:59:39

在設計中想用上AD9254作為ADC,在設計過程中發現datasheet內部提供了多種時鐘設計方案,由于設計的限制,想要省去所有方案中均推薦使用的AD951x芯片,請問是否有曾經使用過該款AD的同仁,使用直接從FPGA差分時鐘引腳引出的時鐘信號,是否能夠滿足設計的要求?

2018-11-02 09:14:32

現在要做一個渦輪流量計脈沖輸出的測量電路,網上查了下 一般是小于等于0.8V為低電平 大于等于8V為高電平 請問怎么設計電路才能用STM32來測量這個信號?就是說怎么才能將這個電平轉換為與STM32兼容的電平信號?

2016-11-07 16:21:35

【推薦】雙脈沖測量解決方案 現在在越來越多的功率器件測量中比如場效應晶體管(MOSFET)和絕緣門雙極晶體管(IGBT),這些功率器件提供了快速開關速度,能夠耐受沒有規律的電壓峰值,被廣泛應用于電源

2020-02-14 11:16:06

介紹一種包含千兆采樣率ADC的系統設計方案

2021-05-14 06:07:02

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

FPGA為平臺怎么測量脈沖寬度的verilog語言

2017-03-21 15:16:01

一種基于FPGA的簡易頻譜分析儀設計方案,其優點是成本低,性能指標滿足教學實驗所要求的檢測信號范圍。

2021-04-30 06:43:21

分享一款不錯的采用FPGA的集群通信移動終端設計方案

2021-05-25 06:32:04

本文以星載測控系統為背景,提出了一種基于 Actel Flash FPGA的高可靠設計方案。采用不易發生單粒子翻轉的 flash FPGA芯片,結合 FPGA內部的改進型三模冗余、分區設計和降級重構,實現了高實時、高可靠的系統。

2021-05-10 06:58:47

利用FPGA的無線通信收發模塊設計方案[hide][/hide]

2009-11-26 10:25:56

,乃至更高幅度的接口電平,通常為功率型電流驅動信號。本文提出了一種兩級測試系統的設計思路,給出了在較寬的范圍內兼容不同接口電平的脈沖信號檢測系統的設計方案,采用標準CPCI總線接口設計,具有良好的兼容性

2012-09-01 16:09:40

本帖最后由 eehome 于 2013-1-5 10:11 編輯

基于FPGA及VHDL的LED點陣漢字滾動顯示設計方案

2012-08-19 23:20:48

上學時做的變頻器設計方案,利用simulink仿真,基于FPGA的變頻器設計方案。

2014-09-10 10:40:12

基于FPGA的數據無阻塞交換設計方案,不看肯定后悔

2021-04-29 06:48:07

。

設計方案

設計一個技術式頻率計,其頻率測量范圍為10Hz到10MHz,測量結果用6只數碼管顯示。有一個撥動開關用來使頻率計復位。有兩只LED,分別用來指示計數器是否正在工作與指示計數器是否有溢出

2024-03-31 16:22:35

1 引言 在學習《電子線路》、《信號處理》等電子類課程時,高校學生只是從理論上理解真正的信號特征。不能真正了解或觀察測試某些信號。而幅頻特性和相頻特性是信號最基本的特征.這里提出了基于單片機和FPGA的頻率特性測試儀的設計方案,可使學生在實踐中真正觀察和測試信號的頻率特性。

2019-07-22 08:19:34

多種EDA工具的FPGA設計方案

2012-08-17 10:36:17

動態相位對準(DPA)電路和對新的外部存儲器接口的支持。AD芯片可以穩定工作在100 MHz,FPGA速度可高達幾百MHz,故可保證系統的測量精度。那么有誰知道如何利用ADC和FPGA設計脈沖信號測量嗎?

2019-07-31 06:25:45

請教:我想把FPGA輸出的TTL脈沖信號放大,波形的特征是:信號周期100us,脈沖寬度100ns,上升時間不大于50ns。

信號如圖所示:

目前想采用的方案是:

FPGA輸出的脈沖信號通過

2024-09-13 08:13:39

如何用FPGA實現DVB碼流分析功能的嵌入式設計方案?

2021-04-28 06:19:10

“玩轉FPGA:iPad2,賽靈思開發板等你拿”活動持續火爆進行中……………………活動得到了廣大電子工程師積極強烈的支持,為了回報電子工程師和網站會員,現在只需提交fpga設計方案,就有機會獲得賽靈

2012-07-06 17:24:41

求一種便攜式RC測量儀的設計方案

2021-05-11 06:32:02

求一種基于FPGA的HDLC協議控制器設計方案

2021-04-30 06:53:06

求一種基于FPGA的永磁同步電機控制器的設計方案。

2021-05-08 07:02:07

求一種數字式溫度測量電路的設計方案

2021-05-17 06:16:41

本文主要提出一種集中式插入法幀同步的FPGA的設計方案。

2021-06-02 06:07:10

測溫系統設計方案,原理方案都有,有圖有真相!

2014-09-05 16:29:53

如圖所示,一個直流信號上疊加上脈沖信號,波形的周期為6.25ms,脈沖信號共有40個,占的周期是3.75ms,脈沖信號的占空比可以調節。如果測量這個波形的有效值。非電氣專業,該向那個方向努力,求指點。

2016-12-06 17:02:56

ADC12DJ3200, PLL型號為LMK04828

ADC的采樣率為5GSPS,采樣時鐘提供2.5GSPS,sysref為3.90625MHz,模式為脈沖模式,一次發送8個脈沖,連接FPGA

2024-11-19 06:36:41

一種基于ADC和FPGA脈沖信號測量系統的設計方案

2021-05-12 06:43:44

根據電力監控系統的要求,提出一種基于FPGA技術的多路交流信號采集與處理系統的設計方法。分析整個系統的結構,并討論FPGA內部硬件資源的劃分和軟件的設計方案,以及各個功能

2009-05-16 14:47:58 27

27 在介紹了GPS 同步時鐘基本原理和FPGA 特點的基礎上,提出了一種基于FPGA 的GPS同步時鐘裝置的設計方案,實現了高精度同步時間信號和同步脈沖的輸出,以及GPS 失步后秒脈沖的平

2009-07-30 11:51:45 45

45 筆記本電腦VGA信號切換設計方案

2010-12-28 11:03:05 43

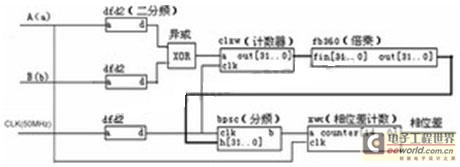

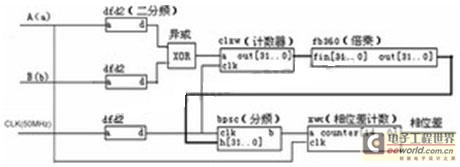

43 基于FPGA的高精度相位測量儀的設計方案

引言

隨著集成電路的發展,利用大規模集成電路來完成各種高速、高精度電子儀器的設計已經成為一種行之有

2009-11-12 09:52:47 1183

1183

毫微安電流測量技術面臨的挑戰與設計方案

對小電流的測量非常微妙。巧妙的模擬設計技術、正確的器件和設備都有助于測量。

要 點

小電流

2009-12-26 09:42:06 1572

1572 基于FPGA的光電抗干擾電路設計方案

光電靶的基本原理是:當光幕內的光通量發生足夠大的變化時,光電傳感器會響應這種變化而產生電信號。這就

2010-02-09 10:31:20 922

922

基于FPGA的高速定點FFT算法的設計方案

引 言 快速傅里葉變換(FFT)作為計算和分析工具,在眾多學科領域(如信號處理、圖像處理、生物信息學、計算物理

2010-02-09 10:47:50 1345

1345

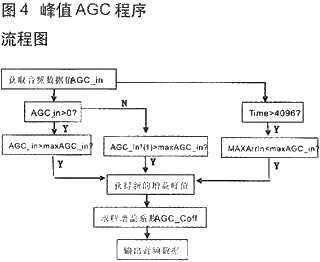

音頻信號采集與AGC算法的DSP設計方案

過去,對大音頻信號采用限幅方式,即對大信號進行限幅輸出

2010-03-05 16:06:08 2184

2184

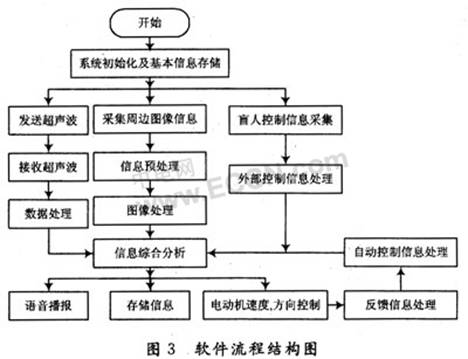

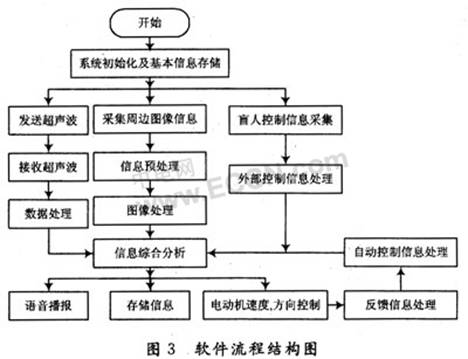

采用FPGA技術的智能導盲犬設計方案

眾所周知眼晴是“心靈之窗”,而對于突然失去或從未擁有過“心靈之窗”的盲人來說,生活上的困難與心理上

2010-03-22 09:40:28 1310

1310

基于Spartan-6的FPGA SP601開發設計方案

Spartan-6是Xilinx公司的FPGA批量應用有最低成本的FPGA,采用45nm低功耗銅工藝,在成本,性能和功耗上有最好的平衡.該系

2010-04-02 14:25:28 2758

2758 采用VC++程序的FPGA重配置設計方案利用現場可編程邏輯器件FPGA的多次可編程配置特點,通過重新下載存儲于存儲器的不同系統數據

2010-04-14 15:14:57 767

767

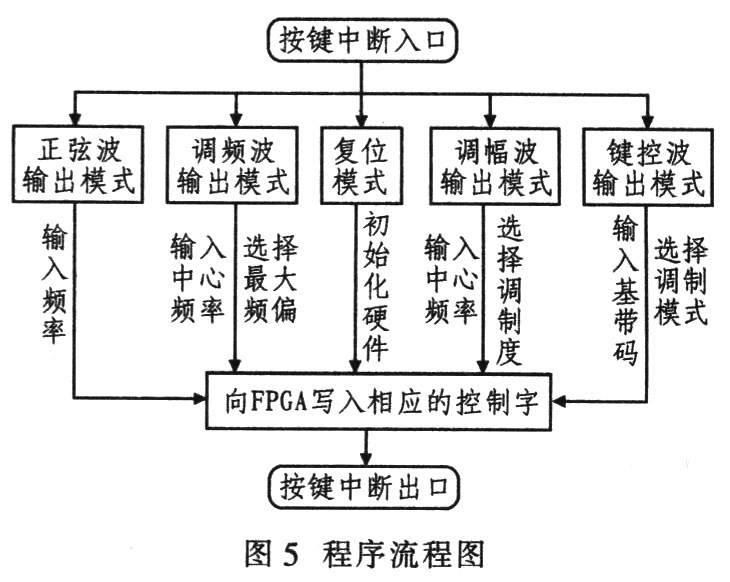

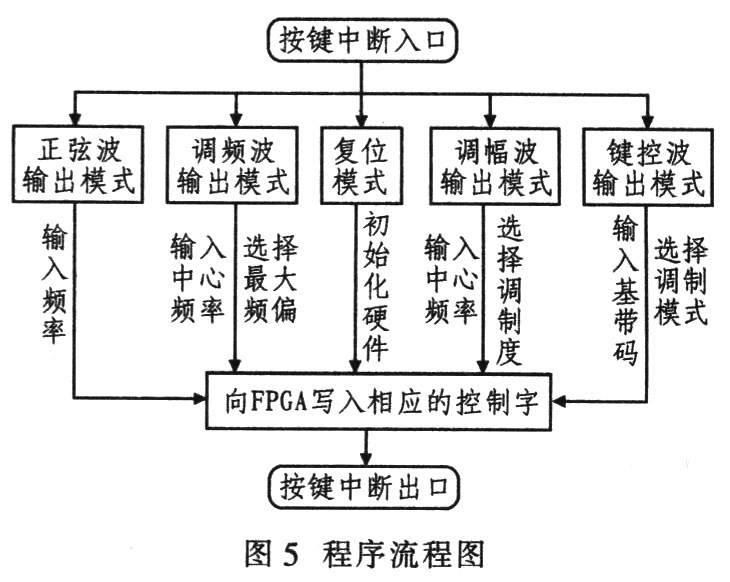

正弦信號發生器設計方案1 引言 為了精確地輸出正弦波、調幅波、調頻波、PSK及

2010-04-15 15:34:41 8065

8065

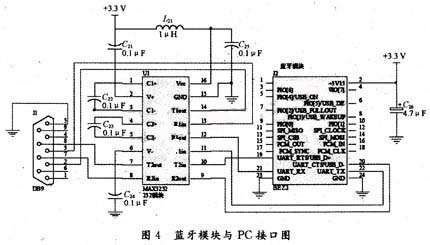

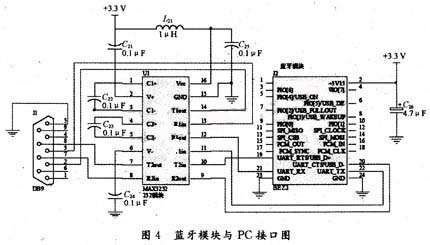

ARM和藍牙無線信號采集系統的設計方案

本文針對無線信號測試,提出一種基于ARM和藍牙的無線信號采集系統的設計與實現。

1 引 言

2010-05-15 18:27:09 1141

1141

多種EDA工具的FPGA設計方案

概述:介紹了利用多種EDA工具進行FPGA設計的實現原理及方法,其中包括設計輸入、綜合、功能仿真、實現、時序仿真、配

2010-05-25 17:56:59 895

895

示波器測量脈沖信號的擴展思路為快沿脈沖信號測量提供了解決方案。解決,隨著傳輸速度的提升, 脈沖信號 的上升時間越來越短,上升沿覆蓋了更寬的頻譜范圍,需要更短的測量時間問題

2011-07-25 10:58:39 35

35 電子發燒友網核心提示:本文提出了基于FPGA的噴油器脈寬處理的設計方案。在QuatusII自帶的仿真軟件下可以觀測到設置不同的脈寬控制參數可以達到輸出信號的占空比可調。整個系統下

2012-11-09 16:04:05 4455

4455 基于FPGA的ADC指標測量及測試系統。

2016-05-10 11:47:13 14

14 該程序基于stc15單片機,可測量脈沖信號的頻率,驅動ads7822測信號幅度,并且配置da:tlv5616輸出電壓,設置窗口比較器的比較電平,配合fpga測量脈沖信號的上升沿下降沿時間,fpga部分的程序在另一個附件

2016-08-17 11:54:06 19

19 基于FPGA技術的RS232接口時序電路設計方案

2017-01-26 11:36:55 30

30 基于FPGA的OLED真彩色顯示設計方案

2017-01-18 20:35:09 25

25 數字電路設計方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 電子發燒友網站提供《基于FPGA的脈沖信號參數測量儀的設計與實現.pdf》資料免費下載

2017-05-27 08:00:00 85

85 功能的下位機FPGA器件各模塊化電路的作用。經過設計和電路測試,輸出波形達到了技術要求,工作穩定可靠。 信號發生器是一種常用的信號源,廣泛應用于通信、測量、科研等現代電子技術領域。信號發生器的核心技術是頻率合成技術,主要方法有

2017-12-04 11:40:09 33

33 FPGA及其外圍電路是整個測量系統的核心。外圍電路包括以下幾個部分:1)電源轉換電路,將5V電源轉換為FPGA工作必需的3.3 V及2.5 V電源;2)程序存儲器電路,負責存儲可執行邏輯代碼,供

2018-02-17 03:02:00 2804

2804

基于FPGA三相正弦波pwm控制器的設計方案

2018-04-08 17:33:39 30

30 脈沖信號是一種離散信號,形狀多種多樣,與普通模擬信號(如正弦波)相比,波形之間在時間軸不連續(波形與波形之間有明顯的間隔)但具有一定的周期性是它的特點。最常見的脈沖波是矩形波(也就是方波)。脈沖信號

2018-04-28 11:18:26 63350

63350 基于FPGA的調焦電路設計方案資料下載

2018-05-07 15:53:08 10

10 本文首先介紹了脈沖信號測量工具,其次闡述了脈沖信號測量的步驟教程,最后介紹了用示波器測量脈沖信號的注意事項。

2018-08-21 17:45:19 38959

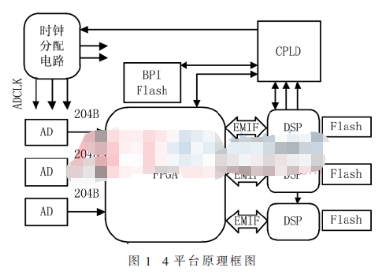

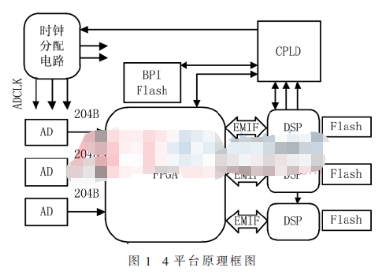

38959 新型多通道通用信號處理平臺主要包括高速AD芯片、Xilinx最新UltraScale系列FPGA和TI的多核DSP,原理框圖如圖1所示。其中FPGA和高速ADC之間數據傳輸采用JESD204B接口總線。

2020-07-16 09:25:16 3387

3387

用于精密測量和快速信號跟蹤的高精度SAR ADC

2021-05-18 09:11:46 12

12 AN-1494:使用AD7982差分脈沖星ADC轉換單端信號

2021-05-27 17:35:28 9

9 基于FPGA的二進制相移鍵控設計方案

2021-05-28 09:36:50 12

12 為研究脈沖星X射線輻射脈沖信號的特點需要記錄X射線脈沖信號的上升沿時刻與脈沖信號峰值。設計了基于FPGA的X射線脈沖信號數據采集系統。重點介紹了數據采集系統的組成、功能及硬件設計。其中,系統采用11

2021-06-01 09:37:44 17

17 基于CPLD/FPGA的半整數分頻器設計方案

2021-06-17 09:37:02 21

21 基于FPGA的偽隨機數發生器設計方案

2021-06-28 14:36:49 4

4 小信號放大電路設計方案匯總

2021-09-14 15:01:12 143

143 如何用示波器去測量脈沖信號以及測量脈沖信號對示波器有什么要求。

2021-10-04 08:49:00 17424

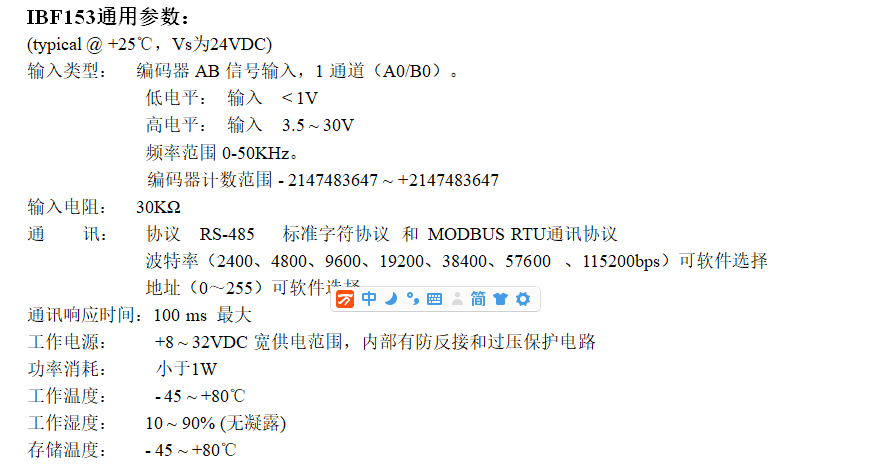

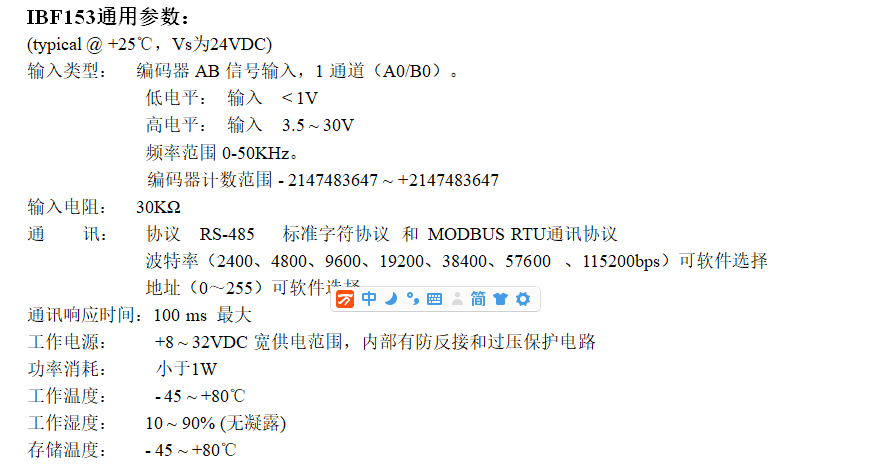

17424 ● 光柵尺脈沖信號測量

● 磁柵尺脈沖信號測量

● 三坐標系統位置測量

● 球柵尺脈沖信號測量

2022-11-26 14:25:06 1453

1453

● 編碼器脈沖信號測量

● 流量計脈沖計數或流量測量

● 生產線產品計數

● 物流包裹數量

2022-11-28 13:58:35 1020

1020

電子發燒友網站提供《基于FPGA的PCI硬件加解密卡的設計方案.pdf》資料免費下載

2023-10-18 11:18:03 1

1 電子發燒友網站提供《簡易信號發生器設計方案.pdf》資料免費下載

2023-10-20 09:43:18 1

1 電子發燒友網站提供《基于CPLD/FPGA的多串口擴展設計方案.pdf》資料免費下載

2023-10-27 09:45:17 4

4 電子發燒友網站提供《高速ADC電源設計方案.pdf》資料免費下載

2023-11-10 16:20:26 0

0 ,需要考慮以下幾個方面:硬件設備的選擇、采樣頻率的確定、實時數據傳輸和處理等。 首先,選擇合適的硬件設備是脈沖信號實時采集的首要任務。傳統的數據采集設備通常使用模數轉換器(ADC)進行采樣,但是對于高速脈沖信號的采集

2023-11-10 15:36:33 3122

3122 APPH信號源分析儀能夠輕松可靠地測量脈沖信號的絕對相位噪聲和加性相位噪聲,最高可達65 GHz。該儀器提供直觀可用的標準脈沖(選件:PULSE)或增強型極窄脈沖(選件 NPS)測量。LO前端輸出選項提供內部低噪聲脈沖信號源的輸出,而無需外部源來測量相加相位噪聲,并使測量設置更快,更直觀,更可靠。

2025-07-15 14:48:45 835

835

電子發燒友App

電子發燒友App

評論