賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 20763

20763

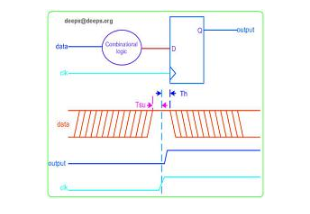

時鐘是整個電路最重要、最特殊的信號,系統(tǒng)內(nèi)大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時序邏輯狀態(tài)出錯。

2020-06-26 10:37:00 6144

6144

7系列FPGA時鐘資源通過專用的全局和區(qū)域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 2068

2068 當我剛開始我的FPGA設計生涯時,我對明顯更小、更不靈活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常簡單的時鐘規(guī)則之一是盡可能只使用單個時鐘。當然,這并不總是可能的,但即便如此,時鐘的數(shù)量仍然有限。

2022-09-30 08:49:26 2145

2145 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現(xiàn)效果;如果使用不當,不但會影響設計的工作頻率和穩(wěn)定性等,甚至會導致設計的綜合、實現(xiàn)過程出錯

2023-07-24 11:07:04 1443

1443

時鐘周期約束是用于對時鐘周期的約束,屬于時序約束中最重要的約束之一。

2023-08-14 18:25:51 1777

1777 通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區(qū)域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現(xiàn)高性能和可靠的時鐘分配

2023-08-31 10:44:31 4432

4432

時鐘設計方案 在復雜的FPGA設計中,設計時鐘方案是一項具有挑戰(zhàn)性的任務。設計者需要很好地掌握目標器件所能提供的時鐘資源及它們的限制,需要了解不同設計技術之間的權衡,并且需要很好地掌握一系列

2024-01-22 09:30:50 1413

1413

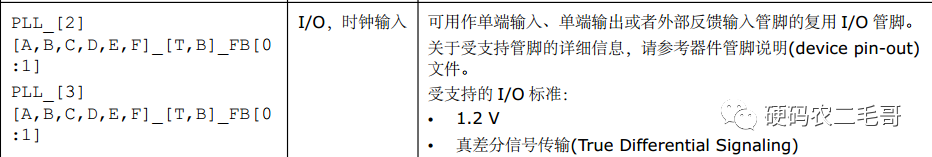

Ultrascale是賽靈思開發(fā)的支持包含步進功能的增強型FPGA架構,相比7系列的28nm工藝,Ultrascale采用20nm的工藝,主要有2個系列:Kintex和Virtex

2025-04-24 11:29:01 2264

2264

FPGA 時鐘分配網(wǎng)絡設計技術

2012-08-20 17:15:27

FPGA時鐘時序資料

2014-06-03 20:13:27

(08)FPGA時鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘概念5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2022-02-23 07:26:05

(12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:08:36

FPGA的DCM模塊,40MHz時鐘輸入,得到clkout1 40MHz,clkout2 60MHz,clkout1 120MHz。對40MHz時鐘添加了約束,系統(tǒng)不是會自動對三個輸出時鐘進行約束

2017-05-25 15:06:47

;count:=0;else count:=count+1;end if; end if;end process; --------------時鐘正常運行 以及時間的調(diào)整的控制開關

2012-06-01 22:02:40

想問下各位大佬,FPGA外部接上晶振后,到底是怎么生成時鐘的,又是怎么使用這個時鐘的?如果沒有外部晶振,內(nèi)部可以自發(fā)的產(chǎn)生時鐘嗎?

2019-03-27 11:45:32

FPGA時鐘和復位電路設計本文節(jié)選自特權同學的圖書《FPGA設計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt FPGA的時鐘輸入都有專用引腳

2015-04-24 08:17:00

你好我有一個關于時鐘斷言的問題基本上我的實驗是JESD204B測試(KC 705帶DAC37J82板)這是基本設置FPGA clk(IP內(nèi)核時鐘來自另一個DAC板通過FMC連接器)系統(tǒng)工作正常1.

2019-04-10 12:35:21

喜我對時鐘門控有一些疑問。從我所讀到/學到的東西 - 時鐘門控可用于低功率fpga設計(關閉時鐘以防止元件切換以節(jié)省功率)。但是,我還讀到時鐘門控很糟糕,因為它可能會引起系統(tǒng)故障。我想我已經(jīng)看到了

2019-02-21 10:21:41

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

一般我們用的FPGA的時鐘都是用晶振來提供的,我想請教一下大家,可以用鎖相環(huán)芯片AD9518(或者其它鎖相環(huán))來生成時鐘供給FPGA,作為FPGA的系統(tǒng)時鐘

2013-08-17 11:20:41

本人菜鳥,寫了一個fpga的時鐘,但是不知道為什么秒上從0變?yōu)? 又變?yōu)?.。。。分跟時就根本沒變化。。。不知道為什么啊。。。求指教//分頻子模塊module fenpin (clk,rst_n

2012-10-25 16:06:12

很大。 在設計PLD/FPGA時通常采用幾種時鐘類型。時鐘可分為如下四種類型:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。多時鐘系統(tǒng)能夠包括上述四種時鐘類型的任意組合。1.全局時鐘對于一個設計項目

2012-12-14 16:02:37

模塊,充分理順模塊間的相互關系對于FPGA設計來說非常重要。以鬧鐘設計為例,我們通過建立四個清晰直觀的模塊(數(shù)碼管顯示模塊,矩陣鍵盤掃描模塊,時鐘計數(shù)模塊,鬧鐘設定模塊),以及建立完善的信號列表和運用

2017-08-02 18:00:01

最近采用ADS58C48采集數(shù)據(jù),ADS58C48的時鐘由FPGA差分提供。上電后,FPGA首先給ADS58C48配置。ADS58C48輸出時鐘作為FPGA采集數(shù)據(jù)的時鐘。

現(xiàn)在由以下幾個問題

2024-12-20 06:32:12

要區(qū)分,MRCC SRSS,要知道Clock Regin的概念,MRCC 進來CLK,Regin里外皆可到,SRCC 進來CLK,只能在Regina里面

2019-05-22 07:24:24

200MHz、125MHz與之類似。我想問的是能不能有方法通過1個晶振給所有該頻率的FPGA管腳提供時鐘。第一次見發(fā)帖,求大神解答

2015-10-09 21:35:56

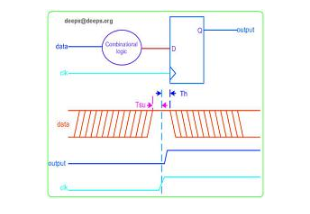

視頻信號(包括數(shù)據(jù)與時鐘,其中數(shù)據(jù)位寬16位,時鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時鐘相對于數(shù)據(jù)的延時,也就是信號的建立與保持時間在經(jīng)過FPGA后出現(xiàn)偏移。造成后端的DA不能正確的采集到數(shù)據(jù)。

2014-02-10 16:08:02

`帶你深入全面了解FPGA硬件資源PLL`

2021-03-30 14:43:12

我在我的同學面前炫耀FPGA是做高速處理的,可是,當人家問我,我的時鐘頻率能達到多少時,我說利用PLL能拉到200MHz,他說,這么低啊?我的手機頻率都是1.5G的呢。我無語。。。后來才了解到,他

2012-03-08 17:11:08

使用FPGA時鐘展頻技術搞定RE測試特權同學原創(chuàng),轉載請注明出處1 關于時鐘展頻應用展頻技術是通過對尖峰時鐘進行調(diào)制處理,使其從一個窄帶時鐘變成為一個具有邊帶諧波的頻譜,從而達到將尖峰能量分散到展頻

2016-10-11 17:32:44

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說

2020-04-25 07:00:00

嗨,我想知道Virtex-6 FPGA可以預期多少時鐘抖動。我已經(jīng)閱讀了有關Virtex-6 FPGA的所有文檔,但沒有找到數(shù)值。我發(fā)現(xiàn)的唯一的事情是它具有低抖動但不低或數(shù)值。

2020-06-12 14:56:20

//基本D觸發(fā)器moduleD_EF(Q,D,CLK)input D,CLK;output Q;regQ;//在always語句中被賦值的信號要聲明為reg類型 寄存器定義always @ (posedgeCLK) //上升沿,下降沿用negedge表示,^_^ 需要記憶begin Q

2016-01-22 14:09:25

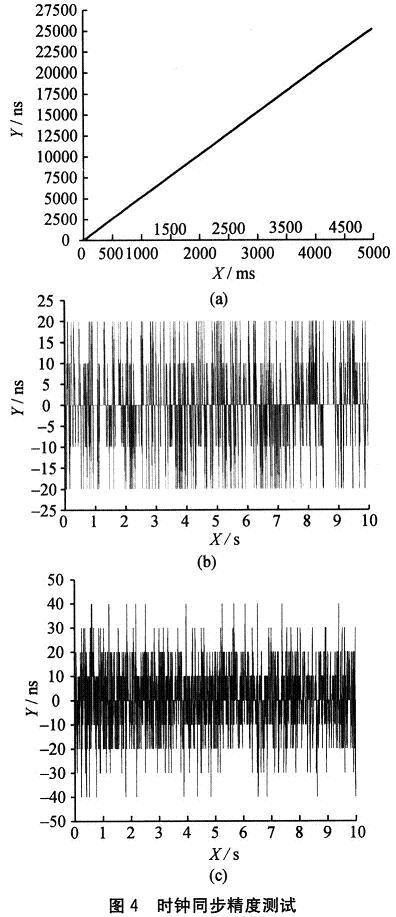

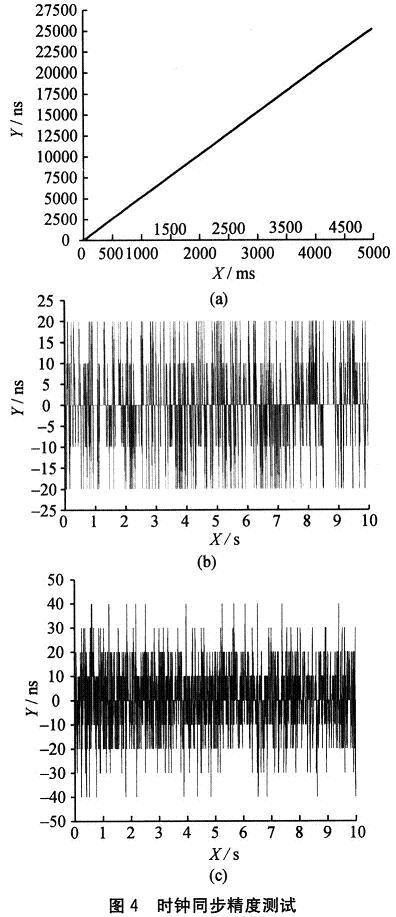

摘要:隨著石油勘探的發(fā)展,在地震勘探儀器中越來越需要高精度的同步技術來支持高效采集。基于這種目的,采用FPGA技術設計了一種時鐘恢復以及系統(tǒng)同步方案,并完成了系統(tǒng)的固件和嵌入式軟件設計。通過室內(nèi)測試

2019-06-18 08:15:35

基于FPGA的時鐘設計

2012-08-17 23:58:55

同步數(shù)字系統(tǒng)中的時鐘信號(如遠程通信中使用的)為系統(tǒng)中的數(shù)據(jù)傳送定義了時間基準。一個時鐘分配網(wǎng)絡由多個時鐘信號組成,由一個點將所有信號分配給需要時鐘信號的所有組件。因為時鐘信號執(zhí)行關鍵的系統(tǒng)功能,很顯然應給予更多的關注,不僅在時鐘的特性(即偏移和抖動)方面,還有那些組成時鐘分配網(wǎng)絡的組件。

2019-10-16 07:11:33

把握DCM、PLL、PMCD和MMCM知識是穩(wěn)健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數(shù)設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

第一次用這種AD芯片,買了個開發(fā)板,發(fā)現(xiàn),開發(fā)板母板上沒有晶振。請教幾個問題。

1。母板上用的時鐘是SCLK作為源時鐘嗎?

2、如果用FPGA采集AD1672,如何保障FPGA時鐘同1672時鐘

2024-12-24 06:17:07

怎樣將FPGA時鐘引腳作為普通輸入引腳設置,在軟件中怎樣設置?求解答{:2:}

2013-05-21 20:11:34

提高FPGA的時鐘精度的方案有哪些,哪位大神告訴一下

2015-10-13 08:22:31

有一篇文章說fpga的時鐘周期一般采用整偶數(shù),這個有什么...

2014-03-16 19:34:02

我做的一個基于DSP的系統(tǒng)中,DSP做主處理器,控制著整個系統(tǒng),包括信號處理,整體調(diào)度等;選擇了一塊Xilinx的FPGA做FIFO UART和系統(tǒng)的邏輯控制和譯碼。DSP的時鐘輸入為15MHz

2023-06-19 06:43:17

計算FPGA外部引腳的頻率。我需要將其與內(nèi)部FPGA時鐘同步嗎?內(nèi)部參考時鐘以60Mhz運行,外部頻率在10khz到15khz之間變化,不同步的外部頻率是否會導致錯誤或問題?以上來自于谷歌翻譯以下

2019-06-18 09:37:29

一種FPGA時鐘網(wǎng)絡中鎖相環(huán)的實現(xiàn)方案:摘 要:本文闡述了用于FPGA 的可優(yōu)化時鐘分配網(wǎng)絡功耗與面積的時鐘布線結構模型。并在時鐘分配網(wǎng)絡中引入數(shù)字延遲鎖相環(huán)減少時鐘偏差,探

2009-08-08 09:07:22 25

25 DLL在FPGA時鐘設計中的應用:在ISE集成開發(fā)環(huán)境中,用硬件描述語言對FPGA 的內(nèi)部資源DLL等直接例化,實現(xiàn)其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發(fā)板設計中的

2009-11-01 15:10:30 33

33 本文闡述了用于FPGA的可優(yōu)化時鐘分配網(wǎng)絡功耗與面積的時鐘布線結構模型。并在時鐘分配網(wǎng)絡中引入數(shù)字延遲鎖相環(huán)減少時鐘偏差,探討了FPGA時鐘網(wǎng)絡中鎖相環(huán)的實現(xiàn)方案。

2010-08-06 16:08:45 12

12 提出了一種基于FPGA的時鐘跟蹤環(huán)路的設計方案,該方案簡化了時鐘跟蹤環(huán)路的結構,降低了時鐘調(diào)整電路的復雜度。實際電路測試結果表明,該方案能夠使接收機時鐘快速準確地跟蹤發(fā)

2010-11-19 14:46:54 31

31 FPGA芯片在高速數(shù)據(jù)采集緩存系統(tǒng)中的應用

概 述在高速數(shù)據(jù)采集方面,FPGA有單片機和DSP無法比擬的優(yōu)勢。FPGA的時鐘頻率高,內(nèi)部時延小,全部控制邏輯都可由硬

2010-03-30 10:51:15 1179

1179

FPGA的時鐘頻率同步設計

網(wǎng)絡化運動控制是未來運動控制的發(fā)展趨勢,隨著高速加工技術的發(fā)展,對網(wǎng)絡節(jié)點間的時間同步精度提出了更高的要求。如造紙機械,運行速

2010-01-04 09:54:32 3161

3161

本文將探討FPGA時鐘分配控制方面的挑戰(zhàn),協(xié)助開發(fā)團隊改變他們的設計方法,并針對正在考慮如何通過縮小其時鐘分配網(wǎng)絡的規(guī)模來擁有更多的FPGA I/O,或提高時鐘網(wǎng)絡性能的設計者們

2011-03-30 17:16:32 1241

1241

DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現(xiàn)的。

2015-10-28 14:25:42 1

1 一種基于FPGA的時鐘相移時間數(shù)字轉換器_王巍

2017-01-07 22:23:13 3

3 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 當Xilinx 7Series FPGA中,存在3種主要的時鐘網(wǎng)絡:BUFG,BUFR,BUFIO以及他們所衍生出的各種變種。那么他們有什么主要特點和區(qū)別呢? BUFIO是IO時鐘網(wǎng)絡,顧名思義,它

2017-02-08 05:31:40 3409

3409

談到數(shù)字邏輯,談到FPGA設計,每位工程師都離不開時鐘。這里我們簡單介紹一下xilinx 7 系列中的時鐘資源。時鐘設計的好壞,直接影響到布局布線時間、timing的收斂情況,FPGA的時鐘

2017-02-08 05:33:31 1192

1192

時鐘設施提供了一系列的低電容、低抖動的互聯(lián)線,這些互聯(lián)線非常適合于傳輸高頻信號、最大量減小時鐘抖動。這些連線資源可以和DCM、PLL等實現(xiàn)連接。 每一種Spartan-6芯片提供16個高速、低抖動的全局時鐘資源用于優(yōu)化性能。

2018-07-14 07:07:00 10817

10817

提出了一種基于FPGA的時鐘跟蹤環(huán)路的設計方粢,該方粢簡化了時鐘跟蹤環(huán)路的結構,降低了時鐘調(diào)整電路的復雜度。實際電路測試結果表明,該方集能夠使接收機時鐘快速準確地跟蹤發(fā)射機時鐘的變化,且時鐘抖動小、穩(wěn)準度高、工作穩(wěn)定可靠。

2017-11-30 15:10:20 5

5 近期,一直在調(diào)試使用 Verilog 編寫的以太網(wǎng)發(fā)送攝像頭數(shù)據(jù)到電腦的工程(以下簡稱 以太網(wǎng)圖傳)。該工程基于今年設計的一款 FPGA 教學板 AC620。AC620 上有一個百兆以太網(wǎng) 接口和一

2018-02-06 14:39:47 9

9 如果輸入信號需要反相,則要盡可能的調(diào)用輸入帶反相功能的符號,而不是使用分離的反相器來進行反相

2018-12-22 15:05:16 2695

2695 本文檔的主要內(nèi)容詳細介紹的是spartan-6 FPGA的時鐘資源的用戶指南資料免費下載。

2019-02-15 16:39:07 28

28 狀態(tài)機可歸納為4個要素,即現(xiàn)態(tài)、條件、動作、次態(tài)。這樣的歸納,主要是出于對狀態(tài)機的內(nèi)在因果關系的考慮。“現(xiàn)態(tài)”和“條件”是因,“動作”和“次態(tài)”是果。

2019-12-04 07:06:00 2981

2981 狀態(tài)機由狀態(tài)寄存器和組合邏輯電路構成,能夠根據(jù)控制信號按照預先設定的狀態(tài)進行狀態(tài)轉移,是協(xié)調(diào)相關信號動作、完成特定操作的控制中心。

2019-12-04 07:03:00 3640

3640

。 不要隨意將內(nèi)部信號作為時鐘,如門控時鐘和分頻時鐘,而要使用CLKDLL或者DCM產(chǎn)生的時鐘,或者可以通過建立時鐘使能或者DCM產(chǎn)生不同的時鐘信號。 FPGA盡量采取同步設計,也就是所有時鐘都是同一個源頭,如果使用兩個沒有相位關系的異步時鐘,必須

2020-12-11 10:26:44 2426

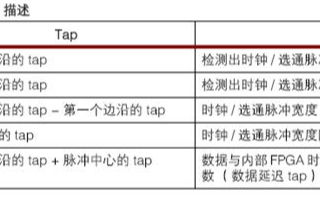

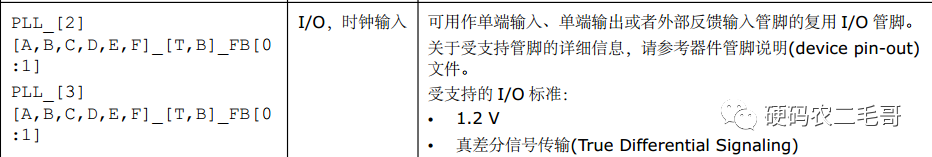

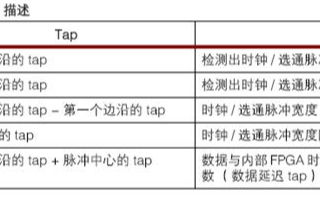

2426 ,并與內(nèi)部 FPGA 時鐘實現(xiàn)中心對齊。在這個方案中,內(nèi)部 FPGA時鐘采集傳出的數(shù)據(jù)。存儲器傳出的時鐘/ 選通脈沖用于決定與數(shù)據(jù)位相關的延遲值。因此,與選通脈沖相關的數(shù)據(jù)位的數(shù)量不受限制。由于無需將選通脈沖分配給相關數(shù)據(jù)位,所以不需要其他時鐘資源。

2020-11-26 10:01:31 1931

1931

區(qū)域(Region):每個FPGA器件被分為多個區(qū)域,不同的型號的器件區(qū)域數(shù)量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA中

2020-12-09 14:49:03 21

21 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 Xilinx7系列FPGA包括四個FPGA系列,它們都是為最低功耗而設計的,以使一個通用設計能夠跨系列擴展以獲得最佳的功率、性能和成本。斯巴達-7系列是7系列產(chǎn)品中密度最低、成本最低的入門級產(chǎn)品

2020-12-10 14:20:00 18

18 本文檔的主要內(nèi)容詳細介紹的是FPGA硬件基礎之理解FPGA時鐘資源的工程文件免費下載。

2020-12-10 14:20:11 6

6 本文檔的主要內(nèi)容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 16

16 全局時鐘資源是一種專用互連網(wǎng)絡,它可以降低時鐘歪斜、占空比失真和功耗,提高抖動容限。Xilinx的全局時鐘資源設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達CLB、IOB和BRAM的延時最小。

2020-12-29 16:59:35 8

8 引言:從本文開始,我們陸續(xù)介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 6070

6070 傳統(tǒng)的異步采集方法會影響采集到的功耗信息的信噪比,降低功耗分析的成功率。針對異步采集的問題提出一種新的時鐘同步功耗信息采集方法。該采集方法基于現(xiàn)場可編程門陣列(FPGA)的時鐘同步采集平臺,和用

2021-03-31 15:50:21 6

6 在設計FPGA項目的時候,對時鐘進行約束,但是因為算法或者硬件的原因,都使得時鐘約束出現(xiàn)超差現(xiàn)象,接下來主要就是解決時鐘超差問題,主要方法有以下幾點。 第一:換一個速度更快點的芯片,altera公司

2021-10-11 14:52:00 4267

4267

(08)FPGA時鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘概念5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 HROW:水平時鐘線,從水平方向貫穿每個時鐘區(qū)域的中心區(qū)域,將時鐘區(qū)域分成上下完全一致的兩部分。全局時鐘線進入每個時鐘區(qū)域的邏輯資源時,必須經(jīng)過水平時鐘線。

2022-06-13 10:07:26 2543

2543 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區(qū)別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 4699

4699 電子發(fā)燒友網(wǎng)站提供《Logos系列FPGA時鐘資源(Clock)用戶指南.pdf》資料免費下載

2022-09-26 10:15:21 11

11 ASIC 和FPGA芯片的內(nèi)核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 1249

1249

隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調(diào)試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼可能無法滿足時序要求。

2023-05-06 09:33:27 1544

1544

幾年前FPGA時鐘只需要連接一個單端輸入的晶振,非常容易。現(xiàn)在不同了,差分時鐘輸入,差分信號又分為LVDS和LVPECL,時鐘芯片輸出后還要經(jīng)過直流或交流耦合才能接入FPGA,有點暈了,今天仔細研究一下。

2023-08-21 11:28:44 14322

14322

2023-11-01 09:05:26 0

0 就是看看超差的那個線路,增加一些中間寄存器,或者使用流水線技術,就是將組合邏輯和時序邏輯分開,大的時序邏輯,盡量優(yōu)化成由很多小的時序邏輯組成一個大的時序邏輯。

2024-02-29 12:47:03 1535

1535

FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產(chǎn)生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

電子發(fā)燒友App

電子發(fā)燒友App

評論