本文將主要介紹Kinetis MCU混合信號(hào)的驗(yàn)證策略和挑戰(zhàn),其中包括混合信號(hào)建模、連接驗(yàn)證、混合信號(hào)VIP、混合信號(hào)功率驗(yàn)證和混合信號(hào)覆蓋范圍。##混合信號(hào)驗(yàn)證往往會(huì)發(fā)現(xiàn)三種類型的功能性錯(cuò)誤。##混合信號(hào)驗(yàn)證的另一大挑戰(zhàn)是功耗驗(yàn)證。Kinetis的功耗驗(yàn)證采用了CPF方法。

2014-07-09 10:14:08 4804

4804 什么是FPGA原型?? FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過將RTL移植到現(xiàn)場可編程門陣列(FPGA)來驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能

2022-07-19 16:27:29 2400

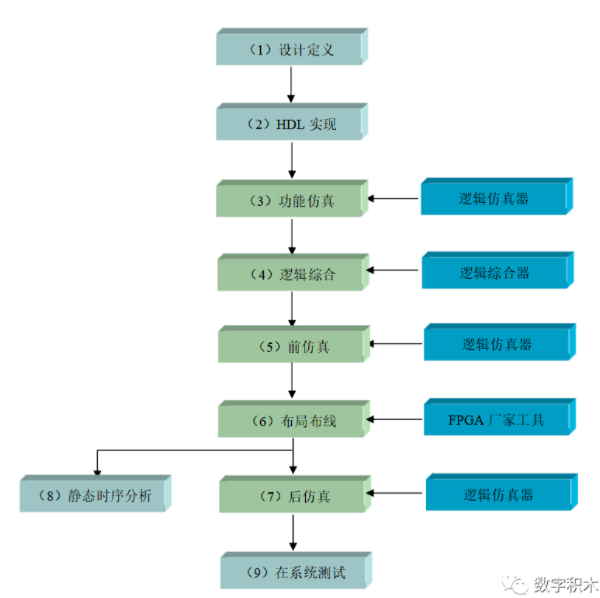

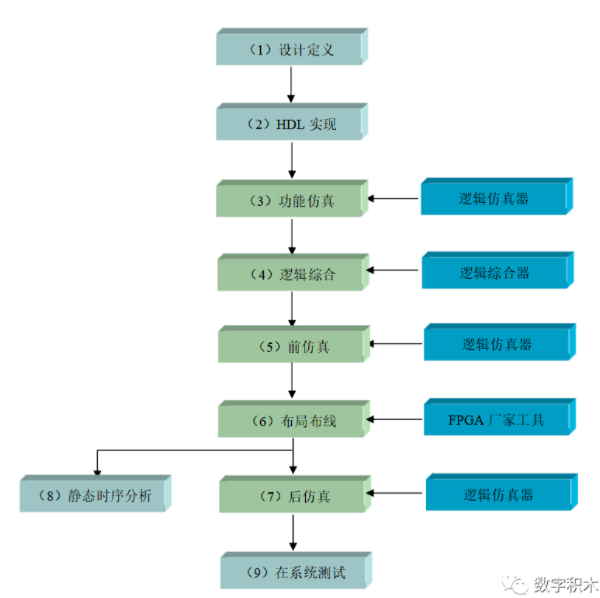

2400 在第一章中,已經(jīng)給出了FPGA/CPLD的基本開發(fā)流程圖。這里不妨回顧一下,如圖5.15所示。這個(gè)流程圖是一個(gè)相對比較高等級(jí)的FPGA/CPLD器件開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行

2015-03-03 14:31:44

調(diào)試驗(yàn)證。圖5.16 FPGA/CPLD設(shè)計(jì)簡易流程 本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA/CPLD邊練邊學(xué)——快速入門Verilog/VHDL》書中代碼請?jiān)L問網(wǎng)盤:http://pan.baidu.com/s/1bndF0bt

2015-02-09 20:14:21

驗(yàn)證無誤,則可以生產(chǎn)下載配置文件燒錄的實(shí)際器件中進(jìn)行板級(jí)的調(diào)試工作。圖5.15 FPGA/CPLD開發(fā)流程當(dāng)然了,對于沒有實(shí)際工程經(jīng)驗(yàn)的初學(xué)者而言,這個(gè)流程圖可能不是那么容易理解。不過沒有關(guān)系,我們會(huì)

2019-01-28 02:29:05

FPGA的設(shè)計(jì)流程就是利用EDA開發(fā)軟件和編程工具對FPGA芯片進(jìn)行開發(fā)的過程。FPGA的開發(fā)流程一般包括功能定義、設(shè)計(jì)輸入、功能仿真、綜合優(yōu)化、綜合后仿真、實(shí)現(xiàn)與布局布線、時(shí)序仿真與驗(yàn)證、板級(jí)仿真

2023-12-31 21:15:31

FPGA開發(fā)流程(特權(quán)同學(xué)版權(quán)所有)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》(特權(quán)同學(xué)版權(quán)所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-31 09:27:38

如圖1.6所示。這個(gè)流程圖是一個(gè)相對比較高等級(jí)的FPGA開發(fā)流程,從項(xiàng)目的提上議程開始,設(shè)計(jì)者需要進(jìn)行FPGA功能的需求分析,然后進(jìn)行模塊的劃分,比較復(fù)雜和龐大的設(shè)計(jì),則會(huì)通過模塊劃分把工作交給一個(gè)

2019-01-28 04:24:37

與通常的單片機(jī)應(yīng)用開發(fā)不同,FPGA有自己的開發(fā)流程。但具體上怎樣操作,作為初學(xué)者,沒有一點(diǎn)經(jīng)驗(yàn)。網(wǎng)站獎(jiǎng)勵(lì)的清華FPGA需要的開發(fā)軟件,到目前還沒有安裝成功。暫且先看看相關(guān)學(xué)習(xí),慢慢積累這方面的知識(shí)

2024-06-23 14:47:24

層次模塊的源代碼以修改錯(cuò)誤。 圖1 自頂向下的FPGA設(shè)計(jì)開發(fā)流程在工程實(shí)踐中,還存在軟件編譯時(shí)長的問題。由于大型設(shè)計(jì)包含多個(gè)復(fù)雜的功能模塊,其時(shí)序收斂與仿真驗(yàn)證復(fù)雜度很高,為了滿足時(shí)序指標(biāo)的要求,往往需要

2017-01-10 15:50:15

仿真驗(yàn)證概述本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 仿真測試是FPGA設(shè)計(jì)流程中必不可少的步驟

2019-04-10 06:35:34

混合信號(hào)FPGA的智能型驗(yàn)證流程是怎樣的?

2021-04-30 06:26:35

1ASIC 驗(yàn)證技術(shù).................................................11.1 ASIC 設(shè)計(jì)流程

2015-09-18 15:26:25

輸入、功能仿真、邏輯綜合、形式驗(yàn)證、時(shí)序/功耗/噪聲分析,布局布線(物理綜合)、版圖驗(yàn)證。 至于FPGA設(shè)計(jì),開發(fā)起來更加簡單,結(jié)合第三方軟件(像Modelsim和Synplify Pro),兩大

2018-08-16 09:14:32

Keysight 8000系列矢量,混合信號(hào),FPGA分析儀

2019-10-12 14:56:19

為什么verilog可以描述硬件?在SOC設(shè)計(jì)中使用verilog,和FPGA為對象使用verilog,有什么區(qū)別?SOC流程和FPGA流程的不同之處在哪里?

2021-06-21 07:02:59

學(xué)習(xí)方法和思想傳遞給大家。 如果大家所認(rèn)為的FPGA開發(fā)流程就是編碼、下載、調(diào)試,那么你就該好好的看下這個(gè)視頻教程了,因?yàn)槲乙舱潜贿@種錯(cuò)誤的學(xué)習(xí)方式耽誤了好久好久,直到參加了培訓(xùn)學(xué)習(xí)才知道,仿真驗(yàn)證

2015-09-19 16:23:18

慮寄生的話是沒有電感的,不能起到濾波作用,因此不能和電感互換。 9、我想知道業(yè)界在模數(shù)混合信號(hào)的設(shè)計(jì)驗(yàn)證方面流程。據(jù)我理解,設(shè)計(jì)驗(yàn)證在設(shè)計(jì)流程中具有舉足輕重的作用,直接會(huì)影響到芯片最終的成敗。設(shè)計(jì)驗(yàn)證

2018-09-21 16:46:09

,其實(shí)這個(gè)階段也應(yīng)該包括第二個(gè)階段的布局布線和時(shí)序驗(yàn)證,因?yàn)檫@兩個(gè)步驟都是和FPGA器件緊密相關(guān)的。我們這么粗略的三個(gè)階段劃分并沒有把FPGA整個(gè)設(shè)計(jì)流程完全的孤立開來,恰恰相反,從我們的階段劃分中,我們也看到FPGA設(shè)計(jì)的各個(gè)環(huán)節(jié)是緊密銜接、相互影響的。 圖1.10 簡化的FPGA開發(fā)流程

2016-07-13 17:25:34

器件燒錄和板級(jí)調(diào)試外,其實(shí)這個(gè)階段也應(yīng)該包括第二個(gè)階段的布局布線和時(shí)序驗(yàn)證,因?yàn)檫@兩個(gè)步驟都是和FPGA器件緊密相關(guān)的。我們這么粗略的三個(gè)階段劃分并沒有把FPGA整個(gè)設(shè)計(jì)流程完全的孤立開來,恰恰相反

2017-10-12 21:02:44

前言 本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成風(fēng)格良好和完整的文檔

2017-12-08 14:47:15

華為FPGA設(shè)計(jì)流程指南本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:l在于規(guī)范整個(gè)設(shè)計(jì)流程,實(shí)現(xiàn)開發(fā)的合理性、一致性、高效性。l形成

2017-12-18 10:45:03

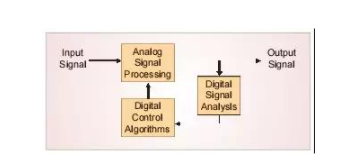

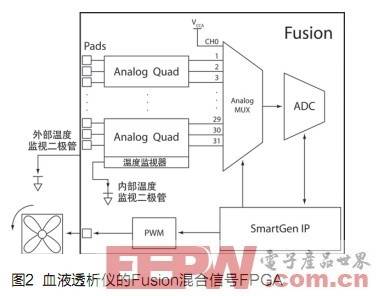

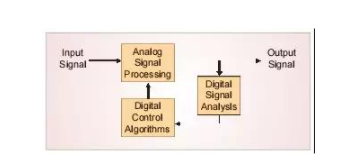

隨著SoC設(shè)計(jì)上的混合信號(hào)組件數(shù)量增加了,基本的功能驗(yàn)證對于硅初期能否成功也愈來愈重要。FPGA在系統(tǒng)整合難題上加入了一個(gè)新特點(diǎn)。在核心上,此新范例-可編程系統(tǒng)單芯片(programmable

2011-10-16 22:55:10

如何利用混合信號(hào)FPGA去實(shí)現(xiàn)智能化熱管理?

2021-04-29 07:06:50

請教一下各位,如何用混合信號(hào)FPGA去控制電壓攀升率?

2021-04-30 06:19:05

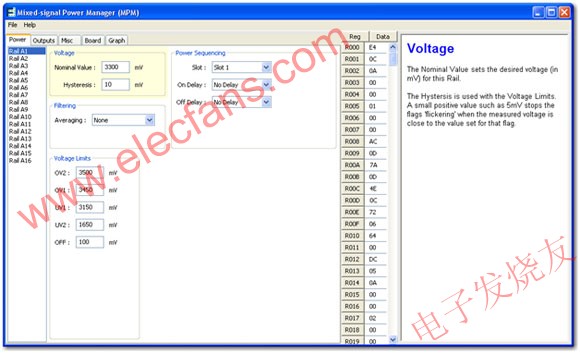

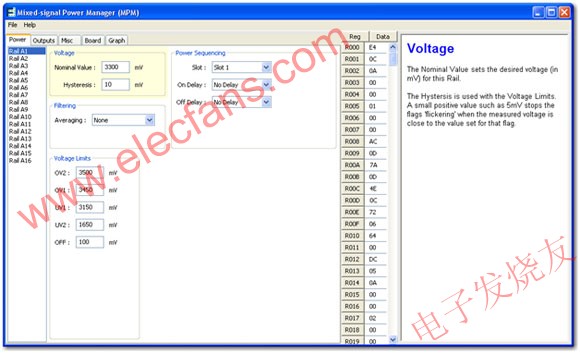

Actel Fusion 混合信號(hào)FPGA能夠?qū)崿F(xiàn)功率管理,包括上電順序、運(yùn)行時(shí)間功率監(jiān)控,以及關(guān)機(jī)控制。此外,愛特公司提供的混合信號(hào)功率管理工具(Mixed-Signal POWER

2019-10-21 07:23:50

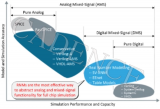

隨著芯片幾何尺寸的進(jìn)一步縮小,不僅芯片上的晶體管數(shù)量在增加,芯片上集成的各種功能數(shù)量也在迅速增加。對模擬到數(shù)字(A/D)混合信號(hào)芯片而言,也即意味著芯片的模擬和數(shù)字部分之間的交互影響也在不斷增加。

2019-06-26 06:29:19

智能型混合信號(hào)FPGA現(xiàn)投入生產(chǎn)愛特公司(Actel Corporation)宣布推出世界首個(gè)智能型混合信號(hào)FPGA器件SmartFusion?,該產(chǎn)品現(xiàn)正投入批量生產(chǎn)。SmartFusion器件

2019-07-15 08:00:42

請問一下,如何利用AMSVF來進(jìn)行混合信號(hào)SoC的全芯片驗(yàn)證?

2021-05-06 07:56:08

本帖最后由 gk320830 于 2015-3-9 19:19 編輯

大家好,我和我的中國同事目前在澳大利亞工作。我們的主要工作范圍是芯片級(jí)模擬數(shù)字混合電路驗(yàn)證(CHIP LEVEL

2011-03-23 19:36:31

請問如何以智能型混合信號(hào)FPGA開發(fā)出真正符合需求的系統(tǒng)?

2021-04-08 06:24:50

運(yùn)動(dòng)控制和混合信號(hào)FPGA的知識(shí)點(diǎn),總結(jié)的太棒了

2021-05-10 06:07:23

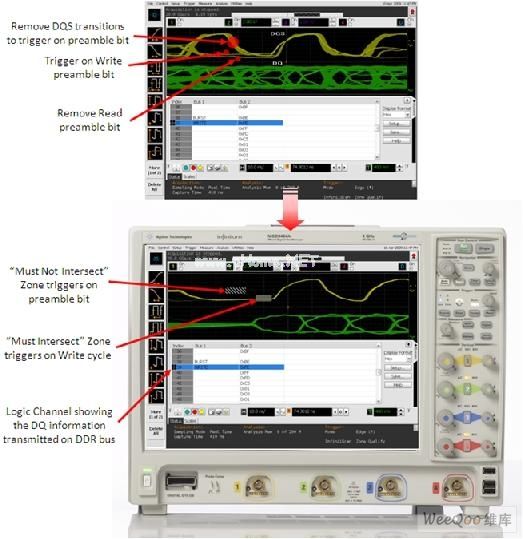

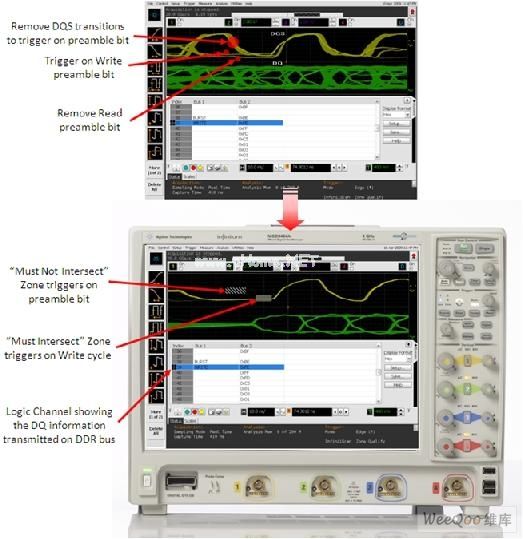

本文詳細(xì)介紹了如何利用安捷倫的混合信號(hào)示波器來完成設(shè)計(jì)調(diào)試和測試。

2009-11-21 15:30:24 10

10 本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:

2010-11-01 17:30:26 182

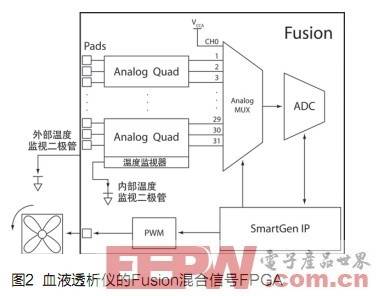

182 ????Actel公司日前宣布推出首款混合信號(hào)(mixed-signal)FPGA產(chǎn)品系列——Actel Fusion融合可編程系統(tǒng)芯片(PSC),且可立即供貨。Actel Fusion器件在單片可編程系統(tǒng)芯片

2006-03-13 13:02:18 1398

1398 MSO6052A安捷倫混合信號(hào)示波器500 MHz安捷倫MSO6052A混合信號(hào)示波器(MSO)模型和傳統(tǒng)的2通道和4通道,DSO系列數(shù)字存儲(chǔ)示波器模型進(jìn)行了優(yōu)化,具有驗(yàn)證和調(diào)試設(shè)計(jì)的能力,包括

2025-08-12 16:00:40

利用混合信號(hào)FPGA推動(dòng)臨床醫(yī)療應(yīng)用設(shè)備的發(fā)展

當(dāng)前,由于醫(yī)療服務(wù)成本的不斷攀高、慢性病的流行、人口的老化,以及中國、印度和巴西等大規(guī)模

2009-11-05 16:51:09 699

699

愛特混合信號(hào)功率管理工具為FUSION混合信號(hào)FPGA提供完整的圖形設(shè)計(jì)方案

設(shè)計(jì)人員可以更簡單方法實(shí)現(xiàn)控制并降低系統(tǒng)級(jí)功率

愛特公司 (Actel Corporation)宣布,

2009-11-11 16:45:13 710

710 Actel增強(qiáng)Fusion混合信號(hào)FPGA IP產(chǎn)品系列

?愛特公司(Actel Corporation)宣布推出與其子公司Pigeon Point Systems攜手開發(fā)的硬件平臺(tái)管理應(yīng)用的IP內(nèi)核增強(qiáng)組件。全新的增強(qiáng)內(nèi)核

2009-11-25 09:41:01 1132

1132 運(yùn)動(dòng)控制和混合信號(hào)FPGA

隨著電子元件的性能和集成度不斷提高而價(jià)格卻不斷降低,電子控制單元的發(fā)展正一日千里。隨著各種技術(shù)和應(yīng)用大量涌現(xiàn),從家電領(lǐng)域到工

2009-12-23 11:19:55 823

823 用高帶寬混合信號(hào)示波器進(jìn)行DDR驗(yàn)證和調(diào)試的技巧

?? DDR存儲(chǔ)器,也稱雙倍數(shù)據(jù)率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,常用于高級(jí)嵌入式電路系統(tǒng)的設(shè)計(jì),包括計(jì)算機(jī)、交通運(yùn)

2010-03-02 11:08:48 929

929

Actel發(fā)布首個(gè)智能型混合信號(hào)FPGA器件SmartFusion

愛特公司(Actel Corporation)宣布推出世界首個(gè)智能型混合信號(hào)FPGA器件SmartFusion™,該產(chǎn)品現(xiàn)正投入批量生產(chǎn)。SmartFusion器

2010-03-04 11:16:05 1188

1188 Actel推出智能型混合信號(hào)FPGA器件SmartFusion

愛特公司(Actel Corporation)宣布推出世界首個(gè)智能型混合信號(hào)FPGA器件SmartFusion,該產(chǎn)品現(xiàn)正投入批量生產(chǎn)。SmartFusion器件帶有Actel經(jīng)

2010-03-09 10:25:55 930

930 模擬與數(shù)字電路使用混合信號(hào)的驗(yàn)證和測量方法

無論是在計(jì)算機(jī)領(lǐng)域,通信領(lǐng)域還是消費(fèi)電子領(lǐng)域,當(dāng)我們隨手拿來一塊電路板時(shí),

2010-03-10 15:25:15 1085

1085 Actel的SmartFusion混合信號(hào)FPGA開發(fā)評(píng)估方案

Actel公司的SmartFusion是集成了FPGA, ARM Cortex-M3和可編程模擬的智能混合信號(hào)FPGA,非常適合硬件和嵌入系統(tǒng)設(shè)計(jì).

2010-03-31 08:46:22 3176

3176

概述

Actel Fusion® 混合信號(hào)FPGA能夠?qū)崿F(xiàn)功率管理,包括上電順序、運(yùn)行時(shí)間功率監(jiān)控,以及關(guān)機(jī)控制。此外,愛特公司提供的混合信號(hào)功

2010-08-26 10:34:28 1433

1433

美高森美公司(Microsemi Corporation)宣布提供100% 通過 -55°C至 +100°C溫度范圍測試的Fusion混合信號(hào)FPGA器件。這一項(xiàng)性能提升使美高森美能夠

2010-11-26 08:49:09 1197

1197 Mentor Graphics的FPGA Advantage是享譽(yù)業(yè)界,具有FPGA設(shè)計(jì)黃金組合的全流程設(shè)計(jì)工具。本次課程將使用戶體驗(yàn)FPGA Advantage如何最大化地加速設(shè)計(jì)的實(shí)現(xiàn)以及復(fù)用。同時(shí)掌握如何利用FPGA Advantage快速實(shí)現(xiàn)設(shè)計(jì)從創(chuàng)建、理解、仿真驗(yàn)證、綜合以及布局布線的全過

2011-03-15 13:39:56 98

98 Harris公司的工程師們經(jīng)常在緊迫的時(shí)限內(nèi)交付基于FPGA的復(fù)雜信號(hào)處理系統(tǒng)。為了滿足客戶時(shí)常十分嚴(yán)格的要求以及自身的質(zhì)量標(biāo)準(zhǔn),工程師們會(huì)在綜合各個(gè)系統(tǒng)前徹底驗(yàn)證HDL設(shè)計(jì)。 在過去,HDL驗(yàn)證需要多步手工操作現(xiàn)在,Harris工程師們使用EDASimulatoLink實(shí)現(xiàn)

2011-03-15 15:36:21 13

13 Actel Fusion 混合信號(hào)FPGA能夠?qū)崿F(xiàn)功率管理,包括上電順序、運(yùn)行時(shí)間功率監(jiān)控,以及關(guān)機(jī)控制。此外,愛特公司提供的混合信號(hào)功率管理工具(Mixed-Signal POWER Manager, MPM)參考設(shè)計(jì),更可在

2011-03-25 15:59:03 107

107 隨著 FPGA 的設(shè)計(jì)速度、尺寸和復(fù)雜度明顯增長,使得整個(gè)設(shè)計(jì)流程中的實(shí)時(shí)驗(yàn)證和調(diào)試成為當(dāng)前FPGA 系統(tǒng)的關(guān)鍵部分。獲得FPGA 內(nèi)部信號(hào)有限、FPGA 封裝和印刷電路板(PCB)電氣噪聲,這一

2011-06-10 15:42:28 28

28 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS),宣布Giantec Semiconductor Corp.已采用Cadence? Virtuoso?統(tǒng)一定制/模擬(IC6.1)以及Encounter?統(tǒng)一數(shù)字流程生產(chǎn)其混合信號(hào)芯片。

2011-09-27 11:06:26 1765

1765 第一編 驗(yàn)證的重要性 驗(yàn)證,顧名思義就是通過仿真、時(shí)序分析、上板調(diào)試等手段檢驗(yàn)設(shè)計(jì)正確性的過程,在 FPGA / IC 開發(fā)流程中,驗(yàn)證主要包括功能驗(yàn)證和時(shí)序驗(yàn)證兩個(gè)部分。為了了解

2012-05-18 11:50:21 8827

8827 新思科技公司日前宣布了一種集成化混合原型驗(yàn)證解決方案,它將Synopsys的Virtualizer虛擬原型驗(yàn)證和Synopsys基于FPGA的HAPS原型驗(yàn)證結(jié)合在一起

2012-06-07 11:26:30 1373

1373 FPGA設(shè)計(jì)的流程,步驟,選型,仿真,軟硬件設(shè)計(jì),調(diào)試流程。

2016-05-11 14:33:02 29

29 一種基于UVM的混合信號(hào)驗(yàn)證環(huán)境_耿睿

2017-01-07 21:39:44 2

2 是德科技使用混合信號(hào)示波器調(diào)試嵌入式混合信號(hào)設(shè)計(jì)

2017-10-24 09:43:37 12

12 設(shè)計(jì)了一種基于FPGA的驗(yàn)證平臺(tái)及有效的SoC驗(yàn)證方法,介紹了此FPGA驗(yàn)證軟硬件平臺(tái)及軟硬件協(xié)同驗(yàn)證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗(yàn)證

2017-11-17 03:06:01 21449

21449

隨著集成電路設(shè)計(jì)技術(shù)的發(fā)展和芯片集成度的提高,驗(yàn)證已經(jīng)成為芯片設(shè)計(jì)流程中的主要瓶頸。本文設(shè)計(jì)了一個(gè)基于FPGA的智能卡驗(yàn)證平臺(tái),并對驗(yàn)證方法做了詳細(xì)闡述。本文對于雙界面智能卡芯片驗(yàn)證的成功實(shí)踐

2017-11-17 16:25:01 1455

1455 1. FPGA 開發(fā)流程: 電路設(shè)計(jì)與設(shè)計(jì)輸入 ;仿真驗(yàn)證:利用Xilinx集成的仿真工具足矣 ;邏輯綜合:利用XST(Xilinx Synthesis Tool)工具 ;布局布線:利用Xilinx

2018-01-12 03:59:48 10715

10715 Mentor Graphics的Tanner EDA是針對全定制lC、模擬/混合信號(hào)(AMS)和MEMS設(shè)計(jì)的一套產(chǎn)品。對物聯(lián)網(wǎng)(IoT)需求的突然上升使全流程混合信號(hào)設(shè)計(jì)環(huán)境面臨獨(dú)特的要求:經(jīng)濟(jì)

2018-03-05 10:43:07 0

0 由于無線技術(shù)的普及,高集成度成為必然趨勢,集成電路越來越多地加入了模擬/混合信號(hào)(AMS)元素。對物聯(lián)網(wǎng)(IoT)器件需求的突然上升使全流程AMS設(shè)計(jì)環(huán)境面臨獨(dú)特的要求:經(jīng)濟(jì)實(shí)惠、易于使用,且足夠

2018-03-06 14:58:22 1

1 本視頻教程主要主要介紹Xilinx公司開發(fā)設(shè)計(jì)流程中的各個(gè)功能模塊,包括ISE中的設(shè)計(jì)輸入,綜合,設(shè)計(jì)實(shí)現(xiàn)及驗(yàn)證等內(nèi)容,此專題將為廣大FPGA工程師深入理解EDA工具實(shí)現(xiàn)原理與FPGA開發(fā)完整流程提供幫助,從而為未來更復(fù)雜的設(shè)計(jì)打下基礎(chǔ)。

2018-06-06 13:46:00 4820

4820 本視頻教程主要主要介紹Xilinx公司開發(fā)設(shè)計(jì)流程中的各個(gè)功能模塊,包括ISE中的設(shè)計(jì)輸入,綜合,設(shè)計(jì)實(shí)現(xiàn)及驗(yàn)證等內(nèi)容,此專題將為廣大FPGA工程師深入理解EDA工具實(shí)現(xiàn)原理與FPGA開發(fā)完整流程提供幫助,從而為未來更復(fù)雜的設(shè)計(jì)打下基礎(chǔ)。

2018-06-08 02:35:00 5829

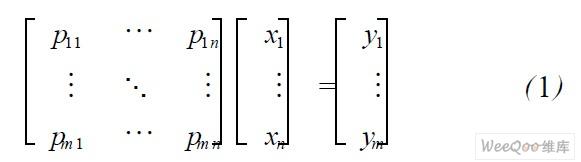

5829 本文提出一種基于FPGA ( Field ProgrammableGate Array)的音頻交換混合矩陣的設(shè)計(jì)方案。該方案以交換技術(shù)原理為基礎(chǔ),采用數(shù)字音頻信號(hào)采樣及處理技術(shù),構(gòu)建交換混合矩陣

2018-12-30 09:27:00 4860

4860

來自中國北京的電子設(shè)計(jì)自動(dòng)化(EDA)解決方案供應(yīng)商華大九天日前宣布,其模擬/混合信號(hào)全流程IC設(shè)計(jì)解決方案已正式進(jìn)入TowerJazz公司參考流程,并已通過工藝設(shè)計(jì)工具包(iPDK)的質(zhì)量驗(yàn)證。

2018-08-30 17:12:31 2417

2417 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的設(shè)計(jì)流程是怎么樣的?FPGA設(shè)計(jì)流程指南詳細(xì)資料免費(fèi)下載內(nèi)容包括了:1.基于HDL 的FPGA 設(shè)計(jì)流程概述2.Verilog HDL 設(shè)計(jì)3. 邏輯仿真4. 邏輯綜合

2018-10-17 17:50:41 32

32 本部門所承擔(dān)的 FPGA 設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和 ASIC 的原型驗(yàn)證。編寫本流程的目的是:

2020-04-28 08:00:00 3

3 開發(fā)的驗(yàn)證仿真云系統(tǒng),支持業(yè)界最大容量的 FPGA 元件 Xilinx Virtex? UltraScale? VU440 和 Intel? Stratix? 10 GX 10M, 可因需求擴(kuò)充搭載的容量, 不受時(shí)間、地點(diǎn)的限制, 大幅縮短復(fù)雜 SoC的設(shè)計(jì)驗(yàn)證流程。

2020-07-13 09:18:38 1030

1030 01 FPGA的設(shè)計(jì)流程 FPGA是可編程芯片,因此FPGA的設(shè)計(jì)內(nèi)容包括硬件設(shè)計(jì)和軟件設(shè)計(jì)兩部分。硬件包括FPGA芯片電路、 存儲(chǔ)器、輸入輸出接口電路以及其他設(shè)備,軟件即是相應(yīng)的HDL程序以及

2020-11-12 18:22:28 7389

7389 介紹了一種雙接口NFC芯片的架構(gòu)和功能,提岀并實(shí)現(xiàn)了用于該雙接口NFC芯片的FPGA驗(yàn)證系統(tǒng)及其驗(yàn)證流程。該FPGA驗(yàn)證系統(tǒng)包括FPGA、PIC單片機(jī)以及帶NFC功能的手機(jī),可有效縮短芯片設(shè)計(jì)周期

2021-05-26 14:03:26 17

17 FPGA設(shè)計(jì)流程指南

2021-11-02 16:29:21 12

12 本部門所承擔(dān)的FPGA設(shè)計(jì)任務(wù)主要是兩方面的作用:系統(tǒng)的原型實(shí)現(xiàn)和ASIC的原型驗(yàn)證。編寫本流程的目的是:

2022-03-15 11:19:26 4832

4832

其次,部分FPGA開發(fā)板也被用在IP和小型芯片設(shè)計(jì)的開發(fā)驗(yàn)證場景。這部分開發(fā)板配備大容量的FPGA芯片,甚至是單板配備多片FPGA芯片來適應(yīng)開發(fā)驗(yàn)證場景,一般由用戶自己負(fù)責(zé)手工實(shí)現(xiàn)從設(shè)計(jì)到FPGA功能原型的流程。

2022-04-28 09:38:33 3563

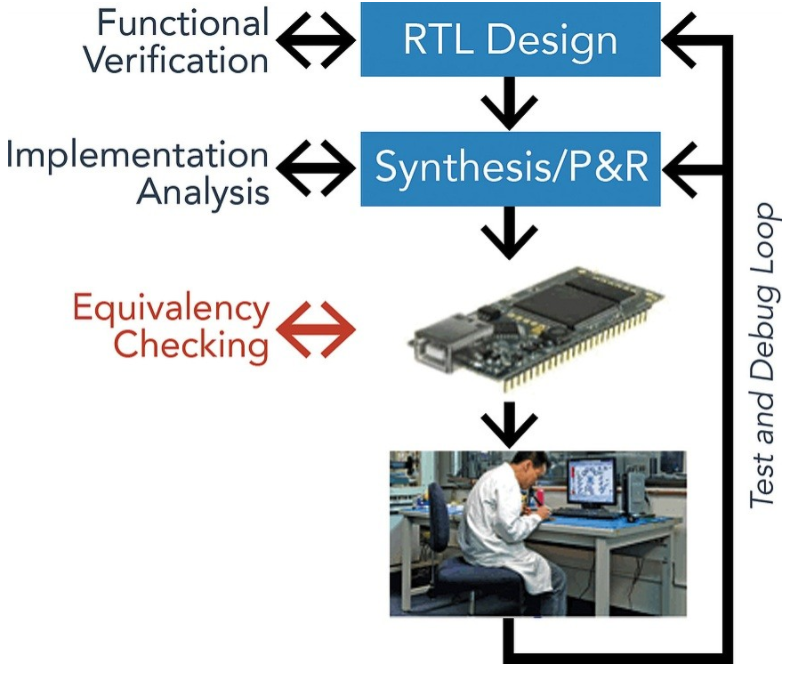

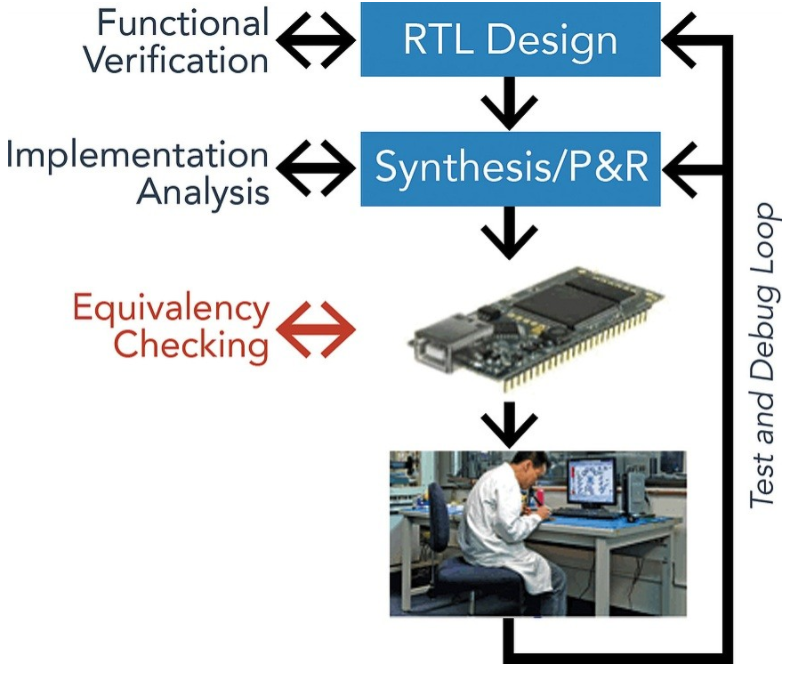

3563 隨著 FPGA 變得越來越大和越來越復(fù)雜,它們的設(shè)計(jì)和功能驗(yàn)證趨向于 ASIC。在現(xiàn)代 FPGA 設(shè)計(jì)流程的先進(jìn)性的推動(dòng)下,這種趨勢現(xiàn)在正在擴(kuò)展到實(shí)現(xiàn)驗(yàn)證領(lǐng)域。EC 現(xiàn)在是該流程的必要組成部分,保留了 FPGA 生產(chǎn)過程中的固有效率。

2022-06-14 09:21:55 2067

2067

芯片驗(yàn)證就是采用相應(yīng)的驗(yàn)證語言,驗(yàn)證工具,驗(yàn)證方法,在芯片生產(chǎn)之前驗(yàn)證芯片設(shè)計(jì)是否符合芯片定義的需求規(guī)格,是否已經(jīng)完全釋放了風(fēng)險(xiǎn),發(fā)現(xiàn)并更正了所有的缺陷,站在全流程的角度,它是一種防范于未然的措施。

2022-07-25 11:48:49 7711

7711 隨著 FPGA 數(shù)字信號(hào)處理系統(tǒng)復(fù)雜度不斷提高,FPGA 信號(hào)處理系統(tǒng)的功能驗(yàn)證已經(jīng)成為影響產(chǎn)品上市時(shí)間和成本的關(guān)鍵[1]。盡管在驗(yàn)證領(lǐng)域已經(jīng)發(fā)展出多種自動(dòng)測試方法,但是針對信號(hào)處理算法進(jìn)行驗(yàn)證

2022-11-04 16:24:47 3692

3692 混合信號(hào)還可以用于檢測和診斷信號(hào),以確定信號(hào)的質(zhì)量。混合信號(hào)測試可以幫助確定信號(hào)的質(zhì)量,以便更好地傳輸和處理信號(hào)。

2023-02-19 14:56:37 2325

2325

在現(xiàn)代SoC芯片驗(yàn)證過程中,不可避免的都會(huì)使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場景了。

2023-03-28 09:33:16 2001

2001 驗(yàn)證其實(shí)是一個(gè)“證偽”的過程,從流程到工具,驗(yàn)證工程師的終極目的都只有一個(gè)。

2023-05-31 10:34:49 2781

2781 FPGA的設(shè)計(jì)流程主要包括HDL代碼編寫、RTL綜合、布局布線、靜態(tài)時(shí)序分析、生成下載文件。下面將逐一介紹各部分。下面是FPGA設(shè)計(jì)的流程圖。

2023-07-04 12:06:08 2138

2138

??FPGA 的詳細(xì)開發(fā)流程就是利用 EDA 開發(fā)工具對 FPGA 芯片進(jìn)行開發(fā)的過程,所以 FPGA 芯片開發(fā)流程講的并不是芯片的制造流程,區(qū)分于 IC 設(shè)計(jì)制造流程喲(芯片制造流程多麻煩,要好

2023-07-04 14:37:17 6719

6719

今天基于微控制器(MCU)、現(xiàn)場可編程邏輯門陣列(FPGA)和數(shù)字信號(hào)處理器(DSP)的嵌入式設(shè)計(jì)一般都會(huì)同時(shí)包含模擬信號(hào)和數(shù)字信號(hào)成分。設(shè)計(jì)工程師以往使用示波器和邏輯分析儀來測試和調(diào)試這些混合信號(hào)

2023-07-23 17:32:18 2007

2007 隨著這些SoC設(shè)計(jì)上的混合信號(hào)組件數(shù)量增加了,基本的功能驗(yàn)證對于硅初期能否成功也愈來愈重要。FPGA在系統(tǒng)整合難題上加入了一個(gè)新特點(diǎn),改善了系統(tǒng)整合面,如整體的系統(tǒng)成本、可靠性、可組態(tài)性、上市時(shí)間等。

2023-10-27 17:02:02 813

813 隨著電子產(chǎn)品的不斷發(fā)展,混合信號(hào)示波器作為一種重要的測試儀器,被廣泛應(yīng)用于電子設(shè)備的開發(fā)和維修過程中。在使用混合信號(hào)示波器進(jìn)行電源測試時(shí),我們需要遵循一定的基本流程,以確保測試的準(zhǔn)確性和可靠性。本文將從以下幾個(gè)方面詳細(xì)介紹混合信號(hào)示波器電源測試的基本流程。

2023-09-22 14:54:44 1550

1550

FPGA驗(yàn)證和UVM驗(yàn)證在芯片設(shè)計(jì)和驗(yàn)證過程中都扮演著重要的角色,但它們之間存在明顯的區(qū)別。

2024-03-15 15:00:41 3024

3024 FPGA原型驗(yàn)證流程是確保FPGA(現(xiàn)場可編程門陣列)設(shè)計(jì)正確性和功能性的關(guān)鍵步驟。它涵蓋了從設(shè)計(jì)實(shí)現(xiàn)到功能驗(yàn)證的整個(gè)過程,是FPGA開發(fā)流程中不可或缺的一環(huán)。

2024-03-15 15:05:33 3058

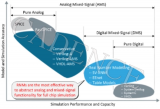

3058 混合信號(hào)設(shè)計(jì)在半導(dǎo)體設(shè)計(jì)飛速發(fā)展的過程中發(fā)揮著關(guān)鍵作用。混合信號(hào)設(shè)計(jì)將模擬與數(shù)字電路無縫集成至一個(gè) SoC 上,為用戶提供了顯著的性能、尺寸和能效優(yōu)勢。

2024-11-21 15:48:12 1356

1356

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論