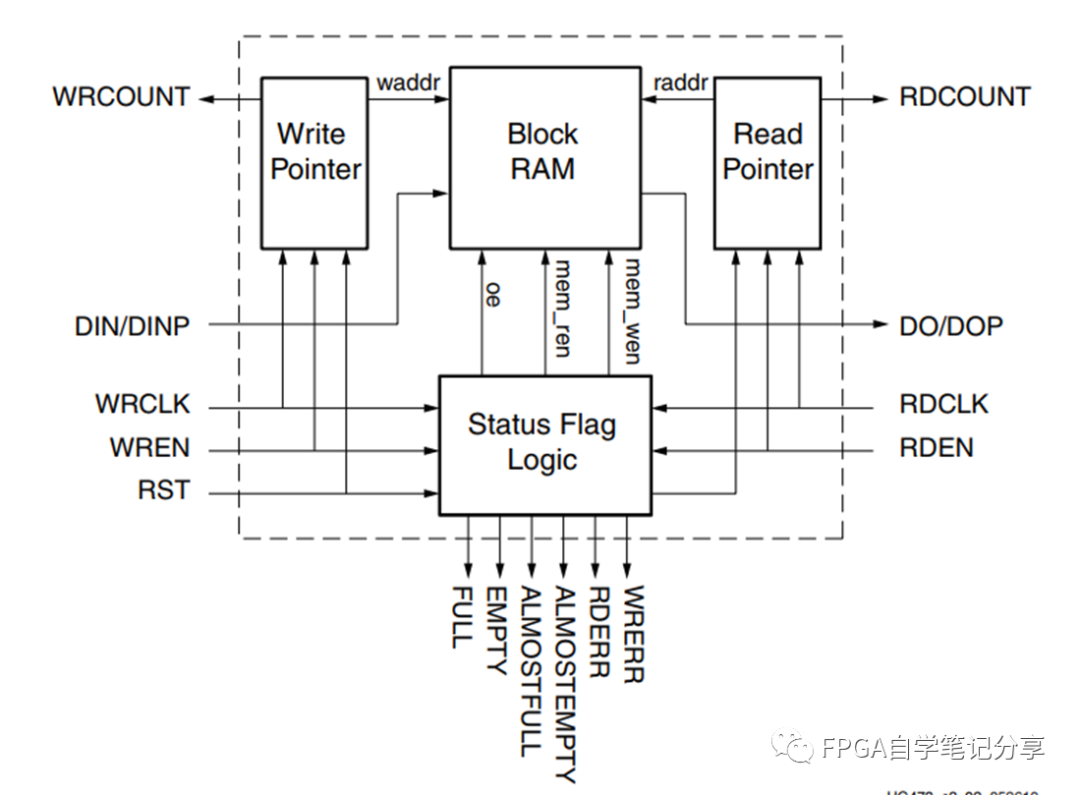

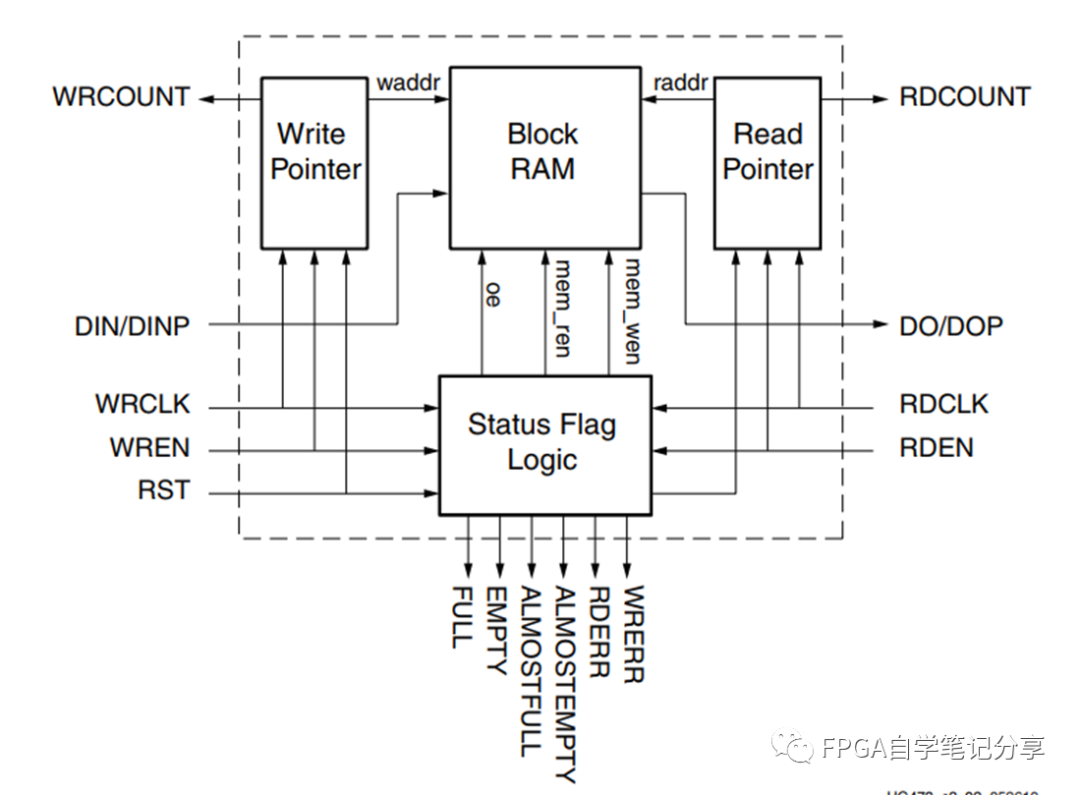

本文介紹了一個基于FPGA的內(nèi)存到串行數(shù)據(jù)傳輸模塊,該模塊設(shè)計用來高效地處理存儲器中的數(shù)據(jù)并傳輸至串行接口。項目中自定義的“datamover_mm2s_fpga_”方案利用異步FIFO結(jié)構(gòu)來解決不同時鐘域之間數(shù)據(jù)傳輸?shù)耐絾栴}。

2025-11-12 14:31:30 4133

4133

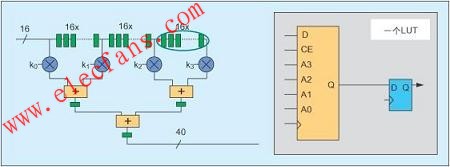

SERDES恢復(fù)出的數(shù)據(jù)進(jìn)入FPGA有一個解復(fù)用和時鐘域轉(zhuǎn)換的問題,Stratix GX包含了專用電路可以完成8/10bit數(shù)據(jù)到8/10/20bit數(shù)據(jù)的Mux/Demux,另外SERDES收端到FPGA內(nèi)部通用邏輯資源之間還有FIFO可以完成數(shù)據(jù)接口同步,其電路結(jié)構(gòu)如圖所示。

2018-04-08 08:46:50 10439

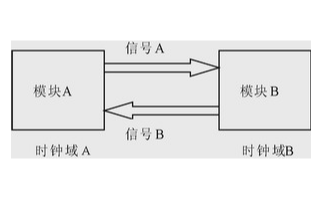

10439 跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。 在本篇文章中,主要

2020-11-21 11:13:01 4997

4997

01、如何決定FPGA中需要什么樣的時鐘速率 設(shè)計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設(shè)計中兩個觸發(fā)器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期 T,則

2020-11-23 13:08:24 4644

4644

有一個有趣的現(xiàn)象,眾多數(shù)字設(shè)計特別是與FPGA設(shè)計相關(guān)的教科書都特別強(qiáng)調(diào)整個設(shè)計最好采用唯一的時鐘域。

2023-12-22 09:04:46 2675

2675

一般的FPGA的數(shù)據(jù)傳輸接送接口不都是用USB的么,我想用藍(lán)牙無線的接口,想買響應(yīng)的藍(lán)牙模塊,有沒有能和Spartan-3 FPGA 系列 相匹配的藍(lán)牙模塊呢?

2019-08-14 16:33:55

一般的FPGA的數(shù)據(jù)傳輸接送接口不都是用USB的么,我想用藍(lán)牙無線的接口,想買響應(yīng)的藍(lán)牙模塊,有沒有能和Spartan-6 FPGA 系列 相匹配的藍(lán)牙模塊呢?

2019-08-13 17:03:34

即可。

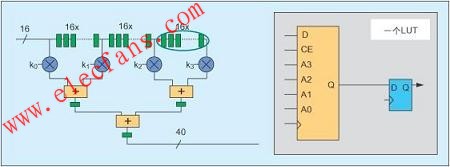

下面是一個4輸入與門的例子。

二、基于查找表(LUT)的FPGA的結(jié)構(gòu)

我們看一看Xilinx Spartan-II的內(nèi)部結(jié)構(gòu),如下圖:

Spartan-II主要包括CLBs

2023-11-03 11:18:38

FPGA 實現(xiàn)大型設(shè)計時,可能需要FPGA 具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘FPGA 設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)據(jù)關(guān)系。設(shè)計過程中

2012-10-26 17:26:43

本帖最后由 lee_st 于 2017-10-31 08:58 編輯

FPGA多時鐘設(shè)計

2017-10-21 20:28:45

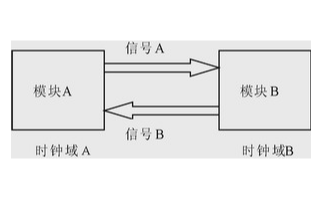

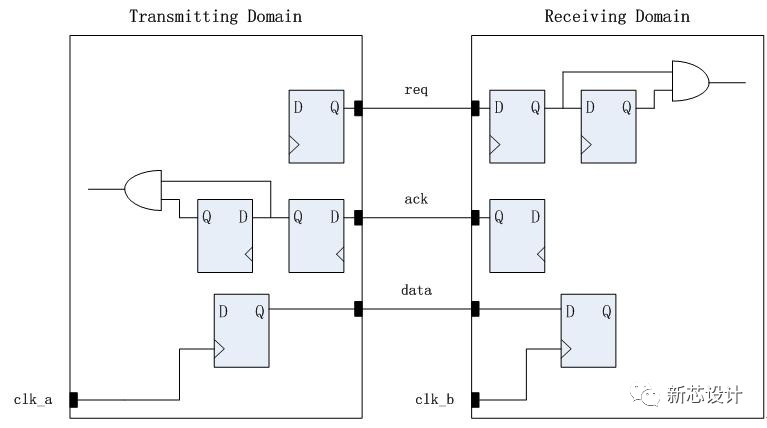

跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還在校生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。這里主要介紹三種跨時鐘域

2021-03-04 09:22:51

利用FPGA實現(xiàn)大型設(shè)計時,可能需要FPGA具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘FPGA設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)據(jù)關(guān)系。設(shè)計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進(jìn)行布線?

2019-08-30 08:31:41

(LUT)的FPGA的結(jié)構(gòu)我們看一看xilinx Spartan-II的內(nèi)部結(jié)構(gòu),如下圖: xilinx Spartan-II 芯片內(nèi)部結(jié)構(gòu)Slices結(jié)構(gòu)Spartan-II主要包括CLBs,I

2012-04-28 14:57:28

FPGA的多時鐘系統(tǒng)設(shè)計 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

FPGA設(shè)計中有多個時鐘域時如何處理?跨時鐘域的基本設(shè)計方法是:(1)對于單個信號,使用雙D觸發(fā)器在不同時鐘域間同步。來源于時鐘域1的信號對于時鐘域2來說是一個異步信號。異步信號進(jìn)入時鐘域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA開發(fā)中,遇到的最多的就是異步時鐘域了。[size=11.818181991577148px]檢查初學(xué)者的代碼,發(fā)現(xiàn)最多的就是這類

2014-08-13 15:36:55

(10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

的Spartan-3A的Spartan-3ESpartan-3系列的Spartan-IIE的Spartan-II謝謝&問候。以上來自于谷歌翻譯以下為原文Sir/ Madam, In our

2019-05-08 14:52:17

Spartan-II 應(yīng)用指南XAPP058 -利用嵌入式微控制器進(jìn)行Xilinx在系統(tǒng)(In-System)編程Xilinx 高性能CPLD、FPGA和可配置的PROM系列提供了在系統(tǒng)

2021-08-12 07:39:42

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進(jìn)行設(shè)計”第 1 章 “概述”第 2 章 “使用全局時鐘資源”第 3

2013-02-27 20:20:10

00000000000001000010....0...01111111111 二.基于查找表(LUT)的FPGA的結(jié)構(gòu) 我們看一看xilinx Spartan-II的內(nèi)部結(jié)構(gòu),如下圖:xilinx

2008-05-20 09:46:10

采用FPGA來設(shè)計一款廣泛應(yīng)用于計算機(jī)、Modem、數(shù)據(jù)終端以及許多其他數(shù)字設(shè)備之間的數(shù)據(jù)傳輸?shù)膶S卯惒讲⑿型ㄐ沤涌谛酒?b class="flag-6" style="color: red">實現(xiàn)了某一時鐘域(如66 MHz)的8位并行數(shù)據(jù)到另一低時鐘域(如40 MHz)16

2011-09-07 09:16:40

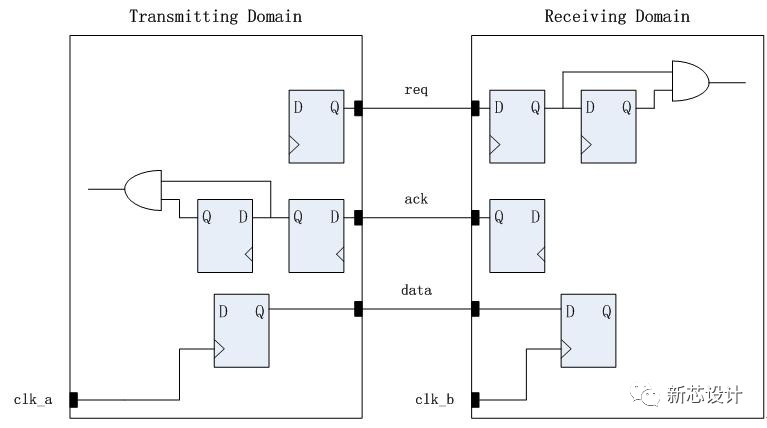

出現(xiàn)問題,來自快時鐘域的控制信號必須寬于較慢時鐘的周期。否則如下圖所示,快時鐘域的控制信號無法被采樣到慢時鐘域。3、在時鐘域之間同步數(shù)據(jù)的兩種常用方法將數(shù)據(jù)從一個時鐘域傳遞到另一個時鐘域類似于傳遞多個

2022-04-11 17:06:57

組來定義策略。在多個時鐘域之間傳遞控制信號時,嘗試使用同步器的策略。嘗試使用FIFO和緩存的數(shù)據(jù)路徑同步器來提高數(shù)據(jù)完整性。現(xiàn)在討論重要的跨時鐘處理問題與策略及其在多時鐘域設(shè)計中的使用。多時鐘域設(shè)計有

2022-06-24 16:54:26

大家好:最近在做基于FPGA 的以太網(wǎng)數(shù)據(jù)通信,現(xiàn)在遇到的問題是利用nios i和以太網(wǎng)芯片通信已經(jīng)實現(xiàn),但是niosII 讀取的以太網(wǎng)傳遞的數(shù)據(jù)怎么傳遞到FPGA 頂層模塊,用硬件邏輯設(shè)計語言實現(xiàn)進(jìn)一步處理,請大家指點(diǎn),小弟不勝感激!

2016-07-13 15:59:26

雙口RAM如何實現(xiàn)跨時鐘域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

利用 FPGA 實現(xiàn)大型設(shè)計時,可能需要FPGA 具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘 FPGA 設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)據(jù)關(guān)系

2012-03-05 14:42:09

跨越時鐘域FPGA設(shè)計中可以使用多個時鐘。每個時鐘形成一個FPGA內(nèi)部時鐘域“,如果需要在另一個時鐘域的時鐘域產(chǎn)生一個信號,需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標(biāo)志第3部分:穿越

2012-03-19 15:16:20

labview生成安裝程序(里面數(shù)據(jù)傳遞用共享變量) 在本電腦上可以傳遞數(shù)據(jù),安裝到其他電腦上無法傳遞數(shù)據(jù),何解?

2016-07-08 13:57:24

關(guān)于異步時鐘域的理解的問題: 這里面的count[25]、和count[14]和count[1]算是多時鐘域吧?大俠幫解決下我的心結(jié)呀,我這樣的理解對嗎?

2012-02-27 15:50:12

平臺。該平臺支持同一時間內(nèi)32 個時鐘運(yùn)行,也就是說每個片上網(wǎng)絡(luò)的內(nèi)核可以在一個獨(dú)立的時鐘下運(yùn)行, 從而使每個路由器和IP 核都運(yùn)行在最佳頻率上。因此適用于設(shè)計多時鐘片上網(wǎng)絡(luò),實現(xiàn)高性能分組交換片上網(wǎng)絡(luò)。

2019-08-21 06:47:43

AD接口:時鐘對齊、根據(jù)幀同步實現(xiàn)串轉(zhuǎn)并數(shù)據(jù)對齊.本人非常熟悉Virtex-5/Virtex-6/7 Series FPGA的內(nèi)置SERDES模塊,包括ISERDES,OSERDES,IODELAY

2014-03-01 18:47:47

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設(shè)計中FPGA的多時鐘設(shè)計策略 利用FPGA實現(xiàn)大型設(shè)計時,可能需要FPGA具有以多個時鐘運(yùn)行的多重數(shù)據(jù)

2012-05-23 19:59:34

利用FPGA實現(xiàn)大型設(shè)計時,可能需要FPGA具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘FPGA設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)據(jù)關(guān)系。設(shè)計過程中

2015-05-22 17:19:26

嗨, 我正在使用Saturn Spartan6 numato板。我在董事會中實現(xiàn)了一個非常簡單的要求版本。現(xiàn)在我想將數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">FPGA或從FPGA傳輸?shù)絇C。請?zhí)岢鲆恍┙ㄗh。謝謝。

2019-07-31 10:36:37

時鐘域轉(zhuǎn)換中亞穩(wěn)態(tài)是怎樣產(chǎn)生的?多時鐘域數(shù)據(jù)傳遞的FPGA實現(xiàn)

2021-04-30 06:06:32

:int main (void){各種初始化while(1){ 觸摸屏 LCD刷新 串口通信 } }就像這個小例子,觸摸屏按鍵的操作和串口的數(shù)據(jù)要顯示在LCD上。換做u/cos II的話,就是建立3個任務(wù),然后之間再有一些數(shù)據(jù)傳遞就可以了?

2019-04-04 06:36:23

跨時鐘域處理是 FPGA 設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個 FPGA 初學(xué)者的必修課。如果是還在校生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。這里主要介紹三種跨

2020-09-22 10:24:55

跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。在本篇文章中,主要

2021-07-29 06:19:11

我無法訪問WebCase網(wǎng)站。如何獲得HW-USB-II-G平臺USB II和XC3S250E-4PQG208C Spartan FPGA的波動性聲明?謝謝。以上來自于谷歌翻譯以下為原文I am

2019-04-28 13:29:42

對多時鐘系統(tǒng)的同步問題進(jìn)行了討論?提出了亞穩(wěn)態(tài)的概念及其產(chǎn)生機(jī)理和危害;敘述了控制信號和數(shù)據(jù)通路在多時鐘域之間的傳遞?討論了控制信號的輸出次序?qū)ν郊夹g(shù)的不同要求,重點(diǎn)論述了常用的數(shù)據(jù)通路同步技術(shù)----用FIFO實現(xiàn)同步的原理及其實現(xiàn)思路

2012-05-23 19:54:32

親愛的朋友們, 我有一個多鎖設(shè)計。時鐘為50MHz,200MHz和400Mhz。如果僅使用400MHz時鐘并使用時鐘使能產(chǎn)生200Mhz和50Mhz時鐘域。現(xiàn)在我需要將信號從一個時鐘域傳遞到另一個

2019-03-11 08:55:24

實現(xiàn)數(shù)據(jù)傳遞需要做些什么?需要用到什么?怎么才能讓數(shù)據(jù)傳遞到另一端?服務(wù)端客戶端

2022-03-02 07:15:44

。雖然這樣可以簡化時序分析以及減少很多與多時鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收

2022-10-14 15:43:00

嗨,我是FPGA的新手(也是Xilinx系列FPGA的新手),所以我想知道Xilinx Spartan-II(XC2S100)FPGA板中是否有內(nèi)置/預(yù)編程的Verilog模塊或變量。這是因為我正在

2019-06-04 12:36:34

你好,我有一個用于VHART開發(fā)的SPARTAN II的舊FPGA設(shè)計。有沒有辦法使用當(dāng)前的設(shè)計工具為SPARTAN II開發(fā)代碼?謝謝tower_dig.vhd 30 KB以上來自于谷歌翻譯以下

2019-06-17 09:23:59

`各位高手,請教下如何用隊列實現(xiàn)vi之間的數(shù)據(jù)傳遞,最好能給出個例子,我是初學(xué)者,謝謝`

2017-09-08 11:01:12

減少很多與多時鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號

2023-06-02 14:26:23

Multiple Clock System Design PLD設(shè)計技巧—多時鐘系統(tǒng)設(shè)計

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 在大規(guī)模集成電路設(shè)計中,一個系統(tǒng)包含了很多不相關(guān)的時鐘信號,當(dāng)其目標(biāo)域時鐘與源域時鐘不同時,如何在這些不同域之間傳遞數(shù)據(jù)成為了一個重要問題。為了解決這個問題,

2009-12-14 10:19:07 14

14 提出一種基于DCT域的數(shù)字水印算法,并用FPGA硬件實現(xiàn)其中關(guān)鍵部分DCT變換。采用VHDL語言有效設(shè)計和實現(xiàn)DCT變換,分析與仿真結(jié)果表明:與軟件實現(xiàn)相比,用FPGA實現(xiàn)水印算法具有高

2010-12-28 10:22:14 20

20 大型設(shè)計中FPGA的多時鐘設(shè)計策略

利用FPGA實現(xiàn)大型設(shè)計時,可能需要FPGA具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘FPGA設(shè)計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 827

827

Spartan-3FPGA能以突破性的價位點(diǎn)實現(xiàn)嵌入式DSP功能。本文闡述了Spartan-3 FPGA針

2010-12-17 11:31:23 1032

1032

利用FPGA實現(xiàn)大型設(shè)計時,可能需要FPGA具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘FPGA設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)

2012-05-21 11:26:10 1591

1591

NBP16 Xilinx Spartan-II PQ208 Rev1.01

2016-02-17 15:04:39 0

0 時鐘設(shè)施提供了一系列的低電容、低抖動的互聯(lián)線,這些互聯(lián)線非常適合于傳輸高頻信號、最大量減小時鐘抖動。這些連線資源可以和DCM、PLL等實現(xiàn)連接。 每一種Spartan-6芯片提供16個高速、低抖動的全局時鐘資源用于優(yōu)化性能。

2018-07-14 07:07:00 10817

10817

在一個SOC設(shè)計中,存在多個、獨(dú)立的時鐘,這已經(jīng)是一件很平常的事情了。大多數(shù)的SOC器件都具有很多個接口,各個接口標(biāo)準(zhǔn)都可能會使用完全不同的時鐘頻率。

2017-02-11 15:07:11 1522

1522 跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還在校的本科生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。 在本篇文章中,主要

2017-11-15 20:08:11 14725

14725 基于FPGA的數(shù)字系統(tǒng)設(shè)計中大都推薦采用同步時序的設(shè)計,也就是單時鐘系統(tǒng)。但是實際的工程中,純粹單時鐘系統(tǒng)設(shè)計的情況很少,特別是設(shè)計模塊與外圍芯片的通信中,跨時鐘域的情況經(jīng)常不可避免。如果對跨時鐘域

2018-09-01 08:29:21 6010

6010

了解如何描述Spartan-6 FPGA中的全局和I / O時鐘網(wǎng)絡(luò),描述時鐘緩沖器及其與I / O資源的關(guān)系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 5904

5904 本文檔的主要內(nèi)容詳細(xì)介紹的是spartan-6 FPGA的時鐘資源的用戶指南資料免費(fèi)下載。

2019-02-15 16:39:07 28

28 Spartan-3an FPGA系列將領(lǐng)先、低成本的FPGA的最佳特性與廣泛密度范圍內(nèi)的非易失性技術(shù)相結(jié)合。該系列結(jié)合了Spartan-3A FPGA系列的所有功能,以及系統(tǒng)閃存中的領(lǐng)先技術(shù),用于配置和非易失性數(shù)據(jù)存儲。

2019-05-27 08:00:00 4

4 跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設(shè)計中的常見現(xiàn)象。在FPGA領(lǐng)域,互動的異步時鐘域的數(shù)量急劇增加。通常不止數(shù)百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 3895

3895 Spartan-6 FPGA 利用CCL 支持布線線路與邏輯單元之間的可配置互聯(lián)功能。Spartan-6 FPGA 是易失性器件- 電源移除時,不能保留原有配置。為了配置Spartan

2020-01-10 15:28:51 28

28 外部輸入的信號與本地時鐘是異步的。在SoC設(shè)計中,可能同時存在幾個時鐘域,信號的輸出驅(qū)動和輸入采樣在不同的時鐘節(jié)拍下進(jìn)行,可能會出現(xiàn)一些不穩(wěn)定的現(xiàn)象。本文分析了在跨時鐘域信號傳遞時可能會遇見的問題,并介紹了幾種處理異步時鐘域接口的方法。

2020-07-24 09:52:24 5223

5223

有一個有趣的現(xiàn)象,眾多數(shù)字設(shè)計特別是與FPGA設(shè)計相關(guān)的教科書都特別強(qiáng)調(diào)整個設(shè)計最好采用唯一的時鐘域。

2020-09-24 10:20:00 3603

3603

跨時鐘域處理是 FPGA 設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個 FPGA 初學(xué)者的必修課。如果是還在校生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。 這里主要介紹三種

2022-12-05 16:41:28 2398

2398 利用 FPGA 實現(xiàn)大型設(shè)計時,可能需要FPGA 具有以多個時鐘運(yùn)行的多重數(shù)據(jù)通路,這種多時鐘FPGA 設(shè)計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數(shù)、異步時鐘設(shè)計和時鐘/數(shù)據(jù)關(guān)系。設(shè)計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進(jìn)行布線,本文將對這些設(shè)計策略深入闡述。

2021-01-15 15:57:00 14

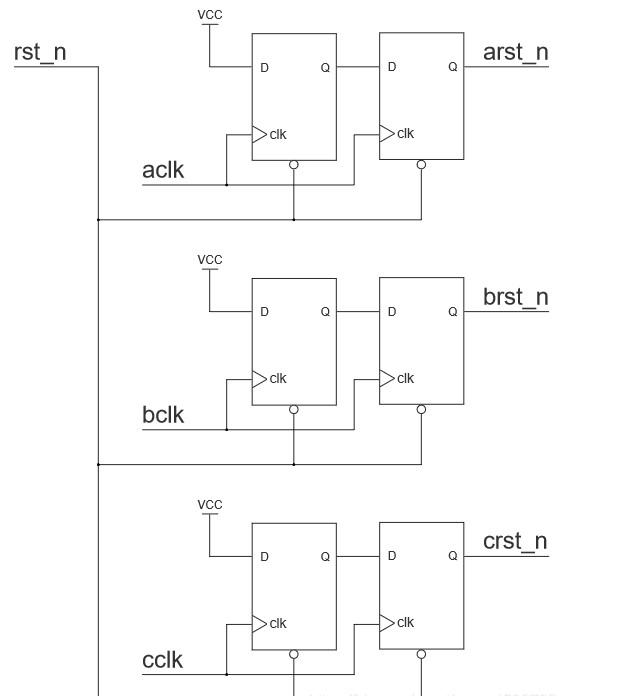

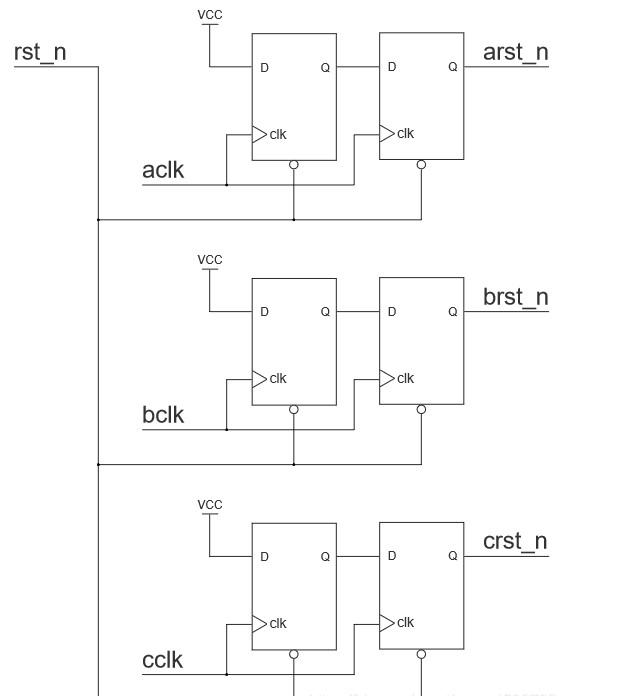

14 1 多時鐘域的異步復(fù)位同步釋放 當(dāng)外部輸入的復(fù)位信號只有一個,但是時鐘域有多個時,使用每個時鐘搭建自己的復(fù)位同步器即可,如下所示。 verilog代碼如下: module CLOCK_RESET

2021-05-08 09:59:07 3063

3063

減少很多與多時鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。 FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗

2021-05-10 16:51:39 4652

4652

EDA技術(shù)使得電子線路的設(shè)計人員能在計算機(jī)上完成電路的功能設(shè)計、邏輯設(shè)計、時序測試直至印刷電路板的自動設(shè)計。本文介紹了以 VHDL 語言和硬件電路為表達(dá)方式,以 Quartus II 軟件為設(shè)計工具,最終通過 FPGA 器件實現(xiàn)數(shù)字時鐘的設(shè)計過程。

2021-05-25 16:28:10 40

40 跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還是在校的學(xué)生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。 在本篇文章中,主要

2021-09-18 11:33:49 23260

23260

減少很多與多時鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗

2021-09-23 16:39:54 3632

3632 說到異步時鐘域的信號處理,想必是一個FPGA設(shè)計中很關(guān)鍵的技術(shù),也是令很多工程師對FPGA望 而卻步的原因。但是異步信號的處理真的有那么神秘嗎?那么就讓特權(quán)同學(xué)和你一起慢慢解開這些所謂的難點(diǎn)

2021-11-01 16:24:39 11

11 (10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結(jié)語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 時鐘域clock domain:以寄存器捕獲的時鐘來劃分時鐘域。

單時鐘域single clock domain,數(shù)據(jù)發(fā)送和接收是同一個時鐘

多時鐘域multiple clock domain,數(shù)據(jù)發(fā)送和接收是不是同一個時鐘

2022-08-29 15:11:21 3317

3317 Spartan-II主要包括CLBs,I/O塊,RAM塊和可編程連線(未表示出)。在spartan-II中,一個CLB包括2個Slices,每個slices包括兩個LUT,兩個觸發(fā)器和相關(guān)邏輯

2022-09-21 14:34:23 2318

2318 跨時鐘域處理是FPGA設(shè)計中經(jīng)常遇到的問題,而如何處理好跨時鐘域間的數(shù)據(jù),可以說是每個FPGA初學(xué)者的必修課。如果是還在校生,跨時鐘域處理也是面試中經(jīng)常常被問到的一個問題。

2022-10-18 09:12:20 9685

9685 我們在ASIC或FPGA系統(tǒng)設(shè)計中,常常會遇到需要在多個時鐘域下交互傳輸?shù)膯栴},時序問題也隨著系統(tǒng)越復(fù)雜而變得更為嚴(yán)重。

2023-04-06 10:56:35 1479

1479 跨時鐘域是FPGA設(shè)計中最容易出錯的設(shè)計模塊,而且一旦跨時鐘域出現(xiàn)問題,定位排查會非常困難,因為跨時鐘域問題一般是偶現(xiàn)的,而且除非是構(gòu)造特殊用例一般的仿真是發(fā)現(xiàn)不了這類問題的。

2023-05-25 15:06:00 2919

2919

上一篇文章已經(jīng)講過了單bit跨時鐘域的處理方法,這次解說一下多bit的跨時鐘域方法。

2023-05-25 15:07:19 1622

1622

所謂數(shù)據(jù)流跨時鐘域即:時鐘不同但是時間段內(nèi)的數(shù)據(jù)量一定要相同。

2023-05-25 15:19:15 2725

2725

電子發(fā)燒友網(wǎng)站提供《在Spartan 6 FPGA上從頭開始實現(xiàn)全加器.zip》資料免費(fèi)下載

2023-06-15 10:13:28 0

0 ??類似于電源域(電源規(guī)劃與時鐘規(guī)劃亦是對應(yīng)的),假如設(shè)計中所有的 D 觸發(fā)器都使用一個全局網(wǎng)絡(luò) GCLK ,比如 FPGA 的主時鐘輸入,那么我們說這個設(shè)計只有一個時鐘域。假如設(shè)計有兩個輸入時鐘,分別給不同的接口使用,那么我們說這個設(shè)計中有兩個時鐘域,不同的時鐘域,有著不同的時鐘頻率和時鐘相位。

2023-06-21 11:53:22 4098

4098

減少很多與多時鐘域有關(guān)的問題,但是由于FPGA外各種系統(tǒng)限制,只使用一個時鐘常常又不現(xiàn)實。FPGA時常需要在兩個不同時鐘頻率系統(tǒng)之間交換數(shù)據(jù),在系統(tǒng)之間通過多I/O接口接收和發(fā)送數(shù)據(jù),處理異步信號,以及為帶門控時鐘的低功耗

2023-08-23 16:10:01 1372

1372 時,由于時鐘頻率不同,所以可能會產(chǎn)生元件的不穩(wěn)定情況,導(dǎo)致傳輸數(shù)據(jù)的錯誤。此時我們需要采取一些特殊的措施,來保證跨時鐘域傳輸?shù)恼_性。 FPGA跨時鐘域通信的基本實現(xiàn)方法是通過FPGA內(nèi)部專門的邏輯元件進(jìn)行數(shù)據(jù)傳輸。發(fā)送方用一個邏輯電路

2023-10-18 15:23:51 1901

1901

電子發(fā)燒友App

電子發(fā)燒友App

評論