?

在眾多當代應用中,嵌入式系統(tǒng)必須滿足極其苛刻的時序要求。其中之一就是啟動時間——即上電后電子系統(tǒng)進入可操作狀態(tài)所需要的時間。PCI Express?產品或汽車應用中基于CAN的電子控制單元(ECU)就是具有嚴格時序要求的電子系統(tǒng)的應用實例。

標準PCI Express?(PCIe)系統(tǒng)上電后僅100毫秒,系統(tǒng)的根組件就開始掃描總線以便弄清拓撲結構,并在這一過程中進行初始化配置。?如果PCIe設備沒有準備好響應配置請求,根組件就找不到此PCIe設備,并認為它不存在。該設備將無法加入PCIe總線系統(tǒng)。[1]

汽車應用中的情形與此大體相仿。在基于CAN的網絡中,ECU進入睡眠模式,這時它們將停止運行并切斷電源連接。只有很少部分電路仍然保持戒備狀態(tài),以便探測喚醒信號。一旦出現(xiàn)喚醒事件,ECU就會重新連接電源并開始引導。雖然在喚醒事件后的頭一個100 毫秒內允許錯過一些消息,但在此之后所有ECU都必須在網絡(如CAN網絡)上做好充分的運行準備。

Xilinx Automotive、Xilinx研究實驗室以及德國卡爾斯魯厄技術研究所之間合作展開了深入的研發(fā)工作,正在設法通過一種FPGA兩步配置方法解決這一問題。

半導體行業(yè)的科技趨勢已經能使FPGA廠家大大增加其器件中的資源。但比特流規(guī)模也在成比例地增長,配置器件需要的時間也是如此。因此,即使對于中等規(guī)模的FPGA,使用低成本配置方案也不可能滿足嚴格的啟動時序要求。圖1表示不同的Xilinx? Spartan?-6 FPGA器件在使用低成本SPI/Quad-SPI配置接口時的配置時間。即使使用快速配置方案(即在40 MHz配置時鐘下運行的Quad-SPI),也只有小型FPGA器件才能達到100 毫秒的啟動時序要求。對于Xilinx Virtex?-6器件來說,這個結果看來更具挑戰(zhàn)性,因為這些器件提供了更豐富的FPGA資源。

為了克服這個難題,F(xiàn)ast Startup分兩步配置FPGA器件,而非單步(整片)的全器件配置。按照這種新穎的思路,我們的策略是在上電時使用最高優(yōu)先級比特流僅載入時序關鍵模塊,然后再載入非時序關鍵模塊。這種方法最大程度地減少了初始配置數(shù)據,從而最大程度地減少了在面向時序關鍵設計的FPGA器件啟動時間。

FAST STARTUP對比部分重配置

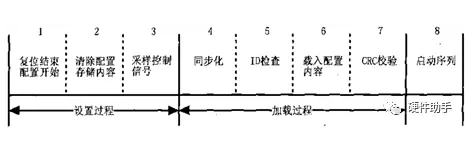

Fast Startup允許FPGA設計盡快啟動設計的關鍵模塊,關鍵模塊的啟動速度比標準全配置方法要快得多[2]。雖然,從本質上來講Fast Startup利用了部分重配置,但它與這種方法的傳統(tǒng)概念所有不同。部分重配置的初衷是將完整設計作為可在運行時修改的初始配置使用。相反,F(xiàn)ast Startup已經使用了一個初始的部分比特流,以在上電時僅僅配置FPGA器件的一個特定(很小的一部分)區(qū)域。第一次配置僅包含完整FPGA設計中必須配置和快速運行的那些部分。而剩下的部分則在以后、在運行時,利用部分重配置進行配置。圖2說明了這一順序概念。

工具流程概述

Fast Startup的工具流程依靠設計保存流程,來創(chuàng)建針對時序關鍵子系統(tǒng)及非時序關鍵子系統(tǒng)的部分比特流。

設計保存流程將FPGA設計分割為邏輯模塊(稱為“分區(qū)”)。分區(qū)構成了層次邊界,將內部模塊與設計中的其他組件相互隔離。分區(qū)一旦實現(xiàn)(即完成布局和布線),就能被其他實現(xiàn)運行導入,以按照每個實例中完全相同的方式實現(xiàn)該分區(qū)的模塊[3]。

因此,使用Fast Startup方法的第一步是將完整的FPGA設計分成兩部分:即含有時序關鍵子系統(tǒng)的高優(yōu)先級分區(qū)和針對其余組件的低優(yōu)先級分區(qū)。

標準PCI Express?(PCIe)系統(tǒng)上電后僅100毫秒,系統(tǒng)的根組件就開始掃描總線以便弄清拓撲結構,并在這一過程中進行初始化配置。?如果PCIe設備沒有準備好響應配置請求,根組件就找不到此PCIe設備,并認為它不存在。該設備將無法加入PCIe總線系統(tǒng)。[1]

汽車應用中的情形與此大體相仿。在基于CAN的網絡中,ECU進入睡眠模式,這時它們將停止運行并切斷電源連接。只有很少部分電路仍然保持戒備狀態(tài),以便探測喚醒信號。一旦出現(xiàn)喚醒事件,ECU就會重新連接電源并開始引導。雖然在喚醒事件后的頭一個100 毫秒內允許錯過一些消息,但在此之后所有ECU都必須在網絡(如CAN網絡)上做好充分的運行準備。

Xilinx Automotive、Xilinx研究實驗室以及德國卡爾斯魯厄技術研究所之間合作展開了深入的研發(fā)工作,正在設法通過一種FPGA兩步配置方法解決這一問題。

半導體行業(yè)的科技趨勢已經能使FPGA廠家大大增加其器件中的資源。但比特流規(guī)模也在成比例地增長,配置器件需要的時間也是如此。因此,即使對于中等規(guī)模的FPGA,使用低成本配置方案也不可能滿足嚴格的啟動時序要求。圖1表示不同的Xilinx? Spartan?-6 FPGA器件在使用低成本SPI/Quad-SPI配置接口時的配置時間。即使使用快速配置方案(即在40 MHz配置時鐘下運行的Quad-SPI),也只有小型FPGA器件才能達到100 毫秒的啟動時序要求。對于Xilinx Virtex?-6器件來說,這個結果看來更具挑戰(zhàn)性,因為這些器件提供了更豐富的FPGA資源。

為了克服這個難題,F(xiàn)ast Startup分兩步配置FPGA器件,而非單步(整片)的全器件配置。按照這種新穎的思路,我們的策略是在上電時使用最高優(yōu)先級比特流僅載入時序關鍵模塊,然后再載入非時序關鍵模塊。這種方法最大程度地減少了初始配置數(shù)據,從而最大程度地減少了在面向時序關鍵設計的FPGA器件啟動時間。

FAST STARTUP對比部分重配置

Fast Startup允許FPGA設計盡快啟動設計的關鍵模塊,關鍵模塊的啟動速度比標準全配置方法要快得多[2]。雖然,從本質上來講Fast Startup利用了部分重配置,但它與這種方法的傳統(tǒng)概念所有不同。部分重配置的初衷是將完整設計作為可在運行時修改的初始配置使用。相反,F(xiàn)ast Startup已經使用了一個初始的部分比特流,以在上電時僅僅配置FPGA器件的一個特定(很小的一部分)區(qū)域。第一次配置僅包含完整FPGA設計中必須配置和快速運行的那些部分。而剩下的部分則在以后、在運行時,利用部分重配置進行配置。圖2說明了這一順序概念。

工具流程概述

Fast Startup的工具流程依靠設計保存流程,來創(chuàng)建針對時序關鍵子系統(tǒng)及非時序關鍵子系統(tǒng)的部分比特流。

設計保存流程將FPGA設計分割為邏輯模塊(稱為“分區(qū)”)。分區(qū)構成了層次邊界,將內部模塊與設計中的其他組件相互隔離。分區(qū)一旦實現(xiàn)(即完成布局和布線),就能被其他實現(xiàn)運行導入,以按照每個實例中完全相同的方式實現(xiàn)該分區(qū)的模塊[3]。

因此,使用Fast Startup方法的第一步是將完整的FPGA設計分成兩部分:即含有時序關鍵子系統(tǒng)的高優(yōu)先級分區(qū)和針對其余組件的低優(yōu)先級分區(qū)。

?

圖1-計算出的Spartan-6配置時間的對數(shù)表示(按最壞情況計算)

圖2 – Fast Startup概念:順序配置

?

?

?

高優(yōu)先級分區(qū)的實現(xiàn)

為了得到盡可能小的高優(yōu)先級分區(qū)的部分比特流,設計中有一些一般性問題需要考慮。首先,該分區(qū)必須只能包含此類組件:或者是時序關鍵組件,或者是系統(tǒng)需要這些組件來執(zhí)行低優(yōu)先級部分(如ICAP)的部分重配置。得到小規(guī)模初始部分比特流的關鍵是使用盡可能小的區(qū)域實現(xiàn)高優(yōu)先級分區(qū)。也就是說,您必須將這個分區(qū)局限在FPGA中的一個適當區(qū)域中。

為了在FPGA中找到理想的物理位置,這個區(qū)域應該提供該設計需要的適當數(shù)量的資源。訪問該區(qū)域以外的資源也是可行的,但我們不鼓勵這么做——盡管對于I/O引腳來說,

這樣做一般是無法避免的。在尋找適當區(qū)域時,還要牢記的是這個FPGA區(qū)域有可能會妨礙FPGA設計中非時序關鍵部分的資源。

當您已經對FPGA進行分區(qū),且已經找到了這些分區(qū)的適當區(qū)域之后,下一步就是使用一個空的(黑盒子)低優(yōu)先級分區(qū)實現(xiàn)高優(yōu)先級分區(qū)。得到的比特流含有很多針對未使用資源的配置幀。您可以刪除這些幀,以便得到針對初步配置高優(yōu)先級分區(qū)的有效部分比特流。[4]

低優(yōu)先級分區(qū)的實現(xiàn)

為了創(chuàng)建低優(yōu)先級的部分比特流,首先,您要創(chuàng)建含有這兩個分區(qū)(即高優(yōu)先級分區(qū)和低優(yōu)先級分區(qū))的完整FPGA設計的實現(xiàn)。從以前的實現(xiàn)中導入高優(yōu)先級分區(qū),從而保證其實現(xiàn)方法與原來的實現(xiàn)方法相同。

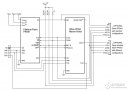

對于Virtex-6器件而言,部分重配置(PR)流程可用于所有上述的實現(xiàn)。這樣,就會自動得到針對低優(yōu)先級分區(qū)的部分比特流。由于Spartan-6器件?系列不支持PR流程,在實現(xiàn)針對Spartan-6設計的Fast Startup時,我們使用了針對差異化的部分重配置的BitGen選項,以獲得低優(yōu)先級分區(qū)的部分比特流。[5]圖3給出了該工具流程的高層概覽。

為了得到盡可能小的高優(yōu)先級分區(qū)的部分比特流,設計中有一些一般性問題需要考慮。首先,該分區(qū)必須只能包含此類組件:或者是時序關鍵組件,或者是系統(tǒng)需要這些組件來執(zhí)行低優(yōu)先級部分(如ICAP)的部分重配置。得到小規(guī)模初始部分比特流的關鍵是使用盡可能小的區(qū)域實現(xiàn)高優(yōu)先級分區(qū)。也就是說,您必須將這個分區(qū)局限在FPGA中的一個適當區(qū)域中。

為了在FPGA中找到理想的物理位置,這個區(qū)域應該提供該設計需要的適當數(shù)量的資源。訪問該區(qū)域以外的資源也是可行的,但我們不鼓勵這么做——盡管對于I/O引腳來說,

這樣做一般是無法避免的。在尋找適當區(qū)域時,還要牢記的是這個FPGA區(qū)域有可能會妨礙FPGA設計中非時序關鍵部分的資源。

當您已經對FPGA進行分區(qū),且已經找到了這些分區(qū)的適當區(qū)域之后,下一步就是使用一個空的(黑盒子)低優(yōu)先級分區(qū)實現(xiàn)高優(yōu)先級分區(qū)。得到的比特流含有很多針對未使用資源的配置幀。您可以刪除這些幀,以便得到針對初步配置高優(yōu)先級分區(qū)的有效部分比特流。[4]

低優(yōu)先級分區(qū)的實現(xiàn)

為了創(chuàng)建低優(yōu)先級的部分比特流,首先,您要創(chuàng)建含有這兩個分區(qū)(即高優(yōu)先級分區(qū)和低優(yōu)先級分區(qū))的完整FPGA設計的實現(xiàn)。從以前的實現(xiàn)中導入高優(yōu)先級分區(qū),從而保證其實現(xiàn)方法與原來的實現(xiàn)方法相同。

對于Virtex-6器件而言,部分重配置(PR)流程可用于所有上述的實現(xiàn)。這樣,就會自動得到針對低優(yōu)先級分區(qū)的部分比特流。由于Spartan-6器件?系列不支持PR流程,在實現(xiàn)針對Spartan-6設計的Fast Startup時,我們使用了針對差異化的部分重配置的BitGen選項,以獲得低優(yōu)先級分區(qū)的部分比特流。[5]圖3給出了該工具流程的高層概覽。

圖3 – Fast Startup工具流程

- FPGA(632043)

- Xilinx(130366)

相關推薦

熱點推薦

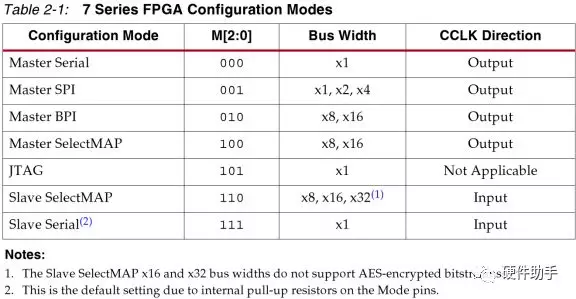

一文詳解xilinx 7系列FPGA配置技巧

本文旨在通過講解不同模式的原理圖連接方式,進而配置用到引腳的含義(手冊上相關引腳含義有四、五頁,通過本文理解基本上能夠記住所有引腳含義以及使用場景),熟悉xilinx 7系列配置流程,以及設計原理圖時需要注意的一些事項,比如flash與FPGA的上電時序。

2025-08-30 14:35:28 9297

9297

9297

9297

詳解Xilinx FPGA的配置模式(Master/Slave模式,Serial/SelectMAP模式)

本文主要介紹Xilinx FPGA的配置模式。

2021-01-01 10:12:00 29342

29342

29342

29342

FPGA配置原理說明

我們所說的FPGA配置電路,一方面要完成從PC上把bit文件下載到FPGA或存儲器的任務,另一方面則要完成FPGA上電啟動時加載配置數(shù)據的任務。

2023-06-10 10:09:52 1107

1107

1107

1107

XILINX FPGA IP之Clocking Wizard詳解

鎖相環(huán)基本上是每一個fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時鐘資源對xilinx fpga的底層時鐘資源做過說明,但是對于fpga的應用來說,使用Clocking Wizard IP時十分方便的。

2023-06-12 17:42:03 8964

8964

8964

8964

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Multiboot是一種在AMD Xilinx 7系列FPGA上實現(xiàn)雙鏡像(或多鏡像)切換的方案。它允許在FPGA中加載兩個不同的配置鏡像,并在需要時切換。

2024-02-25 10:54:32 2398

2398

2398

2398

Xilinx FPGA配置的一些細節(jié)

:CCLK,重新生成download.bit,SelectMAP加載,FPGA工作正常!查Xilinx關于SelectMAP的說明(v4的配置手冊ug71.pdf),發(fā)現(xiàn)一句話:The BitGen

2015-09-22 23:36:50

Xilinx FPGA配置的一些細節(jié)

Xilinx FPGA配置的一些細節(jié)0 參考資料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目錄

2015-08-20 22:57:10

Xilinx FPGA配置的一些細節(jié)

Xilinx FPGA配置的一些細節(jié)0 參考資料(1) Xilinx: Development SystemReference Guide. dev.pdf, v10.1在Xilinx的doc目錄

2016-05-22 23:38:23

Xilinx FPGA入門之PLL實例的基本配置

Xilinx FPGA入門連載24:PLL實例之基本配置 1 工程移植可以復制上一個實例sp6ex7的整個工程文件夾,更名為sp6ex8。然后在ISE中打開這個新的工程。 2 新建IP核文件

2019-01-21 21:33:40

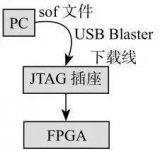

Xilinx FPGA入門連載15:PWM蜂鳴器驅動之FPGA在線下載配置

“Tools à iMPACT...”,啟動專門用于FPGA下載配置的iMAPCT工具。第一次打開通常會彈出如下圖所示的提示,點擊“OK”繼續(xù)。IMAPCT界面打開如下圖所示。 2 初始化下載線纜連接

2015-10-22 12:35:16

Xilinx FPGA無痛入門,海量教程免費下載

-- PWM蜂鳴器驅動之引腳分配Lesson15 特權Xilinx FPGA SF-SP6入門指南 -- PWM蜂鳴器驅動之綜合實現(xiàn)與配置文件產生Lesson16 特權Xilinx FPGA

2015-07-22 11:49:20

Xilinx FPGA片內ROM實例之ROM配置

Xilinx FPGA入門連載44:FPGA片內ROM實例之ROM配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 ROM初始化

2019-01-09 16:02:21

Xilinx FPGA的JTAG配置方式和PROM配置方式的問題

大家好,最近剛接觸FPGA不久 現(xiàn)在手上有一塊xilinx SP3E開發(fā)板,簡單的設計了一個流水燈的程序 通過JTAG下載方式 直接下到FPGA里 板子可以運行 因為想實現(xiàn)斷電后重啟板子自動

2014-10-11 11:16:08

Xilinx SelectMAP 配置問題

想通過SelectMAP方式配置Xilinx Virtex II。Selectmap的時序通過另外一個Altera FPGA控制,配置數(shù)據存放在SRAM中,Altera FPGA讀出SRAM數(shù)據,每

2015-07-16 16:30:47

Xilinx公司的XC5VFX100T型號的FPGA用什么芯片配置

Xilinx公司的XC5VFX100T型號的FPGA用什么芯片配置,我發(fā)現(xiàn)Xilinx公司自己的XCF32P好像存儲空間不滿足,是否有其他芯片,或者就是XCF32P?

2020-01-15 14:16:09

Xilinx_FPGA下載燒寫教程(超詳細)

Xilinx_FPGA下載燒寫教程(超詳細)Step by step 學習下載配置 Xilinx 之 FPGA配合 Mars-EDA 的 Spartan2 核心板,用圖文方式向大家詳細講述如何下載配置 Xilinx的 FPGA。

2017-10-31 12:16:03

什么是Xilinx Spartan-3系列FPGA的配置電路?

這里要談的是Xilinx的spartan-3系列FPGA的配置電路。當然了,其它系列的FPGA配置電路都是大同小異的,讀者可以類推,重點參考官方提供的datasheet,畢竟那才是最權威的資料。

2019-10-10 06:16:52

在Xilinx FPGA上快速實現(xiàn)JESD204B

取代連接轉換器的傳統(tǒng)并行LVDS/CMOS接口,并用來實現(xiàn) JESD204B物理層。本文介紹如何快速在Xilinx? FPGA上實現(xiàn)JESD204B接口,并為FPGA設計人員提供部分應用和調試建議

2018-10-16 06:02:44

在BPI快速模式下配置FPGA無法從Flash啟動的解決辦法?

我使用外部配置emcclk時鐘和閃存PC28F00AP30EFA在BPI-Fast模式下配置了Kintex7 FPGA。我遵循Xilinx AR#44636并定義了Config_Voltage

2020-06-04 12:45:32

如何快速入門FPGA

快速入門FPGA可以遵循以下步驟:

理解FPGA基礎知識:

FPGA(Field Programmable Gate Array)即現(xiàn)場可編程門陣列,是作為專用集成電路(ASIC)領域中的一種半定制

2024-04-28 09:06:45

如何快速入門FPGA?

快速入門FPGA可以遵循以下步驟:

理解FPGA基礎知識:

FPGA(Field Programmable Gate Array)即現(xiàn)場可編程門陣列,是作為專用集成電路(ASIC)領域中的一種半定制

2024-04-28 08:54:35

如何選擇Xilinx的FPGA產品

Xilinx的FPGA、SoC、MPSoC、RFSoC和ACAP產品介紹使用Xilinx的FPGA、SoC和ACAP進行設計和開發(fā)

2021-01-22 06:38:47

怎么使用SPI閃存啟動選項實現(xiàn)FPGA配置文件的故障安全升級?

Flash來存儲我的FPGA配置數(shù)據。XAPP058中描述的方法是否可以用于故障安全升級,因為XCF32P只允許XC6SLX100的一個配置文件空間?有沒有什么方法可以使用SPI閃存啟動選項實現(xiàn)FPGA

2019-05-30 10:05:15

想通過CYUSB3014配置xilinx FPGA,如何下載CYUSB3014的FPGA配置實用程序工具?

你好

我想通過 CYUSB3014 配置 xilinx FPGA,如何下載 CYUSB3014 的 FPGA 配置實用程序工具?

謝謝。

2024-05-22 07:31:59

采用Xilinx FPGA替代Smart Fusion FPGA可行嗎?

嗨,能否建議我用Xilinx FPGA直接替代智能融合FPGA。目前我的參考設計客戶端正在使用智能融合(A2F200M3F-1FGG256I)FPGA。我想用Xilinx FPGA代替。在配置期間,FPGA引腳不應處于浮空狀態(tài),FPGA引腳應處于已知狀態(tài)。這是我項目的嚴格要求。謝謝,C.一個雷迪。

2020-05-13 08:22:47

用PowerPC860實現(xiàn)FPGA 配置

介紹如何用PowerPC860(MPC860)進行FPGA(Xilinx 的Virtex-II 系列)的配置;給出進行FPGA 配置所需的詳細時序圖和原理圖。本配置基本原理對其它FPGA 的配置也適用。

2009-04-16 14:11:36 18

18

18

18簡化Xilinx和Altera FPGA調試過程

簡化Xilinx和Altera FPGA調試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內部迅速移動探點,而無需重新編譯設計方案。能夠把內部FPGA

2009-11-20 17:46:26 27

27

27

27十分鐘學會Xilinx FPGA 設計

十分鐘學會Xilinx FPGA 設計

Xilinx FPGA設計基礎系統(tǒng)地介紹了Xilinx公司FPGA的結構特點和相關開發(fā)軟件的使用方法,詳細描述了VHDL語言的語法和設計方法,并深入討

2010-03-15 15:09:08 179

179

179

179用PowerPC860實現(xiàn)FPGA配置

摘要:介紹如何用PowerPC860(MPC860)進行FPGA(Xilinx的Virtex-II系列)的配置;給出進行FPGA配置所需的詳細時序圖和原理圖。本配置基本原理對其它FPGA的配置也適用。

2009-06-20 11:02:38 1182

1182

1182

1182

Xilinx FPGA的仿真技術設計指南

Power Expert是一套可以支持Xilinx FPGA設計的最新設計工具,設計數(shù)字系統(tǒng)的工程師只要利用這套工具,便可解決仿真電路的設計問題。這個設計工具網頁詳列Xilinx各種不同的FPGA產品以供工程師挑

2011-03-16 14:48:58 137

137

137

137Xilinx FPGA開發(fā)環(huán)境的配置

一、配置Modelsim ISE的Xilinx的仿真庫 1、編譯仿真庫: A、先將Modelsim安裝目錄C=Modeltech_6.2b下面的modelsim.ini改成存檔格式(取消只讀模式); B、在DOS環(huán)境中,進入Xilinx的根目錄,然后依次進入

2011-03-30 10:19:07 307

307

307

307Xilinx配置指南

用不同的方法配置Xilinx 的FPGA 和編程CPLD 以及PROM,有助于滿足系統(tǒng)設計人員的不同需要。本文檔描述了不同的配置模式以幫助設計人員選擇適當?shù)?b class="flag-6" style="color: red">配置或編程方法,并提供了用于生產或

2011-11-01 14:40:45 39

39

39

39WP253 - 簡化FPGA配置設計過程

本文著重介紹了 Xilinx Platform Flash PROM 如何幫助系統(tǒng)和電路板設計人員簡化 FPGA 配置設計。用于配置 FPGA 的可選解決方案有很多,但它們通常都需要大量的前期設計工作和時間。Platform

2012-01-17 17:33:20 36

36

36

36XAPP483 - 利用 Platform Flash PROM 實現(xiàn)多重啟動功能

一些應用利用 Xilinx FPGA 在每次啟動時可改變配置的能力,根據所需來改變 FPGA 的功能。Xilinx Platform Flash XCFxxP PROM 的設計修訂 (Design Revisioning) 功能,允許用戶在單個PROM 中將多種配置存

2012-01-17 17:40:34 43

43

43

43Xilinx-Spartan6 FPGA實現(xiàn)MultiBoot

通過Xilinx Spartan-6 FPGA 的Multiboot特性,允許用戶一次將多個配置文件下載入Flash中,根據不同時刻的需求,在不掉電重啟的情況下,從中選擇一個來重配置FPGA,實現(xiàn)不同功能,提高器件利用率,增加

2012-03-22 17:18:56 66

66

66

66Xilinx FPGA開發(fā)實用教程(第2版)-徐文波、田耘

本書系統(tǒng)地論述了Xilinx FPGA開發(fā)方法、開發(fā)工具、實際案例及開發(fā)技巧,內容涵蓋Xilinx器件概述、Verilog HDL開發(fā)基礎與進階、Xilinx FPGA電路原理與系統(tǒng)設計

2012-07-31 16:20:42 12480

12480

12480

12480

xilinx公司的7系列FPGA應用指南

本文是關于 xilinx公司的7系列FPGA應用指南。xilinx公司的7系列FPGA包括3個子系列,Artix-7、 Kintex-7和Virtex-7。本資料就是對這3各系列芯片的介紹。 下表是xilinx公司的7系列FPGA芯片容量對比表

2012-08-07 17:22:55 201

201

201

201簡化FPGA配置設計過程

本文著重介紹了 Xilinx Platform Flash PROM 如何幫助系統(tǒng)和電路板設計人員簡化 FPGA 配置設計。用于配置 FPGA 的可選解決方案有很多,但它們通常都需要大量的前期設計工作和時間。Platform

2013-03-14 15:18:22 64

64

64

64Xilinx_FPGA系列入門教程(二)—Xilinx_FPA

Xilinx FPGA系列入門教程(二)——Xilinx FPAG開發(fā)環(huán)境的配置

2016-01-18 15:30:20 35

35

35

35Xilinx_FPGA系列入門教程(一)—如何搭建Xilinx

Xilinx FPGA系列入門教程(一)——如何搭建Xilinx FPGA開發(fā)環(huán)境

2016-01-18 15:30:32 52

52

52

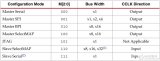

52Xilinx7系列基于PCIe的設計如何滿足PCIe啟動時間的要求

的PCIe設備,需要reboot服務器。眾所周知,FPGA芯片規(guī)模越來越大,那么如何做才能滿足PCIe設備的啟動時間的要求呢? 7系列FPGA常見的配置模式如下圖所示: SelectMAP和Master

2017-02-07 20:55:41 4308

4308

4308

4308

VadaTech面向17款高性能FPGA的Xilinx套件:設計、功耗和性能領先

該 ?FPGA? 載板概覽演示了 ?VadaTech? 如何以一種易于配置的標準化方式使用 ?Xilinx FPGA 。能夠通過多個選項高效低價格地部署復雜計算解決方案只是 ?VadaTech

2017-02-09 02:28:02 370

370

370

370Xilinx FPGA 嵌入式系統(tǒng)程序引導和啟動的流程

這篇blog想弄清楚FPGA上電配置后程序引導和啟動的整個流程是怎么樣的,不是談論如何編寫bootloader。

2017-02-11 05:55:06 2768

2768

2768

2768Xilinx Virtex Ultrascale? FPGA 電源解決方案

PMP9475 12V 輸入參考設計以緊湊高效的設計提供為 Xilinx's Virtex? Ultrascale? 系列 FPGA 供電時所需的所有電源軌。此設計使用幾個 TI 的 PMBus 負載點電壓穩(wěn)壓器以簡化臨界軌的設計/配置和遙測。

2017-02-16 17:50:12 1699

1699

1699

1699

基于Xilinx Kintex UltraScale FPGA的FlexRIO模塊介紹

NI FlexRIO是NI公司推出的FPGA應用的模塊化產品,基于NI LabVIEW可重配置I/ O(RIO)架構的NI FlexRIO在一個平臺中集成了高性能模塊化I / O、功能強大的Xilinx FPGA以及基于PC的技術,是板載處理和實時分析應用系統(tǒng)的理想之選。

2018-07-05 09:11:00 3770

3770

3770

3770Xilinx FPGA設計應用分析

FPGAs have changed dramatically since Xilinx first introduced them just 15 years ago. In the ast

2017-09-20 18:41:55 14

14

14

14V5 FPGA配置回讀

通過SELECTMAP32接口配置和回讀XILINX公司生產的V5系列SRAM型FPGA,被配置的FPGA以下簡稱DUT,產生配置時序的FPGA簡稱配置FPGA。首先硬件上應將M[2:0]接成110

2017-11-17 10:16:01 10667

10667

10667

10667基于CPLD的FPGA快速動態(tài)重構設計

隨著FPGA的廣泛應用, 其實現(xiàn)的功能也越來越多, FPGA 的動態(tài)重構設計就顯得愈發(fā)重要。在分析Xilinx Vertex II Pro系列FPGA配置流程、時序要求的基礎上, 設計了基于CPLD

2017-11-22 07:55:01 1476

1476

1476

1476

FPGA開發(fā)板使用和配置方式

本節(jié)旨在通過給定的工程實例“按鍵開關控制LED”來熟悉Xilinx ISE軟件的基本操作、設計、編譯及仿真流程。同時使用基于Xilinx FPGA的開發(fā)板將該實例進行下載、驗證及調試,完成工程設計的硬件實現(xiàn),熟悉Xilinx FPGA開發(fā)板的使用及配置方式。

2017-11-22 15:31:49 7492

7492

7492

7492Xilinx FPGA電路配置

FPGA配置方式靈活多樣,根據芯片是否能夠自己主動加載配置數(shù)據分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為

2017-11-26 08:12:51 8993

8993

8993

8993

Xilinx品牌FPGA使用的三種證書

JESD204B協(xié)議是目前高速AD,DA通用的協(xié)議。對于基帶使用FPGA用戶來說,Xilinx品牌的FPGA使用更為常見。Xilinx提供了JESD204的IP core,設計起來比較方便。

2018-07-04 10:12:00 4766

4766

4766

4766基于Xilinx FPGA用于ASIC前端驗證的問題總結

FPGA本身是有專門的時鐘cell的,以xilinx FPGA為例,就是primitive庫中的BUFG。

2018-12-22 15:33:59 2175

2175

2175

2175如何使用CPLD和Flas實現(xiàn)FPGA快速配置電路的設計

介紹了采用CPLD和Flash器件對FPGA 實現(xiàn)快速并行配置,并給出了具體的硬件電路設計和關鍵模塊的內部編程思路。

2018-10-24 15:15:49 9

9

9

9如何在小型集群中部署Xilinx FPGA卡

Xilinx FPGA是支持OpenStack的第一個(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺上運行每個演示,并使用OpenStack進行配置和管理。

2018-11-23 06:14:00 4240

4240

4240

4240Xilinx UltraScale+ FPGA和MPSoC互連寬度的使用

從19到32Gb / s的互連寬度正在迅速擴大。

了解Xilinx UltraScale +?FPGA和MPSoC如何直接使用這些互連,以及KCU116和VCU118評估套件如何快速啟動您的設計。

2018-11-22 07:21:00 3677

3677

3677

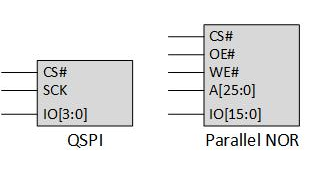

3677使用高速NOR閃存配置FPGA

NOR閃存已作為FPGA(現(xiàn)場可編程門列陣)的配置器件被廣泛部署。其為FPGA帶來的低延遲和高數(shù)據吞吐量特性使得FPGA在工業(yè)、通信和汽車ADAS(高級駕駛輔助系統(tǒng))等應用中得到廣泛采用。汽車場景中

2019-02-21 17:01:30 5339

5339

5339

5339

如何使用高速NOR閃存配置FPGA

NOR閃存已作為FPGA(現(xiàn)場可編程門列陣)的配置器件被廣泛部署。其為FPGA帶來的低延遲和高數(shù)據吞吐量特性使得FPGA在工業(yè)、通信和汽車ADAS(高級駕駛輔助系統(tǒng))等應用中得到廣泛采用。汽車場景中

2019-02-23 10:43:59 3790

3790

3790

3790

xilinx7系列FPGA的7種邏輯代碼配置模式

今天咱們聊聊xilinx7系列FPGA配置的相關內容。總所周知FPGA上電后,其工作的邏輯代碼需要從外部寫入FPGA,FPGA掉電后其邏輯代碼就丟失,因此FPGA可以被無限次的配置不同的邏輯代碼,但

2019-10-20 09:02:00 3778

3778

3778

3778

Xilinx 7系列FPGA可配置邏輯塊的用戶指南

Xilinx7系列FPGA包括四個FPGA系列,它們都是為最低功耗而設計的,以使一個通用設計能夠跨系列擴展以獲得最佳的功率、性能和成本。斯巴達?7系列是7系列產品中密度最低、成本最低的入門級產品

2020-12-09 14:49:00 6

6

6

6Zynq在非JTAG模式下的啟動配置流程

在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實現(xiàn)的。需要注意的是,與傳統(tǒng)的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進行直接啟動配置的,一定要通過 PS 部分來完成。

2022-10-19 09:11:55 2023

2023

2023

2023使用高速NOR閃存配置FPGA

應用中得到廣泛采用。汽車場景中攝像頭系統(tǒng)的快速啟動時間要求就是很好的一個例子——車輛啟動后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設計挑戰(zhàn)。 上電后,FPGA立即加載存儲于NOR器件中的配置比特流。傳輸完成后,FPGA轉換為活動(已配置)狀態(tài)。FP

2023-08-15 13:55:02 1338

1338

1338

1338

羅徹斯特電子攜手AMD/Xilinx可持續(xù)供應Xilinx傳統(tǒng)FPGA產品

羅徹斯特電子攜手AMD/Xilinx,為Xilinx傳統(tǒng)FPGA和相關配置PROM產品提供供貨支持。

2023-11-07 09:04:42 1044

1044

1044

1044適用于 Xilinx? MPSoC 和 FPGA 的可配置多軌PMU TPS650864數(shù)據表

電子發(fā)燒友網站提供《適用于 Xilinx? MPSoC 和 FPGA 的可配置多軌PMU TPS650864數(shù)據表.pdf》資料免費下載

2024-03-06 17:07:17 1

1

1

1Xilinx fpga芯片系列有哪些

Xilinx FPGA芯片擁有多個系列和型號,以滿足不同應用領域的需求。以下是一些主要的Xilinx FPGA芯片系列及其特點。

2024-03-14 16:24:41 5686

5686

5686

5686適用于 Xilinx? MPSoC 和 FPGA的可配置多軌PMU TPS650864數(shù)據表

電子發(fā)燒友網站提供《適用于 Xilinx? MPSoC 和 FPGA的可配置多軌PMU TPS650864數(shù)據表.pdf》資料免費下載

2024-04-01 09:58:42 0

0

0

0采用Xilinx FPGA的AFE79xx SPI啟動指南

電子發(fā)燒友網站提供《采用Xilinx FPGA的AFE79xx SPI啟動指南.pdf》資料免費下載

2024-11-15 15:28:34 0

0

0

0 電子發(fā)燒友App

電子發(fā)燒友App

評論