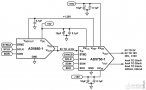

所示電路是一種僅使用兩個(gè)模擬器件的全功能、靈活、可編程的模擬輸出解決方案,它滿足可編程邏輯控制器(PLC)和分布式控制系統(tǒng)(DCS)應(yīng)用的大部分要求。

2013-11-06 10:20:25 2023

2023

可重構(gòu)體系結(jié)構(gòu)分為哪幾種?典型動態(tài)可重構(gòu)系統(tǒng)結(jié)構(gòu)有哪幾種?動態(tài)可重構(gòu)系統(tǒng)有哪些應(yīng)用實(shí)例?

2021-04-28 06:13:00

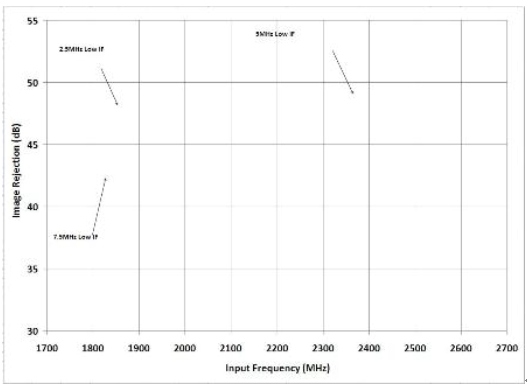

可滿足高性能數(shù)字接收機(jī)動態(tài)性能要求的ADC和射頻器件有哪些?

2021-05-28 06:45:13

吸引力。一些需求能很好地適合這些器件的優(yōu)點(diǎn):保持在某個(gè)產(chǎn)品領(lǐng)域的設(shè)計(jì)前沿,不花費(fèi)很多的設(shè)計(jì)成本,并且不存在會影響任何一個(gè)設(shè)計(jì)進(jìn)入量產(chǎn)的最終用戶需求。這樣的日子可能為時(shí)不遠(yuǎn)了。不過,如果可編程模擬時(shí)代

2019-07-05 07:51:19

什么是可編程模擬器件?如何去實(shí)現(xiàn)相位檢測器?實(shí)現(xiàn)可編程ADC有哪些方法?

2021-04-28 06:50:09

可編程器件的編程原理是什么?指令集對CPU的意義是什么?

2021-11-30 07:39:47

數(shù)據(jù)處理和存儲,以及到儀器儀表、電信和數(shù)字信號處理等。被應(yīng)用的很到位!可編程邏輯器件在設(shè)計(jì)過程中為客戶提供了更大的靈活性,因?yàn)閷τ?b class="flag-6" style="color: red">可編程邏輯器件來說,設(shè)計(jì)反復(fù)只需要簡單地改變編程文件就可以了,而且設(shè)計(jì)改變

2014-04-15 10:02:54

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用.ppt

2017-01-21 20:34:49

)幾個(gè)發(fā)展階段,其中 CPLD/FPGA 屬高密度可編程邏輯器件,CPLD 和 FPGA 是 80年代中后期出現(xiàn)的,其特點(diǎn)是具有用戶可編程的特性。 利用 CPLD/FPGA,電子系統(tǒng)設(shè)計(jì)工程師可以在實(shí)驗(yàn)室

2019-02-26 10:08:08

可編程邏輯器件是如何發(fā)展的?

2021-04-29 06:23:22

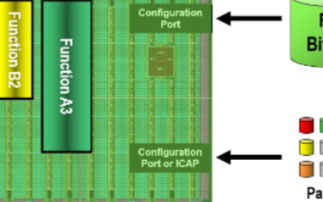

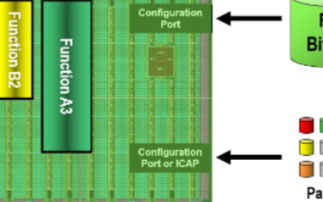

可重構(gòu)設(shè)計(jì)是指利用可重用的軟、硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計(jì)方法。FPGA器件可多次重復(fù)配置邏輯的特性使可重構(gòu)系統(tǒng)成為可能,使系統(tǒng)兼具靈活、便捷、硬件資源可復(fù)用等性能

2011-05-27 10:22:36

CPLD是什么?FPGA包含哪幾類可編程資源呢?FPGA可編程器件和CPLD可編程器件有哪些相同點(diǎn)和不同點(diǎn)?

2021-11-10 07:42:51

`SCH5407-NW是"可編程模擬器件"嗎?`

2013-02-04 16:59:55

可編程模擬器件內(nèi)部結(jié)構(gòu)與基本開發(fā)流程是怎樣的?

2021-04-12 06:38:19

PSoC? 4 是一種混合信號可編程嵌入式系統(tǒng)控制器的可擴(kuò)展、可重構(gòu)的平臺架構(gòu),其核心是 ARM Cortex?-M0 中央處理器(CPU),該系列為嵌入式應(yīng)用提供可編程的平臺。它結(jié)合了靈活的可編程

2013-07-04 09:35:37

批量生產(chǎn)。對有些需要極高性能的應(yīng)用,固定邏輯也可能是最佳的選擇。然而,可編程邏輯器件提供了一些優(yōu)于固定邏輯器件的重要優(yōu)點(diǎn),包括:PLD在設(shè)計(jì)過程中為客戶提供了更大的靈活性,因?yàn)閷τ赑LD來說,設(shè)計(jì)反復(fù)

2009-05-29 11:36:21

本文詳細(xì)介紹了可編程器件、可重編程器件和可重配置器件的基本概念,它對正確選擇器件很有必要。

2021-04-29 06:29:09

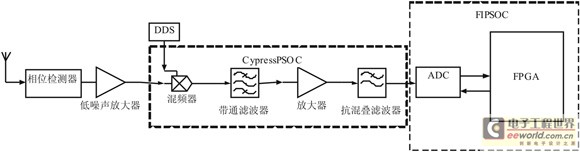

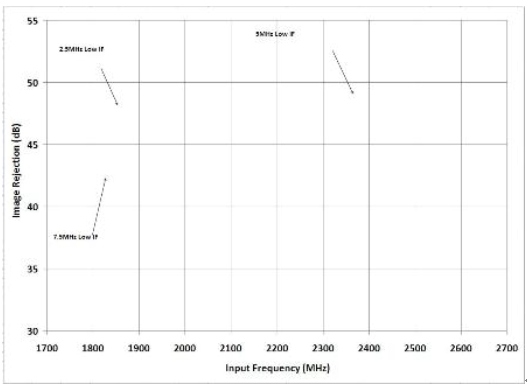

基于IQ解調(diào)器,具有中頻和基帶可變增益以及可編程基帶濾波功能的中頻至基帶接收機(jī)。

2021-05-24 07:00:30

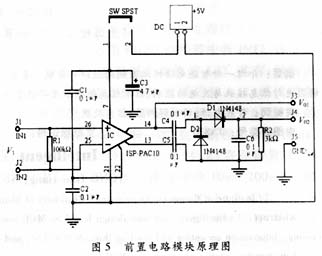

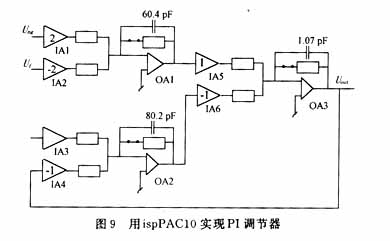

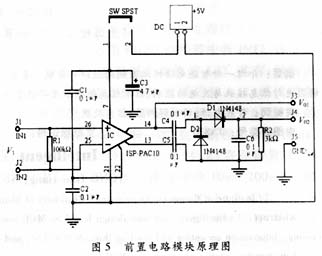

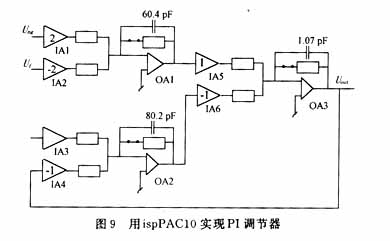

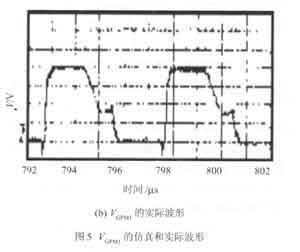

進(jìn)行控制。本文介紹一種方法,介于模擬調(diào)速及數(shù)字調(diào)速二者之間,即采用可編程模擬器件(ispPAC10)實(shí)現(xiàn)模擬調(diào)速系統(tǒng),系統(tǒng)的電路參數(shù)可以通過軟件進(jìn)行調(diào)整,并且可以對建立的系統(tǒng)模型進(jìn)行仿真。采用這種方法對原有的直流調(diào)速器一種CCD相機(jī)的自動變焦系統(tǒng)進(jìn)行改進(jìn),取得了很好的效果。

2019-07-10 07:52:50

1 引 言 在系統(tǒng)可編程模擬電路(In System ProgrammabilityProgrammable Analog Circuits,ispPAC)是可編程模擬器件的一種,其內(nèi)部有可編程

2019-07-02 07:06:27

摘要:介紹了可編程邏輯器件在數(shù)字信號處理系統(tǒng)中的應(yīng)用。并運(yùn)用VHDL語言對采用Lattice公司的ispLSI1032E可編程邏輯器件所構(gòu)成的乘法器的結(jié)構(gòu)、原理及各位加法器的VHDL作了詳細(xì)的描述

2019-06-28 06:14:11

系統(tǒng)運(yùn)行過程中動態(tài)產(chǎn)生。重構(gòu)時(shí)系統(tǒng)可以邊重構(gòu)邊工作。這種重構(gòu)系統(tǒng)設(shè)計(jì)復(fù)雜,但靈活性大,能充分發(fā)揮出硬件運(yùn)算的效率,較適合高速數(shù)字濾波器、演化計(jì)算、定制計(jì)算等方面的應(yīng)用。 從現(xiàn)有的可重構(gòu)系統(tǒng)組織結(jié)構(gòu)看

2011-05-27 10:24:20

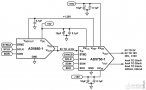

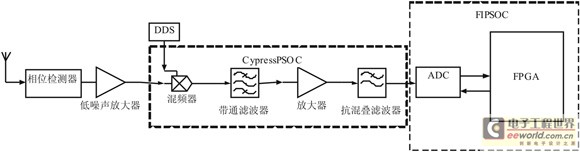

和ASIC電路高速性的解決方案。在筆者所從事的系統(tǒng)設(shè)計(jì)中,當(dāng)模擬器件的一些性能改變但又不能及時(shí)更新調(diào)整后端的數(shù)字基帶處理時(shí),比如濾波器由于工作時(shí)間過長引起的溫漂特性所帶來的影響,此時(shí)就可以用可編程模擬器件替代一部分前端固定模擬器件,進(jìn)而可以實(shí)時(shí)的對FPGA模塊進(jìn)行動態(tài)可重構(gòu)操作,最終達(dá)到系統(tǒng)性能的最優(yōu)化。

2019-07-10 07:56:06

隨著現(xiàn)代通信技術(shù)的迅速發(fā)展,信號的調(diào)制方式向多樣化發(fā)展,解淵技術(shù)也隨之不斷向前發(fā)展。為了對高速大帶寬的信號進(jìn)行實(shí)時(shí)解調(diào),現(xiàn)在很多的解調(diào)關(guān)鍵算法都是在高速硬件上用可編程邏輯器件(FPGA)實(shí)觀,利用

2019-09-19 07:29:47

可編程電源指某些功能或參數(shù)可以通過計(jì)算機(jī)軟件編程進(jìn)行控制的電源。可編程電源的實(shí)現(xiàn)方法有很多種。其中,現(xiàn)場可編程門陣列(Field ProgrammableGate Array,F(xiàn)PGA)具有性能好,規(guī)模大,可重復(fù)編程,開發(fā)投資小等優(yōu)點(diǎn)。

2019-11-04 06:26:07

請問大佬們該如何輸入并實(shí)現(xiàn)自己的可編程模擬電路?

2021-04-12 06:15:29

通過ARM對可編程器件進(jìn)行配置的的設(shè)計(jì)和實(shí)現(xiàn)

2021-04-13 06:20:21

隨著現(xiàn)代通信技術(shù)的迅速發(fā)展,信號的調(diào)制方式向多樣化發(fā)展,解淵技術(shù)也隨之不斷向前發(fā)展。為了對高速大帶寬的信號進(jìn)行實(shí)時(shí)解調(diào),現(xiàn)在很多的解調(diào)關(guān)鍵算法都是在高速硬件上用可編程邏輯器件(FPGA)實(shí)觀,利用

2019-09-05 07:08:02

本文提出的通過微處理器加FPGA結(jié)合串行菊花鏈實(shí)現(xiàn)可重構(gòu)的方式,實(shí)現(xiàn)了動態(tài)可重構(gòu)FPGA結(jié)構(gòu)設(shè)計(jì)的一種應(yīng)用。

2021-05-10 06:22:19

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運(yùn)算情況重組自身資源,實(shí)現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計(jì)算技術(shù)。動態(tài)可重構(gòu)技術(shù)可快速實(shí)現(xiàn)器件的邏輯重建,它的出現(xiàn)為處理大規(guī)模計(jì)算問題提供了一種兼具通用處理器靈活性和ASIC電路高速性的解決方案。

2019-08-13 07:56:00

有哪些,"可編程模擬器件"?

2013-02-04 17:01:33

本文基于現(xiàn)代測控系統(tǒng)的通用化結(jié)構(gòu)特征和可重構(gòu)的現(xiàn)場可編程門陣列FPGA技術(shù)的發(fā)展,提出一種可重構(gòu)測控系統(tǒng)(Reconfigurable Mo—nitoring System,RMS)的設(shè)計(jì)構(gòu)想,并給出其應(yīng)用實(shí)例。

2021-04-30 06:40:43

在系統(tǒng)可編程模擬電路的結(jié)構(gòu)雙二階型濾波器的實(shí)現(xiàn)方法

2021-04-07 06:42:10

如何選擇PLC可編程邏輯器件?

2021-04-27 06:39:03

可重構(gòu)計(jì)算技術(shù)概述隨著20世紀(jì)80年代中期Xilinx公司推出其第一款現(xiàn)場可編程門陣列(FPGA)以來,另一種實(shí)現(xiàn)手段——可重構(gòu)計(jì)算技術(shù)逐漸受到人們的重視,因?yàn)樗軌蛱峁┯布δ艿男屎蛙浖?b class="flag-6" style="color: red">可編程性,隨著可編程器件容量根據(jù)摩爾定律的不斷增大和自動設(shè)計(jì)技術(shù)的發(fā)展,可重構(gòu)技術(shù)正迅速地成熟起來。

2019-07-29 06:26:03

可編程邏輯器件設(shè)計(jì)

(264頁,nlc格式)

2006-03-25 16:41:01 66

66 熟悉常用邏輯器件的分類;了解常用可編程邏輯器件的內(nèi)部結(jié)構(gòu);熟悉可編程邏輯器件的開發(fā)流程;掌握MAX+plusII軟件。重點(diǎn):基于MAX+plusII軟件進(jìn)行PLD設(shè)計(jì)的流程。難點(diǎn):PLD的

2008-12-01 17:36:45 19

19 如何輸入自己的可編程模擬電路摘要:只有為數(shù)不多的公司在模擬IC 中提供拓?fù)?b class="flag-6" style="color: red">可編程性,其中最著名的公司有Zetex 公司、Lattice半導(dǎo)體公司和Anadigm 公司。這些IC 提供可編程連

2009-03-30 16:58:13 34

34 介紹了在系統(tǒng)可編程模擬器件的特點(diǎn),論述用ispPAC 實(shí)現(xiàn)施密特觸發(fā)器、微控制器與傳感器橋的接口電路及高通/ 低通濾波器的原理.關(guān)鍵詞: ispPAC;施密特觸發(fā)器;接口;濾波器

2009-07-11 09:42:08 29

29 可編程邏輯芯片特別是FPGA的快速發(fā)展,使得新的芯片能夠根據(jù)具體應(yīng)用動態(tài)地調(diào)整結(jié)構(gòu)以獲得更好的性能,這類芯片稱為動態(tài)可重構(gòu)FPGA芯片(DRFPGA)。然而,使用這類芯片構(gòu)建的

2010-01-18 08:40:35 10

10 可編程模擬器件原理與開發(fā)作者:趙曙光陳麗萍 殷延瑞 趙明英關(guān)鍵詞:可編程模擬器件,模擬集成電路,ASIC摘要:可編程模擬器件(Programmable Analog Device)是近年來嶄露頭

2010-02-06 17:05:27 44

44 可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

《可編程邏輯器件基礎(chǔ)及應(yīng)用》是一門側(cè)重掌握可編程邏輯器件的基本結(jié)構(gòu)和原理的課程。重點(diǎn)是使學(xué)生掌握基于可編程

2010-03-24 14:22:46 29

29 介紹了在系統(tǒng)可編程技術(shù)的特點(diǎn),以及在系統(tǒng)可編程模擬器件的內(nèi)部結(jié)構(gòu)最后通過一個(gè)有源濾波囂的設(shè)計(jì)實(shí)例介紹了在系統(tǒng)可縞程器件在模擬電路中的應(yīng)用.關(guān)鍵詞模擬電路

2010-04-25 10:08:57 14

14 摘要:從分析在系統(tǒng)可編程模擬電路中的基本單元PAC塊出發(fā).闡述了在系統(tǒng)可編程模擬電路的原理、特點(diǎn)及應(yīng)用。美鍵詞:運(yùn)算跨導(dǎo)放大器 模擬前端

2010-05-08 09:37:20 15

15 摘要:文章介紹了美國Lattice半導(dǎo)體公司推出的可編程模擬器件ispPAC10的內(nèi)部結(jié)構(gòu),并分析研究了用該器件設(shè)計(jì)放大電路,特別是高精度放大電路的方法及措施.關(guān)鍵詞:可編程模

2010-05-18 08:55:30 14

14 摘要:可編程器件已有很久的發(fā)展歷史,除了它體積小、容量大、I/O口豐富、易編程和加密等優(yōu)點(diǎn)外,更突出的特點(diǎn)是其芯片的在系統(tǒng)可編程技術(shù)。也就是說它不但具有可編程和可

2010-07-12 10:04:47 32

32 本文從系統(tǒng)的小型化和可重構(gòu)性出發(fā),利用可編程系統(tǒng)芯片(SOPC)技術(shù),對單芯片可重構(gòu)數(shù)字接收機(jī)的實(shí)現(xiàn)進(jìn)行了研究,給出了具體的實(shí)現(xiàn)方案。在此基礎(chǔ)上,利用系統(tǒng)工具DSP Builde

2010-07-17 17:12:29 12

12 本文以高性能可編程邏輯器件,高精度、低抖動、低畸變可編程時(shí)鐘芯片為核心器件,采用PCI總線技術(shù),設(shè)計(jì)了高速可編程遙感衛(wèi)星數(shù)據(jù)模擬源,在使用windows2000 的高性能服務(wù)器上

2010-08-09 15:27:03 11

11 ?? 摘要:介紹了數(shù)字下變頻器CCl012B,并使用這款芯片構(gòu)建了一個(gè)可編程數(shù)字無線電結(jié)構(gòu)的OFDM[1]傳輸系統(tǒng)的接收機(jī)。 現(xiàn)代

2006-03-11 13:32:55 888

888

在系統(tǒng)可編程模擬器件ispPAC10及其應(yīng)用

介紹lattice半導(dǎo)體公司推出的可編程模擬器件ispPAC10內(nèi)部結(jié)構(gòu)及設(shè)計(jì)應(yīng)用。該控制芯片可方便的完成對信號的放大,衰減及濾波的功能。

2009-03-28 15:11:13 1821

1821

可編程模擬IC之考慮

模擬電路的設(shè)計(jì)與處理器、FPGA和PLD的設(shè)計(jì),在體系結(jié)構(gòu)上有著本質(zhì)的不同。對模擬電路只要你定了電路的拓樸布局和參數(shù),該電路的信號處理功能也就

2009-03-28 16:20:24 1065

1065 基于單片機(jī)的復(fù)雜可編程邏輯器件快速配置方法

基于SRAM(靜態(tài)隨機(jī)存儲器)的可重配置PLD(可編程邏輯器件)的出現(xiàn),為系統(tǒng)設(shè)計(jì)者動態(tài)改變運(yùn)行電路

2009-03-28 16:47:17 1066

1066

動態(tài)可重構(gòu)系統(tǒng)的通信結(jié)構(gòu)分析

動態(tài)可重構(gòu)技術(shù)能在一定控制邏輯的驅(qū)動下,對全部或部分邏輯資源實(shí)現(xiàn)在系統(tǒng)的動態(tài)功能變換和硬

2009-03-29 15:12:52 1330

1330

什么是PLD(可編程邏輯器件)

PLD是可編程邏輯器件(Programable Logic Device)的簡稱,F(xiàn)PGA是現(xiàn)場可編程門陣列(Field Programable Gate Array)

2009-06-20 10:32:32 29733

29733

摘要:介紹了可編程模擬器件的基本原理和開發(fā)流程。列舉了主流器件系列,并說明其核心技術(shù)。展望了可編程模擬器件的發(fā)展前景。

關(guān)鍵詞:

2009-06-20 11:47:34 1593

1593

摘要:ispPAC10是美國Lattice公司最新推出的模擬電路在系統(tǒng)可編程器件,它為電子電路設(shè)計(jì)者進(jìn)行電路設(shè)計(jì)提供了一條有效的新途徑。文中介紹了ispPAC模擬電路在系統(tǒng)可編程器件

2009-06-20 11:49:26 1834

1834

現(xiàn)場可編程門陣列的結(jié)構(gòu)與設(shè)計(jì)

摘要:現(xiàn)場可編程門陣列(FPGA——Field Programmable Gate Array)是上世紀(jì)80年代末發(fā)展起

2009-07-07 10:59:17 1825

1825

基于在系統(tǒng)可編程模擬電路的聲發(fā)射前置電路設(shè)計(jì)

介紹ispPAC在系統(tǒng)可編程模擬電路的技術(shù)特征、工作原理和應(yīng)用,分析了聲發(fā)射檢測系統(tǒng)對前置電

2009-10-13 18:59:31 680

680

用在系統(tǒng)可編程模擬器件實(shí)現(xiàn)雙二階型濾波器

闡述了在系統(tǒng)可編程模擬器件的特點(diǎn)以及用它設(shè)計(jì)雙二階型、連續(xù)時(shí)間低通和帶通濾波器的方法。

2009-12-08 14:57:42 746

746

PAD在接收機(jī)動態(tài)可重構(gòu)結(jié)構(gòu)中的應(yīng)用設(shè)計(jì)

可重構(gòu)結(jié)構(gòu)是一種可以根據(jù)具體運(yùn)算情況重組自身資源,實(shí)現(xiàn)硬件結(jié)構(gòu)自身優(yōu)化、自我生成的計(jì)算技術(shù)。動態(tài)可重構(gòu)技術(shù)可快

2009-12-28 09:15:32 998

998

用可編程模擬器件實(shí)現(xiàn)直流伺服電機(jī)的速度控制

摘 要:介紹了可編程模擬器件在模擬調(diào)速系統(tǒng)中的應(yīng)用,結(jié)合一個(gè)具體實(shí)例,給出了如何用ispPAC10實(shí)現(xiàn)直

2010-01-15 10:55:36 1521

1521

可編程SoC(SoPC),什么是可編程SoC(SoPC)

SOPC ( System on a Programmable Chip,片上可編程系統(tǒng))是以PLD(可編程邏輯器件)取代ASIC(專用集成電路),更

2010-03-26 17:01:35 2726

2726 直接變頻接收機(jī)可實(shí)現(xiàn)多標(biāo)準(zhǔn)/多頻帶運(yùn)行的設(shè)計(jì)方案

現(xiàn)代直接變頻技術(shù)可為現(xiàn)場可編程無線

2010-04-15 11:57:48 3913

3913

1 引言

當(dāng)前在EDA領(lǐng)域,只要具備臺式或筆記本電腦并裝有工具軟件,就可以方便地對可編程ASIC(CPLD/FPGA)進(jìn)行設(shè)計(jì)開發(fā),在系統(tǒng)可編程(ISP)器件為我們提供了這種便利條件。IS

2010-07-15 10:36:02 906

906

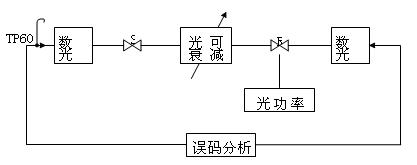

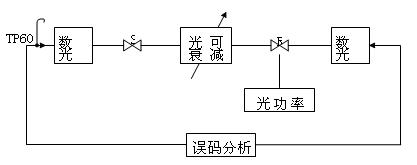

實(shí)驗(yàn) 光接收機(jī)動態(tài)范圍的測試

一 實(shí)驗(yàn)?zāi)康?nbsp; 1 理解光接收機(jī)動態(tài)范圍的概念 2 掌握光接收機(jī)動態(tài)范圍的測試方法

二 實(shí)

2010-08-22 09:26:38 8012

8012

7.1 可編程邏輯器件的基本原理 7.2 可編程邏輯器件的設(shè)計(jì)技術(shù) 7.3 可編程邏輯器件的編程與配置

2012-05-23 10:46:19 142

142 電路是一種僅使用兩個(gè)模擬器件的全功能、靈活、可編程的模擬輸出解決方案,它滿足可編程邏輯控制器(PLC)和分布式控制系統(tǒng)(DCS)應(yīng)用的大部分要求。

2013-01-09 11:06:03 9883

9883

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

2016-12-11 23:38:39 0

0 可編程邏輯器件(書皮)

2022-07-10 14:34:54 0

0 可編程器件緒論

2017-09-19 15:40:11 7

7 基于SRAM的FPGA的問世標(biāo)志著現(xiàn)代可重構(gòu)技術(shù)的開端,并極大地推動了其發(fā)展。可編程FPGA可以根據(jù)不同算法設(shè)計(jì)合理的硬件結(jié)構(gòu),以達(dá)到提高執(zhí)行效率的目的。動態(tài)可重構(gòu)FPGA可以在程序運(yùn)行中動態(tài)完成

2017-11-25 10:20:01 14505

14505

在系統(tǒng)可編程模擬電路(In System ProgrammabilityProgrammable Analog Circuits,ispPAC)是可編程模擬器件的一種,其內(nèi)部有可編程的模擬單元(如

2018-11-14 10:50:00 6328

6328

基于SRAM的FPGA的問世標(biāo)志著現(xiàn)代可重構(gòu)計(jì)算技術(shù)的開端,并極大地推動了其發(fā)展。可重構(gòu)計(jì)算技術(shù)能夠提供硬件的效率和軟件的可編程性,它綜合了微處理器和ASIC的特點(diǎn),空間維和時(shí)間維上均可變,因而

2019-04-18 08:52:00 2281

2281

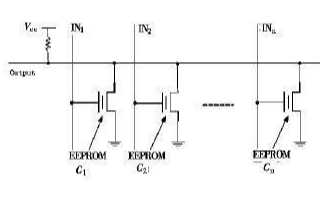

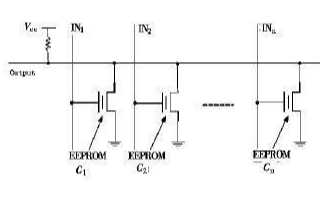

顯然,設(shè)計(jì)基于SRAM編程技術(shù)的CPLD可以很好解決上述應(yīng)用問題。CPLD的設(shè)計(jì)和實(shí)現(xiàn)的關(guān)鍵問題是核心可編程電路結(jié)構(gòu)的實(shí)現(xiàn)。因此,本文主要探討針對CPLD的核心可編程結(jié)構(gòu),如何設(shè)計(jì)具有相似功能且基于SRAM編程技術(shù)的電路結(jié)構(gòu),從而更好滿足動態(tài)重構(gòu)系統(tǒng)中實(shí)現(xiàn)復(fù)雜狀態(tài)機(jī)和譯碼電路的應(yīng)用。

2020-04-25 10:21:00 2449

2449

可編程邏輯器件(PLD)是20世紀(jì)70年代發(fā)展起來的一種新型邏輯器件,是目前數(shù)字系統(tǒng)設(shè)計(jì)的主要硬件基礎(chǔ)。根據(jù)可編程邏輯器件結(jié)構(gòu)、集成度以及編程工藝的不同,它存在以下不同的分類方法。

2020-06-10 17:52:19 30926

30926 可重構(gòu)計(jì)算技術(shù)和自適應(yīng)系統(tǒng)作為最有前途的微處理器體系結(jié)構(gòu)之一引起了人們的極大興趣。可重構(gòu)系統(tǒng)的起源,也被稱為可編程邏輯器件或現(xiàn)場可編程門陣列(fpga),已經(jīng)演變成今天復(fù)雜的片上系統(tǒng)fpga、動態(tài)可重構(gòu)fpga,以及各自適應(yīng)計(jì)算設(shè)備。

2021-03-28 09:40:58 5

5 電子發(fā)燒友網(wǎng)為你提供可編程模擬器件的工作原理和設(shè)計(jì)優(yōu)勢資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-21 08:51:26 5

5 模擬可編程單結(jié)晶體管器件振蕩器設(shè)計(jì)

2021-06-27 10:31:36 28

28 所謂FPGA動態(tài)可重構(gòu)技術(shù),就是要對基于SRAM編程技術(shù)的FPGA實(shí)現(xiàn)全部或部分邏輯資源的動態(tài)功能變換。根據(jù)實(shí)現(xiàn)重構(gòu)的面積不同,動態(tài)可重構(gòu)技術(shù)又可分為全局重構(gòu)和局部重構(gòu)。

2021-07-05 15:41:29 4214

4214

電可編程邏輯器件(Electrically Programmable Logic Device,EPLD)是指采用電信號的可擦可編程邏輯器件。

2022-08-22 18:12:37 2104

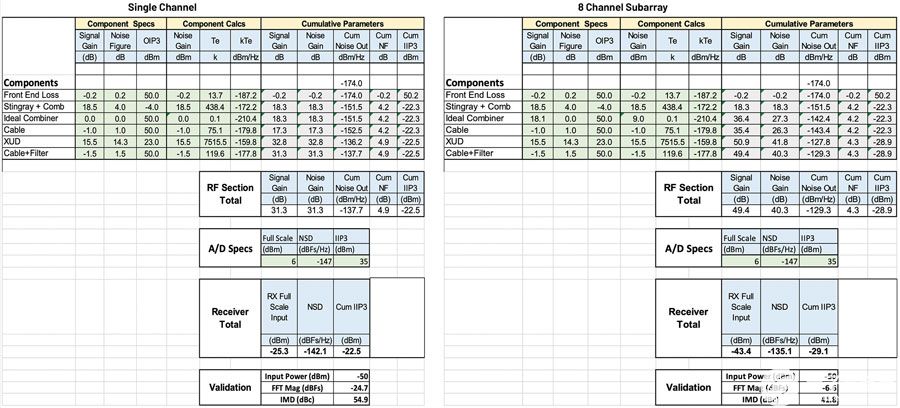

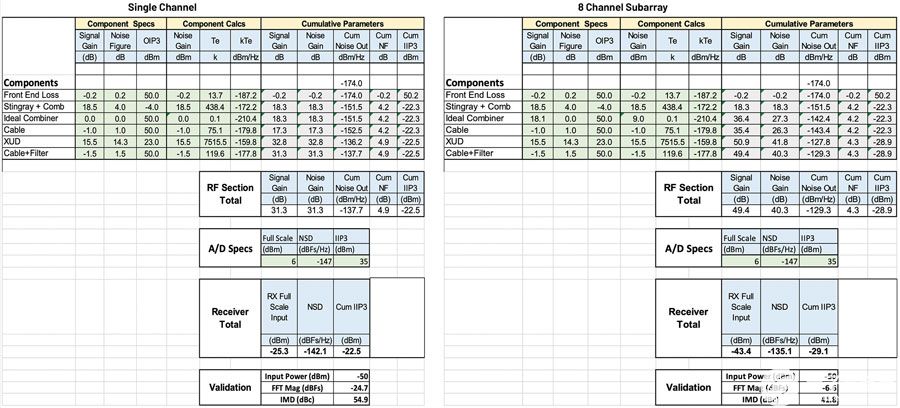

2104 本文介紹了相控陣混合波束成形架構(gòu)中接收機(jī)動態(tài)范圍指標(biāo)的測量與分析的以下比較。商用 32 通道開發(fā)平臺用于通過測量驗(yàn)證分析。回顧了子陣列波束成形的接收機(jī)分析,重點(diǎn)是處理模擬子陣列中信號組合點(diǎn)時(shí)信號增益和噪聲增益之間的差異。

2023-01-16 17:13:01 1886

1886

常見的可編程邏輯器件分為FPGA、EPLD(CPLD)。下面簡單介紹兩類器件的結(jié)構(gòu)和區(qū)別。

2023-03-24 14:18:28 1834

1834

;復(fù)雜 PLD 包括可擦可編程邏輯 (Erasable PLD, EPLD) 器件、復(fù)雜的可編程邏輯 (Complex Programmable Logie Device, CPLD)器件、場可編程

2023-06-06 15:35:59 2881

2881

本文介紹了相控陣混合波束賦形架構(gòu)中接收機(jī)動態(tài)范圍指標(biāo)的測量與分析的比較。測量使用市售32通道開發(fā)平臺進(jìn)行驗(yàn)證分析。本文回顧了子陣列波束賦形接收機(jī)的分析,重點(diǎn)是處理模擬子陣列中信號合并點(diǎn)處的信號增益

2023-06-14 14:22:23 1283

1283

可編程邏輯器件(Programmable Logic Device,PLD)是一類集成電路器件,可以根據(jù)用戶的需求進(jìn)行編程和配置,以實(shí)現(xiàn)特定的邏輯功能。它們具有可編程的邏輯門、時(shí)鐘資源和互連結(jié)構(gòu),可以替代傳統(tǒng)的固定功能邏輯芯片,提供更靈活和可定制的解決方案。

2023-09-14 15:25:55 4351

4351 可編程電源的編程方法和步驟。 ### 1. 可編程電源的基本概念 可編程電源通常由以下幾個(gè)部分組成: - **輸入模塊**:接收交流或直流輸入電源。 - **控制模塊**:接收編程指令,控制電源的輸出。 - **輸出模塊**:根據(jù)控制模塊的指令,提

2024-06-10 15:24:00 3298

3298

電子發(fā)燒友App

電子發(fā)燒友App

評論