摘要:提出了一種基于FPGA的誤碼測(cè)試方案,并簡(jiǎn)要介紹了該方案的設(shè)計(jì)思想。

關(guān)鍵詞:誤碼儀 數(shù)字微波傳輸 ACEX1K系列FPGA

在數(shù)字通信系統(tǒng)的性能測(cè)試中,通常使用誤碼分析儀對(duì)其誤碼性能進(jìn)行測(cè)量。它雖然具有簡(jiǎn)單易用、測(cè)試內(nèi)容豐富、誤碼測(cè)試結(jié)果直觀、準(zhǔn)確等優(yōu)點(diǎn),但是,價(jià)格昂貴、不易與某些系統(tǒng)接口適配,通常需要另加外部輔助長(zhǎng)線驅(qū)動(dòng)電路;此外,誤碼分析儀對(duì)于突發(fā)通信系統(tǒng)的誤碼性能測(cè)試存在先天不足。例如,在對(duì)TDMA系統(tǒng)上行鏈路誤碼性能測(cè)試時(shí),只有通過(guò)外加接口,對(duì)連續(xù)數(shù)據(jù)進(jìn)行數(shù)據(jù)壓擴(kuò),才能為被測(cè)設(shè)備模擬出突發(fā)形式的數(shù)據(jù),從而完成測(cè)試。這給測(cè)試工作帶來(lái)極大的不便。 另一方面,現(xiàn)今的通信系統(tǒng)大量采用FPGA作為系統(tǒng)的核心控制器件。將物理層上的各協(xié)議層的功能集中在FPGA內(nèi)部實(shí)現(xiàn),不僅提高了通信系統(tǒng)的集成,同時(shí)也減少了硬件和軟件設(shè)計(jì)的復(fù)雜度。

基于上述兩方面的考慮,筆者在FPGA內(nèi)部實(shí)現(xiàn)了一個(gè)簡(jiǎn)易的多功能誤碼分析儀。該誤碼儀主要有三方面優(yōu)點(diǎn):一是可以根據(jù)用戶需要,以連續(xù)或突發(fā)的方式產(chǎn)生若干種不同的隨機(jī)序列或固定序列,并據(jù)此測(cè)試數(shù)字通信系統(tǒng)的誤碼性能;二是測(cè)試結(jié)果可以誤碼率或者誤碼數(shù)兩種形式,通過(guò)外圍器件直觀地顯示出來(lái);三是作為被測(cè)系統(tǒng)的一個(gè)嵌入式模塊,便于功能擴(kuò)展及系統(tǒng)調(diào)試。 1 偽隨機(jī)序列(m序列)

許多數(shù)字通信理論的結(jié)論都基于這樣一個(gè)假設(shè):原始的信源信號(hào)為0、1等概并相互獨(dú)立的隨機(jī)數(shù)字序列。同樣,實(shí)際數(shù)字通信系統(tǒng)的設(shè)計(jì),也是基于相同假設(shè)。因此,為使測(cè)試結(jié)果盡可能真實(shí)地反映系統(tǒng)的性能,采用偽隨機(jī)序列(m序列)作為測(cè)試中傳輸?shù)男盘?hào)。

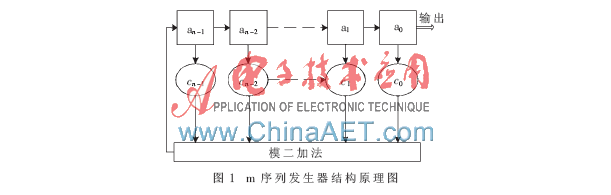

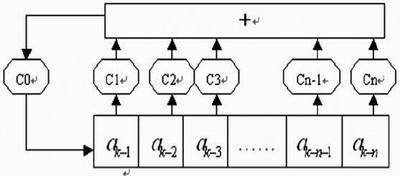

M序列是一種線反饋移位寄存器序列,其原理方框圖如圖1所示。每級(jí)移位寄存器的輸出被反饋系數(shù)Ci加權(quán)(Ci可以取1或0),經(jīng)模2和運(yùn)算再反饋到第一級(jí)。令第一級(jí)的輸入為ak,就有:

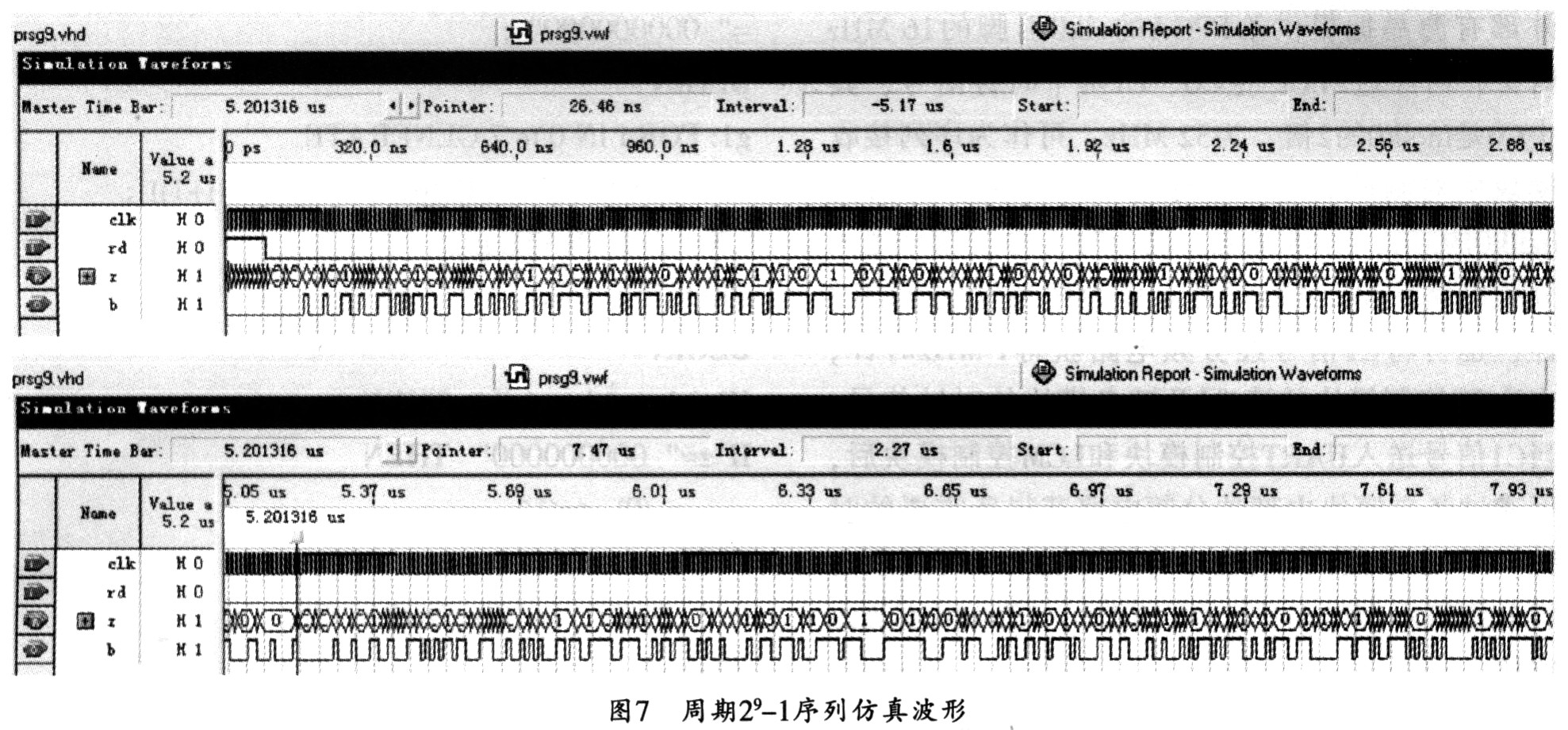

根據(jù)反饋系數(shù)的取值不同,電路可以產(chǎn)生出各種具有不同特性的數(shù)字序列。對(duì)于一定的移位寄存器級(jí)數(shù)r,存在一些特殊的Ci取值,使得輸出序列的周期達(dá)到最長(zhǎng),即為2r-1。這樣的序列被稱為最長(zhǎng)線性反饋移位寄存器序列,即m序列。

2 誤碼儀測(cè)試原理

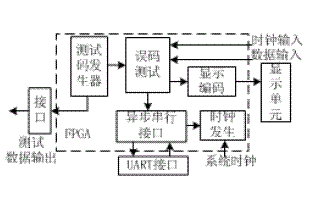

該誤碼儀由發(fā)端模塊和收端模塊兩部分組成。發(fā)端模塊產(chǎn)生連續(xù)或者突發(fā)的比特流,作為通信系統(tǒng)的信源數(shù)據(jù);收端模塊接收通信系統(tǒng)輸出的比特流,并將其與本地產(chǎn)生的、與發(fā)端形式相同的比特流進(jìn)行比較,從而完成誤碼測(cè)試。從邏輯上看,誤碼儀的工作過(guò)程大致可以分成以下幾個(gè)步驟:

(1)發(fā)端模塊產(chǎn)生原始數(shù)據(jù),并使其通過(guò)被測(cè)通信系統(tǒng)構(gòu)成的信道;

(2)收端模塊產(chǎn)生與發(fā)端相同碼型、相同相位的數(shù)據(jù)流;

(3)將收到的數(shù)據(jù)流與收端產(chǎn)生的本地?cái)?shù)據(jù)流逐比特地比較,并進(jìn)行誤碼統(tǒng)計(jì);

(4)根據(jù)誤碼統(tǒng)計(jì)結(jié)果,計(jì)算出相應(yīng)的誤碼率,并輸出誤碼指示。

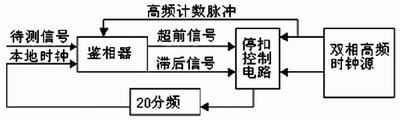

誤碼儀收端模塊所面臨的最主要問(wèn)題是如何準(zhǔn)確地實(shí)現(xiàn)本地產(chǎn)生的m序列與收到的數(shù)據(jù)流同步,即比特對(duì)齊,這是整個(gè)誤碼儀正常工作的前提。為了適應(yīng)各種不同類型的通信系統(tǒng),根據(jù)m序列的性質(zhì),采用隨動(dòng)同步的方法解決這個(gè)問(wèn)題。圖2給出了隨動(dòng)同步的原理框圖。

通過(guò)上述討論知道,周期為2r-1的m序列發(fā)生器由r級(jí)移位寄存器組成。同時(shí),由r個(gè)比特所能組成的所有序列(除全零序列外)都會(huì)在m序列的一個(gè)周期內(nèi)遍歷,且相應(yīng)的前后位置固定。因此,如果兩個(gè)具有相同邏輯結(jié)構(gòu)的m序列發(fā)生器在某一時(shí)刻所有寄存器狀態(tài)完全相同,則由這兩個(gè)m序列發(fā)生器所產(chǎn)生的數(shù)字?jǐn)?shù)據(jù)流保持同步。隨動(dòng)同步就是根據(jù)m序列的這個(gè)性質(zhì)實(shí)現(xiàn)的。

3 誤碼儀邏輯結(jié)構(gòu)

發(fā)端模塊

本誤碼儀的發(fā)端模塊實(shí)質(zhì)上是一個(gè)多功能的序列發(fā)生器。用戶可以通過(guò)相應(yīng)的控制信號(hào),指定其m序列發(fā)生器的線性反饋邏輯。由它產(chǎn)生的數(shù)字?jǐn)?shù)據(jù)流將作為仿真數(shù)據(jù)送出到需要進(jìn)行誤碼性能測(cè)試的數(shù)字通信系統(tǒng)中。

?

收端模塊

收端模塊在邏輯上可以分成兩個(gè)功能子模塊:一是m序列發(fā)生子模塊,二是誤碼統(tǒng)計(jì)子模塊。前者的邏輯功能與發(fā)端模塊相類似,其作用是產(chǎn)生一個(gè)與發(fā)端形式相同并且比特對(duì)齊的本地m序列;后者的作用是將收到的數(shù)據(jù)與本地m序列相比較,同時(shí)統(tǒng)計(jì)誤碼指標(biāo),從而完成對(duì)數(shù)字通信系統(tǒng)的誤碼性能測(cè)試。

在測(cè)試過(guò)程中,接收到的數(shù)字序列被不斷地逐次移入接收數(shù)據(jù)緩沖器中。在接收序列中,任意截取包含r個(gè)連續(xù)比特的片斷(其中r為發(fā)端m序列發(fā)生器的階數(shù)),將其置入本地m序列發(fā)生器的移位寄存器中,作為其初始狀態(tài),并假定此時(shí)收發(fā)雙方已同步在這個(gè)狀態(tài)。此后,本地m序列發(fā)生器與接收數(shù)據(jù)緩沖器同步移位輸出。這樣,只要對(duì)兩個(gè)序列逐位比較,就可以進(jìn)行誤碼統(tǒng)計(jì)了。需要特別注意:如果截取的數(shù)據(jù)片斷中包含誤碼,則據(jù)此得出的收發(fā)雙方已同步的結(jié)論是錯(cuò)誤的。這樣的數(shù)據(jù)片斷將導(dǎo)致整個(gè)誤碼統(tǒng)計(jì)過(guò)程失去意義,不妨稱這種情況為同步。為了消除假同步的影響,需要一種保護(hù)機(jī)制,用以確保收發(fā)雙方的正常同步。 根據(jù)上述思想,筆者設(shè)計(jì)的收端模塊的狀態(tài)機(jī)由4個(gè)狀態(tài)組成,分別為搜索態(tài)(SEARCH)、預(yù)同步態(tài)(PRESYN)、同步態(tài)(SYN)和等待態(tài)(WAIT)。各個(gè)狀態(tài)所完成的功能如下:

搜索態(tài)(SEARCH):在該狀態(tài)下,當(dāng)接收數(shù)據(jù)緩沖器中出現(xiàn)非全零狀態(tài)時(shí),其中的序列被置入收端m序列發(fā)生器的移位寄存器中,同時(shí)進(jìn)入預(yù)同步狀態(tài)。

預(yù)同步態(tài)(PRESYN):在該狀態(tài)下,本地m序列發(fā)生器輸出本地比特流,并使其與收到的數(shù)據(jù)流進(jìn)行逐位比較,同時(shí)進(jìn)行初步的誤碼統(tǒng)計(jì)。如果統(tǒng)計(jì)結(jié)果指示誤碼高于某一事先選定的閾值,則說(shuō)明電路進(jìn)入了假同步,于是需要返回搜索態(tài)重新同步。反之,則可以較大的概率認(rèn)為收發(fā)雙方已經(jīng)同步。反之,則可以較大的概率認(rèn)為收發(fā)雙方已經(jīng)同步,電路進(jìn)入同步態(tài)。

同步態(tài)(SYN):在該狀態(tài)下,電路將進(jìn)行正式的誤碼統(tǒng)計(jì),并且在指定的測(cè)試周期結(jié)束時(shí)進(jìn)入等待狀態(tài),同時(shí)輸出誤碼測(cè)試結(jié)果。

等待態(tài)(WAIT):誤碼測(cè)試尚未啟動(dòng)以及測(cè)試結(jié)束時(shí)所處的狀態(tài)。在該狀態(tài)下誤碼儀等待再一次誤碼測(cè)試的啟動(dòng)信號(hào)。

收端模塊的邏輯狀態(tài)轉(zhuǎn)移圖見(jiàn)圖3。

4 測(cè)試結(jié)果的輸出

通常,誤碼測(cè)試結(jié)果可以以誤碼數(shù)和誤碼率兩種形式輸出。大多數(shù)取代傳統(tǒng)誤碼分析儀的其它誤碼測(cè)試方案均采用易于實(shí)現(xiàn)的誤碼數(shù)形式輸出測(cè)試結(jié)果,但種方式受到輸出位數(shù)的限制而無(wú)法適應(yīng)高誤碼率或需要進(jìn)行長(zhǎng)時(shí)間統(tǒng)計(jì)的測(cè)試環(huán)境。但是,誤碼率的計(jì)算又常常需要進(jìn)行除法運(yùn)算,而在FPGA或其它可編程邏輯器件中實(shí)現(xiàn)除法運(yùn)算通常要消耗掉大量的邏輯資源,有時(shí)甚至超過(guò)了實(shí)現(xiàn)主要功能所需的資源。 事實(shí)上,在一般的工程實(shí)踐中,人們通常關(guān)心的只是誤碼率的量級(jí),因而誤碼儀也就沒(méi)有必要準(zhǔn)確地計(jì)算出實(shí)際的誤碼率。根據(jù)這一想法,該誤碼儀采用某種近似的實(shí)際的誤碼率。根據(jù)這一想法,該誤碼儀采用某種近似的估計(jì)算法,避免了意義不大的除法運(yùn)算,而以較少的資源消耗實(shí)現(xiàn)了對(duì)誤碼率的估計(jì)。下面簡(jiǎn)要介紹該估計(jì)算法。

在誤碼測(cè)試邏輯中,接收到的總比特?cái)?shù)與誤碼個(gè)數(shù)均以二進(jìn)制方式存儲(chǔ)在內(nèi)部的邏輯向量中。它們最高非0比特所處的位置之差實(shí)際上反映了誤碼率的指標(biāo)不。這樣只要根據(jù)這個(gè)差值就可以大致估計(jì)出誤碼率,同時(shí)復(fù)雜的除法運(yùn)算也被簡(jiǎn)單的減法運(yùn)算所代替。

例如:當(dāng)收到總特?cái)?shù)為“00……01110110110”誤碼計(jì)數(shù)值為“00……0110”時(shí),總比特?cái)?shù)的最高非0位為第10位,誤碼計(jì)數(shù)值為第3位,差值為7,誤碼率近似為1/2 7,即7.8×10 -3,與實(shí)際誤碼率6.3×10 -3相當(dāng)。

采用近似算法可能造成的最大系統(tǒng)誤差是輸出誤碼率的50%.但是,在通信系統(tǒng)的誤碼性能統(tǒng)計(jì)中,這樣的誤差并不會(huì)影響對(duì)系統(tǒng)誤碼率數(shù)量級(jí)的判斷。因此,作為調(diào)試使用的簡(jiǎn)易誤碼性能的測(cè)試算法是完全可行的。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論