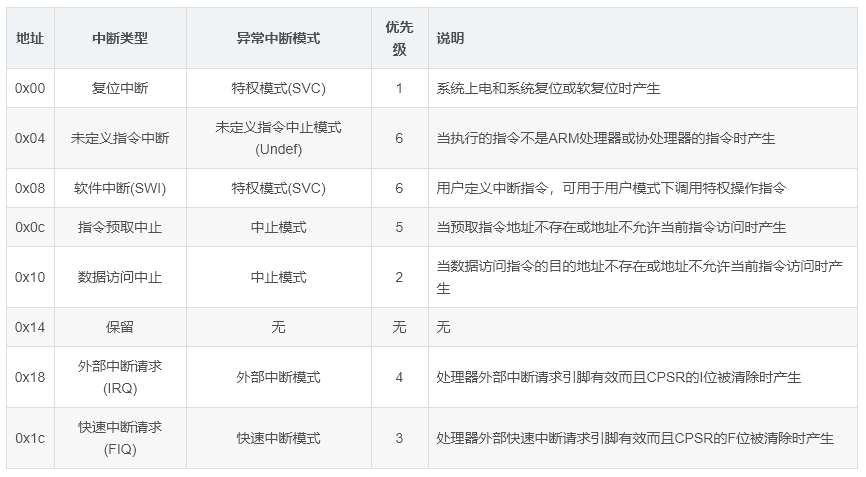

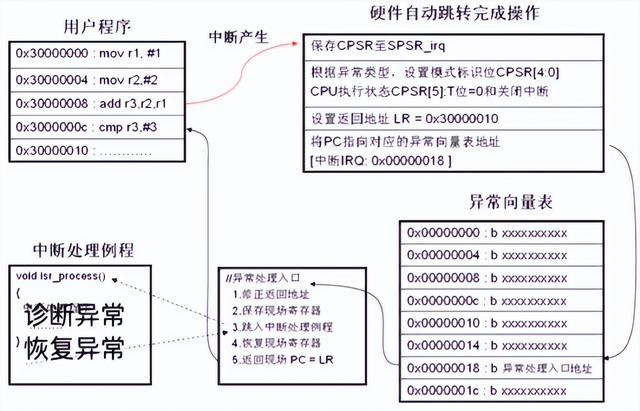

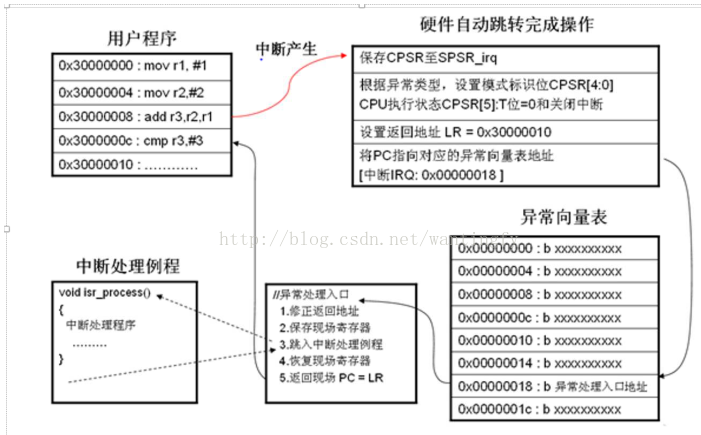

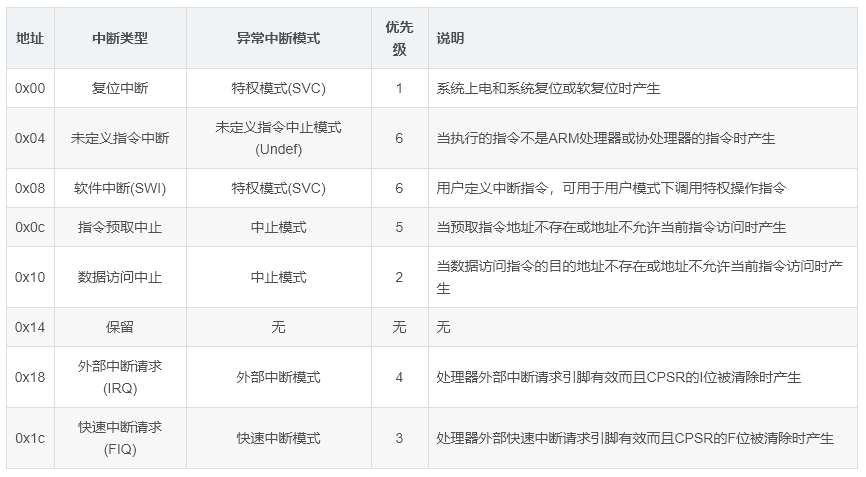

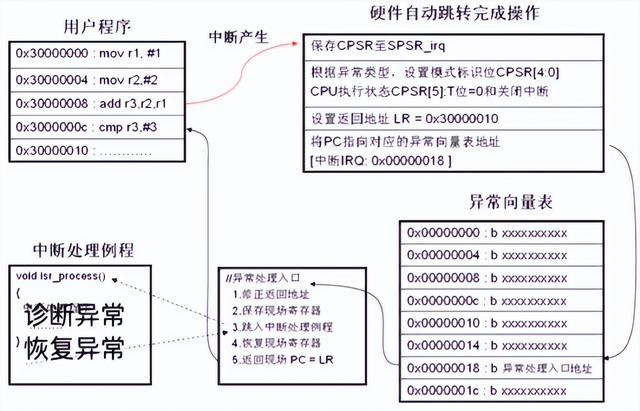

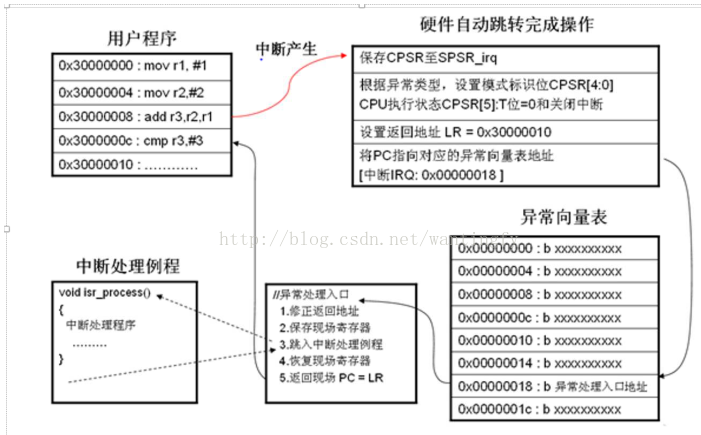

基礎知識 ARM體系架構的處理器中通常將低地址32字節作為中斷向量表,當中斷產生時會執行以下操作: ① 保存處理器當前狀態,設置中斷屏蔽位和各條件標志位 ② 設置當前程序狀態寄存器CPSR中相應位

2020-11-21 11:10:27 3188

3188

01、ARM中斷體系 ① ARM體系中,在存儲地址的低位,固化了一個32字節的硬件中斷向量表。 ② 異常中斷發生時,程序計數器PC所指的位置不同,異常中斷就不同。中斷結束后,中斷不同,返回地址也

2020-11-27 11:01:11 7714

7714

ARM處理器是一種流行的處理器架構,用于許多現代移動設備和嵌入式系統中。中斷和異常是ARM處理器中的兩個重要概念,它們是處理器中斷程序執行的關鍵機制。

2023-09-05 15:45:30 3002

3002

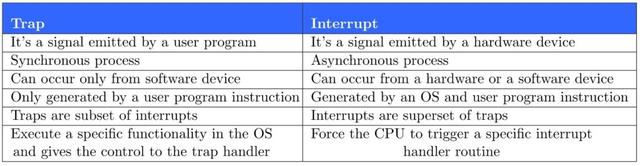

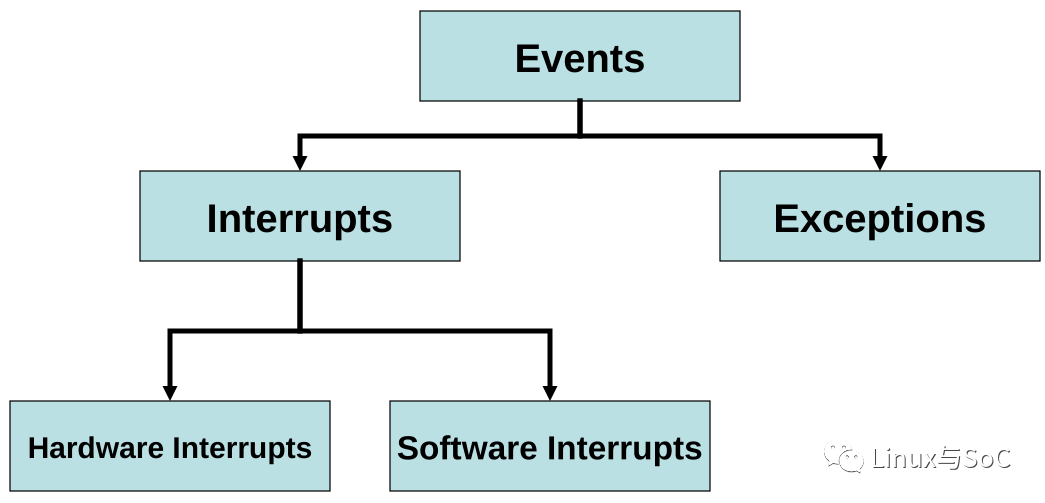

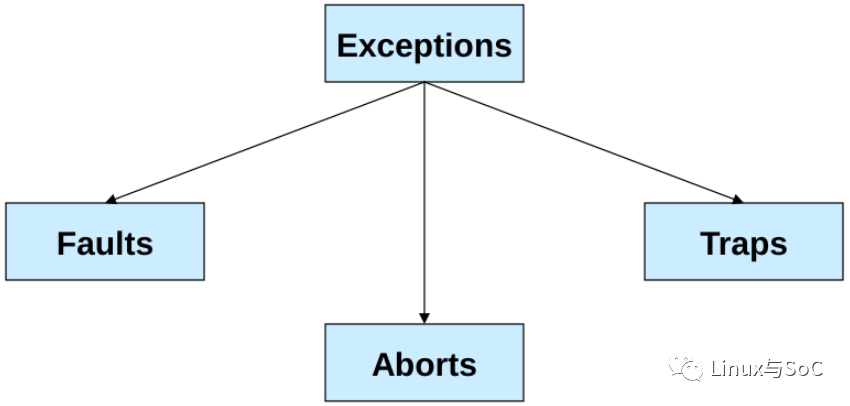

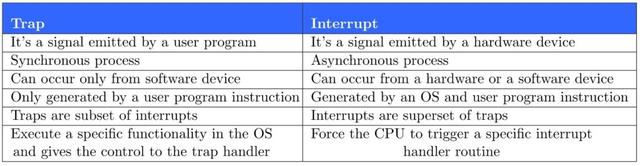

異常和中斷會暫停程序以響應硬件或軟件中的意外事件。中斷是異步事件,異常是同步事件,但是中斷和異常之間的區別也取決于具體情況。

2023-09-14 15:20:18 3346

3346

M0內核支持的資源Cortex-M0處理器最多支持32個外部中斷(通常稱作IRQ),還有一個被稱作不可屏蔽中斷的特殊中斷。中斷事件的異常處理通常被稱作中斷服務程序(ISR)。除此之外,M0處理器還

2021-12-21 06:50:48

中斷和異常的區別中斷是指系統停止當前正在運行的程序轉到其他的服務,可能是程序接收了比自身高優先級的請求,或者是人為設置中斷,中斷是屬于正常現象。異常是指由于CPU本身故障、程序故障或者請求服務等引

2021-08-13 08:54:59

學習單片機一貫的套路,搞完時鐘和GPIO就要折騰中斷了。1. 中斷和異常的區別1.1 中斷是指系統停止當前正在運行的程序轉而其他服務,可能是程序接收了比自身高優先級的請求,或者是人為設置中斷,中斷

2021-08-13 08:14:41

stm32學習筆記(2)中斷和異常的區別外中斷——就是我們指的中斷——是指由于外部設備事件所引起的中斷,如通常的磁盤中斷、打印機中斷等;內中斷——就是異常——是指由于 CPU 內部事件所引起的中斷

2022-01-07 08:05:11

中斷向量表|異常處理過程中斷隨機產生之后,怎么跳轉到中斷的處理程序中去(中斷向量表)SWI軟中斷指令:模擬CPU外面的某個硬件的管腳產生中斷信號4. 軟中斷處理程序實例原作者:西二旗指南

2022-05-05 10:16:31

在ARM處理器中,我們常常使用SWI指令來產生一個軟中斷。軟中斷指令SWI指令中包含了一個24位的立即數,這個立即數指示了用戶請求的特定的SWI功能,即這個立即數表示的是SWI指令所想要觸發中斷

2017-01-10 15:09:37

ARM處理器或者是系統中的協處理器認為當前指令未定義時,產生未定義的指令異常中斷。可以通過該異常中斷機制仿真浮點向量運算。軟中斷(software interrupt):這是一個由用戶定義的中斷

2020-08-28 08:09:17

類似的看作中斷,本質上兩者還是有區別的。異常/中斷是硬件和軟件進行異步工作的一種方式。經典ARM微處理器發生異常時,ARM微處理器會自動調用預先寫好的異常處理程序。為...

2021-07-16 07:04:57

NXP的ARM7帶ucos中硬中斷與軟中斷響應詳細分析一.帶UCOS系統的軟中斷響應過程 11.第一步: 22.第二步: 2二.帶UCOS系統的硬中斷響應過程 6下面的主要分析LPC系列ARM7

2011-12-02 17:32:17

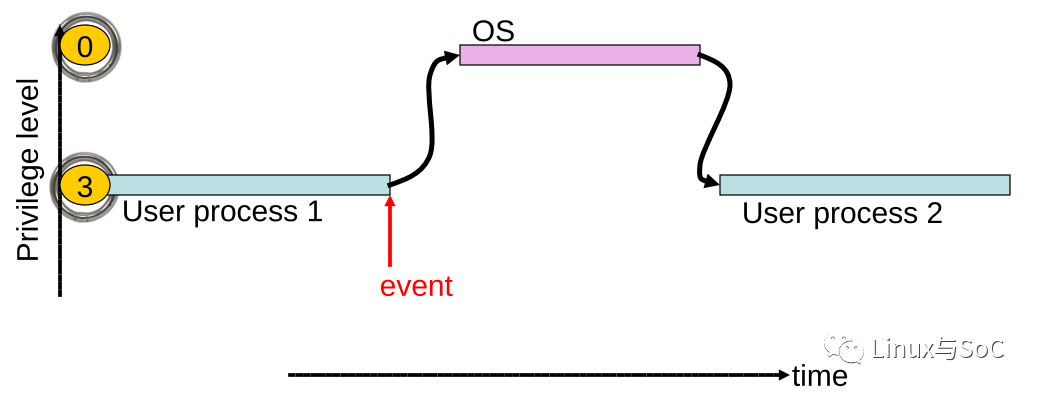

異常是能夠引起程序流偏離正常流程的事件,當異常發生時,正在執行的程序就會被掛起,處理器轉而執行一塊與該事件相關的代碼(異常處理)。事件可以是外部輸入,也可以是內部產生的,外部產生的事件通常被稱作中斷

2021-10-11 10:15:51

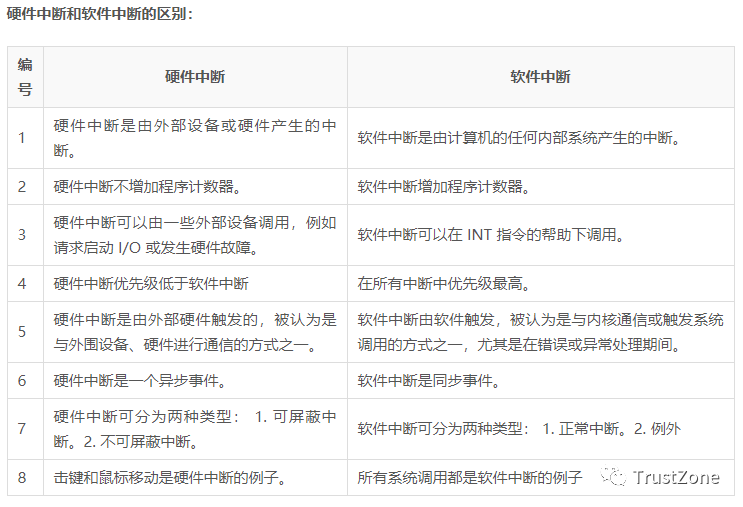

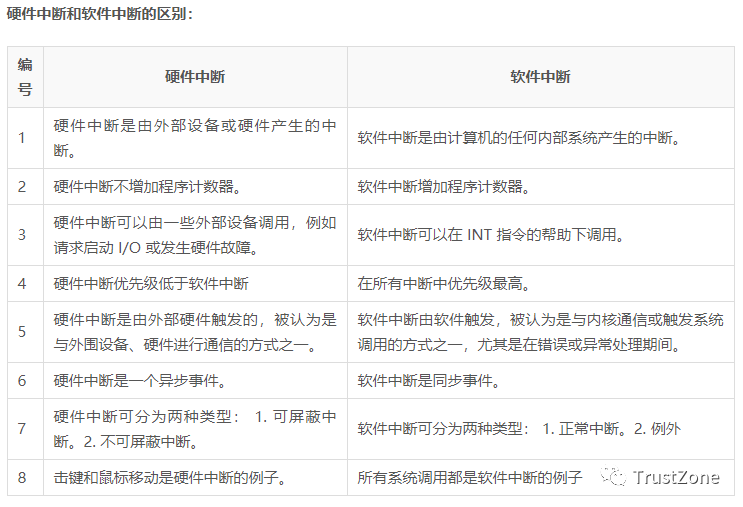

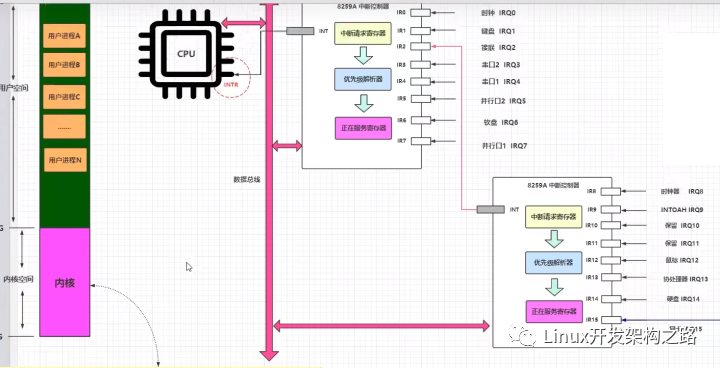

同步中斷,是指CPU內部出現的中斷,即在CPU執行特定指令時出現的非法情況,因此只有在一條指令執行后才會發出中斷,不可能在指令執行期間發生異常。硬中斷:是由外設引發的,中斷號是由中斷控制器提供的,是可屏蔽的。軟中斷:是執行中斷指令產生的,中斷號由指令直接指出,無需使用中斷控制器,且不可屏

2022-01-10 07:26:39

。高效的處理能夠極大的提升系統的性能。ARM處理器一共有7種可以暫停指令的執行序列的異常。主要分為三個部分:點擊這里

2021-12-14 09:23:07

uCOS-III(15)中斷管理異常與中斷中斷延遲中斷延遲發步代碼中斷延遲發布任務初始化異常與中斷異常是指任何打斷處理器正常執行,并迫使處理器進入一個由有特權的特殊指令執行的事件。異常通常可以分為

2022-02-18 07:45:44

以 ARM7TDMI處理器為例,詳細介紹 ARM內核的三種中斷:常規中斷、快中斷和軟件中斷;結合應用,給出優化的中斷處理程序的ARM指令代碼,對電子設計人員有較大的參考價值。

2009-04-09 10:01:19 18

18 通過基于立宇泰S3C44B0X 開發板的BSP 移植調試,闡述了VxWorks 的異常中斷處理機制,實現了VxWorks 基于S3C44B0X 處理器的中斷處理,并以外部中斷EINT4/5/6/7為例分析了中斷的響應過程,

2009-09-03 11:25:12 17

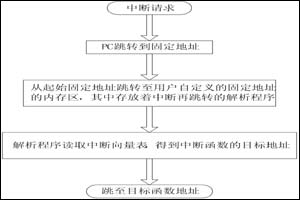

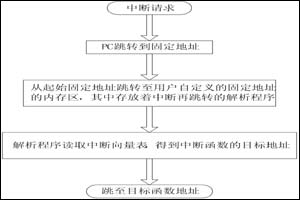

17 摘要:本文首先簡要概述了ARM處理器的異常中斷種類、響應和返回過程;然后重點討論了中斷解析程序的原理和實現,并分別給出了普通中斷和向量中斷的處理示例流程圖和詳細

2006-03-11 12:18:54 1191

1191

s3c2410中斷程序在此要注意的是區別中斷向量表和異常向量表。中斷發生后總是從IRQ 或者FIQ 異常

2008-09-11 18:49:40 2522

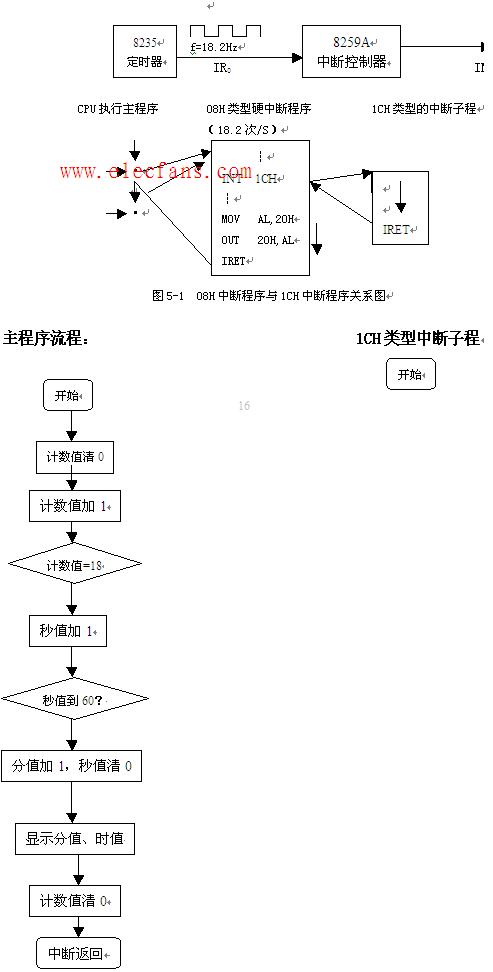

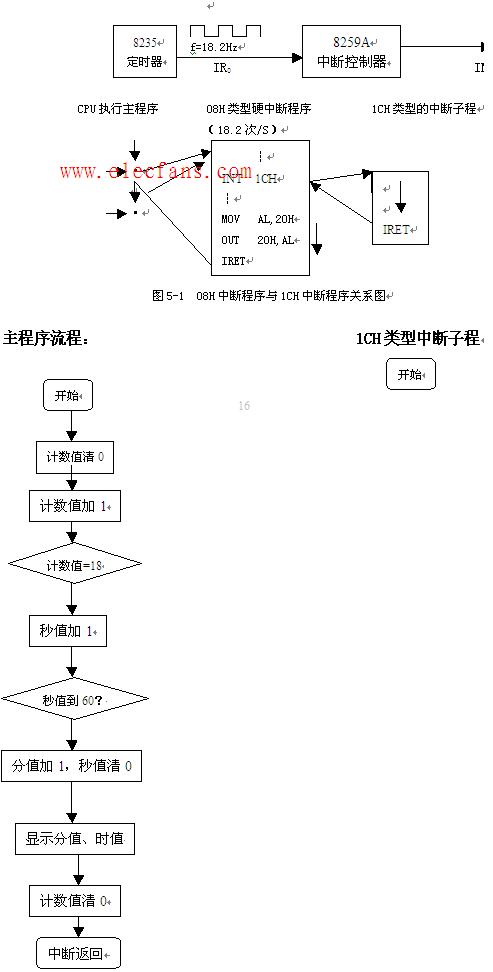

2522 實 驗 五 軟中斷程序設計

一、實驗目的 通過對軟中斷程序的編寫和調試,掌握IBM-PC系列機的軟中斷程序設計方法

2008-09-28 23:26:49 3066

3066

微處理器中斷發生器電路

2009-02-12 07:51:34 550

550

Linux 2.6 中斷處理原理簡介

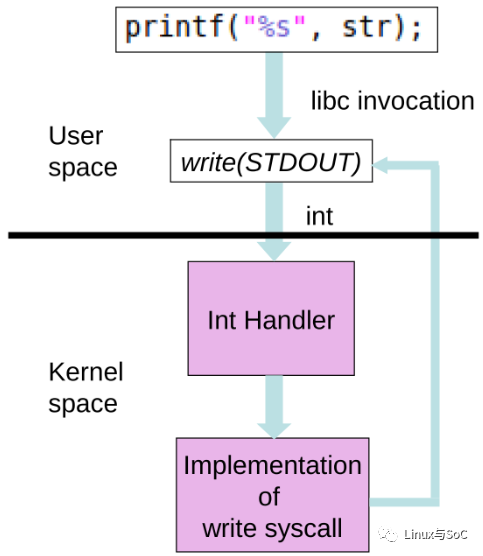

中斷描述符表(Interrupt Descriptor Table,IDT)是一個系統表,它與每一個中斷或異常向量相聯系,每一個向量在表中存放的是相應的中斷或

2010-02-05 10:52:28 940

940 對ARM處理器的普通中斷處理、任務切換中斷處理、可重人中斷處理和基于優先級的可重人性中斷處理的上下文保存技術進行分析與總結。為保證理論的正確性,核心的程序代碼都經過了

2011-07-06 12:08:09 4539

4539

1、中斷的種類 由CPU外部產生的中斷(interrupt) 由專設指令(如INT)產生的陷阱 (trap)由CPU本身在執行指令時產生的異常(exception) 2、X86 CPU對中斷的硬件支持 引入了門(gate) 門的

2011-11-03 22:36:32 54

54 異常主要是從處理器被動接受的角度出發的一種描述,指意外操作引起的異常。而中斷則帶有向處理器主動申請的意味。但這兩種情況具有一定的共性,都是請求處理器打斷正常的程序

2011-12-06 16:45:46 49

49 WindowsCE異常和中斷服務程序,中斷和異常都是異步發生的事件,當該事件發生,系統將停止目前正在執行的代碼轉而執行事件響應的服務程序。

2012-01-04 15:37:34 1987

1987 當CPU(中央處理器)執行一條現行指令的時候,如果外設向CPU發出中斷請求,那么CPU在滿足響應的情況下,將發出中斷響應信號,與此同時關閉中斷,表示CPU不在受理另外一個設備的中斷。

2015-10-29 14:23:33 0

0 微機原理--中斷和異常

2016-12-12 22:07:22 0

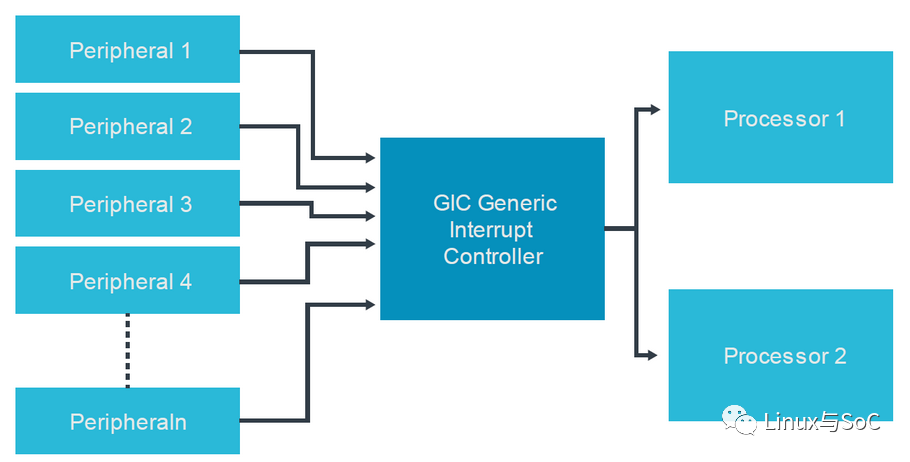

0 在現今SOC設計中,當周邊裝置(PeripheralIP)想要和中央處理器(CPU)溝通時,最常使用的機制是透過中斷(Interrupt)。周邊裝置可觸發中斷給中央處理器,當中央處理器接收到中斷

2017-09-15 09:16:38 11

11 ARM體系中的異常中斷及其應用

2017-09-22 16:51:52 4

4 )。 注意在ARM文檔中,使用術語Exception來描述異常。Exception主要是從處理器被動接受異常的角度出發,而Interrup

2017-10-18 13:29:56 1

1 所示。 圖11.63 SWI指令的編碼格式 軟中斷指令SWI(Software Interrupt)用于使處理器產生軟中斷異常

2017-10-19 09:32:58 0

0 中斷指令產生軟中斷,處理器進入管理模式 BKPT斷點中斷指令處理器產生軟件斷點 9.5.1 軟中斷指令SWI 1.指令編碼格式 軟件中斷指令SWI(Software Interrupt)用于產生軟中斷

2017-10-19 10:11:32 1

1 情況下,軟中斷和信號有些類似,同時,軟中斷又是和硬中斷相對應的,硬中斷是外部設備對CPU的中斷,軟中斷通常是硬中斷服務程序對內核的中斷,信號則是由內核(或其他進程)對某個進程的中斷(《Linux內核源代碼情景分析》第三章)。

2017-11-02 11:01:58 0

0 服務例程,以便對引起中斷的原因進行尋址。中斷可能來自下列三個地方之一: ?硬件 – 直接連接處理器的電子信號 ?軟件 – 處理器加載的軟件說明 ?異常情況 – 發生錯誤或異常事件時處理器出現的異常情況。

2017-11-18 09:17:01 14443

14443

當異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下一條指令處繼續執行。在進入異常中斷處理程序時,要保存被中斷程序的執行線程。從中斷處理程序退出時要恢復被中斷程序的執行現場。

2017-12-16 08:57:03 5404

5404 本文介紹A了RM S3C4510B系統 的 異常中斷 機制,包括異常中斷的分類,響應與返回;中斷處理程序的安裝與調用;SWI,IRQ中斷的實例與關鍵代碼。隨著人們對于電子產品的要求越來越高,以

2018-02-03 05:32:01 2138

2138

異常中斷通常用在下面幾種情況: 1、系統加電時 2、系統復位時 3、跳轉到復位中斷向量處執行,稱為軟復位 未定義的指令 當ARM處理器或者是系統中協處理器認為當前指令未定義時,產生未定義指令異常中斷。可以通過該異常中斷機制仿真浮點向量運算。

2018-04-05 10:51:00 1649

1649 SH-3的中斷處理方式與一般處理器不同,沒有固定的中斷向量表,比較靈括,用戶可以在存儲器中建立上述僅是對P09702的基本應用。通過該文介紹的方法,并結合SSDl303的指令集,讀者將能夠對P09702應用自如。一個處理異常事件(Exeeplaonevents)的程序結構,作為中斷向量表。

2018-04-08 11:25:02 1489

1489

在一些嵌入式處理器系統中,這個問題較易解決。因為嵌入式處理器系統很清楚在當前系統中存在多少個PCI設備,這些PCI設備使用了哪些中斷資源。在多數嵌入式處理器系統中,PCI設備的數量小于中斷控制器提供的外部中斷請求引腳數,而且在嵌入式系統中,多數PCI設備僅使用INTA#信號提交中斷請求。

2018-04-11 09:12:35 7156

7156 在處理器中,所謂中斷,是一個過程,即CPU在正在執行程序過程中,遇到外部/內部緊急事件需要處理,暫時中止當前程序執行轉而去

2018-06-27 10:06:00 7910

7910

任何一種中斷模式都可以通過手動的修改cpsr的值來進入。但是User和System模式是僅有的2個不能由相應中斷進入的模式,換句話說,我們必須要通過手動修改cpsr才能進入。

2018-06-25 10:49:01 5085

5085

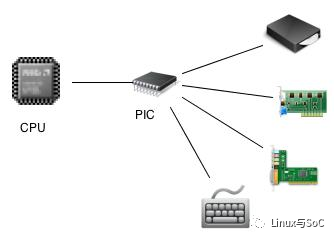

從本質上來講,中斷是一種電信號,當設備有某種事件發生時,它就會產生中斷,通過總線把電信號發送給中斷控制器。

2018-10-30 14:34:52 6131

6131

1. 在匯編中保存現場,然后調用C語言編寫的中斷處理程序,任務處理完成之后,再返回到匯編中恢復現場,并返回到斷點。其中C語言編寫的中斷處理程序,通過switch語句對INTOFFSET進行判斷,然后散轉執行對應的服務函數。

2018-11-15 16:17:02 1228

1228 在STM32處理器中有43個可屏蔽中斷通道(不包含 16個 Cortex?-M3的中斷線)。共設置了16個可編程的優先等級(使用了 4位中斷優先級);它的嵌套向量中斷控制器(NVIC)和處理器核

2018-11-16 15:35:40 8990

8990

從本質上來講,中斷是一種電信號,當設備有某種事件發生時,它就會產生中斷,通過總線把電信號發送給中斷控制器。

2019-01-17 09:38:38 11625

11625

從本質上來講,中斷是一種電信號,當設備有某種事件發生時,它就會產生中斷,通過總線把電信號發送給中斷控制器。

2019-05-05 11:48:44 18402

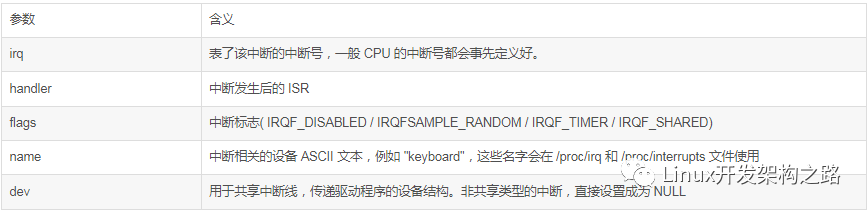

18402 在硬件上,中斷源可以通過中斷控制器向CPU提交中斷,進而引發中斷處理程序的執行,不過這種硬件中斷體系每一種CPU都不一樣,而Linux作為操作系統,需要同時支持這些中斷體系,如此一來,Linux中就

2019-05-08 13:49:02 917

917 在前一個專題里曾分析過所有IRQ中斷處理流程,經過SAVE_ALL保存硬件環境后,都會進入do_IRQ()進行處理,今天接著分析do_IRQ()處理的相關東西.分為兩部中斷處理程序與軟中斷兩個大的部份進行介紹.

2019-05-10 10:57:43 3126

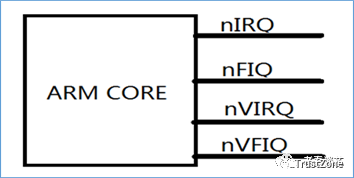

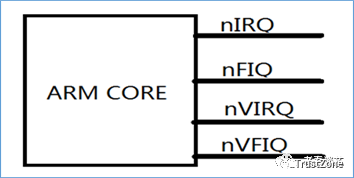

3126 快速中斷請求(FIQ)要求具有最高優先級。如果分配給FIQ 的請求多于1 個,VIC將中斷請求“相或”后向ARM 處理器產生FIQ 信號。當只有一個中斷被分配為FIQ 時可實現最短的FIQ 等待時間

2019-09-27 17:26:00 14

14 當ARM異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理程序處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下條指令處執 行。在進入異常中斷處理程序時,要保存被中斷程序的執行現場,從異常中斷處理程序退出時,要恢復被中斷程序的執行現場。

2020-06-17 10:05:12 9203

9203 外部中斷請求(IRQ) 當處理器的外部中斷請求引腳有效,而且CPSR的寄存器的I控制位被清除時,處理器產生外部中斷請求異常中斷。系統中個外設通過該異常中斷請求處理服務。

2020-08-27 14:21:29 3119

3119 opensbi下的riscv64裸機編程2(中斷與異常) 1.本文說明 2.riscv特權模式下的異常 2.1 CSPs 2.2 異常開關的寄存器 2.3 與中斷相關的指令 3.中斷測試 3.1

2021-01-07 10:30:37 3641

3641 Intc外設的Device Tree 4. 擴展MIO中斷 4.1. GPIO中斷控制器 4.2. 外設使用GPIO中斷控制器5. 檢查Linux中斷信息 01 MPSoC的中斷處理介紹 MPSoC是帶

2021-05-07 15:34:15 4690

4690 PCI總線的中斷機制 PCI總線使用INTA#、INTB#、INTC#和INTD#信號向處理器發出中斷請求。這些中斷請求信號為低電平有效,并與處理器的中斷控制器連接。在PCI體系結構中,這些中斷信號

2021-07-18 10:10:40 3593

3593 。 STM32中斷類型: 系統異常:內核水平 10個 外部中斷:外設水平 60個 STM32關全局中斷有多種方法,分別操作PRIMASK、FAULTMASK和BASEPRI寄存器。 第一種方法,:操作

2021-07-22 10:52:54 29445

29445 異常是能夠引起程序流偏離正常流程的事件,當異常發生時,正在執行的程序就會被掛起,處理器轉而執行一塊與該事件相關的代碼(異常處理)。事件可以是外部輸入,也可以是內部產生的,外部產生的事件通常被稱作中斷

2021-10-12 17:14:18 5881

5881 51單片機各個引腳功能IO口引腳:中斷系統的主要功能:處理隨機突發事件中斷系統結構:什么是中斷系統:數據的輸入/輸出傳送方式:中斷傳送方式特點:51系統允許的5個中斷源:51單片機中斷系統內部結構

2021-11-22 12:51:07 14

14 這里寫目錄標題先驗知識回顧控制寄存器回顧1、8086中斷類型1、外部可屏蔽中斷2、外部不可屏蔽中斷3、除法錯中斷4、單步中斷5、斷點中斷6、溢出中斷7、軟中斷2、8086中斷向量表3、8086中斷

2021-11-24 16:51:09 16

16 以STM32l0xx為例多外部中斷共用中斷源時,要通過判斷中斷請求狀態來分配中斷stm32l0xx的寄存器如下單個中斷時處理如下多個中斷時處理如下通過__HAL_GPIO_EXTI_GET_IT

2021-11-24 16:51:10 4

4 一、基礎知識中斷源:引起中斷的原因中斷過程-中斷請求-中斷響應-中斷服務程序-中斷返回初始化步驟:-設置觸發方式-開中斷EA=1,ET0=1-優先級PT0=1二、單片機中斷處理過程有效的中斷

2021-11-24 17:21:05 13

13 中斷基礎知識異常就是中斷,中斷就是異常。但是習慣上稱系統產生的為異常,外部產生的為中斷,即系統異常和外部中斷。談到中斷,必須知道NVIC。NVIC 是嵌套向量中斷控制器,控制著整個芯片中斷相關的功能

2021-12-04 17:06:09 7

7 STM32中斷應用中斷知識介紹STM32 中斷應用概覽異常NVIC優先級定義中斷知識介紹STM32 中斷應用概覽STM32 中斷非常強大,每個外設都可以產生中斷。異常F103 在內核水平上搭載了一個

2021-12-04 17:21:05 9

9 中斷介紹中斷就是當CPU 執行程序時,由于發生了某種隨機的事件(外部或內部),引起CPU 暫時中斷正在運行的程序,轉去執行一段特殊的服務程序(中斷服務子程序或中斷處理程序),以處理該事件,該事件處理

2021-12-04 19:21:06 1

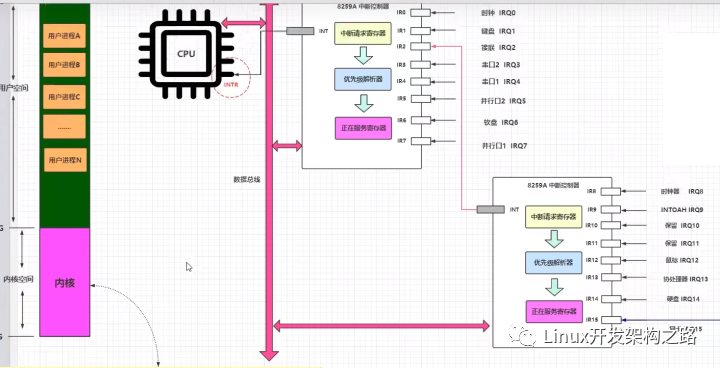

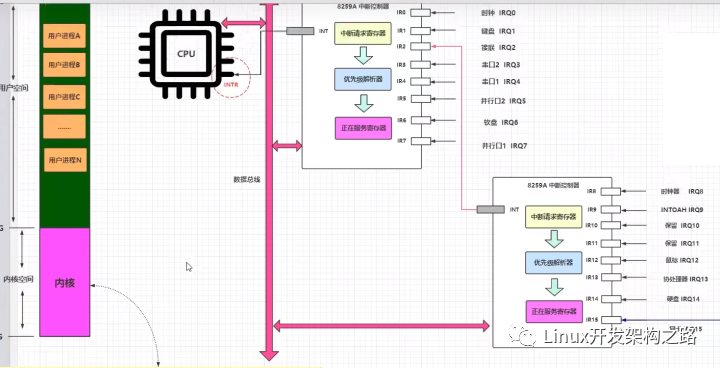

1 中斷處理處理外界發出的信號。中斷信號可能是關于數據讀寫操作的,也可能與外部設備控制有關。Intel處理器只有一個外部中斷引腳INTR,為了使處理器能夠同時接收多個硬件設備發送來的中斷請求信號,特將鎖

2021-12-17 18:44:38 7

7 uCOS-III(15)中斷管理異常與中斷中斷延遲中斷延遲發步代碼中斷延遲發布任務初始化異常與中斷異常是指任何打斷處理器正常執行,并迫使處理器進入一個由有特權的特殊指令執行的事件。異常通常可以分為

2021-12-23 19:54:33 3

3 FREERTOS中斷組屏蔽實驗Cortex M中斷管理(該段取自正點原子FREETRTOS開發手冊,我覺得比較詳細了)當多個中斷來臨的時候處理器應該響應哪--個中斷是由中斷的優先級來決定的,高優先級

2021-12-31 19:16:04 6

6 的主要功能。i.中斷管理。ii.支持異常及中斷向量化處理。iii.支持前臺中斷。2、外部中斷控制器EXTI。3、按鍵中斷實例。4、串口中斷實例。問題引入問題引入:我們想通過 按鍵 控制燈亮 ,怎么做一...

2022-01-13 10:19:40 0

0 1.按照中斷請求的來源可以分為 ○ 內部中斷(完全在CPU內部實現) § 異常中斷----異常事件引起的(掉電、除法、溢出等) § 軟件中斷----中斷指令引起的(INT n---中斷調用系統

2022-01-14 14:55:45 2

2 STM32中斷——總結及實操一、中斷是什么?1.1 中斷的含義1.2 中斷的作用(了解即可)1.3 中斷的流程二、中斷資源2.1 NVIC中斷控制器2.2 NVIC寄存器三、優先級的概念四、中斷

2022-01-14 15:48:01 4

4 概述

從本質上來講,中斷是一種電信號,當設備有某種事件發生時,它就會產生中斷,通過總線把電信號發送給中斷控制器。

如果中斷的線是激活的,中斷控制器就把電信號發送給處理器的某個特定引腳。處理器于是

2022-02-10 12:02:01 0

0 處理器中的NVIC能夠處理多個可屏蔽中斷通道和可編程優先級,中斷輸入請求可以是電平觸發,也可以是最小的一個時鐘周期的脈沖信號。每一個外部中斷線都可以獨立的使能、清除或掛起,并且掛起狀態也可以手動地設置和清除。

2022-05-10 10:02:17 4616

4616 在Cortex‐M0內核上搭載了一個異常響應系統,支持眾多的系統異常和外部中斷。其中,編號為1-15的對應系統異常,大于等于16的則全是外部中斷,優先級的數值越小,則優先級越高。除了個別異常的優先級被定死外,其它異常的優先級都是可編程的。

2022-06-01 14:41:41 6262

6262 由中斷或異常處理程序執行的代碼不是一個進程。而是一個內核控制路徑,比一個進程的上下文要少,建立或終止需要的時間很少。

2022-08-17 11:31:22 974

974 如果一個中斷發生了,卻無法立即處理,這個中斷請求將會被掛起。掛起狀態保存在一個寄存器中,如果處理器的當前優先級還沒有降低到可以處理掛起的請求,并且沒有手動清除掛起狀態,該狀態將會一直保持。

2023-05-13 12:24:41 698

698

本文針對CW32L083系列MCU,同系列產品亦可參考。ARM?Cortex?-M0+內核的嵌套向量中斷控制器(NVIC),用于管理中斷和異常。NVIC和處理器內核緊密相連,可以實現低延遲的異常

2022-12-01 11:36:10 1500

1500

的機制,能夠提高系統的實時性和可靠性。在ARM處理器中,中斷的實現主要涉及到下面的幾點。 一、中斷控制器 ARM系統中,中斷控制器是實現中斷的重要組成部分。中斷控制器的主要作用是監控外部硬件中斷請求并向CPU發出中斷請求信號,同時還需要

2023-09-05 16:22:23 1765

1765 Cortex-M 內核中斷/異常系統、中斷優先級/嵌套 詳解

2023-09-27 15:29:36 3699

3699

當異常中斷發生時,程序將當前執行指令的下一條指令的地址存入新的異常模式的鏈接寄存器LR中(R14_<mode>),以便程序在異常處理完后,能正確返回原程序。

2023-10-18 17:25:43 1619

1619 arm處理器有哪些中斷源?arm處理器對異常中斷的響應過程? ARM處理器是一種廣泛使用的嵌入式處理器,運行著各種不同類型的應用程序。為了保證應用程序的穩定性和正確性,ARM處理器需要在遇到異常

2023-10-19 16:35:59 2358

2358 ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢? 在計算機系統中,異常和中斷是兩個常見的概念。 在ARM中,異常和中斷的主要目的是幫助處理器響應與系統操作相關的事件。 由于處理器必須同時執行

2023-10-19 16:36:11 1741

1741 ARM9中斷中(C語言)如何實現復位功能,而不是返回中斷前的狀態? 在ARM9處理器的中斷中,當系統發生異常時,處理器會暫停正在執行的指令并處理中斷請求。處理中斷的方式有兩種,一種是通過向處理器發送

2023-10-19 16:42:43 2024

2024 什么是中斷響應次序?什么是中斷處理次序? 中斷響應次序和中斷處理次序是計算機系統中非常重要的概念,它們有助于確保系統穩定、可靠、高效地運行。本文將詳述這兩個概念的含義、作用和實際應用。 一、中斷響應

2023-10-24 11:49:12 3840

3840 在ARM處理器中,當一個中斷信號被觸發時,中斷控制器會發出一個中斷請求,并將該請求傳遞給CPU。 CPU接收到中斷請求后,會根據中斷號在中斷向量表中查找對應的中斷服務程序入口地址。 中斷向量表是一個

2023-10-30 17:19:02 2256

2256 的理論知識。 硬件中斷: 硬件中斷是由某些硬件設備引起的,例如啟動 I/O 的請求、硬件故障或類似的事情。引入硬件中斷是為了避免在輪詢循環中浪費處理器寶貴的時間,等待外部事件。 例如,當 I/O 操作完成時,例如從磁帶驅動器將一些數據讀入計算機

2023-11-07 16:52:28 2114

2114

? 硬中斷是由外部事件引起的因此具有隨機性和突發性;硬中斷是否可以嵌套的,是否有優先級(由硬件設計體系決定)。 ? 軟中斷是執行中斷指令產生的,無面外部施加中斷請求信號,因此中斷的發生不是隨機的而是

2023-11-07 17:02:58 1822

1822 今天來看一下中斷及ARM體系中對中斷的處理,直接進入正題。 中斷是指計算機運行過程中,出現某些意外情況需主機干預時,機器能自動停止正在運行的程序并轉入處理新情況的程序,處理完畢后又返回原被暫停的程序

2023-11-07 17:11:52 1403

1403

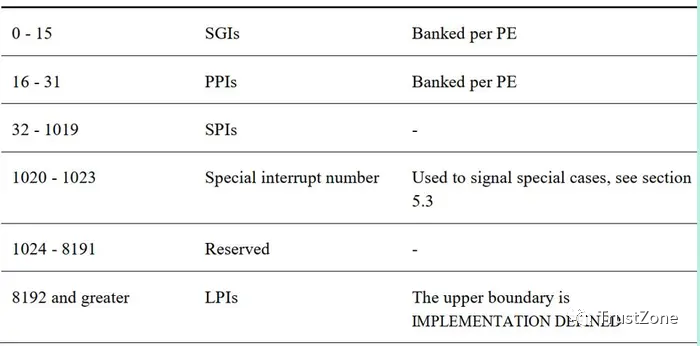

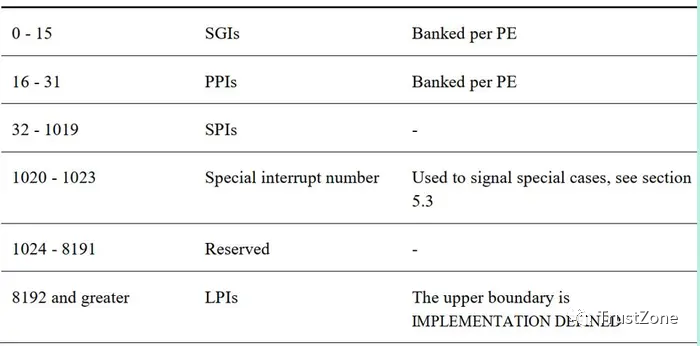

:(shared peripheral interrupt),共享外設中斷,該中斷來源于外設,但是該中斷可以對所有的core有效。 ? ?SGI:(software-generated interrupt),軟

2023-11-07 18:01:29 1521

1521

當MCU接收到一個中斷信號時,它會暫停當前正在執行的任務,保存現場,然后跳轉到預設的中斷處理程序(Interrupt Service Routine, ISR)去處理這個中斷。

2023-11-08 12:57:27 2840

2840 去繼續運行被暫時中斷的程序。Linux中通常分為外部中斷(又叫硬件中斷)和內部中斷(又叫異常)。 軟件對硬件進行配置后,軟件期望等待硬件的某種狀態(比如,收到了數據),這里有兩種方式,一種是輪詢(polling):CPU 不斷的去讀硬件狀態。另一

2023-11-09 16:46:26 1434

1434

進程來持有CPU進行需要的操作! 有了中斷之后,提升了操作系統的性能!可以異步并行處理很多任務! 軟中斷(80中斷) 由CPU產生的;CPU檢查到程序代碼段發生異常會切換到內核態; 硬中斷 由硬件設備發起的中斷稱為硬中斷!可以發生在任何時間;

2023-11-10 11:29:49 1367

1367

進程來持有CPU進行需要的操作! 有了中斷之后,提升了操作系統的性能!可以異步并行處理很多任務! 軟中斷(80中斷) 由CPU產生的;CPU檢查到程序代碼段發生異常會切換到內核態; 硬中斷 由硬件設備發起的中斷稱為硬中斷!可以發生在任何時間;

2023-11-13 11:36:10 1597

1597

當MCU接收到一個中斷信號時,它會暫停當前正在執行的任務,保存現場,然后跳轉到預設的中斷處理程序(Interrupt Service Routine, ISR)去處理這個中斷。

2023-12-13 11:48:37 2799

2799 STM32是一款非常強大的微控制器系列,具有豐富的外設和功能。中斷是STM32中非常重要的部分,能夠幫助我們提高系統的響應速度和效率。本文將詳細介紹STM32中斷的處理方法。 一、中斷的基本概念

2024-01-02 17:35:10 3832

3832 ARM中斷的實現是通過中斷控制器和異常模式實現的。ARM處理器通過中斷控制器來接收和處理外部的中斷信號,而異常模式用于處理內部的異常事件。本文將詳細介紹ARM中斷的原理和實現方式。 一、ARM中斷

2024-01-05 15:18:11 1806

1806 ARM處理器的異常中斷響應是嵌入式系統設計中一個至關重要的環節,它確保了系統在面對內部或外部事件時能夠穩定、可靠地運行。

2024-09-10 11:18:16 2700

2700 電子發燒友網站提供《OMAP5912多媒體處理器中斷參考指南.pdf》資料免費下載

2024-12-17 16:25:25 0

0 串口中斷通常被視為外部中斷。雖然串口控制器(如USART、UART等)可能集成在微控制器或處理器的內部,但從中斷的角度來看,串口中斷是由處理器外部的通信事件觸發的。這些事件包括數據的接收、發送完成、錯誤檢測等,它們通過串口控制器的內部邏輯檢測,并轉換為中斷信號發送給處理器。

2025-01-29 15:03:00 2783

2783

電子發燒友App

電子發燒友App

評論