德國慕尼黑,2022 年 6 月——可定制RISC-V處理器硅知識產權(IP)的領導者Codasip日前宣布,其Codasip Studio平臺現已支持蘋果公司macOS Monterey(當前

2022-06-28 14:06:36 1444

1444

汽車提供跨域功能的安全集成。 ? S32平臺的擴展意義重大,允許恩智浦客戶在其新的汽車架構中利用該平臺的共性和優勢,如Arm? Cortex?處理器內核、集成硬件安全引擎(HSE)、ISO 26262 ASIL D功能安全支持和通用軟件開發環境以及面向應用的處理器系列。S32G汽車

2022-07-18 11:29:15 1306

1306

就目前而言,64位處理器對于用戶來說,并沒有太大的意義。不過在未來,或許手機真的需要8GBRAM甚至更高的RAM時,64位處理器及系統應用才能真正得到性能上的發揮,讓用戶真正的體驗到64位處理器的強大優勢。

2014-10-03 13:30:54 1934

1934 ,RISC-V?嵌入式處理器IP的領先供應商Codasip在捷克布爾諾和德國漢堡宣布,嵌入式電機和運動控制集成電路及微系統領域的全球領導者Trinamic選擇了Codasip的Bk3處理器用于其下一代產品系列。

2018-03-01 16:23:47 10637

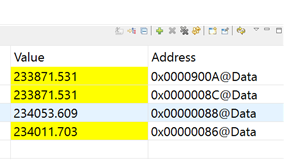

10637 C28x+FPU架構的C2000微處理器在原有的C28x定點CPU的基礎上加入了一些寄存器和指令,來支持IEEE 單精度浮點數的運算。對于在定點微處理器上編寫的程序,浮點C2000也完全兼容,不需要

2018-03-07 08:57:35 11767

11767

德國慕尼黑,2022年5月——處理器設計自動化領域的領導性企業Codasip宣布:通過采用西門子集團Siemens EDA的OneSpin?IC驗證工具,擴大了其形式驗證解決方案的可用工具范圍,以

2022-05-07 13:55:42 7148

7148

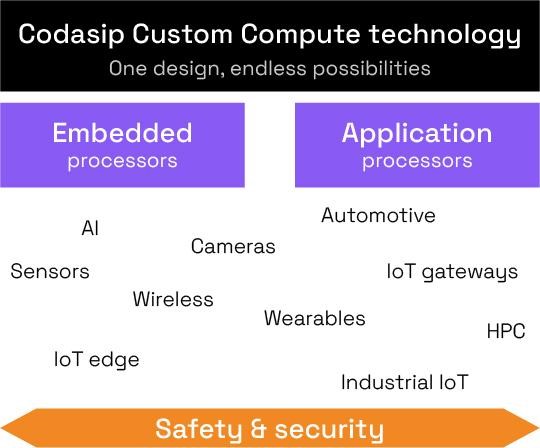

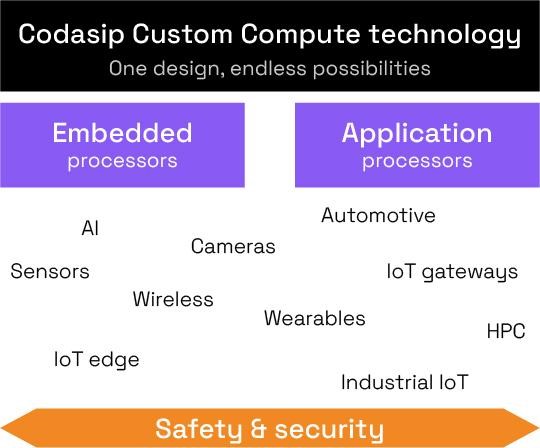

而今,除了少數應用外,最先進的處理節點對所有應用而言都太過昂貴。在大多數情況下,架構創新是提供更高性能的唯一途徑。對于計算要求較高的應用而言,理想情況下,處理器架構應與計算工作負載相匹配。

2022-12-14 13:44:36 3573

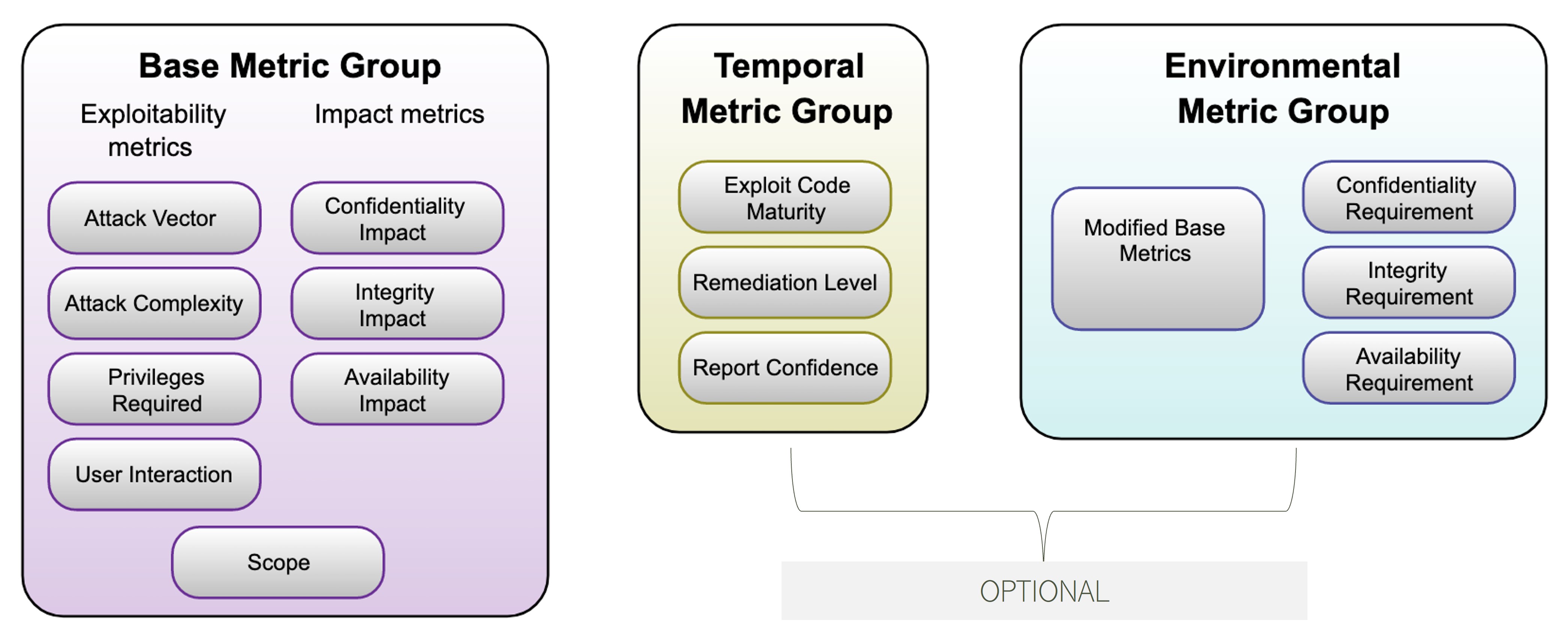

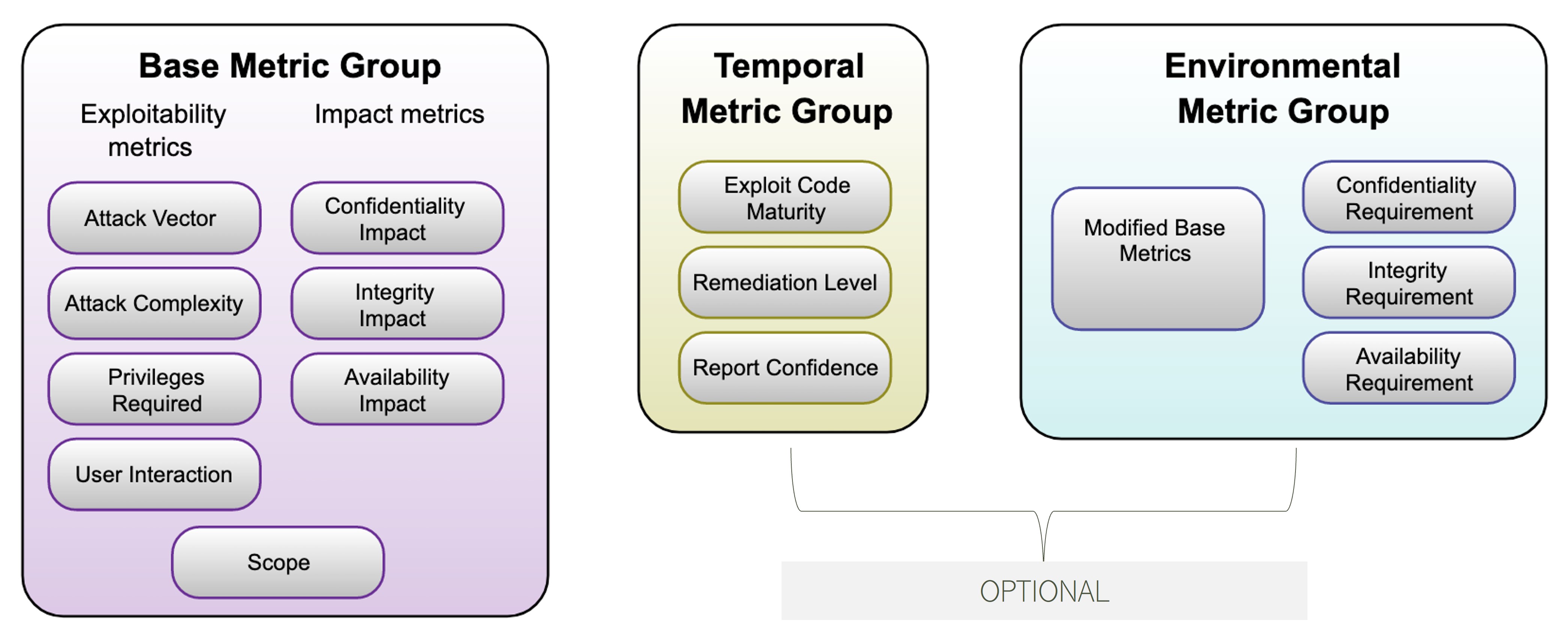

3573 驗證處理器的安全性已成為現代電子系統設計中必不可少的步驟。用戶希望確保他們的消費類設備不會被黑客入侵,并且他們的個人和財務數據在云中是安全的。有效的安全驗證涉及處理器硬件和在其上運行的多層軟件

2023-03-16 10:47:01 10765

10765

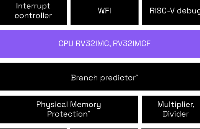

推出高度靈活的700系列,以實現無限創新 德國慕尼黑,2023年10月17日 ——RISC-V定制計算領域的領導者Codasip?今日宣布:推出一款全新的、高度可配置的RISC-V基準性處理器系列

2023-10-24 17:25:33 1009

1009

嵌入式系統以各種類型的嵌入式處理器為核心,而隨著技術的發展,對于嵌入式處理器的性能及功耗的要求愈加嚴苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩定

2019-07-19 08:29:10

對于 T2080 處理器的預布局仿真,請共享 IBIS 文件(用于仿真 Hyperlynx SI)

2023-04-03 08:51:23

喜對于Virtex-6和用于FPGA的新7個系列,我沒有任何類型或硬處理器,為什么?有沒有計劃加入新的硬處理器,如果是這樣,什么樣的處理器?謝謝

2020-06-08 16:33:35

對于WL1837MOD的CPU的選擇,如果僅用一個ARM處理器來作為CPU可以嗎?該ARM處理器需要滿足什么功能?目前的ARM處理器,選擇哪款比較好呢?

希望大神們可以一一做出解答,萬分感謝!!!

2018-06-07 10:07:52

對于i.MX 8M Mini處理器,使用mscale ddr工具生成DDR校準值的目的是什么?

我有一個運行 u-boot 的 i.MX 8M Mini 處理器。查看 u-boot 源代碼,我相信

2023-05-05 09:09:34

ARM cortex 處理器本身仿真要注意什么,uvm仿真時處理器本身arm提供驗證list嗎?

2022-08-05 14:14:40

ARM處理器模式和ARM處理器狀態有何區別?

2022-11-01 15:15:13

RK3399處理器與AR9201處理器有哪些不同之處呢?hi3559A處理器與RV1126處理器有哪些不同之處呢?

2022-02-21 07:29:27

為什么我的處理器漏電?

2021-03-02 08:19:38

嵌入式系統以各種類型的嵌入式處理器為核心,而隨著技術的發展,對于嵌入式處理器的性能及功耗的要求愈加嚴苛。目前,嵌入式處理器分為8位、16位、32位及64位等,8位微處理器/MCU市場已逐步趨向穩定

2019-07-05 07:52:22

1、在AWS云中使用Arm處理器設計Arm處理器 Amazon Web Services (AWS) 宣布推出基于 Arm 的全新 AWS Graviton2 處理器,以及相關的第 6代

2022-09-02 15:55:27

多內核是指在一枚處理器中集成兩個或多個完整的計算引擎(內核),多核處理器是單枚芯片(也稱為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統會利用所有相關的資源,將它的每個執行內核作為分立的邏輯

2019-06-20 06:47:01

慮性能、實時能力和應用靈活性的情況下,AM57x處理器也是更好的解決方案。工業以太網網關對于每個工業網絡都是不可或缺的,而性能與能夠可靠地將Gb以太網數據傳輸至工業網絡的實時能力也是必須的。全新

2018-09-04 10:07:50

微處理器的結構是由哪些部分組成的?微處理器的代碼是如何執行的呢?

2022-02-28 09:25:10

1、STM32時鐘系統概述1.1 時鐘系統的概念與意義概念時鐘系統是由振蕩器(信號源)、定時喚醒器、分頻器等組成的電路。常用的信號源有晶體振蕩器和RC振蕩器。意義時鐘是嵌入式系統的脈搏,處理器內核在

2021-08-12 07:16:57

請問RISC處理器和ARM7處理器的區別在哪?求大神解答

2022-06-30 17:51:06

處理器相關的兩個問題,望哪位大神不吝指教下:1.是不是不帶FPU的處理器都是定點處理器啊? 比如定點數值信號處理器 C55XX系列的,比如51單片機,再比如RAM常用的Cortex-M3內核處理器!2.對于定點處理器上面大神分享的經驗是不是都通用的,還是根據編譯器而定的?

2019-05-13 01:09:48

面向多核處理器的低級并行程序驗證要 隨著多核處理器的廣泛使用以及人們對軟件提出了更高的可靠性要求,多核并行程序驗證的重要性日益凸顯。本文提出了一個完整的基于多核的并行程序驗證框架,該驗證框架包括抽象

2009-10-06 09:56:26

片上系統SoC(Sytem。n Chip),即是將整個系統集成在單個的芯片上。與傳統的板級電路不同,SoC集成的完整系統一般包括系統級芯片控制邏輯模塊、微處理器/微控制器CPU內核模塊、數字信號

2019-08-30 08:27:15

片上系統SoC(Sytem。n Chip),即是將整個系統集成在單個的芯片上。與傳統的板級電路不同,SoC集成的完整系統一般包括系統級芯片控制邏輯模塊、微處理器/微控制器CPU內核模塊、數字信號

2019-09-02 07:06:58

指令集作為微處理器軟件和硬件的分界線在計算機體系結構中占有重要地位。測試程序自動生成(RTPG)是微處理器指令集驗證的主要方法之一。該文比較目前主流的RTPG 技術和驗證策略

2009-03-28 10:01:19 8

8 Tensilica 如何驗證處理器核心Tensilica 公司供稿由于半導體廠商不斷地將摩爾定律往前推進,系統單芯片(SoC)設計正陷入混亂的驗證泥潭。驗證工作在百萬門SoC 設計中所占

2009-12-19 08:26:24 10

10 摘要:在使用傳統的動態仿真方法對通用微處理器這樣大規模的設計進行功能驗證時仿真速度成為了瓶頸,而使用FPGA物理原型驗證又不能提供很好的可調試性。本文主要介紹了基

2010-06-07 10:55:29 24

24 摘要:在使用傳統的動態仿真方法對通用微處理器這樣大規模的設計進行功能驗證時仿真速度成為了瓶頸,而使用FPGA物理原型驗證又不能提供很好的可調試性。本文主要介紹了基于

2010-06-07 11:20:54 0

0 什么是雙核處理器 什么是雙核處理器呢?雙核處理器背后的概念蘊涵著什么意義呢?簡而言之,雙核處理器即是基于單個半導體的一個處理器上擁有兩個一樣功能的處理器核

2006-10-12 09:47:11 17682

17682 Banias處理器

2003年1月,Intel全新的移動處理器迅馳(Banias)問世,,與以往處理器不同,從Banias開始Intel將不再使用與桌面處理器核

2010-01-22 10:26:10 534

534 什么是移動處理器

要了解何謂移動處理器之前,我們不得不弄明白什么是處理器,處理器英文全名為Central Processing Unit,即中央處理器。是電腦中

2010-01-23 11:06:24 2026

2026 信號處理器(DSP),信號處理器(DSP)是什么意思

DSP是(digital signal processor)的簡稱,是一種專門用來實現信號處理算法的微處理器芯片

2010-03-26 14:53:54 16529

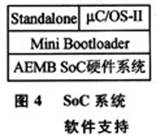

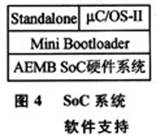

16529 AEMB軟核處理器設計的SoC系統驗證平臺

本文采用OpenCores組織所發布的32位微處理器AEMB作為SoC系統的控制中心,通過Wishbone總線互聯規范將OpenCores組織

2010-05-24 11:02:58 1040

1040

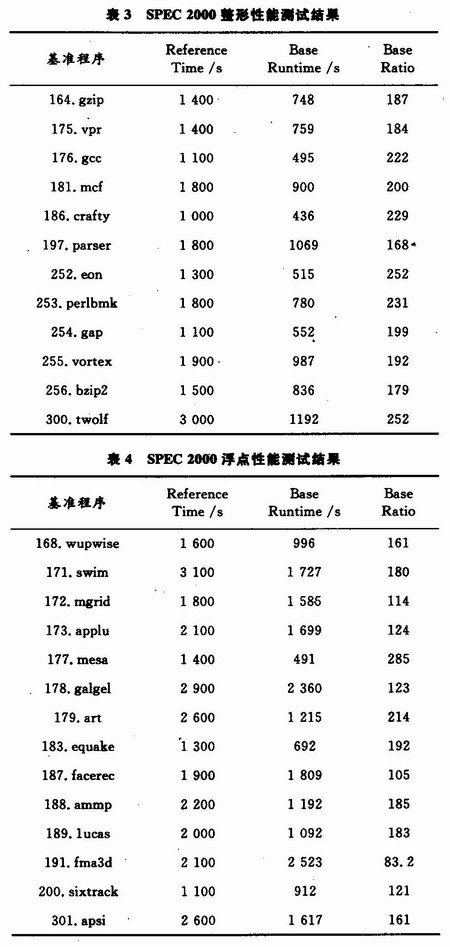

引言

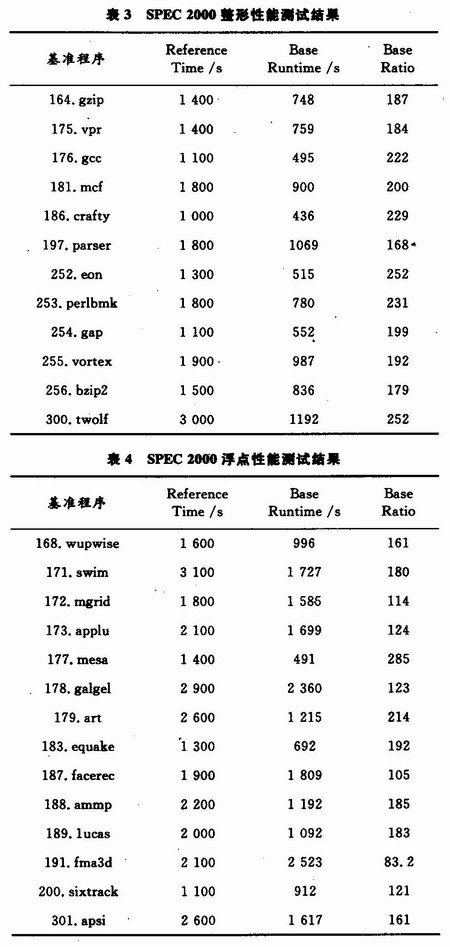

自主研發高性能處理器芯片對于經濟和國家安全方面具有重要意義。龍芯系列處理器的成功研制填補了我國自主研發高性能通用處理器的空白,龍芯2號采

2010-11-03 10:17:52 2152

2152

基于動態的RTL仿真依然是驗證超大規模集成電路的主要方法 在使用動態仿真方法對通用微處理器這樣大規模的設計進行功能驗證時仿真速度成為了瓶頸#通常的解決方案是使用:.? 進行硬

2011-06-28 17:09:13 40

40 本文利用Altera公司的FPGA開發工具對皋于國產龍芯I號處理器IP核的SoC芯片進行ASIC流片前的系統驗證,全實時方式運行協同設計所產生的硬件代碼和軟件代碼,構建一個可獨立運行、可現場

2012-04-21 15:22:01 8802

8802

基于OVM的32位微處理器驗證_吳勇昊

2017-03-17 08:00:00 3

3 為了能夠靈活地驗證和實現自主設計的基于NoC的多核處理器,縮短NoC多核處理器的設計周期,提出了設計集成4片Virtex-6—550T FPGA的NoC多核處理器原型芯片設計/驗證平臺。分析和評估了

2017-11-22 09:15:01 5267

5267 性能驗證-ON-Intel的Xeon的處理器和Xeon的PHI-協處理器簇

2018-11-07 06:36:00 4721

4721 4分鐘的FPGA簡單入門介紹,主要介紹了邏輯塊、相對于處理器的并行操作。搬運于YouTube,字幕自制。

2019-08-29 06:05:00 2925

2925 小米手機對于高通驍龍處理器依賴性大

2019-08-20 15:51:20 4304

4304 處理器,中央處理器,一臺電腦的大腦,可想而知,處理器對于電腦是多么重要。性能強的處理器可以更快地處理文檔、表格、瀏覽網頁、編輯照片和打游戲。但同時,高性能處理器也意味著筆記本價格更貴、電池續航更差

2020-05-26 09:56:06 1891

1891 經常能夠聽到專業人員在談處理器,那么處理器是什么?

2020-06-13 10:23:47 19082

19082 據了解,SoC 設計技術服務平臺這個項目是在海滄科技局和清華大學微電子所、廈門半導體投資集團,三家共同協作來完成的一個技術服務平臺。旨在能夠降低國產處理器設計的門檻,培養高端的設計人才,同時滿足中小型的設計企業面向新興市場對于處理器的需求。

2020-08-10 14:26:36 914

914 EE-368:ADSP-BF70x Blackfin+處理器加密算法驗證

2021-05-24 08:49:32 0

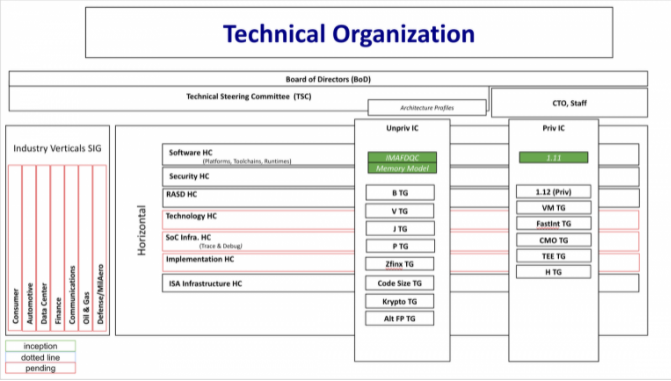

0 Codasip 科達希普公司詳細介紹 RISC-V處理器IP和處理器自動化設計工具領先供應商 2014年始創于捷克科技重鎮布爾諾 10余年的大學科研是CODASIP的萌生之本 國際RISC-V基金會

2021-06-22 14:15:29 2431

2431 IAR Systems專業的開發工具IAR Embedded Workbench for RISC-V現已能夠支持Codasip的低功耗嵌入式處理器。

2021-12-02 13:46:59 1732

1732 領先的定制化RISC-V處理器半導體知識產權(IP)內核供應商Codasip日前宣布:公司已任命Ron Black博士擔任首席執行官。

2021-12-06 10:19:37 2188

2188

Dave Higham作為ISO 26262道路車輛功能安全國際標準和安全方面的著名專家,將繼續推動Codasip去拓展定制處理器機遇。

2022-02-09 11:51:51 1777

1777

芯來科技將正式采用芯華章自主研發的新一代智能驗證系統穹景 (GalaxPSS)及數字仿真器穹鼎 (GalaxSim)等系列EDA驗證產品,加速新一代復雜RISC-V處理器IP的設計研發。

2022-03-03 10:32:25 2269

2269 德國慕尼黑 -?2022年4月—定制RISC-V處理器半導體知識產權(IP)領域的領導性企業Codasip日前宣布:已任命Jamie Broome先生為負責其全新汽車業務的副總裁。Broome在

2022-04-25 16:02:34 2402

2402

? ?Codasip支持汽車制造商在創新和差異化能力方面實現突破 德國慕尼黑 - 2022年4月—定制RISC-V處理器半導體知識產權(IP)領域的領導性企業Codasip日前宣布:已任命Jamie

2022-04-25 16:05:57 4114

4114 Codasip 已在其 DV 測試平臺中包含 Imperas 黃金參考模型,以確保有效的驗證流程能夠適應各種靈活的功能和選項,同時在未來內核的整個路線圖中進行擴展,以實現對功能質量的嚴格確認。

2022-06-01 10:11:36 1425

1425 riscvOVPsim 的可用升級包括虛擬平臺開發和仿真、多核軟件開發、可擴展平臺套件和多處理器主機 (MPonMP) 加速軟件上的 QuantumLeap 多處理器目標。

2022-06-21 09:40:21 1586

1586

功能支持Codasip的RISC-V處理器。在固件加載到Codasip處理器上時,Veridify的安全算法就會對其進行驗證,以使RISC-V開發人員確信嵌入式系統是安全可用的。 Veridify的安全

2022-07-06 16:06:07 1361

1361 盡管由于開源架構設計新的微處理器在經濟上是可行的,但測試和驗證仍然是主要障礙。 隨著 RISC-V 等開源處理器架構的出現,芯片設計變得越來越大眾化,越來越多的組織敢于涉足處理器設計,從嵌入式微控制器

2022-07-29 10:02:00 958

958

德國慕尼黑 , 2022 年 8 月 31 日 – 處理器設計自動化和可定制RISC-V處理器知識產權(IP)的領導者Codasip日前宣布,將通過 Intel ò Pathfinder

2022-09-02 15:36:02 658

658

隨著Codasip Studio 9.2.0版本的發布,Codasip Studio新版本通過擴展和優化等系列新功能賦能處理器設計自動化。

2022-09-14 17:21:13 1869

1869 可定制RISC-V處理器知識產權(IP)的領導者Codasip日前宣布:已任命胡征宇(Julian Hu)為該公司大中華區總經理,以進一步滿足區域內客戶對可定制RISC-V處理器的強勁需求,并通過更完善的技術支持組織架構來助力本地區客戶取得成功。

2022-10-20 09:43:49 1410

1410 在Codasip的驗證方法中使用智能隨機測試,使我們既能有針對性,又能廣泛地在這個新領域有效地找到更多的漏洞。這種測試方法包括調整測試,以更頻繁地激活觸發該漏洞的其他事件。

2022-11-01 10:08:20 845

845 在應用于處理器驗證的瑞士奶酪模型中,其原理類似于航空業:如果有一條直接穿過所有切片的路徑,那么飛機就有墜毀的風險。這就是為什么航空業對程序、飛行檢查單和冗余系統要求嚴格?

2022-11-01 15:57:35 1982

1982 SiliconArts光線追蹤解決方案將采用Codasip的RISC-V處理器內核IP。Codasip Studio工具將支持客戶為其圖形應用實現高度優化。通過獲得Codasip完整的架構授權,SiliconArts從此項合作伙伴關系中獲得了充分的靈活性。

2022-11-03 11:21:14 1239

1239 SiliconArts光線追蹤解決方案將采用Codasip的RISC-V處理器IP。Codasip Studio工具將支持客戶為其圖形應用實現高度優化。

2022-11-04 12:06:14 827

827 “ Codasip通過收購Cerberus增強RISC-V的安全性能,而業界需要對RISC-V的安全性足夠重視 ” 2022年11月,德國慕尼黑 - 處理器設計自動化和可定制RISC-V處理器

2022-11-12 09:15:31 1005

1005 Codasip通過收購Cerberus增強RISC-V處理器設計的安全性 RISC-V的安全性問題需要得到高度重視 德國慕尼黑市,2022年11月 - 處理器設計自動化和RISC-V處理器硅知識產權

2022-11-16 19:37:05 843

843 來源:Codasip 德國慕尼黑,2022年12月7日——處理器設計自動化和RISC-V處理器IP的領導者Codasip今日宣布成立Codasip實驗室(Codasip Labs)。作為公司內部創新

2022-12-09 15:55:58 1006

1006 Codasip成立Codasip實驗室以加速行業前沿技術的開發和應用 日前處理器設計自動化和RISC-V處理器IP的領導者Codasip宣布成立Codasip實驗室(Codasip Labs)。作為

2022-12-09 18:23:01 4372

4372 在業界屢獲獎項的Codasip L31是一個小型、高效的32位嵌入式RISC-V處理器核,針對低功耗的AI/ML應用,如物聯網邊緣設備等。憑借3級流水線、32個通用寄存器以及對谷歌

2023-02-28 10:45:30 1090

1090 處理器驗證是一個全新的領域。我們知道 Arm 和 Intel 對處理器質量的期望設置了很高的標準。在 RISC-V 中,我們必須嘗試并遵循這一點。

2023-03-22 15:19:32 1002

1002 RISC-V是一個模塊化的指令集架構,可以為其開發一個架構測試套件。它被用于基于仿真的驗證,以驗證一個處理器的實現。

2023-04-17 14:54:11 1016

1016 這種靈活性對于處理器IP來說雖然不太常見,但是可以使用Codasip IP來實現。所有的Codasip RISC-V內核都是用一種叫做CodAL的高級語言設計的,并且可以用Codasip

2023-05-31 15:25:25 1709

1709

轉型RISC-V,大家才發現處理器驗證絕非易事。新標準由于其新穎和靈活性而帶來的新功能會在無意中產生規范和設計漏洞,因此處理器驗證是處理器開發過程中一項非常重要的環節。

2023-06-01 09:07:01 1193

1193

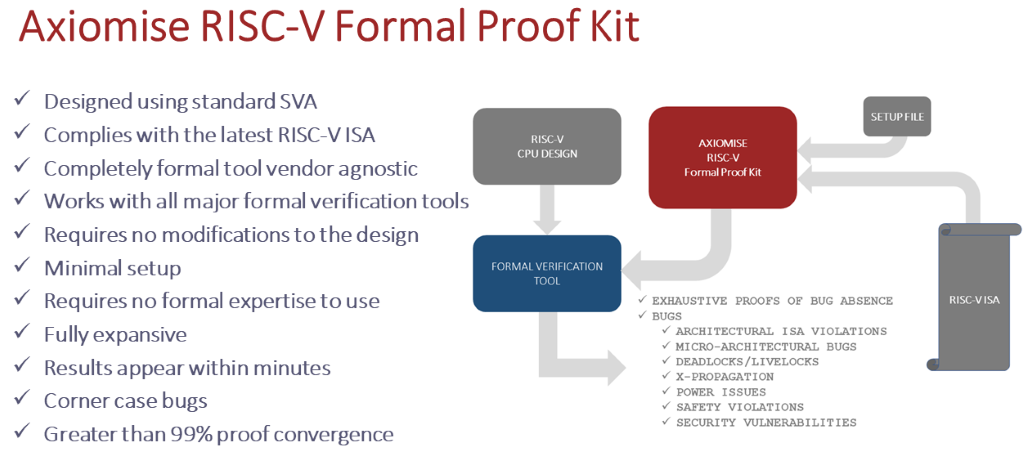

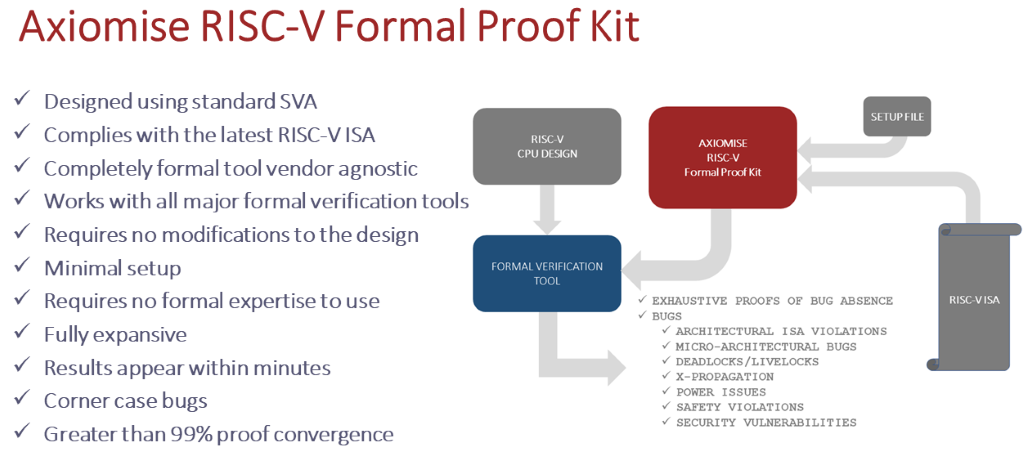

隨著RISC-V處理器的快速發展,如何保證其正確性成為了一個重要的問題。傳統的測試方法只能覆蓋一部分錯誤情況,而且無法完全保證處理器的正確性。因此,基于形式驗證的方法成為了一個非常有前途的方法,可以更加全面地驗證處理器的正確性。本文將介紹一種基于形式驗證的高效RISC-V處理器驗證方法。

2023-06-02 10:35:17 2127

2127 的客戶現在可以根據同一授權協議和合同去購買一系列精選的SmartDV外設IP的授權。這一合作伙伴關系支持使用Codasip RISC-V處理器的芯片設計人員,通過使用已驗證過兼容性和集成便捷性等特性

2023-07-03 16:13:04 1320

1320 在本文中,我們將以西門子EDA處理器驗證應用程序為例,結合Codasip L31這款廣受歡迎的RISC-V處理器IP提供的特性,來介紹一種利用先進的EDA工具,在實際設計工作中對處理器進行驗證的具體方法。

2023-07-10 10:28:41 1129

1129

RISC-V的開放性允許定制和擴展基于 RISC-V 內核的架構和微架構,以滿足特定需求。這種對設計自由的渴望也正在將驗證部分的職責轉移到不斷壯大的開發人員社群。然而,隨著越來越多的企業和開發人員轉型RISC-V,大家才發現處理器驗證絕非易事。

2023-07-10 09:42:08 1469

1469

基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現網絡交換芯片的驗證,包括四個FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片驗證任務,多任務功能驗證。

2023-07-25 14:17:35 1311

1311

本板卡系我司自主研發的基于6U CPCI處理板,適用于多核處理器多輸入芯片驗證的應用。芯片采用工業級設計。

2023-07-31 15:50:32 1462

1462

基于XCVU440-FLGA2892的多核處理器多輸入芯片驗證板卡為實現網絡交換芯片的驗證,包括四個FMC接口、DDR、GPIO等,板卡用于完成甲方的芯片驗證任務,多任務功能驗證。

2023-08-24 10:58:23 1542

1542

德國慕尼黑,2023年9月5日——RISC-V定制計算領域的領導者Codasip宣布:公司現在可為其定制RISC-V處理器內核提供Tessent Enhanced Trace Encoder增強型

2023-09-07 15:38:38 1261

1261 RISC-V定制計算領域的領導者Codasip?宣布:公司現在可為其定制RISC-V處理器內核提供Tessent? Enhanced Trace Encoder增強型追蹤編碼器解決方案,該方案

2023-09-12 09:03:25 1056

1056 基于XCVU440T的多核處理器多輸入芯片驗證板卡基于6U CPCI架構,是單機中的一個計算控制板卡,以Xilinx XCVU440-FLGA2892 FPGA(作為處理器載體)為核心,FPGA

2023-09-12 10:30:46 1974

1974

RISC-V定制計算領域領導者 Codasip 今天宣布推出全新高度可配置的RISC-V基準處理器系列,旨在實現無限創新。該"700家族系列"包括應用和嵌入式處理器內核。700

2023-10-18 10:03:55 1297

1297 工智能加速技術,在極端數據分析的可擴展性方面取得突破性進展。Codasip在該項目中的職責是開發基于RISC-V矢量擴展(RVV)的領域專用加速器。我們將利用設計自動化工具 Codasip Studio 和 CodAL 處理器描述語言完成這項工作。

2023-10-18 14:57:05 1719

1719 2023年年尾最為重要的集成電路年會,Codasip作為銀牌贊助商向客戶和觀眾展示了其獨特的定制計算解決方案、新產品RISC-V處理器700系列以及Codasip Studio設計工具的獨到之處。 Codasip作為全球領先的RISC-V處理器IP核供應商,我們在此次展會上再次證明了其在處理器的設計、開發和優

2023-11-11 10:22:32 1081

1081 基辛格指出,英特爾已經成功交付Sierra Forest的最后樣品給客戶;而Granite Rapids處理器的生產狀況超過預期,正在進行通電驗證,結果令人滿意。

2024-01-30 11:28:19 1132

1132 與同級內核相比,CodasipL110每瓦性能提高50%,代碼規模縮小20% 德國慕尼黑,2024年6月4日— RISC-V定制計算領域的領導者Codasip推出了新的低功耗嵌入式處理器核和新一代

2024-06-05 17:23:56 1298

1298 ARM處理器的寄存器組織是其核心架構的重要組成部分,對于理解ARM處理器的運行機制和性能特點具有重要意義。以下是對ARM處理器寄存器組織及功能的詳細闡述。

2024-09-10 11:11:33 3443

3443 Codasip是一家歐洲領先的RISC-V處理器IP核供應商,目前正在掛牌出售。以下是相關情況: 出售背景 Codasip在CEO Ron Black的領導下,計劃在未來三個月內出售公司。 公司已獲

2025-07-02 16:31:57 2210

2210

電子發燒友App

電子發燒友App

評論