很多人在配置STM32中斷時對固件庫中的這個函數NVIC_PriorityGroupConfig()——配置優先級分組方式,會很不理解,尤其是看中文翻譯版的,因為中文翻譯版里把這里翻譯成“先占優先級和從優先級”這樣翻譯其實是不對的,很容易讓人誤解。

2017-12-22 06:25:00 11318

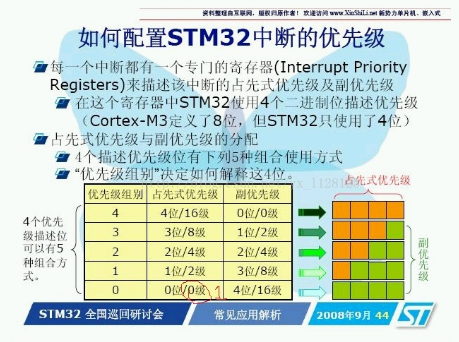

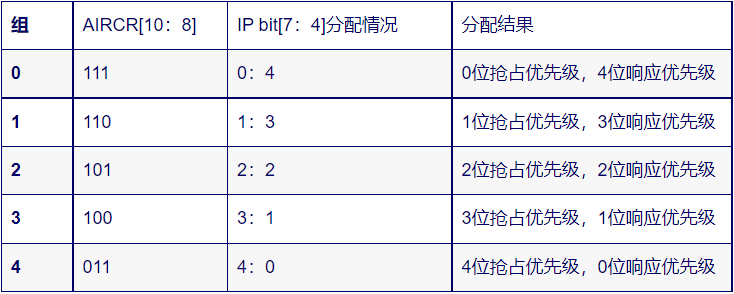

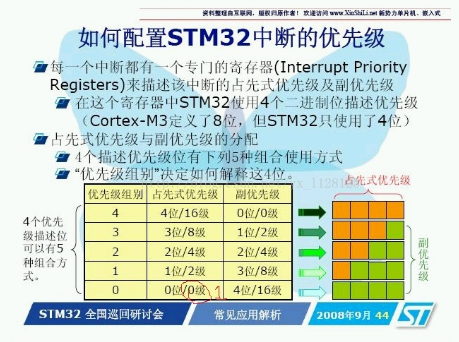

11318 STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作‘亞優先級’或‘副優先級’,每個中斷源都需要被指定這兩種優先級。

2018-01-10 14:12:36 11196

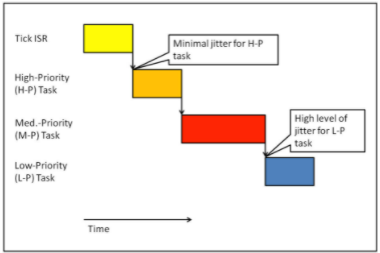

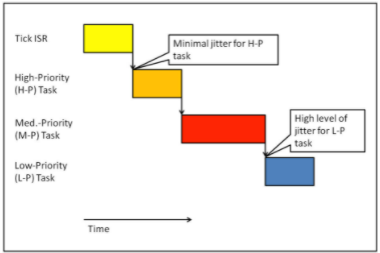

11196 在嵌入式系統中,如果使用基于優先級調度算法的RTOS,系統中可能發生優先級反轉現象。優先級反轉用來描述系統中高優先級任務由于等待低優先級任務完成才能繼續執行的情景,通常發生在試圖獲取信號量使用權或

2022-12-14 11:00:53 1979

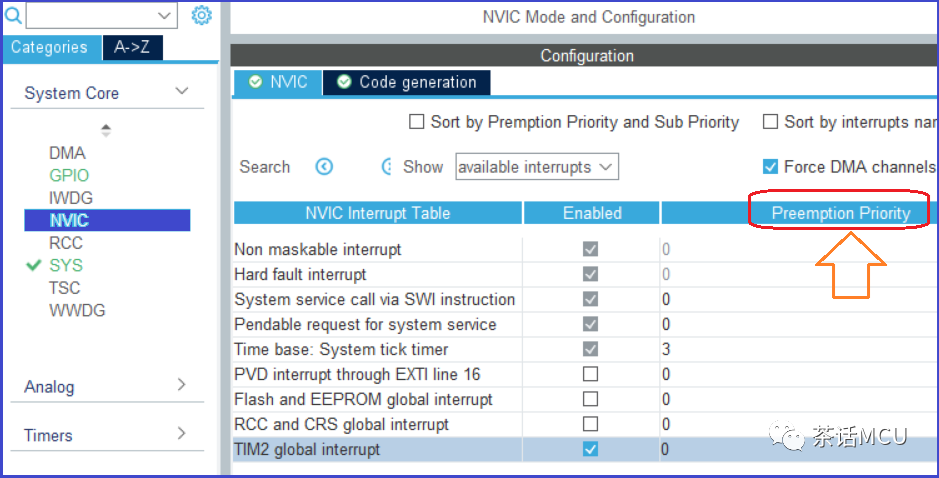

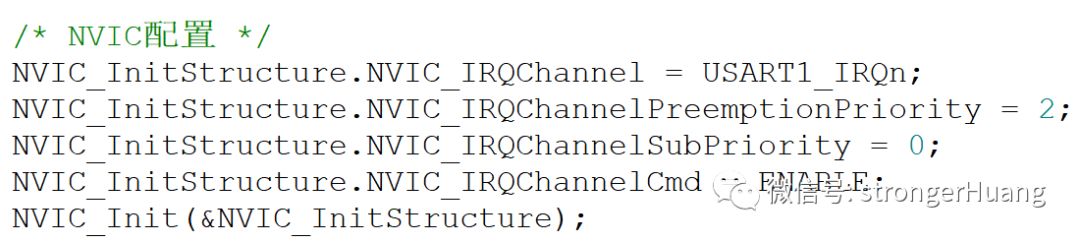

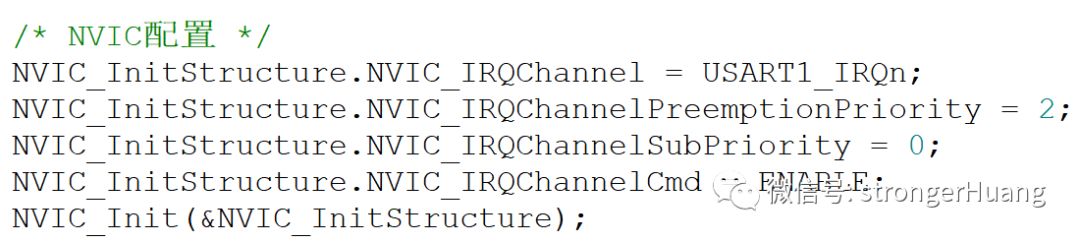

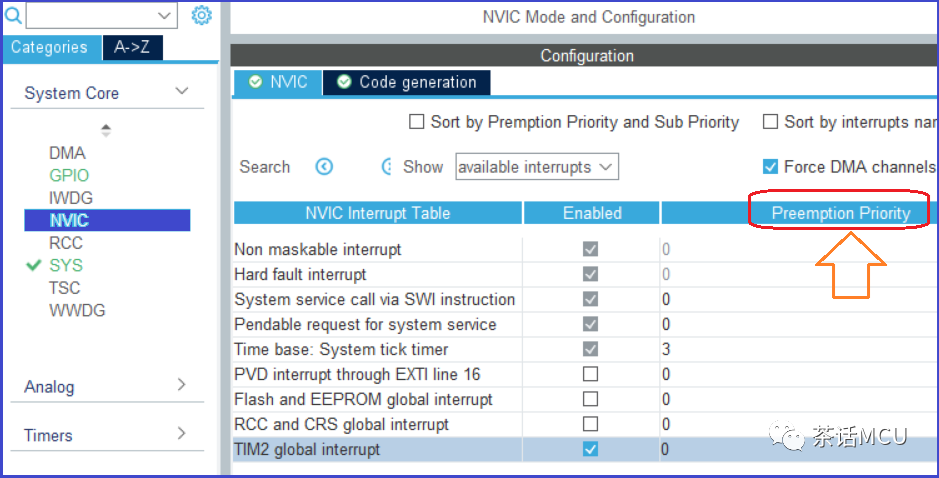

1979 時,不難發現一個問題,那就是怎么沒有中斷子優先級【或稱響應優先級、副優先級等】的配置?!【當然,很多時候我們或許沒有關注子優先級】如下圖所示,只看到搶占優先級的配置,看不到子優先級的配置項。

2023-09-09 09:25:32 3134

3134

若單片機同時接收到幾個中斷請求時,單片機對中斷請求的響應順序是如何確定的?實際上,單片機是通過中斷優先級來確定中斷響應順序的。

2023-10-31 14:42:51 3625

3625

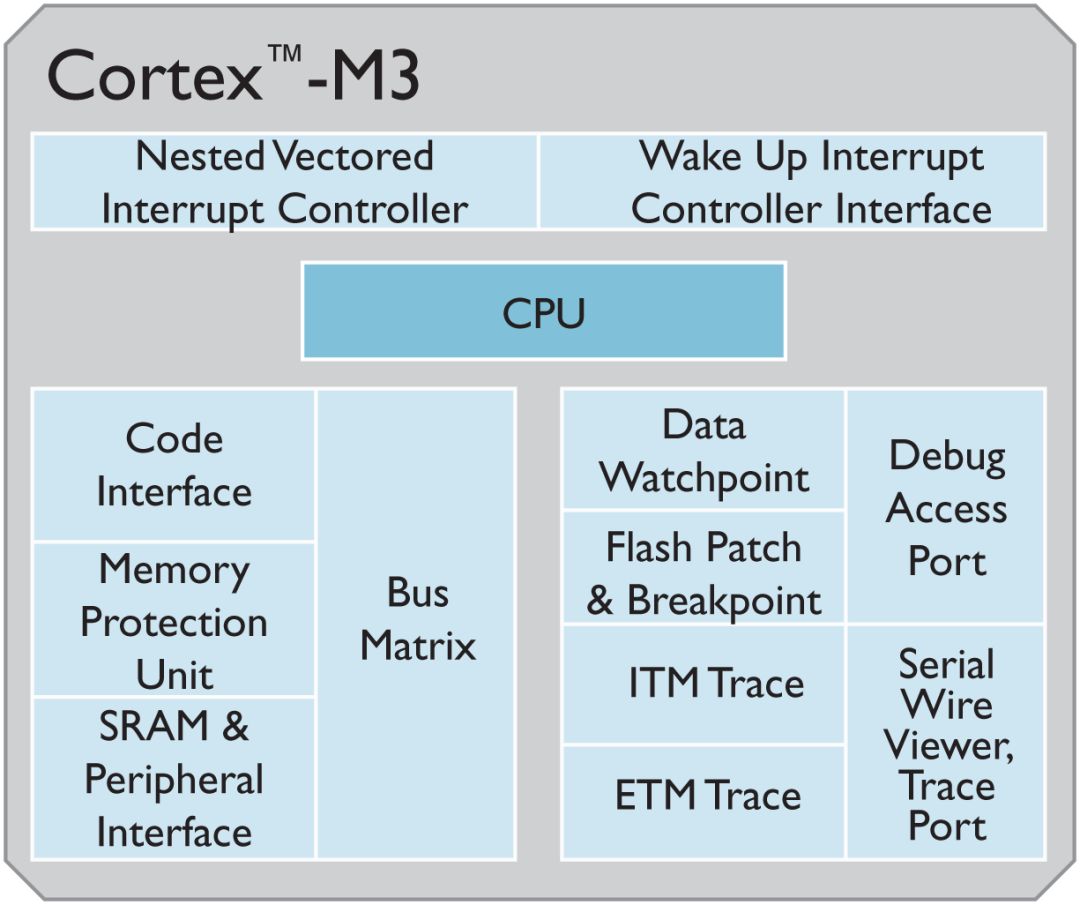

置頂/星標公眾號,不錯過每一條消息!很多朋友對中斷的一些知識還是不了解,今天就寫點關于Cortex-M3處理器中斷相關,以及FreeRTOS中斷優先級配置的內容。...

2021-08-13 06:16:45

的處理能力。

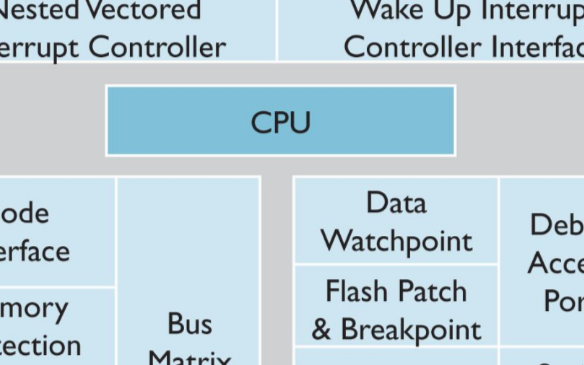

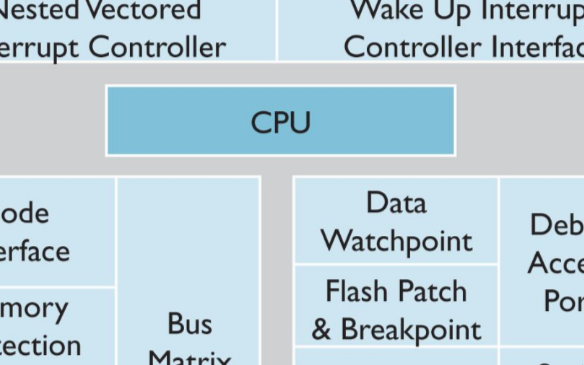

中斷控制器:Cortex-M處理器內置了靈活的中斷控制器,能夠支持多種中斷優先級和高效的中斷處理機制。

訪問控制單元(ACU):ACU提供了對存儲器和外設的訪問控制,以保證系統

2025-11-26 07:22:38

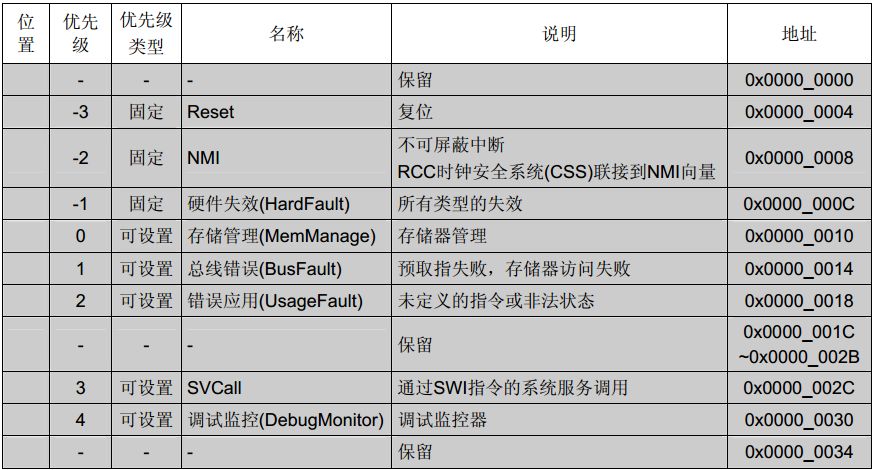

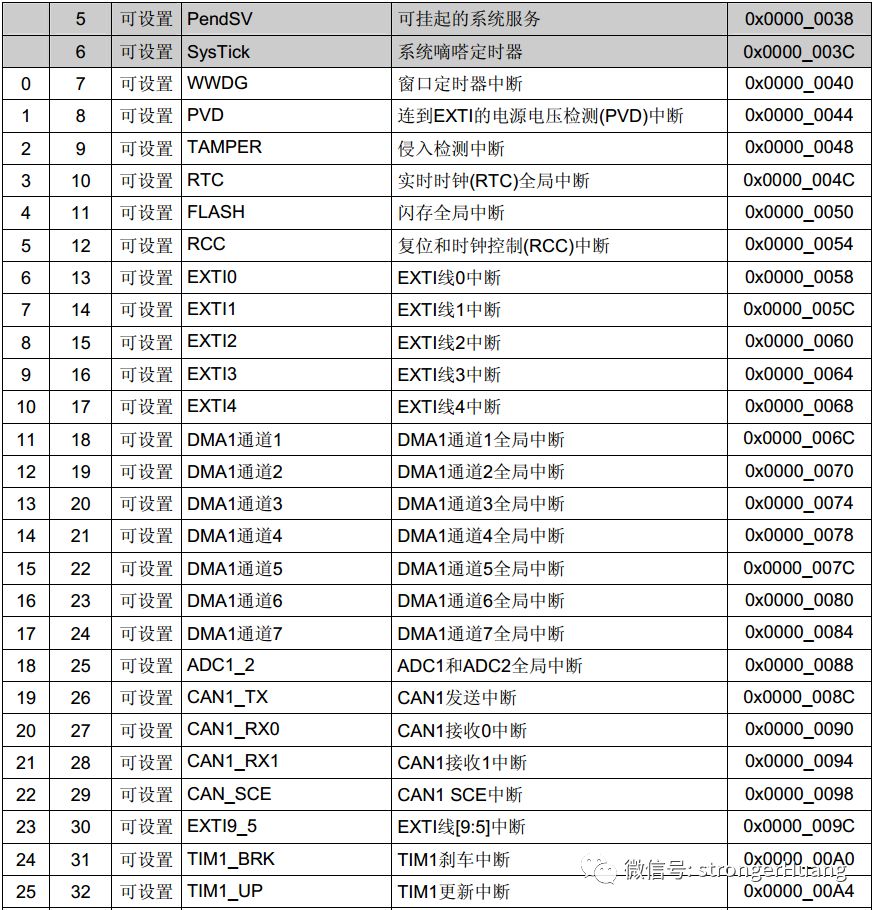

6.Cortex-M系列中斷(1)Coretx-M內核都具有NVCI(嵌套向量中斷控制器)①中斷向量表在STM單片機的啟動.s文件中,可以查找到具體的中斷源與中斷服務函數(2)搶占優先級和響應優先級

2022-01-25 07:32:03

Cortex M內核中每個中斷都有一個8位的優先級設置寄存器這個8位的寄存器可以分為搶占優先級和子優先級兩個部分(通過設置優先級組設置)搶占優先級和子優先級有什么用?舉例說明:有兩個中斷A、BA

2022-01-25 06:07:42

一、中斷優先級配置的函數:1.NVIC_IRQChannelPreemptionPriority配置搶占優先級2.NVIC_IRQChannelSubPriority配置響應優先級二、搶占優先級與響應優先級的描述:1、搶占優先級不同,...

2021-08-04 08:24:55

中斷優先級配置的函數有哪幾種?怎樣去比較搶占優先級與響應優先級呢?

2021-10-19 08:02:05

單片機芯 片: STC12C5A60S2 晶振是11.0592MHZ中斷優先級的基本規則1.低優先級中斷可被高優先級中斷所中斷2.任何中斷都不被同級中斷所中斷然而datashhet里

2021-11-25 06:32:12

最多可以有四位數)。二:優先級判斷STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作'亞優先級'或'副優先級',每個中斷源都需要被指...

2021-08-13 06:50:02

CC1310rtos里面,優先級定義時,是1的優先級高還是2的優先級高?

2018-06-21 10:12:15

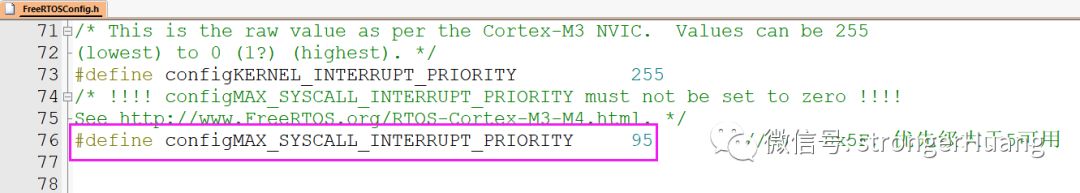

FreeRTOS中斷優先級和任務優先級架構:Cortex-M3版本:FreeRTOS V9.0.0前言:最開始,我并沒有搞清楚什么是中斷優先級和任務優先級,但看了部分資料后發現這兩個并沒有半毛錢關系

2022-02-08 06:36:37

1 NVIC中斷優先級分組1.1NVIC的中斷向量表Cortex-M3和CM4內核都支持256個中斷,其中包含了16個內核中斷(異常)和240個外部中斷,并且具有256級的可編程中斷設置。但是

2022-01-25 07:19:42

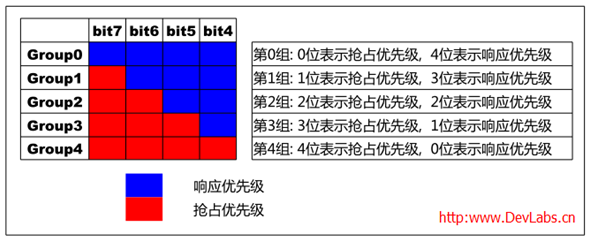

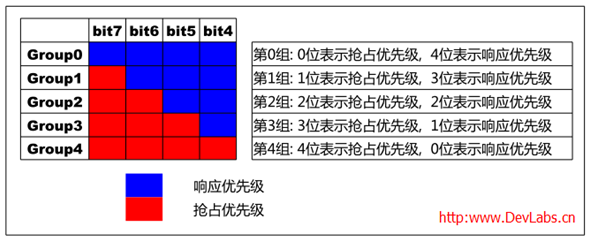

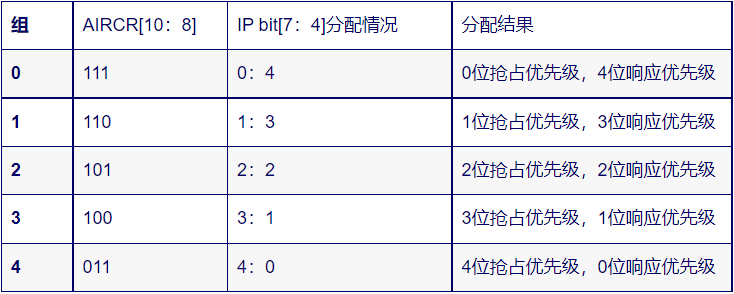

NVIC中斷優先級管理中斷優先級分組:STM32F407系列把中斷分為5個組:(0~4)對0-4每個中斷設置一個搶占優先級和響應優先級值(值越小優先級越高)且第n個分組來說,有n位搶占優先級(值0

2021-08-16 08:06:19

一、中斷優先級:STM32(Cortex-M3)中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作'亞優先級'或'副優先級',每個中斷

2021-08-16 07:21:27

STM32中斷優先級和開關總中斷一,中斷優先級:STM32(Cortex-M3)中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作

2021-08-16 07:05:56

STM32中斷優先級和開關總中斷一,中斷優先級:STM32(Cortex-M3)中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作

2021-08-23 07:06:14

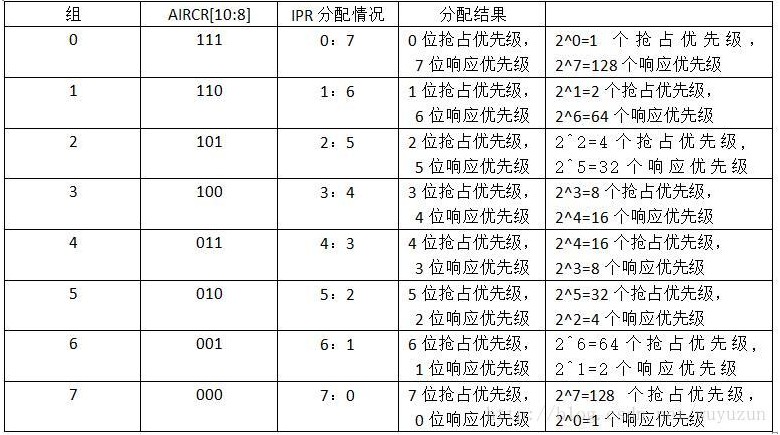

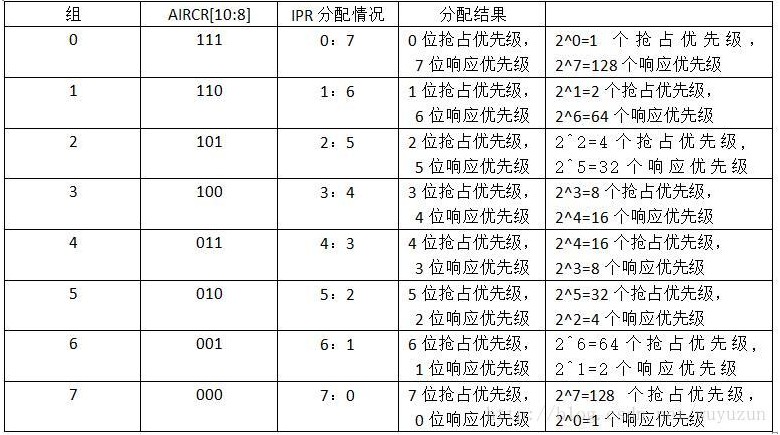

優先級,就需要有相應的寄存器位記錄每個中斷的優先級;在Cortex-M3中定義了8個比特位用于設置中斷源的優先級,這8個比特位在NVIC應用中斷與復位控制寄叢器(AIRCR)的中斷優先級分組域中,可以有

2018-07-06 03:27:03

STM32d的中斷優先級由NVIC_IPRx寄存器來配置,IPR的寬度為8bit所以原則上每個中斷可配置的優先級為0~255,數值越小優先級越高,但對于大部分的 Cortex-M3芯片都會精簡

2021-08-11 09:08:46

使用該內核所有的東西,但對我們來說只是會配置就可以了。對于其中斷數量只是了解就OK了,如果真的有需要用到其所有數量的中斷的大佬,也不會看我的文章了,中斷作為單片機最重要的外設之一,其優先級是最重要的,STM32的中斷優先級配置主要有以下兩個方面一是中斷分組;二是對每一個中斷中斷設置其搶占優先級和響應優先級。

2022-01-14 09:13:10

STM32 (Cortex-M3) 中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念:搶占式優先級和響應優先級,也把響應優先級稱作“亞優先級”或“副優先級”,每個中斷源都需要被指定

2021-08-16 06:49:41

單片機有一定了解的都知道51單片機有5個中斷源,2個優先級,通過對IP這個寄存器賦值來進行中斷優先級的處理而STM32的中斷非常強大,每個外設都可以產生中斷,那...

2021-08-13 07:44:46

的四個中斷分別設置,個人覺得可以分別獨立配置表2真值表就是具體配置STM32中斷級優先級別了。表2來自ST官方資料,STM32F10xxx Cortex-M3編程手冊-英文版.pdf第135頁。參考理解Cortex-M3 權威指南.PDF

2014-04-15 14:14:09

在stm32開發中,我們可能需要多個串口同時收發,這時需要配置下中斷的優先級問題。中斷優先級中搶占優先級與響應優先級位數可自行分配。初始化時NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2); //2 位搶占優先級、2位響應優先級可根據需要自行替代分配,如下:...

2021-08-13 06:24:23

STM32F具有多達 98 個可屏蔽中斷通道(不包括帶 FPU 的Cortex?-M7 的 16 根中斷線),16 個可編程優先級(使用了 4 位中斷優先級),可以將中斷分成5個組,分別為組0-4

2021-08-16 07:02:55

仍然是以我們最熟悉的Cortex-M系列為例,而M系列我就說說Freescale目前兩大當家的——M0+和M4的優先級設置問題。我們知道ARM從Cortex-M系列開始引入了NVIC的概念(Nested

2015-01-19 14:22:09

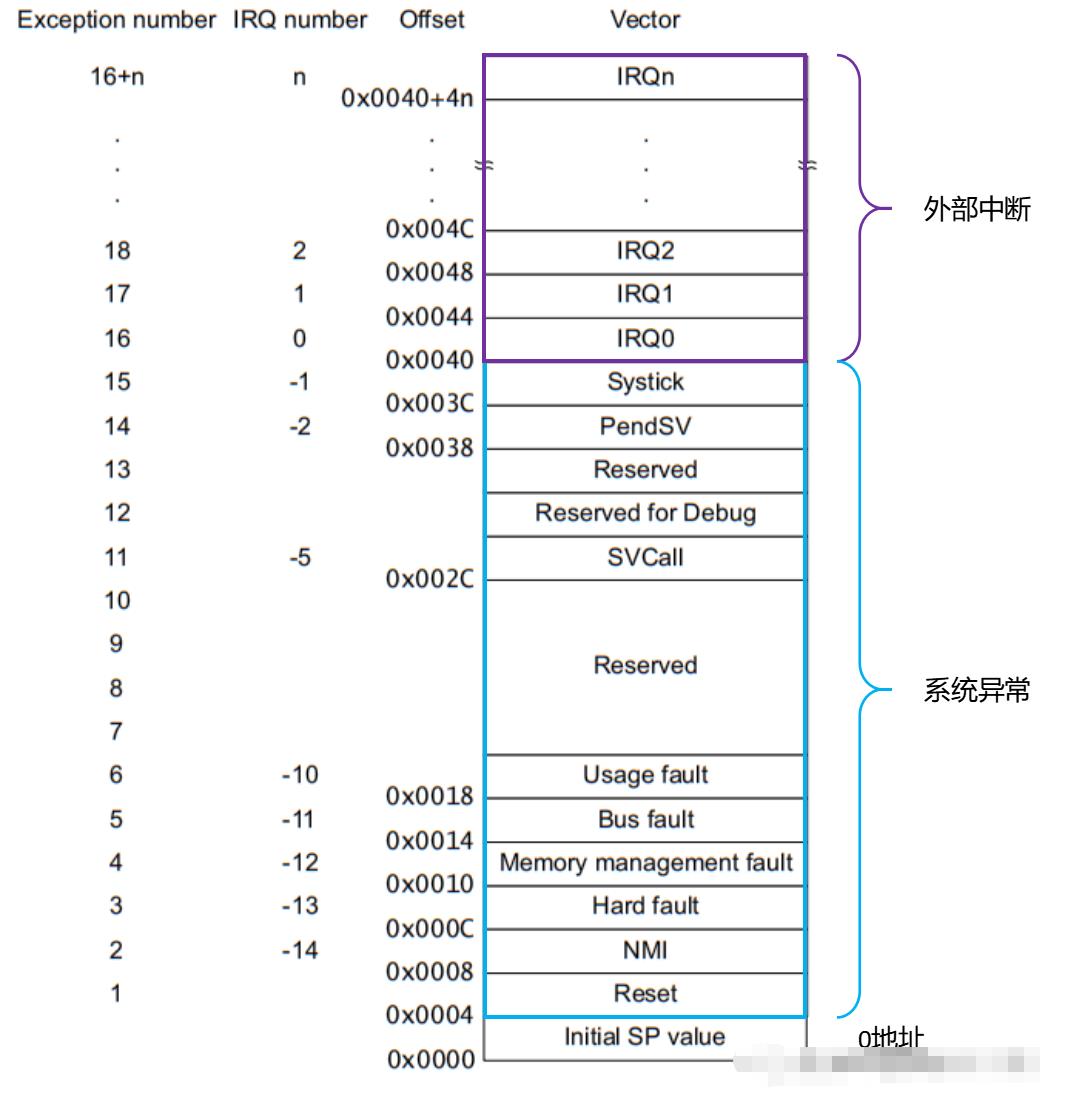

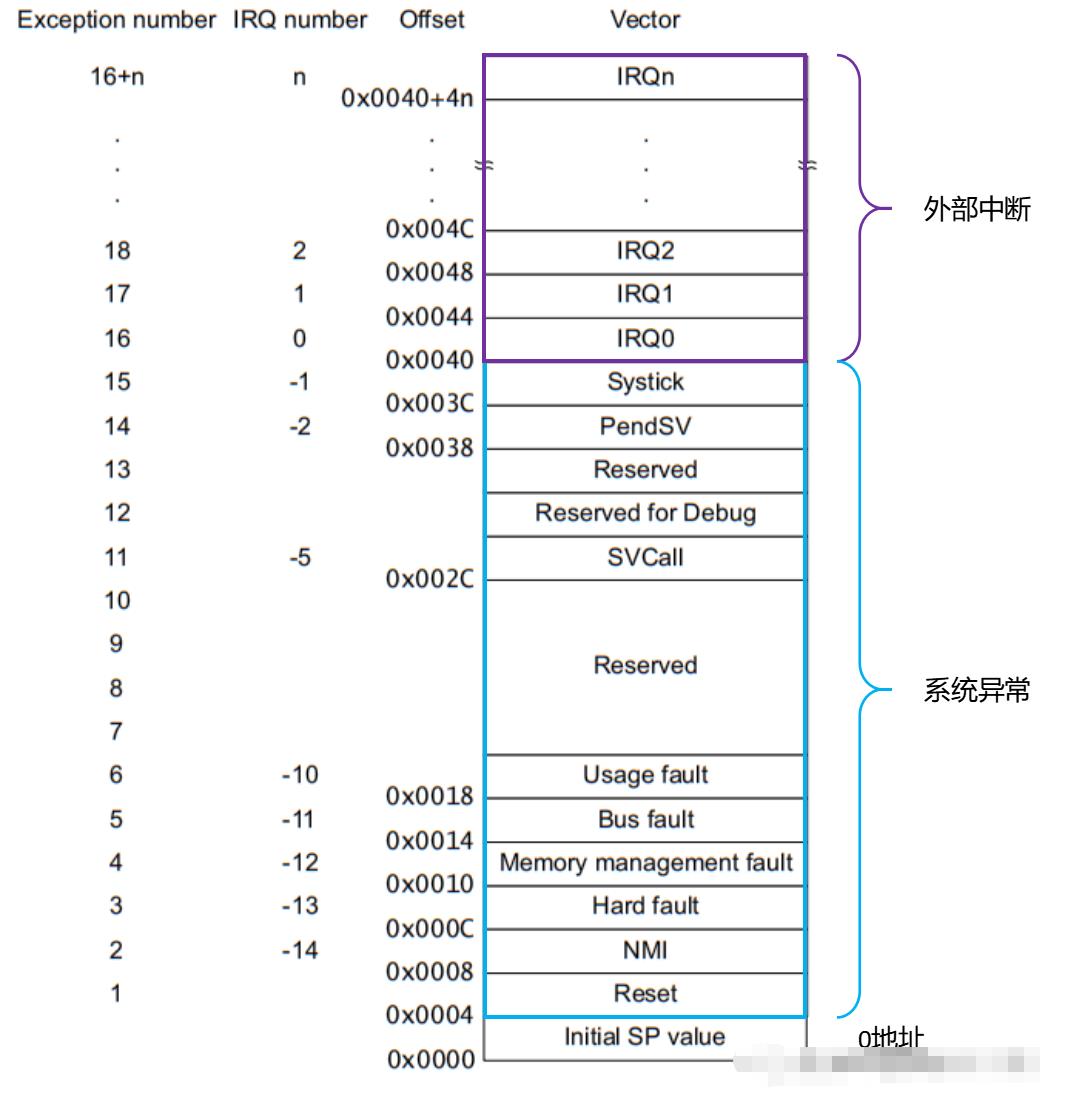

應用設計的,沒有獨立MCU。異常類型??Cortex-M 處理器的異常中,編號 1~15 的為系統異常,16及以上的則為中斷輸入。所有終端機部分系統異常都具有可編程的優先級。部分系統異常具有固定優先級。ARM給出

2020-08-27 17:40:42

仍然是以我們最熟悉的Cortex-M系列為例,而M系列我就說說Freescale目前兩大當家的——M0+和M4的優先級設置問題。我們知道ARM從Cortex-M系列開始引入了NVIC的概念(Nested

2021-11-16 06:30:01

你好恩智浦團隊。我嘗試配置 SysTick 中斷但沒有成功。問題 1:如何更改 SysTick IRQ 優先級?我使用了下面提到的兩種方法:1.2. 由于 RTD 函數中存在保護,解決方案 2 在

2023-02-28 09:41:49

優先級范圍從0x00~0xFF), 是絕大多數微控制器制造商只是使用其中的一部分優先級NXP 1062 使用了其中的高4bits,所以中斷優先級在0-15,共16個在Cortex-M內核中,一個中斷的優先級數值越低,邏輯優先級卻越高從RTOS角度RTOS中斷嵌套方案將有效的中斷優先級分成兩組:?可以

2021-12-16 07:08:25

STM32中斷優先級和開關總中斷一,中斷優先級:STM32(Cortex-M3)中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作

2022-01-14 07:43:52

stm32的中斷嵌套優先級stm32NVIC優先級分組中斷優先級配置寄存器NVIC_IPRx描述搶占優先級與響應優先級 ,在Cortex_m3中,該寄存器被定義為8bit,考慮stm32允許具有較少

2021-08-13 09:45:55

一:綜述 STM32 目前支持的中斷共為 84 個(16 個內核+68 個外部), 16 級可編程中斷優先級 的設置(僅使用中斷優先級設置 8bit 中的高 4 位)和16個搶占優先級(因為搶占優先級最多可以有四位數)。 二:優先級判斷 STM32(Cortex-M3)中有兩

2021-08-13 07:08:40

知道NVIC的核心工作原理即是對一張中斷向量表的維護上,其中M4最多支持240+16個中斷向量,M0+則最多支持32+16個中斷向量,而這些中斷向量默認的優先級則是向量號越小的優先級越高,即從

2015-01-28 14:48:50

鑒于MCS-51 系統只提供“二級中斷嵌套”, 提出擴展51 系統中斷優先級的純軟件方法。其利用51系統內建的中斷允許寄存器IE 和中斷優先級寄存器IP,通過屏蔽字機制來實現;以C51 的

2009-05-15 16:23:34 19

19 允許標志位)始終為1.對于表1所列的中斷優先級分配情況,各中斷源的“中斷屏蔽字”配置如表2所列。表1 中斷源的優先級分配表中斷源X1T1T0SX0優先級01234最后,給各中斷源的ISR

2006-03-11 11:49:11 1202

1202

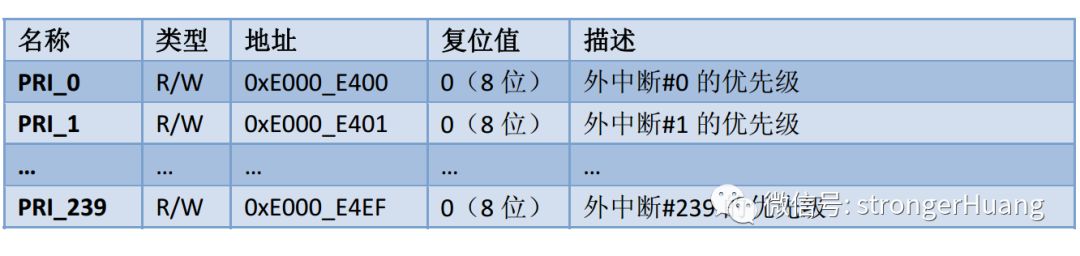

1.ARM cortex_m3內核支持256個中斷(16個內核+240外部)和可編程256級中斷優先級的設置,與其相關的中斷控制和中斷優先級控制寄存器(NVIC、SYSTICK等)也都屬于cortex_m3內核的部分。STM32采用了cortex_m3內核,所以這部分仍舊保留使用,但STM32并沒有使用

2011-02-28 14:38:38 146

146 STM32(Cortex-M3)中有兩個優先級的概念搶占式優先級和響應優先級,有人把響應優先級稱作亞優先級或副優先級,每個中斷源都需要被指定這兩種優先級。

2011-11-04 15:02:43 41

41 STM32中斷優先級和開關總中斷 教程

2015-11-23 18:03:11 0

0 NVIC中斷優先級分組

2017-03-26 10:45:36 1

1 什么是優先級 優先級是具有高搶占式優先級的中斷可以在具有低搶占式優先級的中斷處理過程中被響應,即中斷嵌套,或者說高搶占式優先級的中斷可以嵌套低搶占式優先級的中斷。 當兩個中斷源的搶占式優先級相同

2017-10-13 11:48:47 5898

5898 原以為2812中斷不能設置優先級。實際上硬件上優先級是做好的。但軟件上有辦法來設置優先級。

2018-04-08 17:20:48 20

20 我前面提到一句,M4雖然指令集是向下兼容M0+的,但是在中斷優先級管理上是有區別的,由于M4的中斷源比較多(最多允許256),所以其對中斷優先級管理是略有些復雜的,不過一定要仔細看下去,因為我們平時

2018-08-14 09:29:10 9010

9010 先占優先級也就是搶占優先級,概念等同于51單片機中的中斷。假設有兩中斷先后觸發,已經在執行的中斷先占優先級如果沒有后觸發的中斷 先占優先級更高,就會先處理先占優先級高的中斷。也就是說又有較高的先占優先級的中斷可以打斷先占優先級較低的中斷。這是實現中斷嵌套的基礎。

2018-12-07 15:09:53 10085

10085

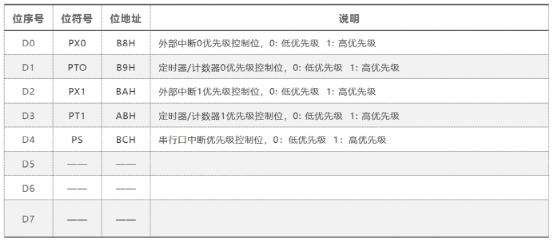

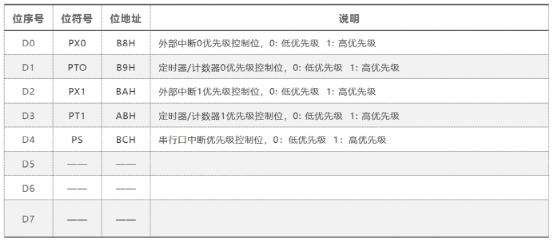

PS:串行口中斷優先級控制位。PS=1設定串行口為高優先級中斷;PS=0為低優先級中斷。

PT1:T1中斷優先級控制位。PT1=1設定定時器T1為高優先級中斷;PT1=0為低優先級中斷

2018-12-17 16:28:45 34691

34691 STM32屬于ARM中Cortex-M系列處理器,比如:STM32F1數據Cortex-M3,STM32F7數據Cortex-M7。

2018-12-30 11:23:00 7852

7852

基本型80C51系列單片機有5個中斷源,2個優先級,每個中斷源可通過軟件設置為高優先級或低優先級中斷,可以實現二級中斷服務嵌套。

2019-09-03 17:28:00 5

5 在MCS-中斷優先級中由中斷優先級寄存器IP來高置的,IP中某位設為1,相應的中斷就是高優先級,否則就是低優先級。

2019-08-20 17:31:00 2

2 同一優先級中的中斷申請不止一個時,則有中斷優先權排隊問題。同一優先級的中斷優先權排隊,由中斷系統硬件確定的自然優先級形成。

2019-08-02 17:34:00 1

1 51單片機(80C51系列)有5個中斷源,2個優先級,可以實現二級中斷服務嵌套。現在很多擴展的51單片機已經有4個優先級(或更多)和更多的中斷源了。在說到中斷之前,我先來定義一下優先級,明白了

2019-07-23 17:37:00 1

1 51單片機(80C51系列)有5個中斷源,2個優先級,可以實現二級中斷服務嵌套。現在很多擴展的51單片機已經有4個優先級(或更多)和更多的中斷源了。在說到中斷之前,我先來定義一下優先級,明白了

2019-07-09 17:41:00 3

3 其實都是查詢優級。首先查詢優先級是不可以更改和設置的。這是一個中斷優先權排隊的問題。是指多個中斷源同時產生中斷信號時,中斷仲裁器選擇對哪個中斷源優先處理的順序。而這與是否發生中斷服務程序的嵌套

2019-07-03 17:41:00 1

1 1.ARM cortex_m3內核支持256個中斷(16個內核+240外部)和可編程256級中斷優先級的設置,與其相關的中斷控制和中斷優先級控制寄存器(NVIC、SYSTICK等)也都屬于

2019-09-26 15:25:00 2

2 Cortex支行中斷嵌套, 允許高優先級的中斷搶占低優先級的中斷。 Cortex M3/M4可支行多達256級的可編程優先級和128級的搶占, 但有3個系統異常優先級固定, 并且優先級為負數, 高于其它任何異常, 這三個異常分依次為 復位, NMI, Hard Fault.

2019-10-14 16:31:45 12316

12316

寫作原由:因為之前有對stm32 優先級做過研究,但是沒時間把整理的東西發表,最近項目需要2個串口,但是不是兩個串口同時使用,只是隨機使用其中一個,程序對2個串口的優先級需要配置;

2019-10-18 16:46:23 9414

9414

1.ARM cortex_m3內核支持256個中斷(16個內核+240外部)和可編程256級中斷優先級的設置,與其相關的中斷控制和中斷優先級控制寄存器(NVIC、SYSTICK等)也都屬于

2019-12-05 16:45:39 12

12 1.ARM cortex_m3內核支持256個中斷(16個內核+240外部)和可編程256級中斷優先級的設置,與其相關的中斷控制和中斷優先級控制寄存器(NVIC、SYSTICK等)也都屬于

2020-01-03 16:39:04 6

6 Cortex-M0的NVIC沒有優先級分組功能,以及衍生內容

2020-03-01 13:08:31 6237

6237 STM32中斷,及FreeRTOS中斷優先級配置

2020-03-04 11:45:36 10082

10082

中斷優先級是CPU響應中斷的先后順序。中斷優先處理的原則是:

2020-07-17 09:35:40 12282

12282 電子發燒友網為你提供STM32的中斷:搶占優先級和響應優先級資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-03 08:40:37 105

105 電子發燒友網為你提供關于Cortex-M3的中斷優先級描述資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-25 08:43:07 2

2 單片機芯 片: STC12C5A60S2 晶振是11.0592MHZ中斷優先級的基本規則1.低優先級中斷可被高優先級中斷所中斷2.任何中斷都不被同級中斷所中斷然而datashhet里

2021-11-17 09:36:03 6

6 STM32d的中斷優先級由NVIC_IPRx寄存器來配置,IPR的寬度為8bit所以原則上每個中斷可配置的優先級為0~255,數值越小優先級越高,但對于大部分的 Cortex-M3芯片都會精簡

2021-11-19 10:21:04 52

52 msp430的中斷優先級和中斷嵌套 MSP430的中斷優先級按所在的向量的大小排列,中斷向量地址越高優先級就越大,但是默認的MSP430是不能中斷嵌套的,要想在執行某一中斷時能夠響應更高優先級

2021-11-19 19:06:02 11

11 、NVIC中斷優先級管理1. 中斷簡介在Cortex-M3(CM3)內核中,每個中斷的優先級都是用寄存器中的8位來設置的,這樣就有2^8 =256級中斷,意味著可以支持256個中斷,這其中包含了16個內核

2021-11-26 11:36:12 2

2 1 NVIC中斷優先級分組1.1NVIC的中斷向量表Cortex-M3和CM4內核都支持256個中斷,其中包含了16個內核中斷(異常)和240個外部中斷,并且具有256級的可編程中斷設置。但是

2021-11-30 13:36:10 7

7 時會導致系統不穩定,并且systick中斷的優先級還比一般中斷的優先級要高,這可能會導致其他中斷程序被打斷。這里給出一種systick不進中斷的延時方法,精度比一般軟件延時高,且不會占用內核的大量運算

2021-12-01 11:51:05 3

3 Cortex M內核中每個中斷都有一個8位的優先級設置寄存器這個8位的寄存器可以分為搶占優先級和子優先級兩個部分(通過設置優先級組設置)搶占優先級和子優先級有什么用?舉例說明:有兩個中斷A、BA

2021-12-01 11:51:05 4

4 6.Cortex-M系列中斷(1)Coretx-M內核都具有NVCI(嵌套向量中斷控制器)①中斷向量表在STM單片機的啟動.s文件中,可以查找到具體的中斷源與中斷服務函數(2)搶占優先級和響應優先級

2021-12-01 12:36:05 9

9 NVIC中斷優先級管理NVIC中斷優先級分組NVIC中斷優先級設置NVIC總結CM3 內核支持 256 個中斷,其中包含了 16 個內核中斷和 240 個外部中斷,并且具有 256級的可編程中斷設置

2021-12-04 17:06:08 7

7 FreeRTOS中斷優先級和任務優先級架構:Cortex-M3版本:FreeRTOS V9.0.0前言:最開始,我并沒有搞清楚什么是中斷優先級和任務優先級,但看了部分資料后發現這兩個并沒有半毛錢關系

2021-12-04 20:21:10 14

14 的中斷(優先級編號小)肯定是首先得到響應,而且高優先級的中斷可以搶占低優先級的中斷,這個就是中斷嵌套。Cortex-M 處理器的有些中斷是具有固定的優先級的,比如復位、NMI、HardFault,這些中斷的優先級都是負數,優先級也是最高的。Cortex-M處理器有三個固定優先級和256個可編程的優先級

2021-12-31 19:16:04 6

6 stm32中斷優先級分組轉載:http://news.eeworld.com.cn/mcu/article_2018053039408.html一、搶占優先級和響應優先級STM32 的中斷

2022-01-14 15:04:46 3

3 STM32NVIC中斷優先級CM3內核共支持256個中斷,其中包含了16個內核中斷,240個外部中斷,并且具有256級可編程中斷設置。但是stm32并沒有使用CM3內核全部的東西,stm32有84

2022-01-14 15:15:49 2

2 STM32中斷優先級和開關總中斷一,中斷優先級:STM32(Cortex-M3)中的優先級概念STM32(Cortex-M3)中有兩個優先級的概念——搶占式優先級和響應優先級,有人把響應優先級稱作

2022-01-14 15:24:52 13

13 中斷優先級分組(NVIC)值越低,優先級越高

2022-01-14 15:27:55 1

1 硬件中斷優先級中0最高,依次優先級降低。只有當軟件優先級相同時,單片機才進行硬件優先級的判斷,且硬件優先級不能中斷嵌套。軟件配置中斷優先級時,0為優先級最低,依次優先級增加。軟件中斷可以有高優先級中斷搶占低優先級的情況,實現中斷嵌套。...

2022-01-14 15:28:56 1

1 STM32NVIC中斷優先級管理1. 優先級先后順序搶占優先級高于響應優先級(又稱子優先級),數值越小代表的優先級就越高如果兩個中斷的搶占優先級和響應優先級都相同,則看哪個中斷先發生就先執行高優先級

2022-01-14 15:29:56 1

1 使用該內核所有的東西,但對我們來說只是會配置就可以了。對于其中斷數量只是了解就OK了,如果真的有需要用到其所有數量的中斷的大佬,也不會看我的文章了,中斷作為單片機最重要的外設之一,其優先級是最重要的,STM32的中斷優先級配置主要有以下兩個方面一是中斷分組;二是對每一個中斷中斷設置其搶占優先級和響應優先級。

2022-01-14 15:46:00 1

1 STM32F103只用了4個位來表達優先級,因此最多支持16級的可編程優先級(0~15),15為最低優先級。

2022-01-25 18:59:01 1

1 下面就來說說關于Cortex-M的中斷,及FreeRTOS中斷優先級配置原理。

2022-02-08 15:30:51 3

3 首先我們需要知道什么是中斷優先級:中斷優先級是CPU響應中斷的先后順序

2022-05-18 15:10:46 31409

31409

RTOS 內核用戶在配置滴答優先級和頻率方面可能具有的靈活性肯定會給剛接觸內核的開發人員帶來一些困難。

2022-06-29 09:12:33 1942

1942

優先級翻轉簡介:就是高優先級的任務運行起來的效果好像成了低優先級,而低優先級比高優先級先運行;

2023-02-10 15:31:33 2217

2217

本文詳細介紹Cortex-M3中斷優先級相關知識。

2023-03-23 11:45:56 3826

3826

AXI Interrupt Controller支持中斷優先級。 在Vivado Block Design中, bit-0連接的中斷優先級最高

2023-07-11 17:03:58 1736

1736

時,不難發現一個問題,那就是怎么沒有中斷子優先級【或稱響應優先級、副優先級等】的配置?!【當然,很多時候我們或許沒有關注子優先級】如下圖所示,只看到搶占優先級的配置,看不到子優先級的配置項。 上圖是我

2023-09-09 15:32:11 2133

2133

Cortex-M 內核中斷/異常系統、中斷優先級/嵌套 詳解

2023-09-27 15:29:36 3699

3699

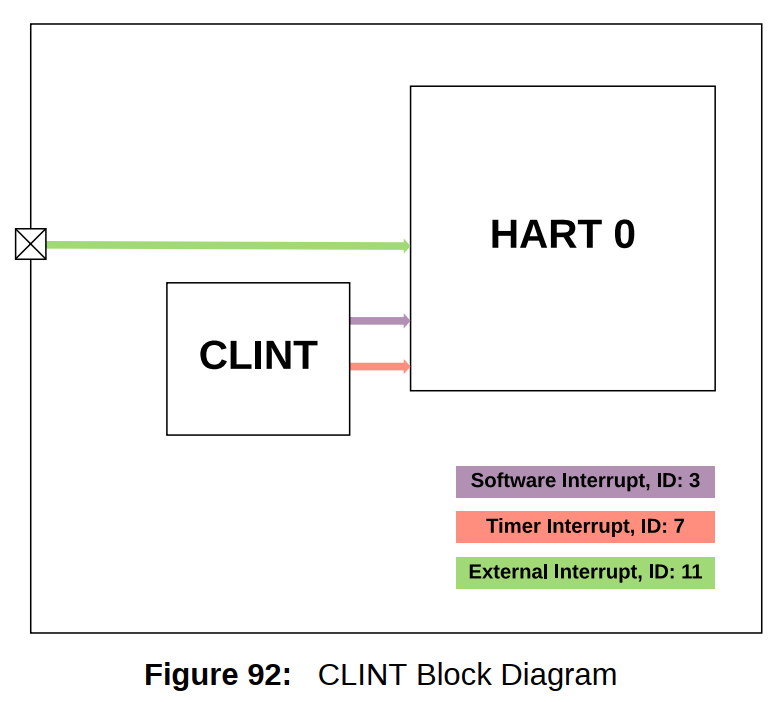

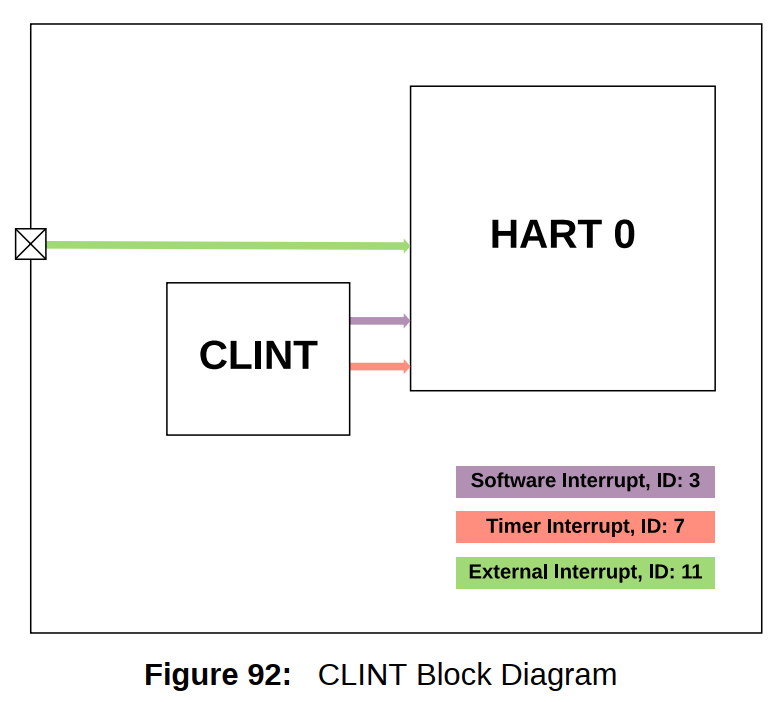

提供軟件、定時器和外部中斷。CLINT 塊還保存與軟件和定時器中斷相關的內存映射控制和狀態寄存器。 CLINT 優先級和搶占 CLINT 具有固定的優先級方案,但不支持給定特權級別內的嵌套中斷(搶占)。然而,較高的特權級別可能會搶占較低的特權級別。CLINT 提供兩種操作模式,直

2023-10-08 09:30:53 1416

1416

看到一個交流群在討論關于【關于STM32中斷優先級的話題】,其中就有小伙伴提到:為什么有些STM32中斷沒有【子優先級】?

2023-10-17 15:50:58 1755

1755

使用GD32 MCU的過程中,大家可能會有以下疑問:中斷優先級如何配置和使用?

2024-01-10 10:30:39 4802

4802

FreeRTOS是一個流行的實時操作系統,它廣泛應用于嵌入式系統開發。在FreeRTOS中,中斷優先級是一個重要的概念,因為它決定了中斷處理的順序和響應時間。 1. 理解中斷優先級 在討論如何設置

2024-09-02 14:17:03 2220

2220 當一個高優先級任務正在等待一個資源,但一個低優先級任務正在持有它,一個中等優先級任務繼續在中間運行時,就會發生優先級反轉——阻止低優先級任務釋放它。

2025-09-09 14:50:22 857

857

電子發燒友App

電子發燒友App

評論