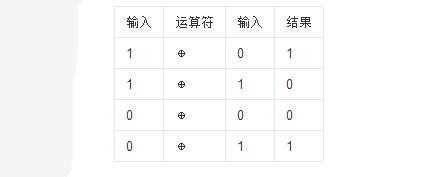

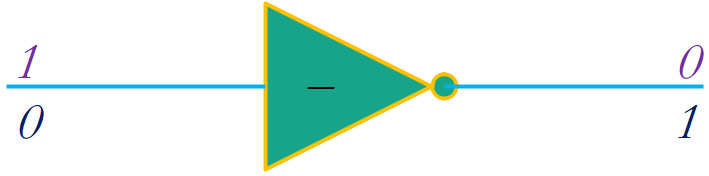

與異或門(mén)一樣,也只有兩個(gè)輸入端,同或門(mén)輸出端的小圓圈說(shuō)明輸出結(jié)果跟異或門(mén)輸出相反,當(dāng)輸入的兩個(gè)電平為相反電平時(shí),同或門(mén)輸出低電平。

2024-02-04 14:08:59 38132

38132

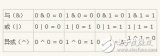

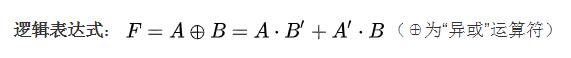

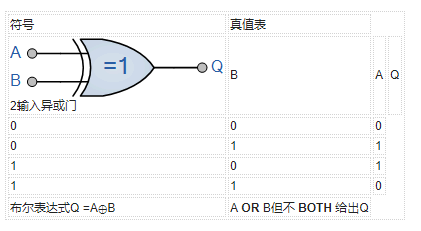

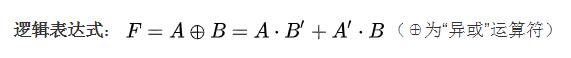

異或門(mén)(XOR gate)是數(shù)字邏輯電路中常用的一種邏輯門(mén)。它的作用是對(duì)兩個(gè)輸入信號(hào)進(jìn)行邏輯運(yùn)算,輸出一個(gè)結(jié)果。

2024-02-04 14:18:46 23552

23552

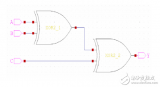

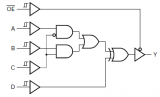

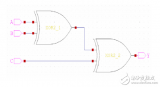

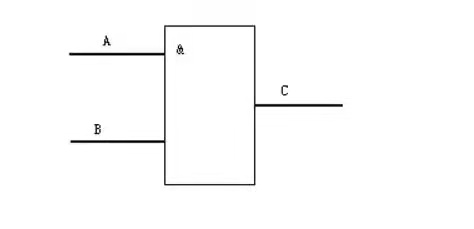

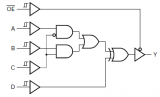

利用74LS00二輸入與非門(mén)實(shí)現(xiàn)“與電路”、“或電路”、“或非電路”、“異或電路”、“同或電路”,要寫(xiě)出以上各電路的邏輯表達(dá)式和真值表,畫(huà)出用二輸入與非門(mén)實(shí)現(xiàn)的邏輯圖并在實(shí)驗(yàn)箱上加以驗(yàn)證

2020-11-04 17:04:17

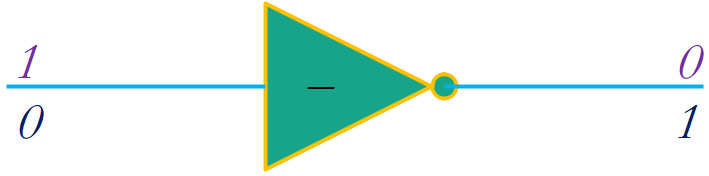

一款Proteus非門(mén)仿真供大家參考

2013-10-31 20:34:10

74LS125 1塊雙全加器 74LS183 1塊實(shí)驗(yàn)報(bào)告要求1. 畫(huà)出實(shí)驗(yàn)邏輯圖, 列出實(shí)驗(yàn)數(shù)據(jù)表格, 填入實(shí)驗(yàn)結(jié)果, 并寫(xiě)出各種門(mén)電路的邏輯函數(shù)表達(dá)式或邏輯功能。2. 敘述在與非門(mén)、或非門(mén)、異或門(mén)、三態(tài)門(mén)實(shí)驗(yàn)中用示波器觀察方波波形的結(jié)果,并說(shuō)明原因。

2008-09-25 17:28:34

組成的邏輯門(mén)電路,可實(shí)現(xiàn)2輸入或3輸入的AND,OR,NAND,NOR,EXOR操作。與非門(mén)或非門(mén)或門(mén)與門(mén)異或門(mén)三輸入與非門(mén)三輸入或非門(mén)三輸入與門(mén)三輸入或門(mén)

2019-07-08 10:36:28

個(gè)1個(gè)1個(gè)1個(gè)布爾表達(dá)式Q = A + B讀為A或B得出Q反相邏輯門(mén)邏輯與非門(mén)符號(hào)真相表乙一種問(wèn)001個(gè)01個(gè)1個(gè)1個(gè)01個(gè)1個(gè)1個(gè)0布爾表達(dá)式Q =A。乙讀為A和B不會(huì)給出Q邏輯或非門(mén)符號(hào)真相表乙

2021-01-27 08:00:00

一、邏輯與或非基礎(chǔ)理論:邏輯與或非,運(yùn)算對(duì)象是布爾值(1或0,真或假),類似于數(shù)字電路的與門(mén),或門(mén),非門(mén)。與關(guān)系運(yùn)算符配合,一般用于選擇語(yǔ)句與循環(huán)語(yǔ)句中1、邏輯與符號(hào)為&&。 參與

2022-01-24 06:30:51

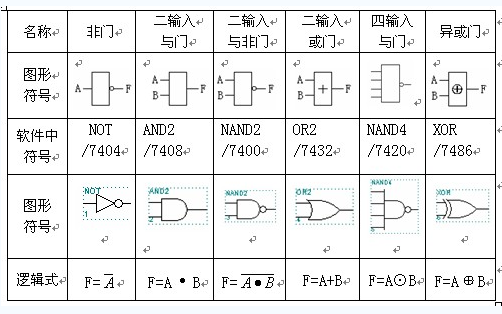

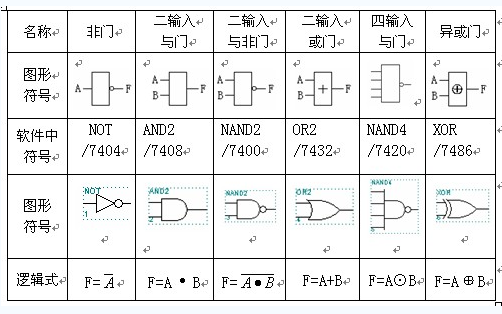

邏輯門(mén)電路電子教案 邏輯門(mén)電路:用以實(shí)現(xiàn)基本和常用邏輯運(yùn)算的電子電路。簡(jiǎn)稱門(mén)電路。 基本和常用門(mén)電路有與門(mén)、或門(mén)、非門(mén)(反相器)、與非門(mén)、或非門(mén)、與或非門(mén)和異或門(mén)等。 邏輯0和1: 電子電路

2009-09-16 16:10:39

TTL邏輯門(mén)與普通邏輯門(mén)的區(qū)別在哪里為什么引入OC門(mén)?

2021-03-29 07:23:21

輸出上給出邏輯“ 1”,否則為邏輯電平“ 0”。然后,這種類型的門(mén)在輸入“邏輯上相等”或“相等”時(shí)給出并輸出“ 1” ,這就是為什么“異或”門(mén)有時(shí)稱為“等效門(mén)”的原因。異或非門(mén)的邏輯符號(hào)只是在其輸出

2021-01-25 09:20:33

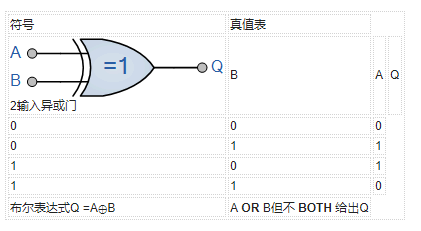

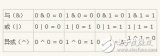

加法器,因?yàn)樗o出兩個(gè)二進(jìn)制數(shù)的總和,因此,其設(shè)計(jì)比其他基本類型的邏輯門(mén)更復(fù)雜。真值表,邏輯符號(hào)和2輸入異或門(mén)的實(shí)現(xiàn)如下所示。數(shù)字邏輯“異或”門(mén)2輸入異或門(mén)符號(hào)真相表2輸入異或門(mén)乙一種問(wèn)00001個(gè)1個(gè)

2021-01-23 08:00:00

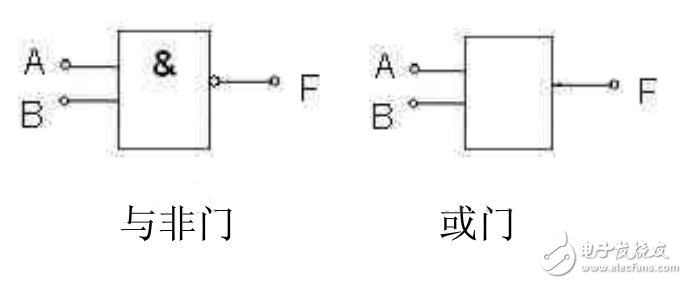

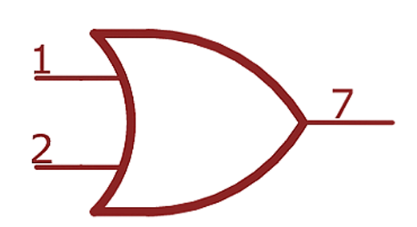

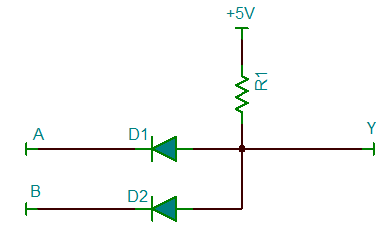

端“或”門(mén),輸入直接連接到晶體管基極。對(duì)于Q的輸出,兩個(gè)晶體管都必須飽和為“ ON” 。邏輯或門(mén)可使用數(shù)字電路產(chǎn)生所需的邏輯功能,并帶有一個(gè)符號(hào),其形狀表示或門(mén)的邏輯操作。數(shù)字邏輯“或”門(mén)類型2輸入

2021-01-20 09:00:00

端“或”門(mén),輸入直接連接到晶體管基極。對(duì)于Q的輸出,兩個(gè)晶體管都必須飽和為“ ON” 。邏輯或門(mén)可使用數(shù)字電路產(chǎn)生所需的邏輯功能,并帶有一個(gè)符號(hào),其形狀表示或門(mén)的邏輯操作。數(shù)字邏輯“或”門(mén)類型2輸入

2021-01-21 08:00:00

具有兩個(gè)或更多邏輯輸入的“與”或“或”門(mén)。商用非門(mén)IC可在單個(gè)IC封裝中的4個(gè)或6個(gè)單獨(dú)的門(mén)中使用。上方非門(mén)符號(hào)結(jié)尾處的“氣泡”(o)表示輸出信號(hào)的信號(hào)反相(互補(bǔ))。但是該氣泡也可能出現(xiàn)在柵極輸入端,以

2021-01-21 09:00:00

的邏輯的邏輯或布爾表達(dá)式NAND門(mén)的是,對(duì)邏輯加法,這是相反的AND門(mén),以及它執(zhí)行對(duì)互補(bǔ)的輸入端。邏輯與非門(mén)的布爾表達(dá)式由單點(diǎn)或句點(diǎn)符號(hào)(。) 表示,在表達(dá)式上帶有線或上劃線( ̄ ̄),以表示與非門(mén)的非或

2021-01-22 08:00:00

直接連接到晶體管的基極。兩個(gè)晶體管都必須截止為“ OFF”,以在Q輸出。邏輯或非門(mén)可使用數(shù)字電路產(chǎn)生所需的邏輯功能,并被賦予一個(gè)符號(hào),其形狀為帶有圓圈的標(biāo)準(zhǔn)或門(mén)的形狀,有時(shí)在其輸出處稱為“反轉(zhuǎn)氣泡”,以

2021-01-22 09:00:00

條導(dǎo)線上,將這些與非門(mén)上的數(shù)據(jù)(狀態(tài)電平)用同一條導(dǎo)線輸送出去.因此,需要一種新的與非門(mén)電路--OC門(mén)來(lái)實(shí)現(xiàn)“線與邏輯”.OC門(mén)主要用于3個(gè)方面:1、實(shí)現(xiàn)與或非邏輯,用做電平轉(zhuǎn)換,用做驅(qū)動(dòng)器.由于OC

2016-08-23 21:39:46

三態(tài)門(mén)和OC門(mén)一、OC門(mén)實(shí)際使用中,有時(shí)需要兩個(gè)或兩個(gè)以上與非門(mén)的輸出端連接在同一條導(dǎo)線上,將這些與非門(mén)上的數(shù)據(jù)(狀態(tài))用同一條導(dǎo)線輸送出去。因此,需要一種新的與非門(mén)電路來(lái)實(shí)現(xiàn)線與邏輯,這種門(mén)電路

2008-05-26 13:01:37

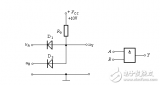

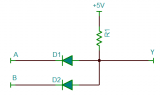

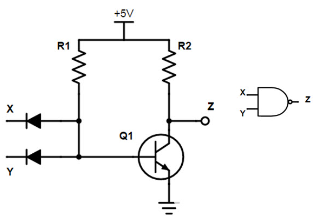

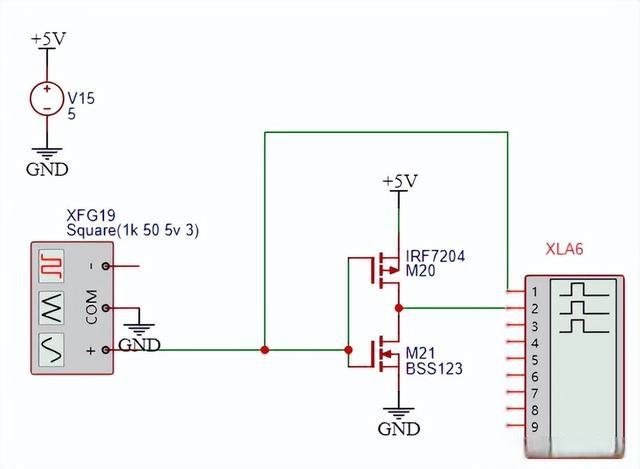

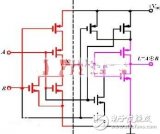

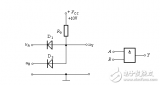

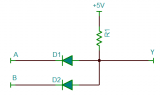

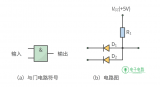

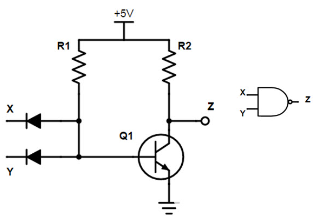

網(wǎng)上看到有用二極管實(shí)現(xiàn)與或非的,想知道同或異或有沒(méi)有可能實(shí)現(xiàn)。看到了一個(gè)說(shuō)可以用三極管實(shí)現(xiàn)的,如下圖

2017-09-18 16:37:36

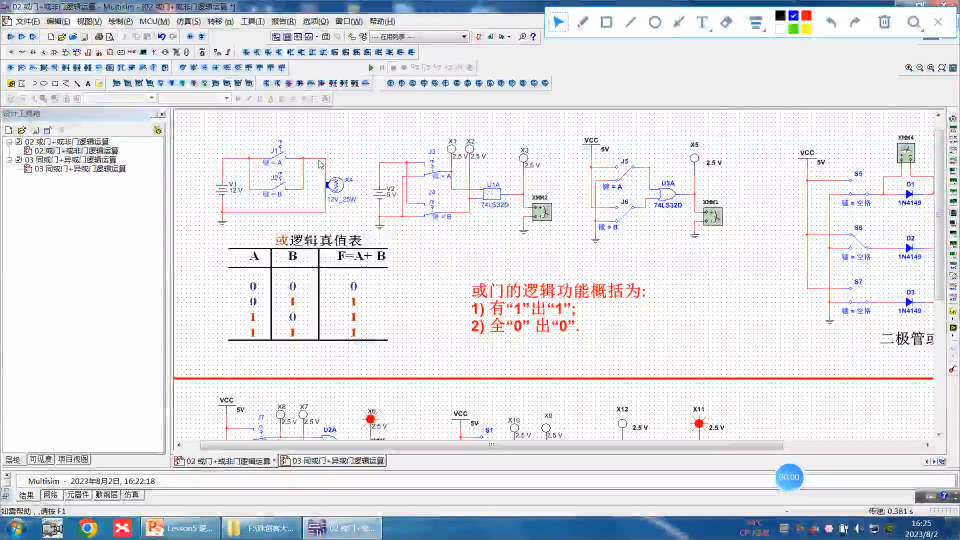

1、集成邏輯門(mén)及其基本應(yīng)用介紹本實(shí)驗(yàn)涉及到的基本邏輯門(mén)有“與門(mén)”、“與非門(mén)”、“或門(mén)”、“或非門(mén)”、“異或門(mén)”和“同或門(mén)”,功能簡(jiǎn)單,實(shí)驗(yàn)時(shí)使用2個(gè)撥動(dòng)開(kāi)關(guān)模擬邏輯門(mén)的輸入信號(hào),通過(guò)LED燈的點(diǎn)亮或

2022-07-01 15:18:51

本帖最后由 樂(lè)樂(lè)leles 于 2019-6-5 11:07 編輯

常用與、或、非邏輯門(mén)芯片引腳圖一、或門(mén):74LS32四路二輸入或門(mén)74HC27 三路三輸入或非門(mén) 二、與門(mén):74LS21二路四輸入與門(mén) 74LS11 三輸入與門(mén) 三、非門(mén):74LS04

2019-05-24 08:49:59

你好。我是在FPGA上設(shè)計(jì)系統(tǒng)的初學(xué)者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想計(jì)算基本15位2輸入加法器的邏輯延遲。如果我能檢查AND門(mén)或OR門(mén)的延遲等

2020-05-25 07:28:24

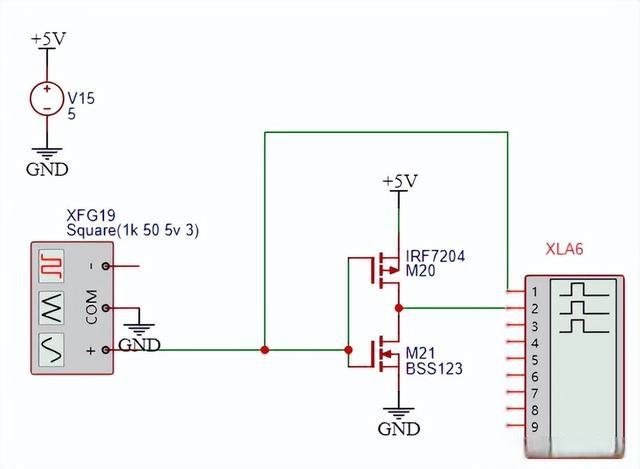

現(xiàn)在我需要一個(gè)邏輯門(mén)器件,與門(mén)和或門(mén)。要求是在輸入時(shí)間為100ns的脈沖信號(hào)(可調(diào)),兩個(gè)輸入,一個(gè)輸出。然后通過(guò)這個(gè)邏輯門(mén)器件之后可以用示波器檢測(cè)到。。。新人也不懂 啊,需要什么型號(hào)的器件呢?

2018-09-17 16:01:36

更多信號(hào),并且僅在所有輸入關(guān)閉時(shí)才打開(kāi)輸出。下面是邏輯門(mén)的真值表和繪圖。 也不或非門(mén)用于接收 2 個(gè)或更多信號(hào),并且僅在所有輸入關(guān)閉時(shí)才打開(kāi)輸出。下面是邏輯門(mén)的真值表和繪圖。 異或異或門(mén)用于接收 2 個(gè)

2022-09-08 07:42:05

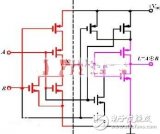

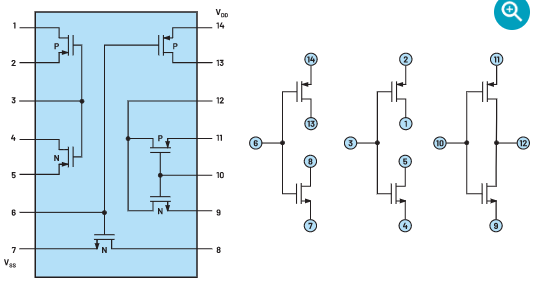

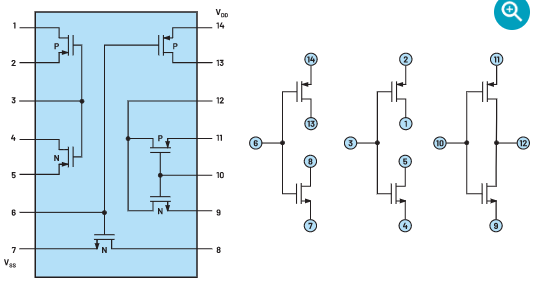

上一節(jié)我們講了由NMOS與PMOS組成的CMOS,也就是一個(gè)非門(mén),各種邏輯門(mén)一般是由MOSFET組成的。上圖左邊是NMOS右邊是PMOS。上圖兩圖是非門(mén)兩種情況,也就是一個(gè)CMOS,輸入高電壓輸出

2023-02-15 14:35:23

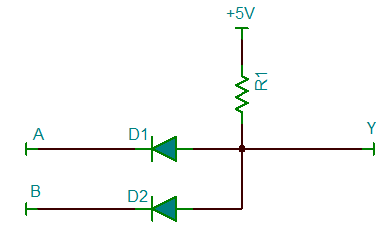

/topic-dianyabjq.html構(gòu)建邏輯門(mén)只不過(guò)是將二極管邏輯與一些電阻組合起來(lái),以實(shí)現(xiàn)必需的邏輯功能。圖2給出了實(shí)現(xiàn)了邏輯“與(AND)”和邏輯“或(OR)”功能的簡(jiǎn)單電路,以及略為復(fù)雜的邏輯“異或(XOR)”功能的電路。圖中

2011-12-23 11:49:06

組成的邏輯門(mén)電路,可實(shí)現(xiàn)2輸入或3輸入的AND,OR,NAND,NOR,EXOR操作。與非門(mén)或非門(mén)或門(mén)與門(mén)異或門(mén)三輸入與非門(mén)三輸入或非門(mén)三輸入與門(mén)三輸入或門(mén)

2018-10-11 17:44:32

列出4中能做非門(mén)的邏輯門(mén)(非門(mén)除外)

2010-04-29 18:54:58

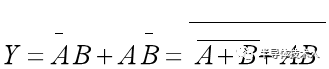

異成門(mén)邏輯符號(hào)圖/同或門(mén)邏輯符號(hào)圖

2019-10-23 03:49:43

“^”是按位異或那異或的符號(hào)是什么呢?

2014-05-25 18:56:53

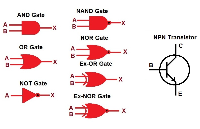

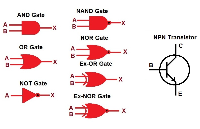

“門(mén)”電路是什么?是門(mén)里的電路嗎? 并不是哦,門(mén)電路是一種邏輯關(guān)系電路,用來(lái)實(shí)現(xiàn)基本的邏輯運(yùn)算和符合邏輯元素的單元電路。所以像平時(shí)聽(tīng)見(jiàn)的與門(mén),或門(mén),非門(mén),與非門(mén),異或門(mén)都是門(mén)電路。 (圖

2023-04-13 17:44:29

電子技術(shù)--門(mén)電路與邏輯代數(shù)了解數(shù)字電路的特點(diǎn)以及數(shù)制和編碼的概念掌握與門(mén)、或門(mén)、與非門(mén)、異或門(mén)的邏輯符號(hào)、邏輯功能和表示方法了解TTL和CMOS門(mén)電路的特點(diǎn)以

2010-04-12 17:50:45 0

0 實(shí)驗(yàn)?zāi)康?. 掌握與非門(mén)、或非門(mén)、與或非門(mén)及異或門(mén)的邏輯功能。2. 了解三態(tài)門(mén)的邏輯功能以及禁止?fàn)顟B(tài)的判別方法。了解三態(tài)門(mén)的應(yīng)用。3. 掌握組合邏輯電路的設(shè)計(jì)和實(shí)

2010-08-18 14:50:44 0

0 異成門(mén)和同或門(mén)的邏輯符號(hào)圖:

2009-04-06 23:30:10 4821

4821

TTL或非門(mén)、集電極開(kāi)路門(mén)和三態(tài)門(mén)電路

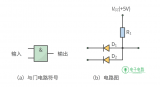

1.TTL或非門(mén)

下圖為T(mén)TL或非門(mén)的邏輯電路及其代表符號(hào)。

2009-04-07 00:11:59 17425

17425

下圖為T(mén)TL或非門(mén)的邏輯電路及其代表符號(hào)。

由圖可見(jiàn) ,或非邏輯功能是對(duì)TTL

2009-04-07 00:13:30 9669

9669

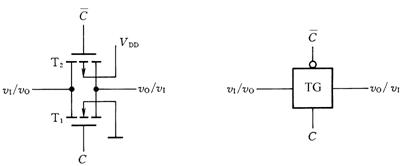

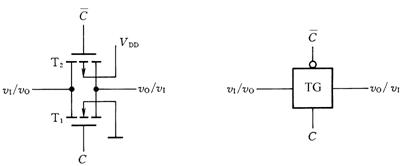

CMOS傳輸門(mén)的電路結(jié)構(gòu)和邏輯符號(hào)

2009-07-15 19:06:52 12534

12534

異或門(mén)電路

異或門(mén)和同或門(mén)的邏輯符號(hào)如下圖所示。

2009-07-16 07:55:17 22523

22523

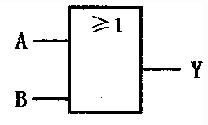

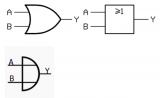

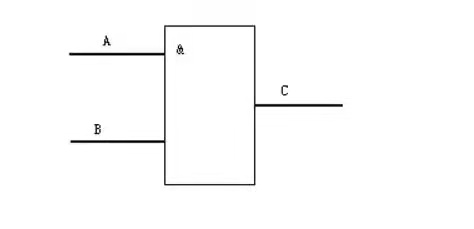

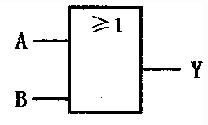

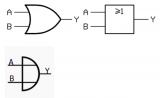

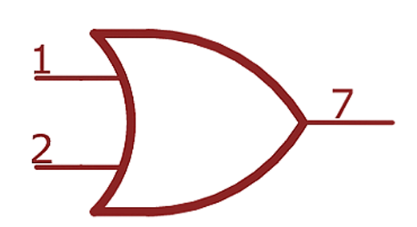

或門(mén)符號(hào)

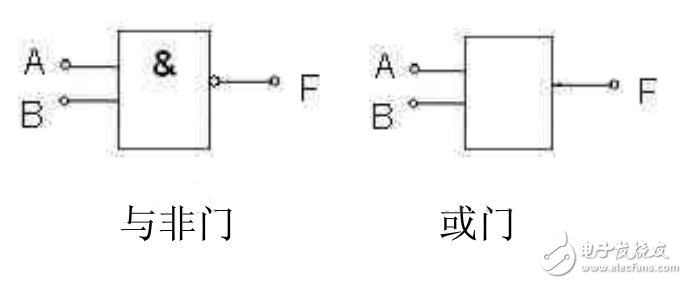

實(shí)現(xiàn)或邏輯關(guān)系的門(mén)電路叫做或門(mén)電路。圖1為2輸入端或門(mén)邏輯符號(hào),方框 中符號(hào)“≥1”表示只要滿足一個(gè)或一個(gè)以上的條

2009-07-16 08:00:43 25320

25320

同或門(mén)符號(hào),同或門(mén)邏輯符號(hào)

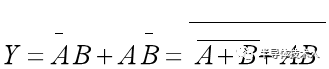

異或與同或是一對(duì)互補(bǔ)的邏輯運(yùn)算,因?yàn)樗兄庇^的邏輯意義

2009-07-16 08:04:17 122096

122096

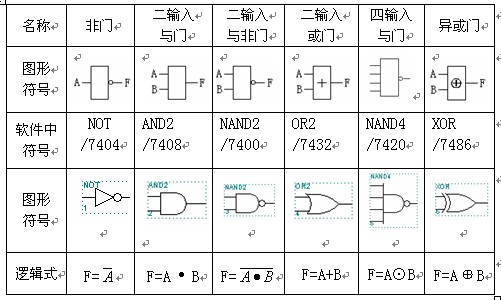

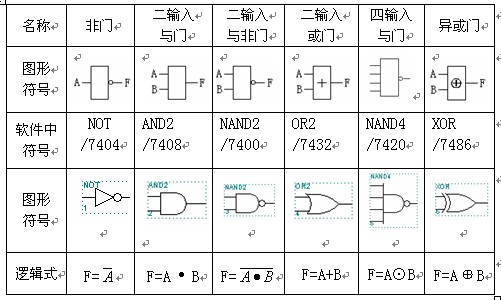

邏輯門(mén)電路符號(hào)圖(與門(mén)或門(mén)非門(mén)異或門(mén)同或門(mén))

2009-07-16 08:17:00 142949

142949

常用邏輯門(mén)及其符號(hào)簡(jiǎn)介

2009-12-03 10:59:42 63103

63103 或門(mén),或門(mén)是什么意思

或邏輯及或門(mén):

或邏輯指的是:在決定某事件的諸條件中,只要有一個(gè)或一個(gè)以上的條件具備,該事件就會(huì)發(fā)生

2010-03-08 11:39:13 20411

20411 Cool-ORing冷或門(mén)系列-60V,12A 全功能有源或門(mén)方案,PI2127

2016-01-07 10:20:17 4

4 邏輯門(mén)是邏輯電路的基本組成部分,可以由晶體管來(lái)構(gòu)成,邏輯門(mén)大致可以分為基本門(mén)、萬(wàn)用門(mén)和延伸門(mén)等三種,其中基本門(mén)又可以分為與門(mén)、或門(mén)和非門(mén)三種。邏輯門(mén)可以使信號(hào)的高低電平轉(zhuǎn)化為響應(yīng)的邏輯信號(hào),從而實(shí)現(xiàn)邏輯運(yùn)算

2017-05-22 14:16:38 61883

61883

6.2 EOR邏輯異或指令 1.指令的編碼格式 邏輯異或EOR(Exclusive OR)指令將寄存器《Rn》中的值和《shifter_operand》的值執(zhí)行按位異或操作,并將執(zhí)行結(jié)果存儲(chǔ)到目的

2017-10-18 13:38:16 1

1 異或門(mén) (英語(yǔ):Exclusive-OR gate,簡(jiǎn)稱XOR gate,又稱EOR gate、ExOR gate)是數(shù)字邏輯中實(shí)現(xiàn)邏輯異或的邏輯門(mén)。有多個(gè)輸入端、1個(gè)輸出端,多輸入異或門(mén)可由2輸入

2017-11-19 17:59:49 73486

73486

異或門(mén) (英語(yǔ):Exclusive-OR gate,簡(jiǎn)稱XOR gate,又稱EOR gate、ExOR gate)是數(shù)字邏輯中實(shí)現(xiàn)邏輯異或的邏輯門(mén)。有多個(gè)輸入端、1個(gè)輸出端,多輸入異或門(mén)可由2

2017-11-20 08:54:42 107772

107772

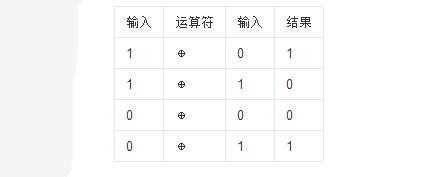

異或,是一個(gè)數(shù)學(xué)運(yùn)算符,英文為exclusive OR,縮寫(xiě)為xor,應(yīng)用于邏輯運(yùn)算。異或的數(shù)學(xué)符號(hào)為“⊕”,計(jì)算機(jī)符號(hào)為“xor”。

2017-11-28 11:19:15 125005

125005

異或符號(hào)在word里的輸入方法一、輸入 “+ ”并選中 “+ ”,然后進(jìn)入菜單“格式”-》“中文版式”-》“帶圈字符”;

2017-11-28 11:40:51 29505

29505 異或門(mén)是數(shù)字邏輯中實(shí)現(xiàn)邏輯異或的邏輯門(mén)。有多個(gè)輸入端、1個(gè)輸出端,多輸入異或門(mén)可由2輸入異或門(mén)構(gòu)成。若兩個(gè)輸入的電平相異,則輸出為高電平1;

2017-11-28 12:07:05 68904

68904

本文為大家介紹與非門(mén)構(gòu)成或門(mén)、與門(mén)、非門(mén)方法。

2018-01-12 17:24:56 130741

130741

本文為大家介紹二極管與、或門(mén),三極管非門(mén)電路原理。

2018-01-14 09:21:33 144558

144558

本文開(kāi)始對(duì)邏輯異或運(yùn)算進(jìn)行了介紹,介紹了邏輯異或運(yùn)算性質(zhì),其次分析了邏輯異或運(yùn)算該怎么算,最后介紹了邏輯異或運(yùn)算的應(yīng)用。

2018-03-01 15:11:26 109551

109551

本文開(kāi)始介紹了同或運(yùn)算的應(yīng)用領(lǐng)域與同或運(yùn)算符號(hào)和公式,其次介紹了同或運(yùn)算真值表和邏輯電路,最后介紹了java語(yǔ)言中同或運(yùn)算的實(shí)現(xiàn)程序。

2018-03-28 16:00:37 20052

20052

方案則是用一個(gè)集成場(chǎng)效應(yīng)管和控制芯片的元件, 來(lái)代替或門(mén)二極管。優(yōu)點(diǎn)是把 功耗減少10倍, 故障監(jiān)測(cè)準(zhǔn)確度提升2倍, 反應(yīng)時(shí)間快25%。

2018-06-19 14:05:00 4276

4276

verilog實(shí)現(xiàn)反相器,2輸入與門(mén)、2輸入或門(mén)、2輸入與非門(mén)、2輸入或非門(mén)、2輸入異或門(mén)、2輸入同或門(mén);

2018-07-01 10:28:00 7312

7312 邏輯或門(mén)是一種數(shù)字邏輯電路,僅當(dāng)其一個(gè)或多個(gè)輸入為高電平時(shí),其輸出變?yōu)楦唠娖街?b class="flag-6" style="color: red">邏輯電平因此邏輯“或”門(mén)可以正確地描述為“包含OR門(mén)”,因?yàn)楫?dāng)兩個(gè)輸入都為真(HIGH)時(shí)輸出為真。然后我們可以將2輸入邏輯或門(mén)的操作定義為。

2019-06-26 14:45:12 20250

20250

邏輯與非門(mén)是數(shù)字邏輯與門(mén)和非門(mén)串聯(lián)連接在一起的組合,NAND (非與)門(mén)具有當(dāng)輸入的ALL處于邏輯電平“1”時(shí),輸出通常處于邏輯電平“1”并且僅“低”到邏輯電平“0”。邏輯與非門(mén)是我們之前看到的AND門(mén)的反向或“互補(bǔ)”形式。

2019-06-26 14:20:46 11837

11837

邏輯或門(mén)控柵極是數(shù)字邏輯“或”門(mén)與串聯(lián)連接在一起的反相器或非門(mén)的組合,包含NOR(非或)門(mén)的輸出為當(dāng)輸入的ANY處于邏輯電平“1”時(shí),它通常處于邏輯電平“1”并且僅“低”到邏輯電平“0”。邏輯NOR門(mén)是我們之前看到的包含OR門(mén)的反向或“互補(bǔ)”形式。

2019-06-26 14:13:52 35985

35985

異或邏輯功能是一種非常有用的電路,可用于許多不同類型的計(jì)算電路,兩種類型的數(shù)字邏輯門(mén)雖然它們本身不是基本門(mén),因?yàn)樗鼈兪峭ㄟ^(guò)將其他邏輯門(mén)組合在一起構(gòu)建的,但它們的輸出布爾函數(shù)非常重要,可以被視為完整的邏輯門(mén)。這兩個(gè)“混合”邏輯門(mén)稱為異或(Ex-OR)門(mén),它與異或(Ex-NOR)門(mén)互為補(bǔ)充。

2019-06-26 14:08:15 56447

56447

Exclusive-NOR Gate功能是一個(gè)數(shù)字邏輯門(mén),是Exclusive-OR功能的反向或互補(bǔ)形式,基本上,“異或”門(mén)是一個(gè)組合異或門(mén)和非門(mén),但有一個(gè)類似于標(biāo)準(zhǔn)NOR門(mén)的真值表,因?yàn)樗妮敵鐾ǔ?b class="flag-6" style="color: red">邏輯電平“1”,當(dāng)ANY時(shí),輸出“低”到邏輯電平“0”其輸入處于邏輯電平“1”。

2019-06-26 14:02:57 21187

21187

用以實(shí)現(xiàn)基本邏輯運(yùn)算和復(fù)合邏輯運(yùn)算的單元電路稱為門(mén)電路。常用的門(mén)電路在邏輯功能上有與門(mén)、或門(mén)、非門(mén)、與非門(mén)、或非門(mén)、與或非門(mén)、異或門(mén)等幾種。

2019-08-15 15:42:44 16481

16481 上表包括與門(mén),或門(mén),非門(mén),同或門(mén),異或門(mén),還有這些門(mén)電路的邏輯表達(dá)式,

2019-08-31 11:47:16 41142

41142

在數(shù)字電路中,所謂“門(mén)”就是只能實(shí)現(xiàn)基本邏輯關(guān)系的電路。最基本的邏輯關(guān)系是與、或、非,最基本的邏輯門(mén)是與門(mén)、或門(mén)和非門(mén)。邏輯門(mén)可以用電阻、電容、二極管、三極管等分立原件構(gòu)成,成為分立元件門(mén)。也可以將門(mén)電路的所有器件及連接導(dǎo)線制作在同一塊半導(dǎo)體基片上,構(gòu)成集成邏輯門(mén)電路。

2019-11-05 11:28:23 22565

22565

方案則是用一個(gè)集成場(chǎng)效應(yīng)管和控制芯片的元件, 來(lái)代替或門(mén)二極管。優(yōu)點(diǎn)是把 功耗減少10倍, 故障監(jiān)測(cè)準(zhǔn)確度提升2倍, 反應(yīng)時(shí)間快25%。

2020-07-02 12:03:00 3075

3075 常見(jiàn)的晶體管有二極管、三極管和MOS管,主要的邏輯門(mén)電路:與門(mén)、或門(mén)、非門(mén)、與非門(mén)、或非門(mén)、異或門(mén)等,這篇文章介紹用晶體管搭建常見(jiàn)的邏輯門(mén)電路。

2020-11-01 11:03:30 17072

17072

異或,英文為exclusive OR,縮寫(xiě)成xor。異或(eor)是一個(gè)數(shù)學(xué)運(yùn)算符。它應(yīng)用于邏輯運(yùn)算。異或的數(shù)學(xué)符號(hào)為“⊕”,計(jì)算機(jī)符號(hào)為“eor”。

2020-11-19 16:00:25 34608

34608 異或門(mén) (英語(yǔ):Exclusive-OR gate,簡(jiǎn)稱XOR gate,又稱EOR gate、ExOR gate)是數(shù)字邏輯中實(shí)現(xiàn)邏輯異或的邏輯門(mén)。有多個(gè)輸入端、一個(gè)輸出端,多輸入異或門(mén)可由兩輸入

2020-11-19 16:06:26 104679

104679

中的1和0表示。 在數(shù)字電路中,門(mén)電路是數(shù)字電路的基本單元,很多復(fù)雜的數(shù)字電路都是由這些基本的單元組成的。最基本的門(mén)電路是與門(mén)、或門(mén)、非門(mén)。 ? 這3種基本的邏輯門(mén)電路通過(guò)相互組合,還能組合出與非門(mén)、或非門(mén)、同或門(mén)、

2021-02-01 13:39:55 38453

38453

或門(mén)英文名為OR gate,功能是實(shí)現(xiàn)邏輯和基本運(yùn)算。如果多個(gè)條件下,只要有一個(gè)條件得到滿足,某事件就會(huì)發(fā)生,這就是“或”邏輯關(guān)系。具有“或”邏輯關(guān)系的電路叫做或門(mén)。

2021-07-15 11:30:50 70334

70334 上篇文章我們講解了與邏輯, 緩沖器和非門(mén)只差一個(gè)圈嗎? 而與之對(duì)應(yīng)的就是或邏輯,在數(shù)字電路中與、或、非為三大基礎(chǔ)邏輯門(mén)電路,其后續(xù)的與非、或非、同或、異或,都是建立在基礎(chǔ)邏輯門(mén)電路的基礎(chǔ)上邊。 那么

2021-10-29 11:09:43 10760

10760

翻轉(zhuǎn)機(jī)制,在單納米賽道上模擬實(shí)現(xiàn)了“異或門(mén)”, “或門(mén)”, “與非門(mén)”等7種基本布爾邏輯門(mén)的構(gòu)建及其重構(gòu)過(guò)程。

2022-05-11 11:54:49 1994

1994 邏輯門(mén)是許多數(shù)字電子電路的基礎(chǔ)。從基本的觸發(fā)器到微控制器,邏輯門(mén)構(gòu)成了比特如何存儲(chǔ)和處理的基本原理。他們使用算術(shù)邏輯陳述系統(tǒng)的每個(gè)輸入和輸出之間的關(guān)系。有許多不同類型的邏輯門(mén),它們中的每一個(gè)都有

2022-08-23 15:38:29 4150

4150

邏輯門(mén)是數(shù)字世界中的基本元素,之前已經(jīng)介紹過(guò)基本的邏輯門(mén)。這些基本的邏輯門(mén)可以由通用門(mén)構(gòu)成。數(shù)字邏輯中有兩個(gè)通用門(mén),即與非門(mén)(NAND Gate)和或非門(mén)(NOR Gate)。

2022-09-12 14:50:00 13786

13786

邏輯門(mén)電路是一種電路設(shè)計(jì),用于處理數(shù)字信號(hào)(僅包括0和1)。 它們使用邏輯門(mén)來(lái)執(zhí)行不同的邏輯操作,如與門(mén)、或門(mén)、非門(mén)、異或門(mén)等,這些門(mén)基于布爾代數(shù)。 邏輯門(mén)電路通常使用晶體管、集成電路或其他電子元件實(shí)現(xiàn)。

2023-03-23 11:45:26 9378

9378

邏輯門(mén)(LogicGates)是集成電路設(shè)計(jì)的基本組件,通過(guò)晶體管或MOS管組成的簡(jiǎn)單邏輯門(mén),可以對(duì)輸入的電平(高或低)進(jìn)行一些簡(jiǎn)單的邏輯運(yùn)算處理,而簡(jiǎn)單的邏輯門(mén)可以組合成為更復(fù)雜的邏輯運(yùn)算,是超大規(guī)模電路集成設(shè)計(jì)的基礎(chǔ)。

2023-04-30 09:14:00 5462

5462

常見(jiàn)的晶體管有二極管、三極管和MOS管,主要的邏輯門(mén)電路:與門(mén)、或門(mén)、非門(mén)、與非門(mén)、或非門(mén)、異或門(mén)等,這篇文章介紹用晶體管搭建常見(jiàn)的邏輯門(mén)電路。

2023-04-26 14:51:33 14399

14399

本實(shí)驗(yàn)活動(dòng)的目標(biāo)是進(jìn)一步強(qiáng)化上一個(gè)實(shí)驗(yàn)活動(dòng) “使用CD4007陣列構(gòu)建CMOS邏輯功能” 中探討的CMOS邏輯基本原理,并獲取更多使用復(fù)雜CMOS門(mén)級(jí)電路的經(jīng)驗(yàn)。具體而言,您將了解如何使用CMOS傳輸門(mén)和CMOS反相器來(lái)構(gòu)建傳輸門(mén)異或(XOR)和異或非邏輯功能。

2023-05-29 14:17:17 5354

5354

引言:在板極的邏輯控制中,基本邏輯門(mén)的使用特別廣泛,包括與門(mén),或門(mén)和外置信號(hào)驅(qū)動(dòng)器,緩沖器等等,基本邏輯門(mén)相比于分立元件搭建的邏輯門(mén),抗干擾能力和驅(qū)動(dòng)能力更強(qiáng),信號(hào)質(zhì)量更好。運(yùn)用最基本的邏輯門(mén)電路,使用邏輯代數(shù)可以構(gòu)建出更復(fù)雜的控制邏輯以此滿足設(shè)計(jì)需求。

2023-07-04 15:06:21 8237

8237

異或門(mén) (簡(jiǎn)稱XOR gate)是數(shù)字邏輯中實(shí)現(xiàn)邏輯異或的邏輯門(mén)。

2023-07-06 16:17:00 5420

5420

為什么異或門(mén)又稱可控反相器? 異或門(mén)是一種常見(jiàn)的邏輯門(mén),其中包含兩個(gè)輸入管腳和一個(gè)輸出管腳。在邏輯運(yùn)算中,異或門(mén)的輸出值與兩個(gè)輸入值的邏輯值不同,稱為“異或”,也被稱為“可控反相器”。 在數(shù)

2023-09-12 10:51:22 10783

10783 介紹:

邏輯門(mén)是任何數(shù)字系統(tǒng)的基本構(gòu)建塊。它是一種具有一個(gè)或多個(gè)輸入且只有一個(gè)輸出的電子電路。輸入和輸出之間的關(guān)系是基于一定的邏輯的。

基于此,邏輯門(mén)被命名為與門(mén)、或門(mén)、非門(mén)、與非門(mén)、或非門(mén)、異或門(mén)

2023-09-25 11:40:35 1580

1580

“門(mén)”電路是什么?是門(mén)里的電路嗎? 并不是哦,門(mén)電路是一種邏輯關(guān)系電路,用來(lái)實(shí)現(xiàn)基本的邏輯運(yùn)算和符合邏輯元素的單元電路。所以像平時(shí)聽(tīng)見(jiàn)的與門(mén),或門(mén),非門(mén),與非門(mén),異或門(mén)都是門(mén)電路。 (圖:與門(mén)

2023-11-07 14:42:23 2306

2306

邏輯門(mén)是數(shù)字電路中的基本構(gòu)建塊,它們執(zhí)行基本的邏輯運(yùn)算,如與(AND)、或(OR)、非(NOT)、異或(XOR)等。邏輯門(mén)芯片是集成了多個(gè)邏輯門(mén)的集成電路,廣泛應(yīng)用于計(jì)算機(jī)、通信、自動(dòng)化控制等領(lǐng)域

2024-09-24 10:48:10 6719

6719 。基本邏輯門(mén)包括: 非門(mén)(NOT) :只有一個(gè)輸入和一個(gè)輸出,輸出是輸入的邏輯反。 與門(mén)(AND) :多個(gè)輸入,只有當(dāng)所有輸入都為高電平時(shí),輸出才為高電平。 或門(mén)(OR) :多個(gè)輸入,只要有一個(gè)輸入為高電平,輸出就為高電平。 異或門(mén)(XOR) :兩個(gè)

2024-11-18 10:36:44 2520

2520 和編程中有著廣泛的應(yīng)用。 邏輯異或的定義 邏輯異或,也稱為異或運(yùn)算,是一種二元邏輯運(yùn)算,用符號(hào)“⊕”表示。對(duì)于兩個(gè)輸入值A(chǔ)和B,邏輯異或的真值表如下: A B A ⊕ B 0 0 0 0 1 1 1 0 1 1 1 0 從真值表可以看出,只有當(dāng)兩個(gè)輸入值不同時(shí),邏輯異或的結(jié)果才為

2024-11-19 09:40:24 4237

4237 ,Python中的 ^ 符號(hào)實(shí)際上是一個(gè)按位異或運(yùn)算符,用于對(duì)整數(shù)的二進(jìn)制表示進(jìn)行異或操作。 盡管如此,我們?nèi)匀豢梢酝ㄟ^(guò)一些方法來(lái)實(shí)現(xiàn)邏輯異或的功能,即當(dāng)兩個(gè)布爾值不同時(shí)為真,相同時(shí)為假。這可以通過(guò)使用邏輯運(yùn)算符來(lái)實(shí)現(xiàn),而不是直接使用 ^ (因?yàn)?^ 在

2024-11-19 09:46:00 1289

1289 邏輯異或(Exclusive OR,簡(jiǎn)稱XOR)和邏輯或(OR)是數(shù)字邏輯和編程中兩種基本的邏輯運(yùn)算,它們各自具有獨(dú)特的功能和應(yīng)用場(chǎng)景。以下是對(duì)邏輯異或和邏輯或的比較分析: 一、定義與功能 邏輯異或

2024-11-19 09:48:34 2569

2569 邏輯異或(Exclusive OR,簡(jiǎn)稱XOR)與異或門(mén)的工作原理是數(shù)字邏輯電路中的核心概念。以下是對(duì)邏輯異或和異或門(mén)工作原理的介紹: 一、邏輯異或的定義 邏輯異或是一種邏輯運(yùn)算,其輸出取決于兩個(gè)

2024-11-19 09:52:34 6225

6225 在計(jì)算機(jī)科學(xué)和數(shù)據(jù)處理領(lǐng)域,邏輯異或(XOR)是一種基本的位運(yùn)算,它在多個(gè)方面展現(xiàn)出其獨(dú)特的價(jià)值。 邏輯異或的原理 邏輯異或,也稱為“異或”(Exclusive OR),是一種二進(jìn)制運(yùn)算,其基本規(guī)則

2024-11-19 09:54:00 1311

1311 邏輯異或(Exclusive OR,簡(jiǎn)稱XOR)在理解和應(yīng)用過(guò)程中,確實(shí)存在一些常見(jiàn)的誤區(qū)。以下是對(duì)這些誤區(qū)的分析以及相應(yīng)的解決方法: 一、常見(jiàn)誤區(qū) 混淆邏輯異或與按位異或 : 邏輯異或通常

2024-11-19 09:56:20 1481

1481 中微愛(ài)芯推出可配置多功能邏輯門(mén)電路AiP74LVC1G99,該電路可配置為多種三態(tài)邏輯門(mén),如“與門(mén)”、“與非門(mén)”、“或門(mén)”、“或非門(mén)”、“異或門(mén)”、“同或門(mén)”、“反相器”、“緩沖器”以及“多路復(fù)用器”,用法靈活多樣。

2025-06-17 10:52:56 1055

1055

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論