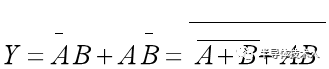

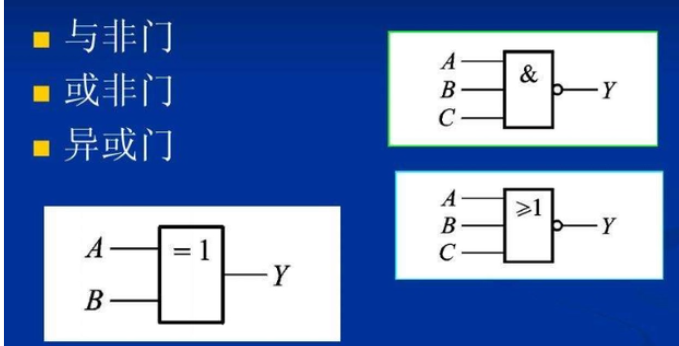

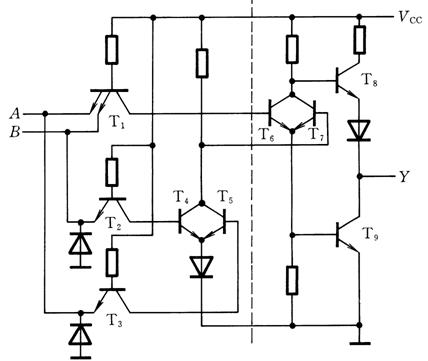

異或門(mén) (簡(jiǎn)稱XOR gate)是數(shù)字邏輯中實(shí)現(xiàn)邏輯異或的邏輯門(mén)。有多個(gè)輸入端、一個(gè)輸出端,多輸入異或門(mén)可由兩輸入異或門(mén)構(gòu)成。若兩個(gè)輸入的電平相異,則輸出為高電平1;若兩個(gè)輸入的電平相同,則輸出為低電平0。即如果兩個(gè)輸入不同,則異或門(mén)輸出高電平1。

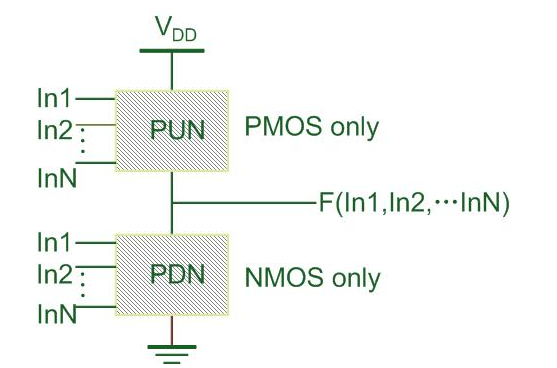

雖然異或不是開(kāi)關(guān)代數(shù)的基本運(yùn)算之一,但是在實(shí)際運(yùn)用中相當(dāng)普遍地使用分立的異或門(mén)。大多數(shù)開(kāi)關(guān)技術(shù)不能直接實(shí)現(xiàn)異或功能,而是使用多個(gè)門(mén)組合設(shè)計(jì)。

##############################################

##############################################

隨著超大規(guī)模集成電路的復(fù)雜程度不斷提高,電路制造后的測(cè)試所需的時(shí)間和經(jīng)濟(jì)成本也不斷增加。電路在設(shè)計(jì)時(shí)向電路添加一些特殊的結(jié)構(gòu)(例如掃描鏈和內(nèi)建自測(cè)試),能夠大大方便之后的電路測(cè)試。這樣的設(shè)計(jì)被即為可測(cè)試性設(shè)計(jì),它們使電路更加復(fù)雜,但是卻能憑借更簡(jiǎn)捷的測(cè)試降低整個(gè)項(xiàng)目的成本。

隨著超大規(guī)模集成電路的集成度不斷提高,同時(shí)市場(chǎng)競(jìng)爭(zhēng)壓力的不斷增加,集成電路設(shè)計(jì)逐漸引入了可重用設(shè)計(jì)方法學(xué)。可重用設(shè)計(jì)方法學(xué)的主要意義在于,提供IP核(知識(shí)產(chǎn)權(quán)核)的供應(yīng)商可以將一些已經(jīng)預(yù)先完成的設(shè)計(jì)以商品的形式提供給設(shè)計(jì)方,后者可以將IP核作為一個(gè)完整的模塊在自己的設(shè)計(jì)項(xiàng)目中使用。

-

CMOS

+關(guān)注

關(guān)注

58文章

6217瀏覽量

242817 -

高電平

+關(guān)注

關(guān)注

6文章

225瀏覽量

22819

發(fā)布評(píng)論請(qǐng)先 登錄

異或門(mén)的應(yīng)用電路圖

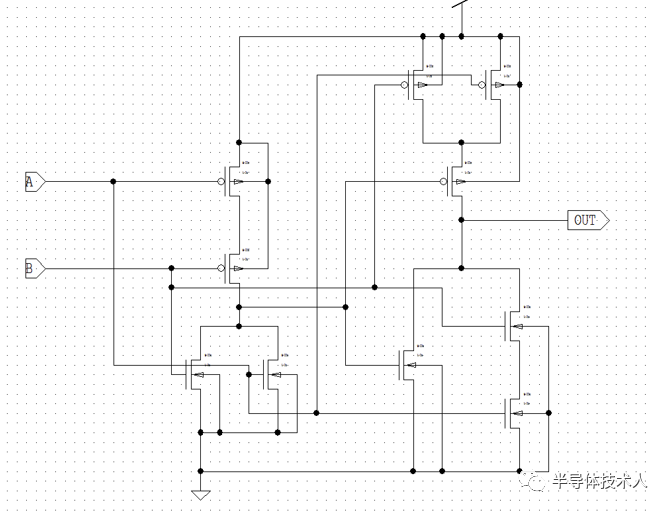

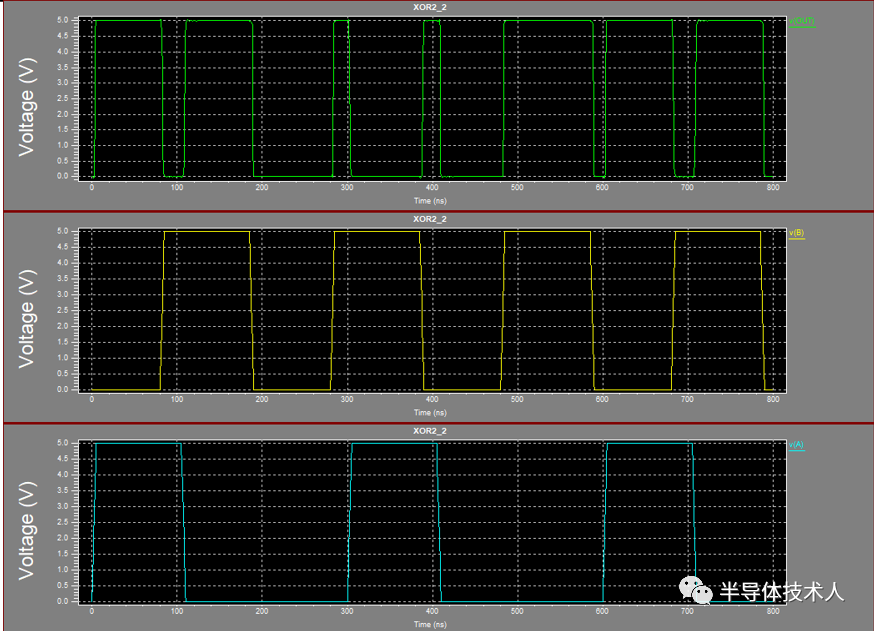

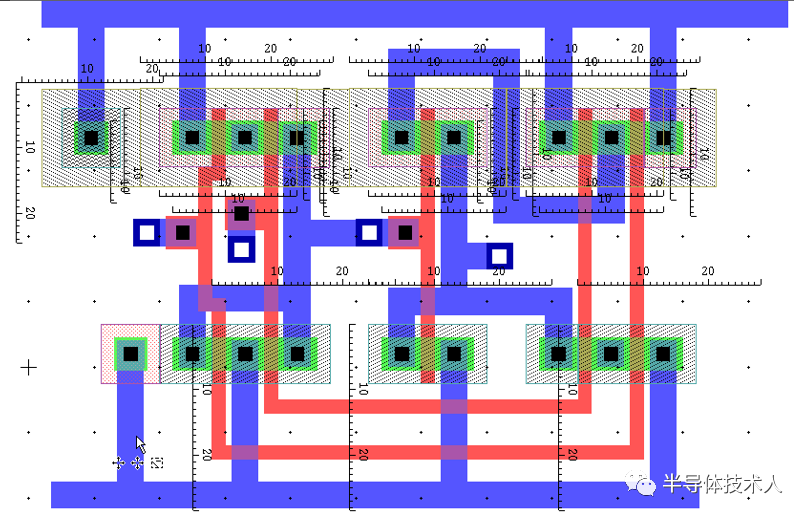

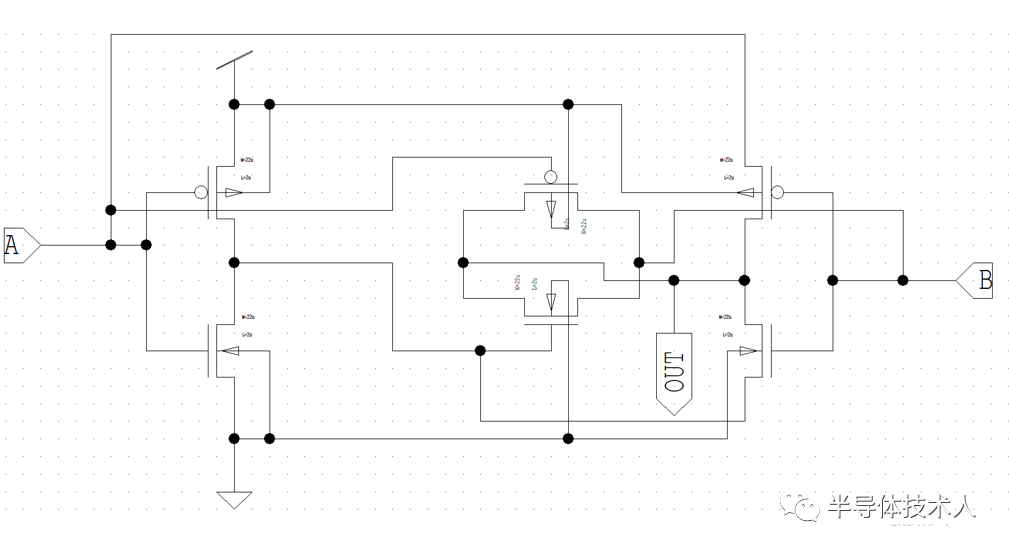

CMOS異或門(mén)的設(shè)計(jì)方法及技巧

電路中用了四異或門(mén)74HC86D,但是異或門(mén)輸出的信號(hào)有干擾?

【數(shù)字電路】關(guān)于邏輯異或門(mén)基礎(chǔ)知識(shí)點(diǎn)總結(jié)教程

異或門(mén)電路圖

異或門(mén)符號(hào),異或門(mén)邏輯符號(hào)

異或門(mén),異或門(mén)是什么意思

異或門(mén)的邏輯功能解析

異或門(mén)邏輯測(cè)試的Multisim仿真實(shí)例電路圖免費(fèi)下載

為什么異或門(mén)又稱可控反相器

異或門(mén)兩種常見(jiàn)的實(shí)現(xiàn)方式

低功耗,1.8/2.5/3.3-V輸入,3.3-V CMOS輸出,2輸入 異或門(mén)數(shù)據(jù)表

低功率,1.8/2.5/3.3-V輸入,3.3-V CMOS輸出,2輸入異或門(mén)數(shù)據(jù)表

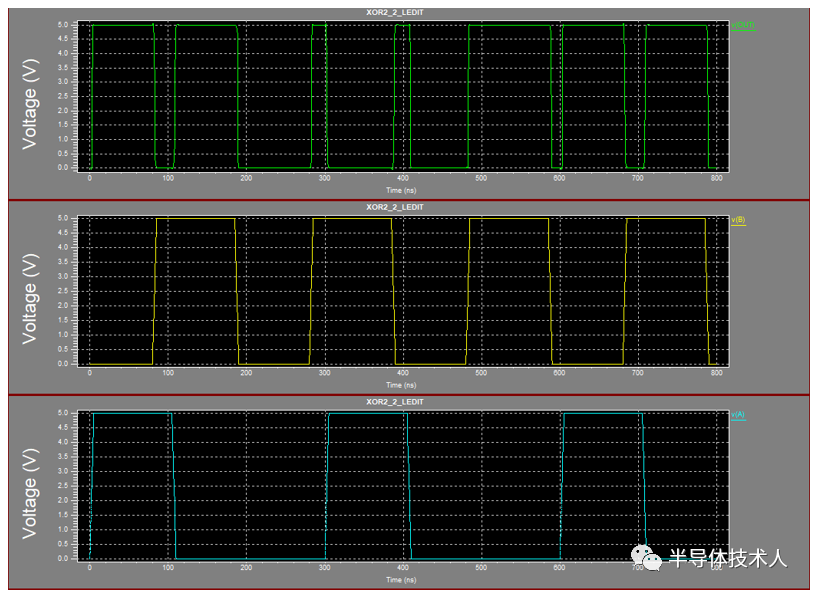

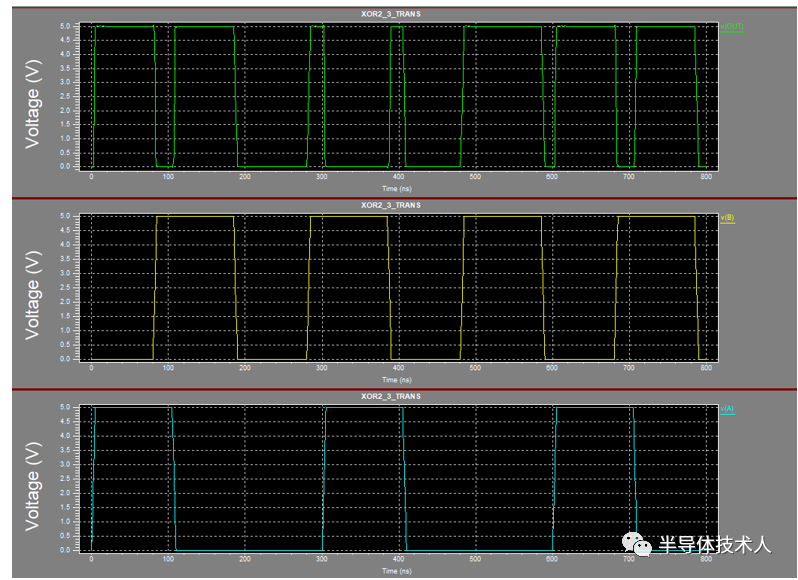

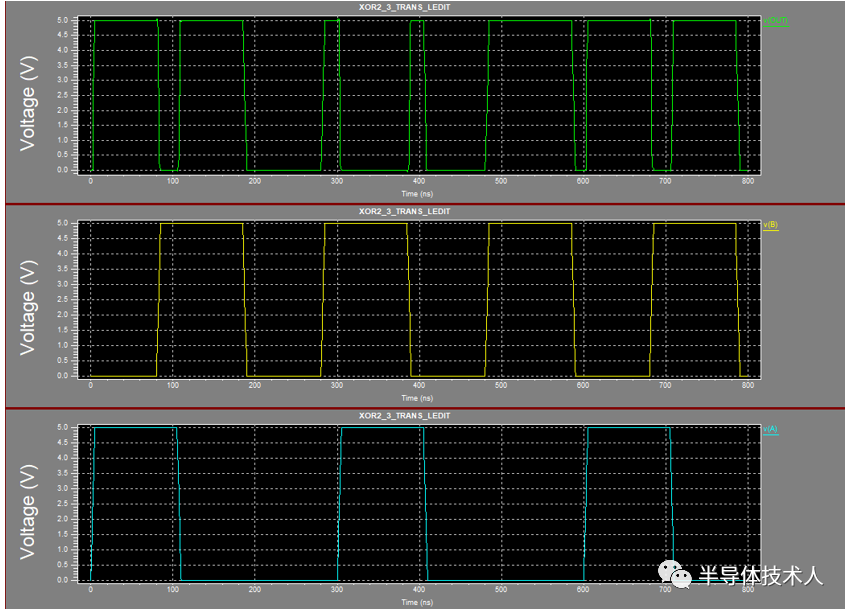

CMOS異或門(mén)仿真設(shè)計(jì)

CMOS異或門(mén)仿真設(shè)計(jì)

評(píng)論