HDLBits: 在線學習 SystemVerilog(十四)-Problem 80-89(觸發器和鎖存器(1))

HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

網址如下:

https://hdlbits.01xz.net/

關于HDLBits的Verilog實現可以查看下面專欄:

https://www.zhihu.com/column/c_1131528588117385216

縮略詞索引:

- SV:SystemVerilog

從今天開始新的一章-時序電路,包括觸發器、計數器、移位寄存器、狀態機等。

今天更新觸發器和鎖存器,這也是FPGA部分需要了解的基礎部分。

觸發器和鎖存器

《觸發器全知道》

《FPGA的設計中為什么避免使用鎖存器》

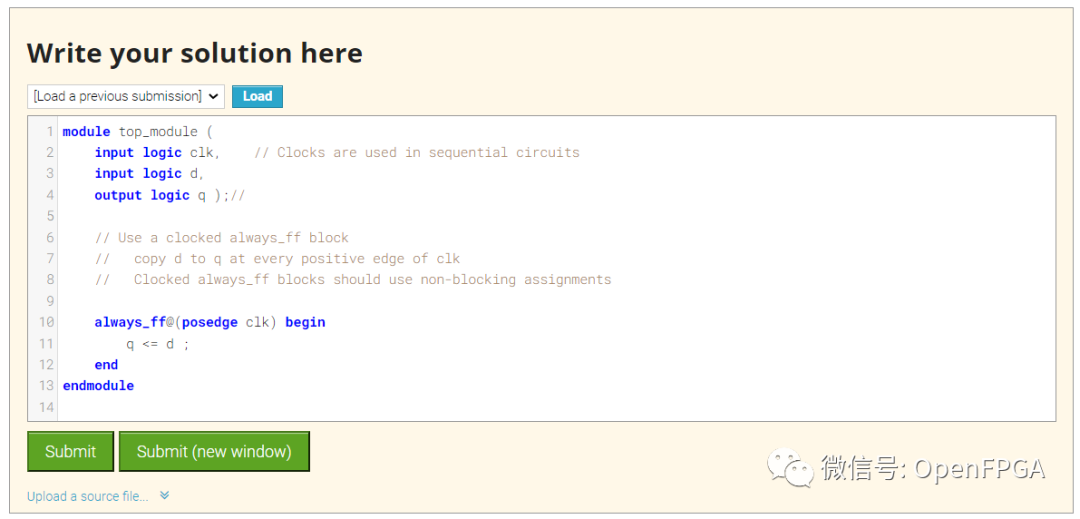

Problem 80-Dff

SystemVerilog中程序塊的使用

《SystemVerilog-程序塊 (procedural blocks)》

題目說明

D 觸發器是一個電路,存儲 1bit 數據,并定期地根據觸發器的輸入(d)更新這 1 bit 數據,更新通常發生在時鐘上升沿(clk)。存儲的數據會通過輸出管腳(q)輸出。

本題要求利用always程序塊創建一個D觸發器。

模塊端口聲明

moduletop_module(

inputclk,//Clocksareusedinsequentialcircuits

inputd,

outputregq);

題目解析

moduletop_module(

inputlogicclk,//Clocksareusedinsequentialcircuits

inputlogicd,

outputlogicq);//

//Useaclockedalways_ffblock

//copydtoqateverypositiveedgeofclk

//Clockedalways_ffblocksshouldusenon-blockingassignments

always_ff@(posedgeclk)begin

q<=?d?;

????end

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

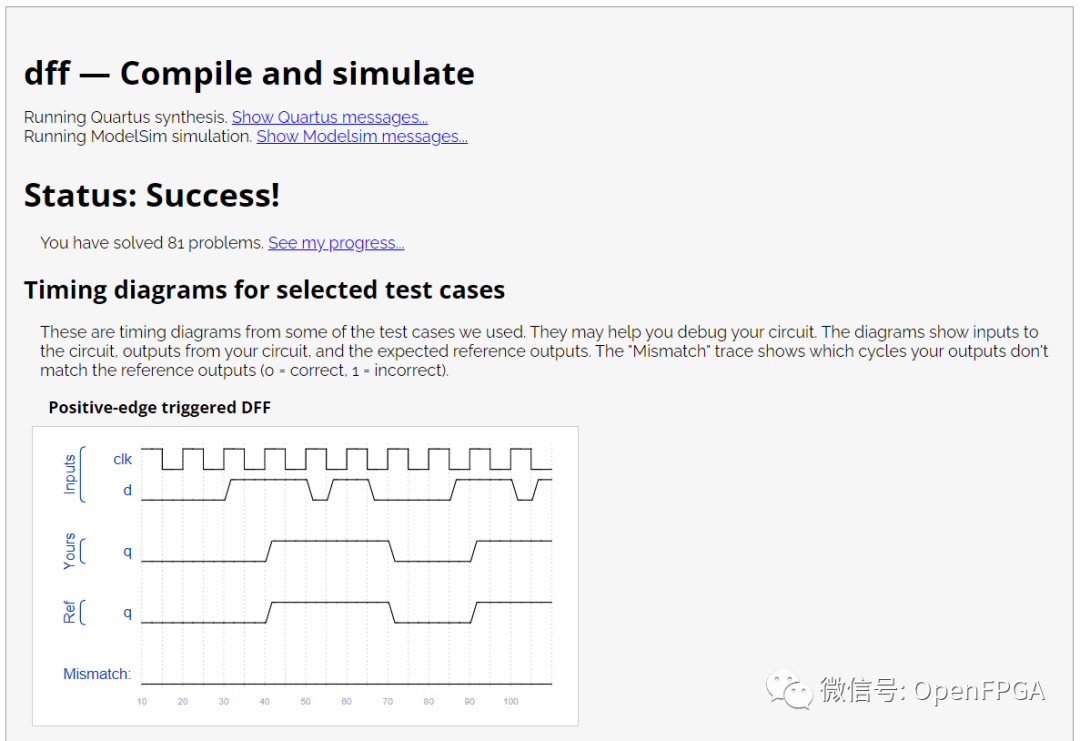

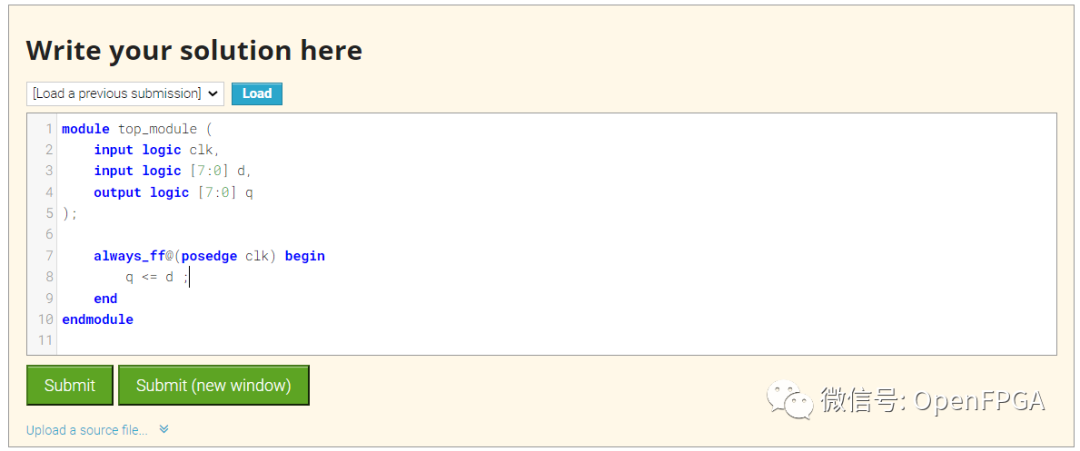

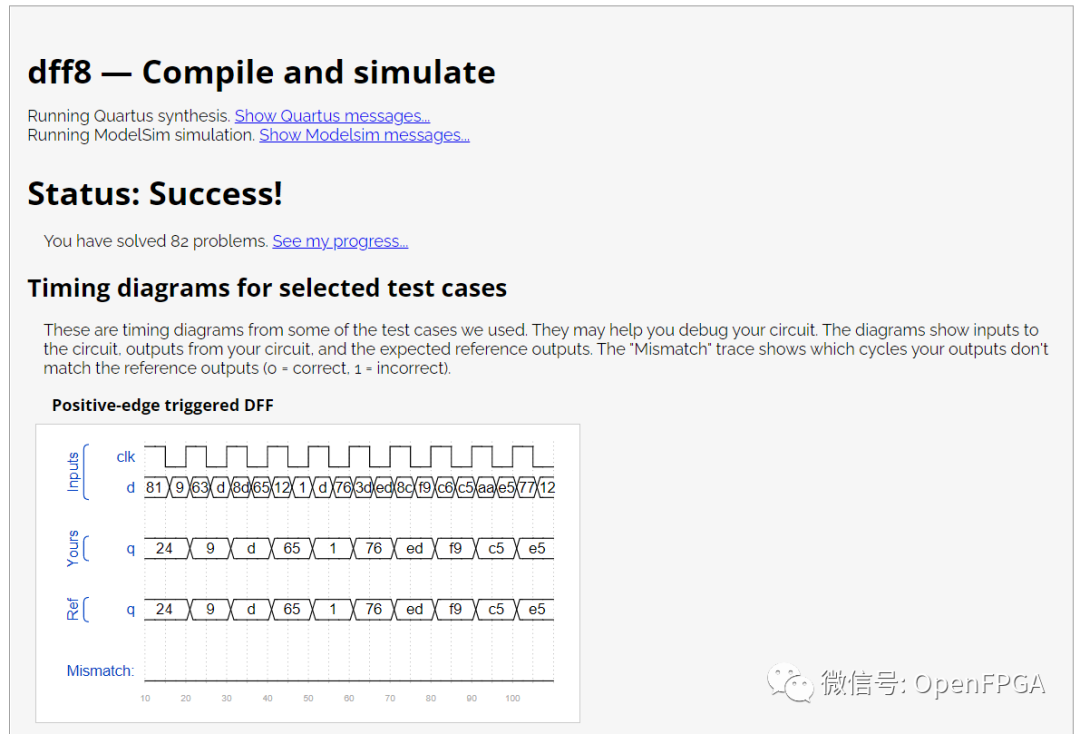

Problem 81-Dff8

題目說明

實現 8 個 D 觸發器。

模塊端口聲明

moduletop_module(

inputclk,

input[7:0]d,

output[7:0]q

);

題目解析

不需要將上面的電路復制八遍,只需將輸入輸出的位寬提高到八位即可,綜合器會幫我們實現我們需要的8個觸發器。

moduletop_module(

inputlogicclk,

inputlogic[7:0]d,

outputlogic[7:0]q

);

always_ff@(posedgeclk)begin

q<=?d?;

????end

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 82-Dff8r

題目說明

在上一題基礎上加上同步復位電路。

模塊端口聲明

moduletop_module(

inputclk,

inputreset,//Synchronousreset

input[7:0]d,

output[7:0]q

);

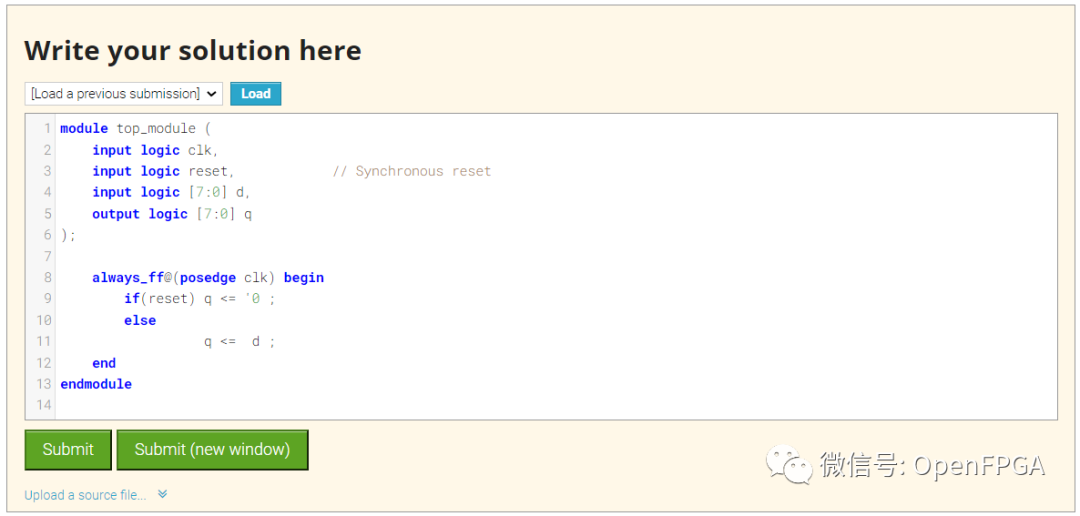

題目解析

這題難度不大,需要我們舉一反三:明白同步復位和異步復位。

對于電路中的時序元件,把復位信號受到時鐘的控制和復位信號不受時鐘的控制兩種電路分別稱為同步復位電路和異步復位電路。

moduletop_module(

inputlogicclk,

inputlogicreset,//Synchronousreset

inputlogic[7:0]d,

outputlogic[7:0]q

);

always_ff@(posedgeclk)begin

if(reset)q<=?'0;

else

q<=??d?;

????end

endmodule

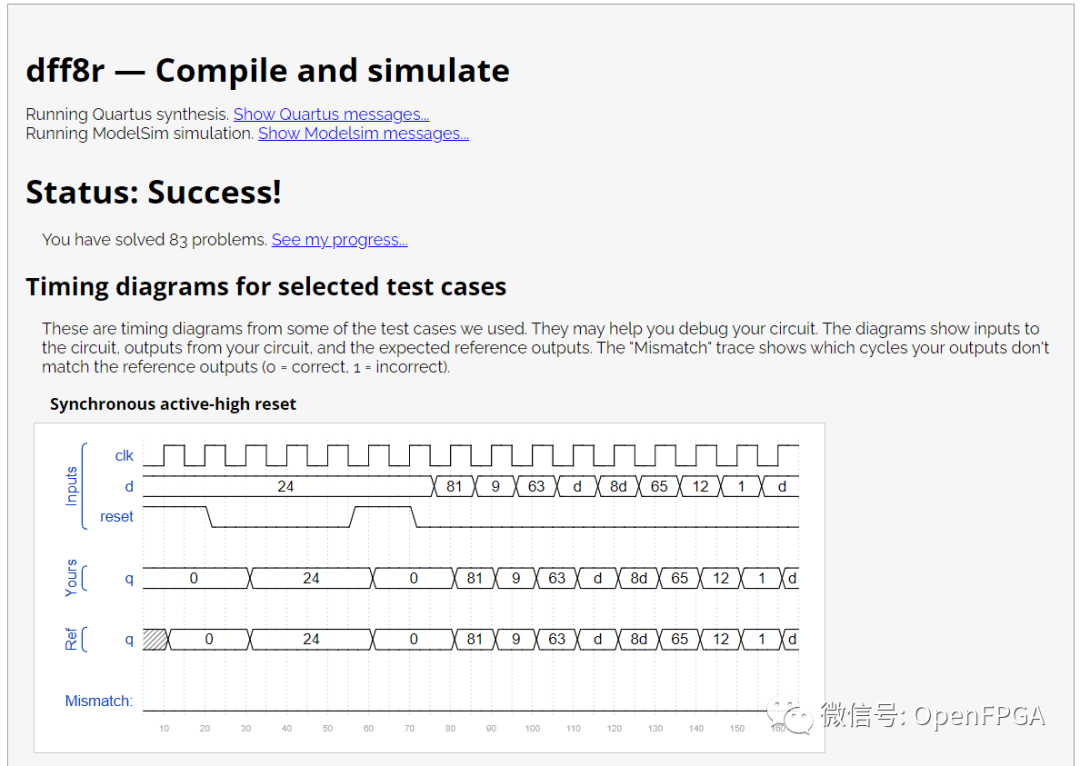

點擊Submit,等待一會就能看到下圖結果:

在vivado中綜合的結果如下:

其中,FDRE:D Flip-Flop with Clock Enable and Synchronous Reset 帶使能功能的同步復位D觸發器。

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 83-Dff8p

題目說明

在上一題同步復位基礎上,觸發器必須復位時候為 0x34 而不是零。所有 DFF 都應由clk的下降沿觸發。

模塊端口聲明

moduletop_module(

inputclk,

inputreset,

input[7:0]d,

output[7:0]q

);

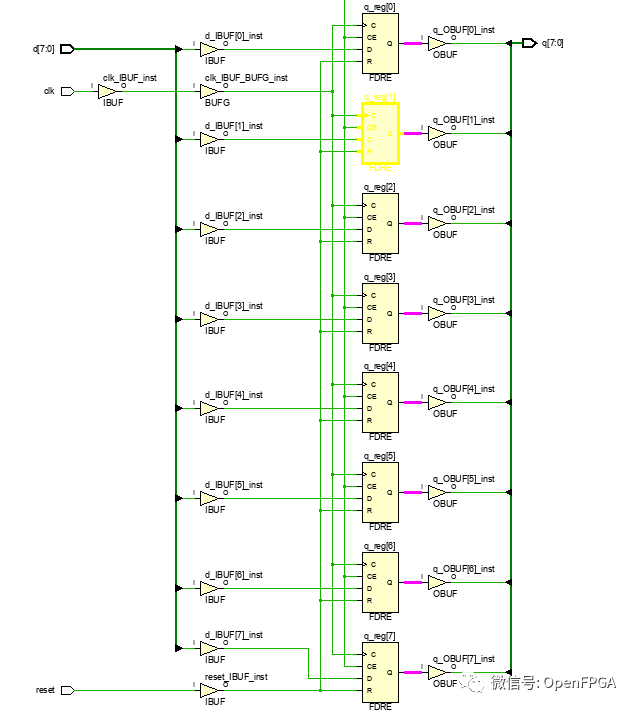

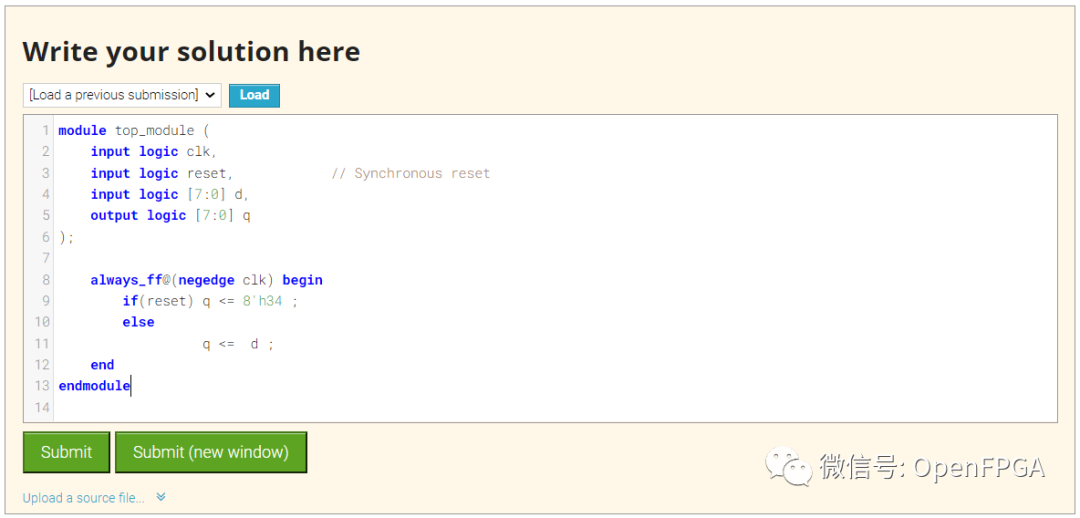

題目解析

moduletop_module(

inputlogicclk,

inputlogicreset,//Synchronousreset

inputlogic[7:0]d,

outputlogic[7:0]q

);

always_ff@(negedgeclk)begin

if(reset)q<=?8'h34;

else

q<=??d?;

????end

endmodule

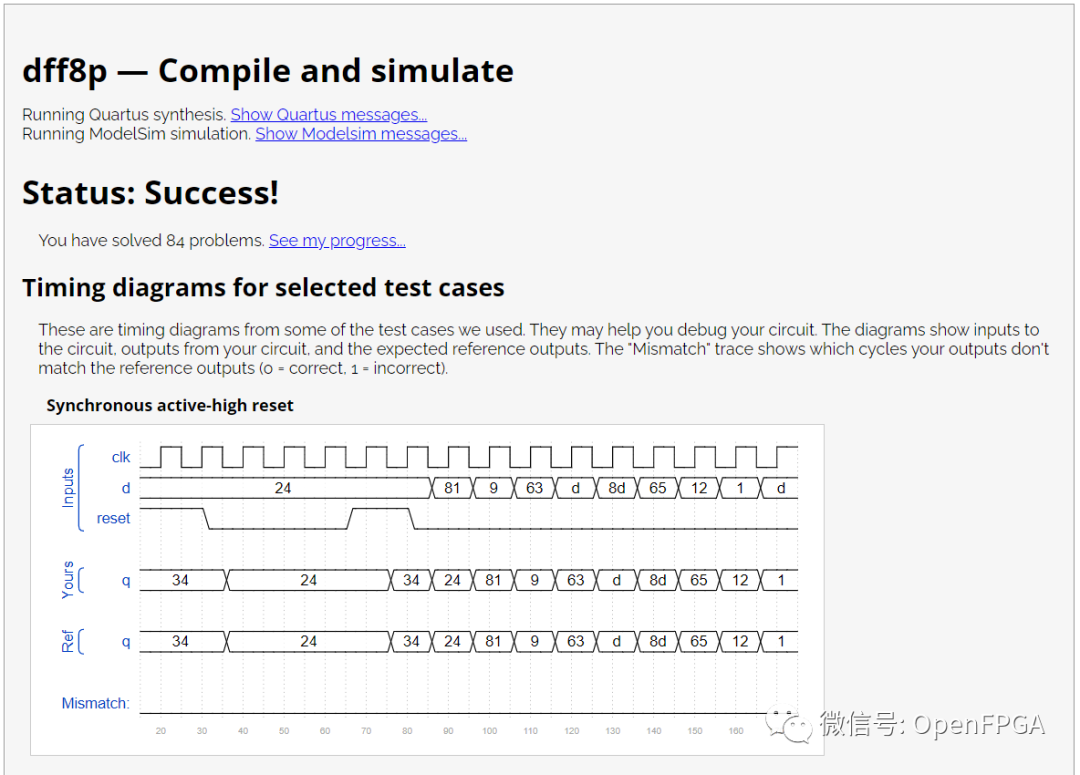

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 84-Dff8ar

題目說明

本題中的觸發器引入了異步復位。當異步復位端有效時,觸發器的輸出復位為 0 。

模塊端口聲明

moduletop_module(

inputclk,

inputareset,//activehighasynchronousreset

input[7:0]d,

output[7:0]q

);

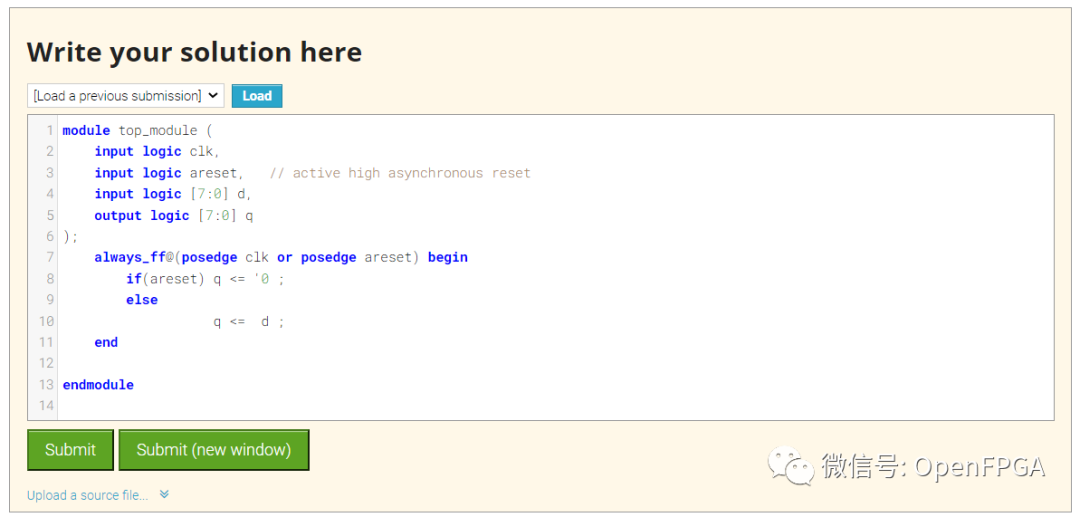

題目解析

moduletop_module(

inputlogicclk,

inputlogicareset,//activehighasynchronousreset

inputlogic[7:0]d,

outputlogic[7:0]q

);

always_ff@(posedgeclkorposedgeareset)begin

if(areset)q<=?'0;

else

q<=??d?;

????end

endmodule

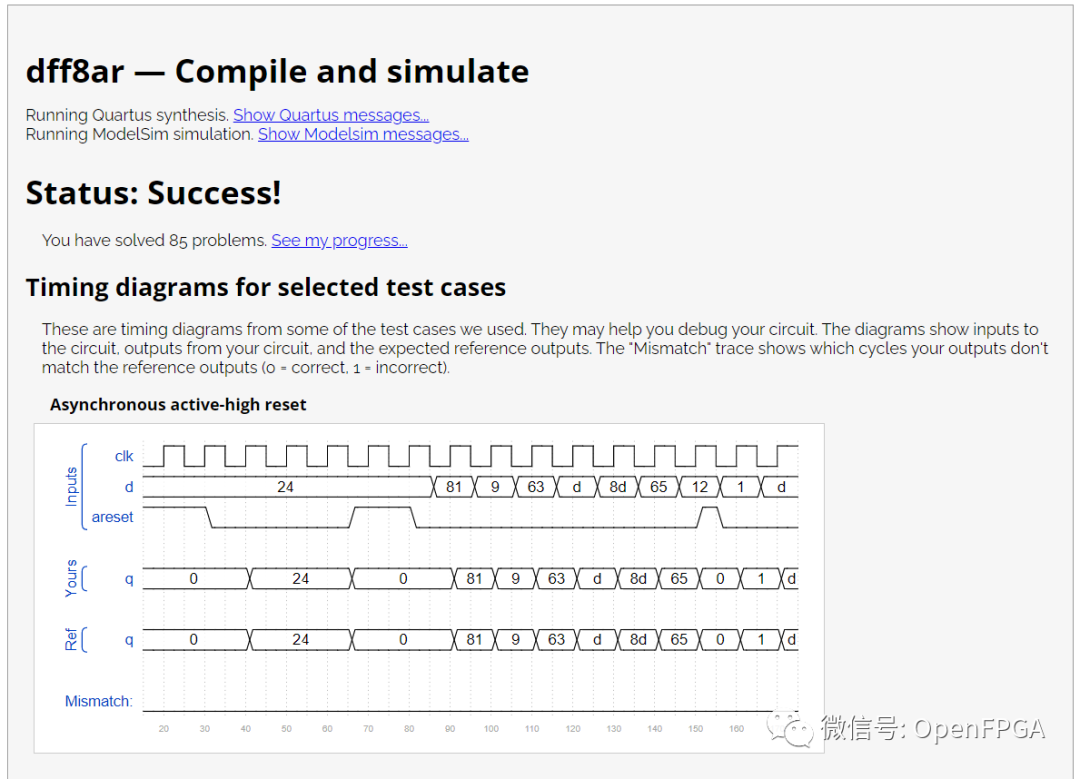

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

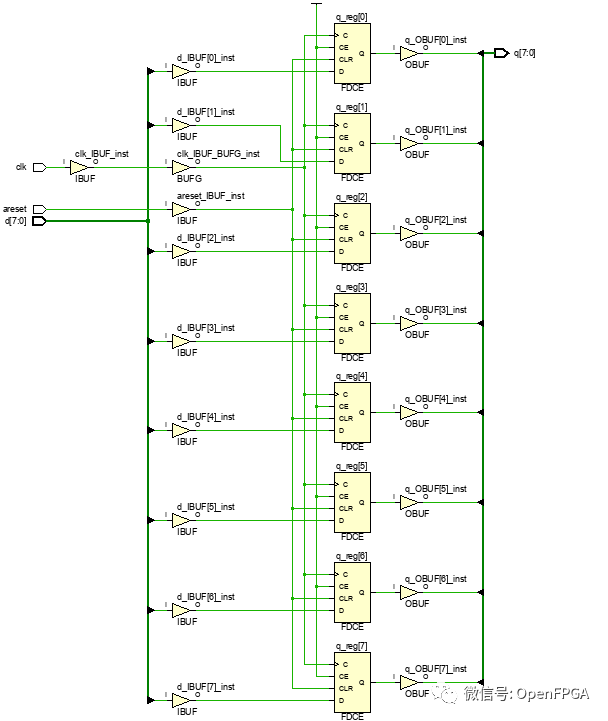

下圖是Vivado中綜合的結果:

FDC :: D Flip-Flop with Asynchronous Clear 帶異步清除D觸發器;FDCE:D Flip-Flop with Clock Enable and AsynchronousReset 帶使能功能的異步清除D觸發器,相比與FDRE將同步復位變化成異步復位,當同步復位接口為高電平時,直接觸發寄存器復位(置0)。

這一題就結束了。

Problem 85-Dff16e

題目說明

創建一個 16 路 D觸發器。部分情況下,只需要多路觸發器中的一部分觸發器工作,此時可以通過 ena 使能端進行控制。使能端 ena 信號有效時,觸發器在時鐘上升沿工作。

byteena 使能信號以 byte 為單位管理 8 路觸發器在時鐘邊沿觸發與否。byteena [1] 作為 d[15:8] 高位字節的使能端,byteena [0] 則控制 d 的低位字節。

resetn 為同步,低電平有效復位信號。

模塊端口聲明

moduletop_module(

inputclk,

inputresetn,

input[1:0]byteena,

input[15:0]d,

output[15:0]q

);

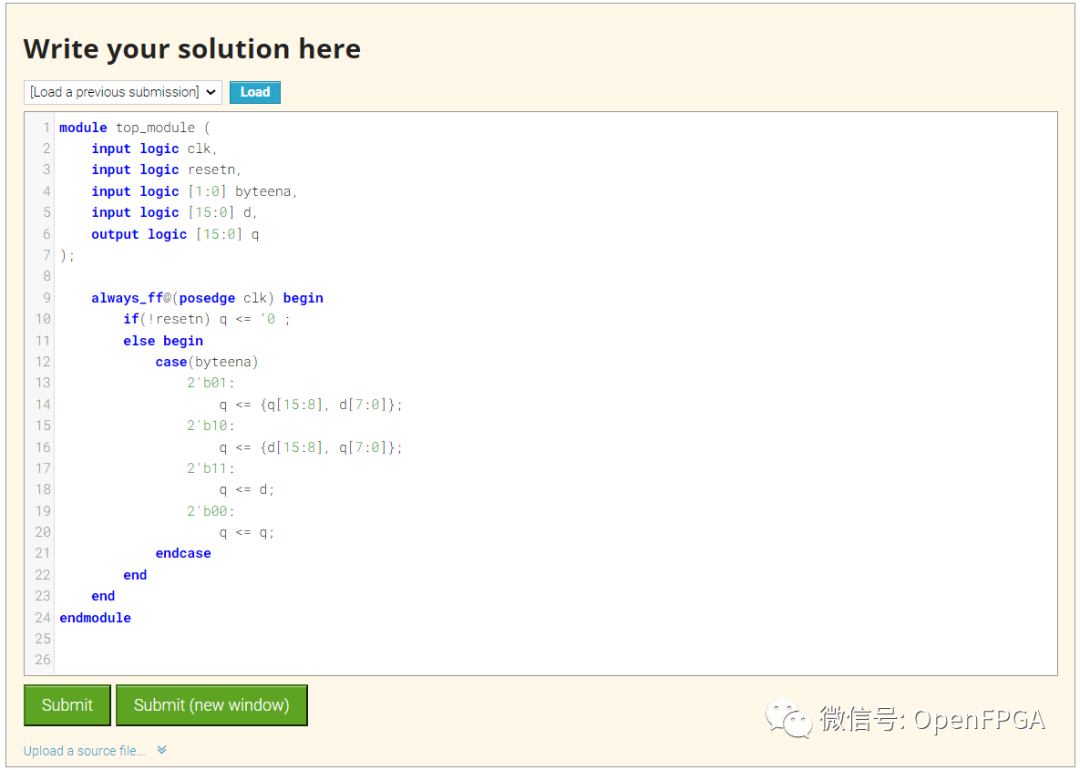

題目解析

moduletop_module(

inputlogicclk,

inputlogicresetn,

inputlogic[1:0]byteena,

inputlogic[15:0]d,

outputlogic[15:0]q

);

always_ff@(posedgeclk)begin

if(!resetn)q<=?'0;

elsebegin

case(byteena)

2'b01:

q<=?{q[15:8],?d[7:0]};

????????????????2'b10:

q<=?{d[15:8],?q[7:0]};

????????????????2'b11:

q<=?d;

????????????????2'b00:

q<=?q;

????????????endcase

????????end

????end

endmodule

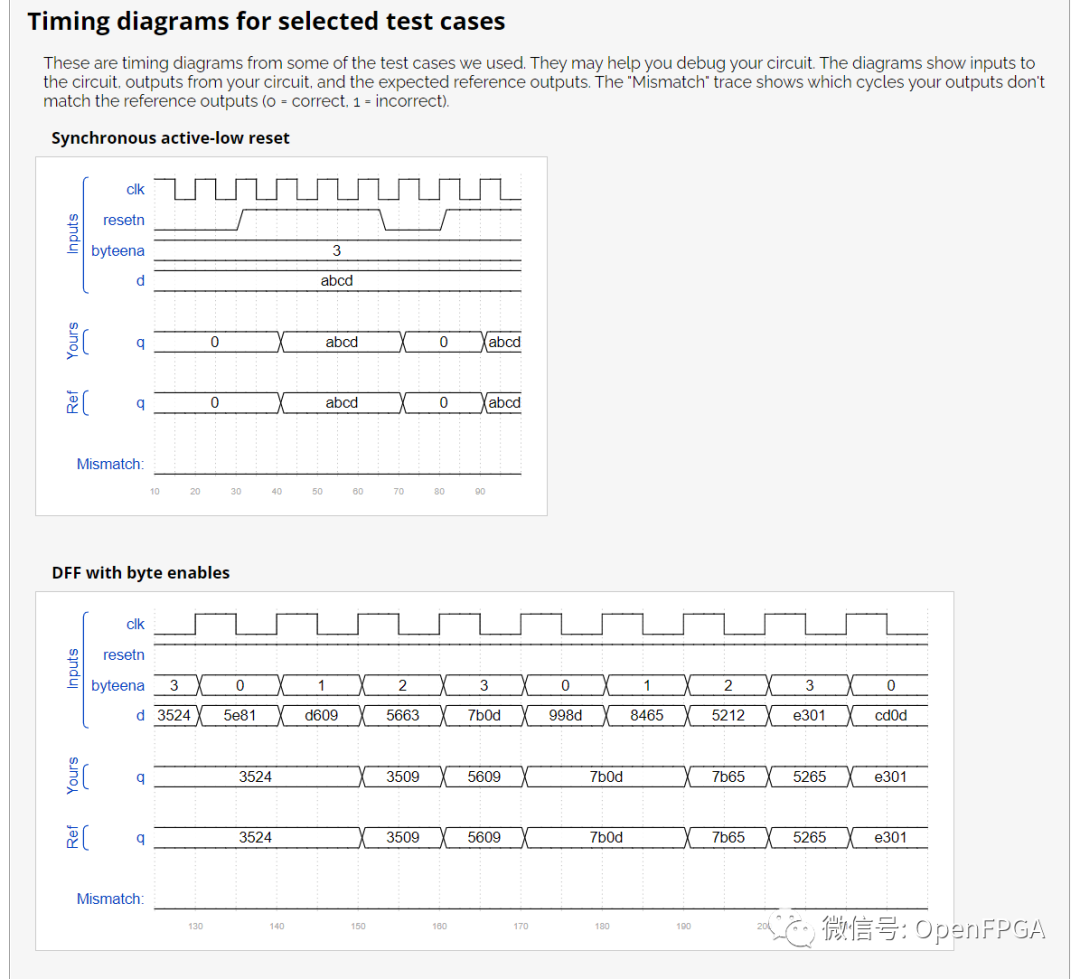

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 86-m2014 q4a

題目說明

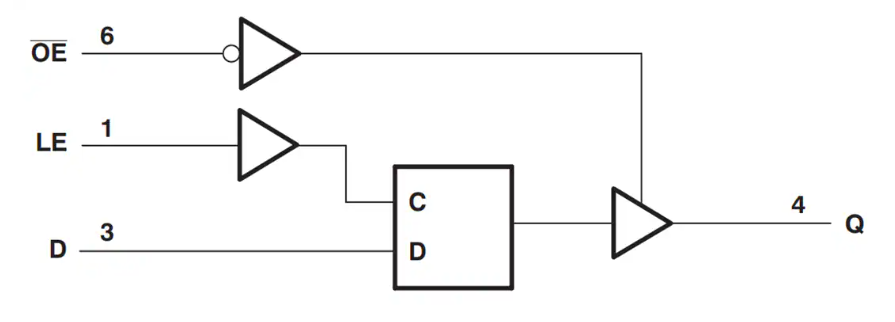

實現一個如下的電路:

從看到圖片上的電路就應該認出這個基本元器件-鎖存器,同D觸發器對比這個元件沒有 clk 端口,取而代之的是 ena 端口。

鎖存器的特征在于,相較于 D觸發器的觸發事件發生于 clk 時鐘的邊沿,鎖存器鎖存的觸發事件發生于使能端 ena 的電平。

模塊端口聲明

moduletop_module(

inputd,

inputena,

outputq);

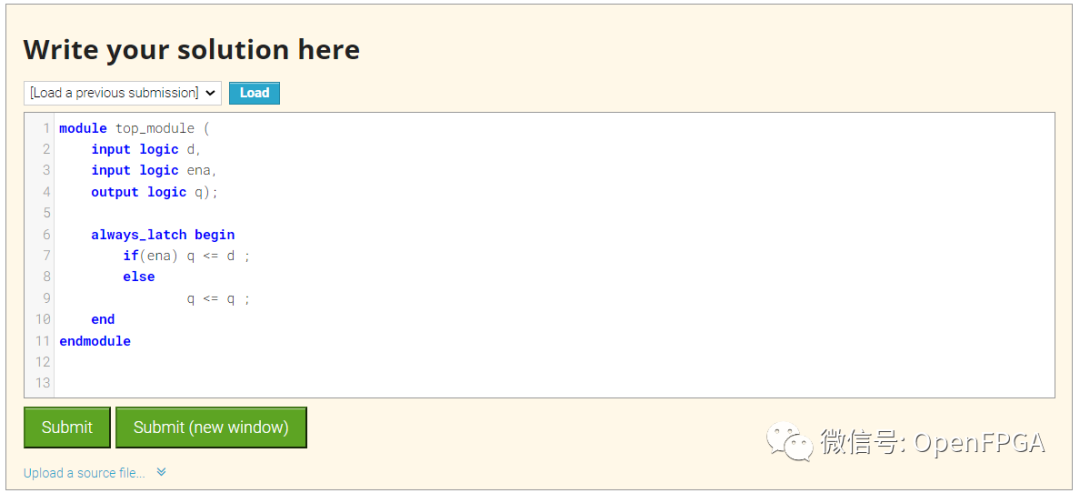

題目解析

moduletop_module(

inputlogicd,

inputlogicena,

outputlogicq);

always_latchbegin

if(ena)q<=?d?;

????????else

q<=?q?;

????end

endmodule

從上面的代碼可以看出,SV在硬件描述過程中比Verilog代碼可讀性高很多,一眼就能看出這個電路的功能,而Verilog需要根據描述的功能推測電路功能。

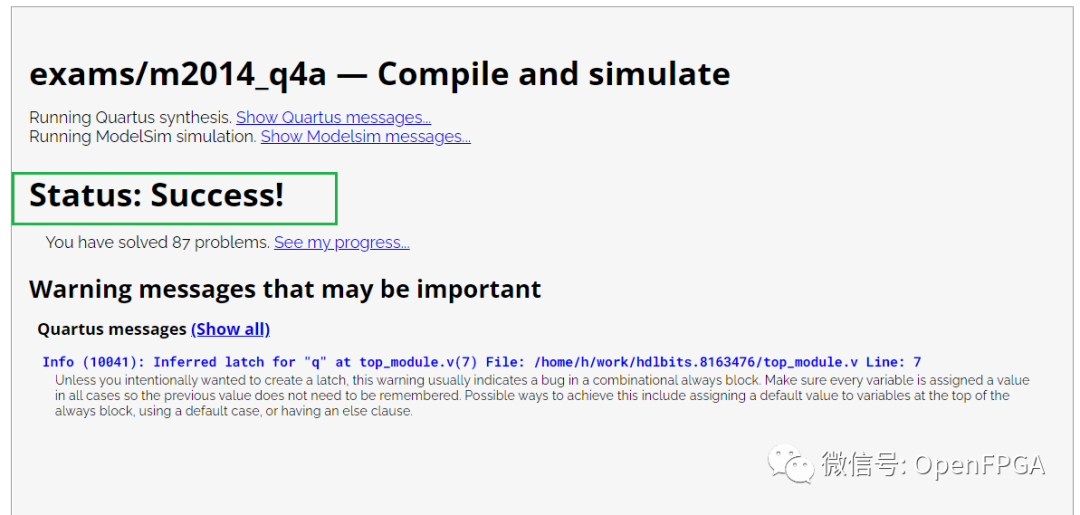

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。但是注意圖中的警告,這個在實際使用中非常重要,鎖存器相比觸發器會消耗更多的資源,所以綜合器會在推斷出鎖存器時產生提醒,防止開發者在不想使用鎖存器時,因為代碼風格等原因誤產生了鎖存器。

這一題就結束了。

Problem 87-m2014_q4b

題目說明

實現一個如下的電路:

模塊端口聲明

moduletop_module(

inputclk,

inputd,

inputar,//asynchronousreset

outputq);

題目解析

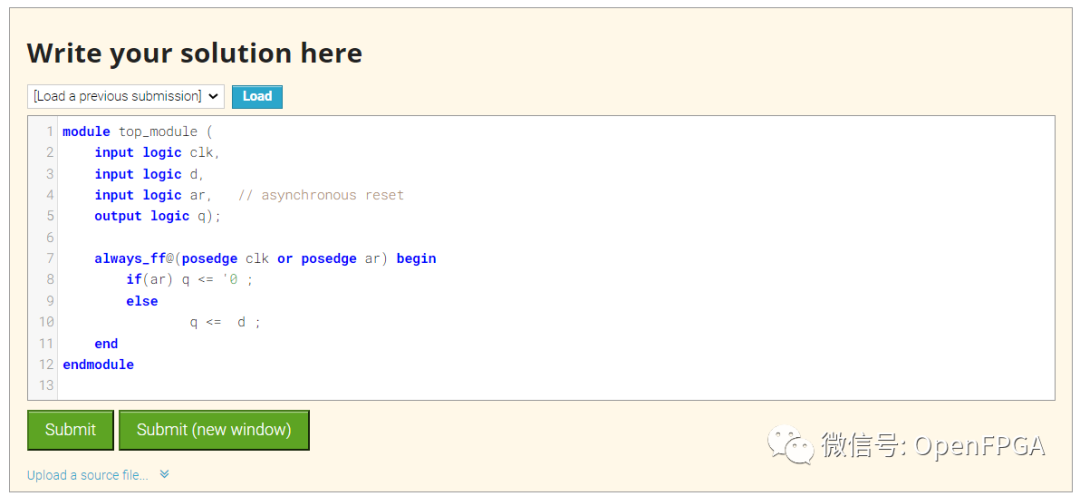

AR 代表 asynchronous reset,所以這是一個帶有異步復位的 D 觸發器。

圖中的三角形代表時鐘,不再用 CLK 標出。

moduletop_module(

inputlogicclk,

inputlogicd,

inputlogicar,//asynchronousreset

outputlogicq);

always_ff@(posedgeclkorposedgear)begin

if(ar)q<=?'0;

else

q<=??d?;

????end

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

Problem 88-m2014_q4c

題目說明

實現一個如下的電路:

模塊端口聲明

moduletop_module(

inputclk,

inputd,

inputr,//synchronousreset

outputq);

題目解析

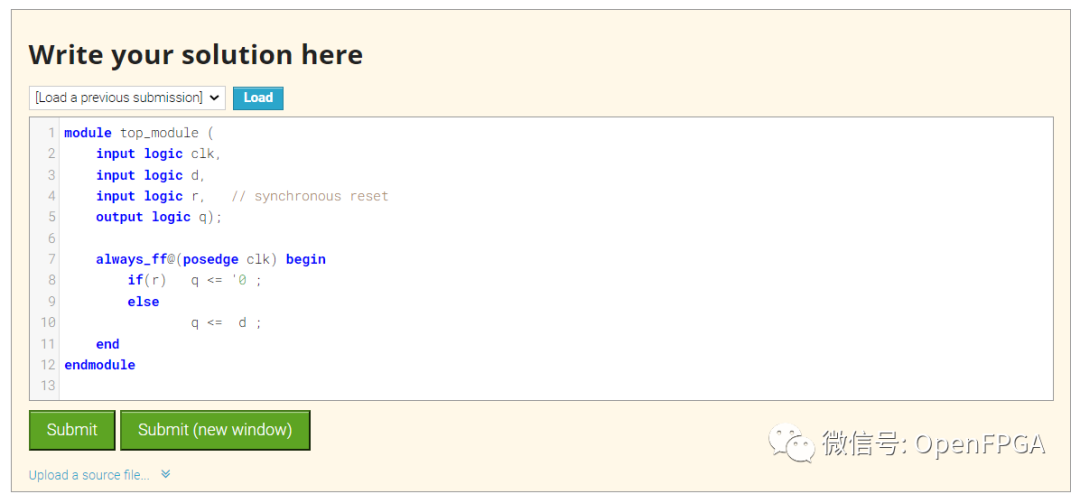

R 代表 synchronous reset。所以這是一個同步復位的D觸發器。

moduletop_module(

inputlogicclk,

inputlogicd,

inputlogicr,//synchronousreset

outputlogicq);

always_ff@(posedgeclk)begin

if(r)q<=?'0;

else

q<=??d?;

????end

endmodule

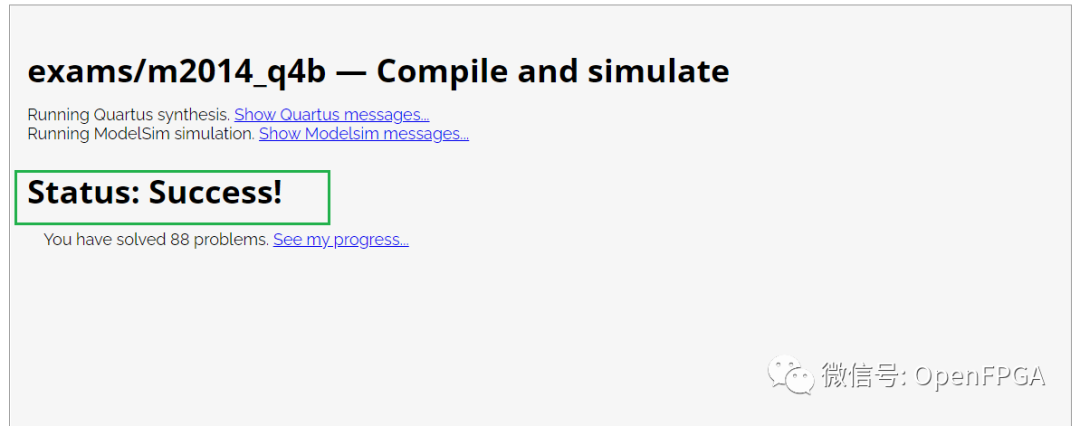

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

Problem 89-m2014_q4d

題目說明

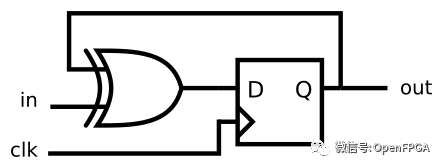

實現一個如下的電路:

模塊端口聲明

moduletop_module(

inputclk,

inputin,

outputout);

題目解析

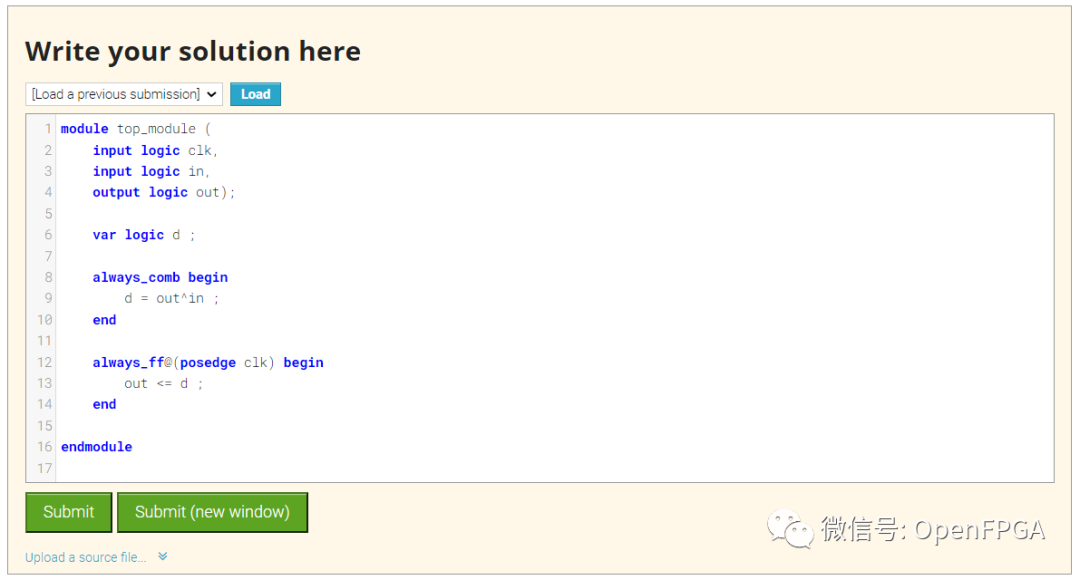

觸發器的輸出 q 和輸入信號 in 一起作為異或門的輸入。

moduletop_module(

inputlogicclk,

inputlogicin,

outputlogicout);

varlogicd;

always_combbegin

d=out^in;

end

always_ff@(posedgeclk)begin

out<=?d?;

????end

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

總結

今天的幾道題就結束了,對于理解觸發器的非常有幫助,尤其同步復位、異步復位及鎖存器的理解非常有幫助,對于這些簡單的代碼,建議放到實際的EDA工具中跑下綜合,查看一下FPGA具體的實現元器件是什么樣,這樣在后期自己設計代碼時候的理解很有幫助。

最后我這邊做題的代碼也是個人理解使用,有錯誤歡迎大家批評指正,祝大家學習愉快~

代碼鏈接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

審核編輯 :李倩

-

鎖存器

+關注

關注

8文章

956瀏覽量

44944 -

觸發器

+關注

關注

14文章

2056瀏覽量

63407 -

代碼

+關注

關注

30文章

4968瀏覽量

73970

原文標題:總結

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

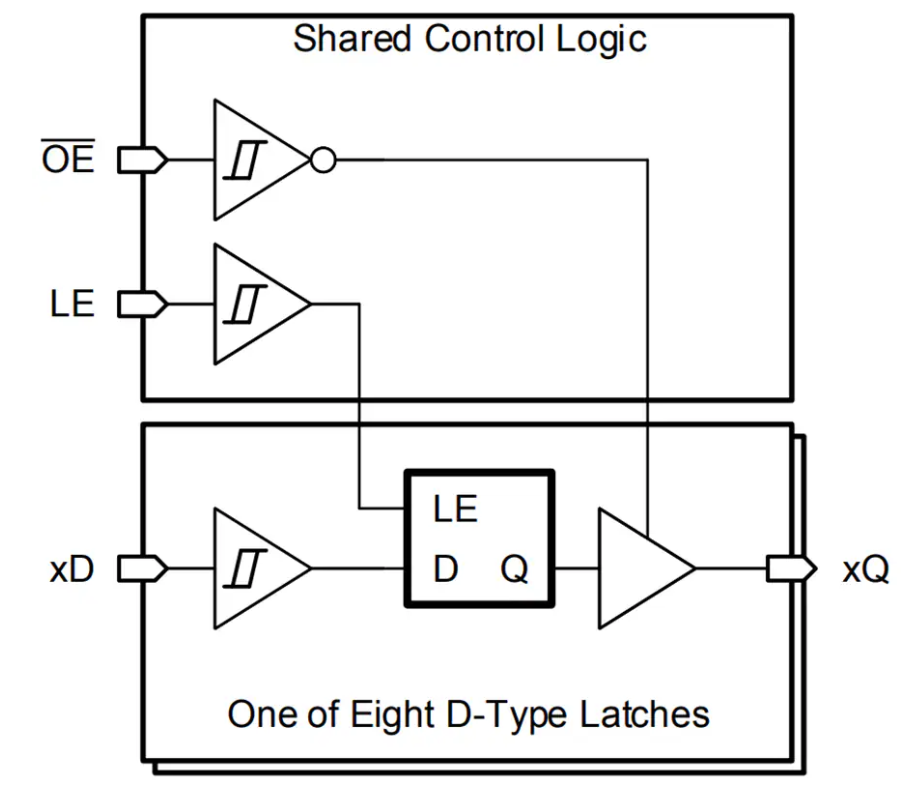

SN74HCS574QPWRQ1 8 通道 D 型觸發器

施密特觸發器光耦在門鈴系統中的應用

高速施密特觸發器密封光耦合器 skyworksinc

Texas Instruments SN74LVC1G373單D型鎖存器數據手冊

密封表面貼裝、高速施密特觸發器光耦合器 skyworksinc

用于混合組裝的微型高速施密特觸發器光耦合器 skyworksinc

一文讀懂Allegro先進磁性開關和鎖存器

施密特觸發器光耦特性

Problem 80-89(觸發器和鎖存器(1))

Problem 80-89(觸發器和鎖存器(1))

評論