HDLBits 是一組小型電路設(shè)計(jì)習(xí)題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習(xí)數(shù)字硬件設(shè)計(jì)~

網(wǎng)址如下:

https://hdlbits.01xz.net/

關(guān)于HDLBits的Verilog實(shí)現(xiàn)可以查看下面專欄:

https://www.zhihu.com/column/c_1131528588117385216

縮略詞索引:

- SV:SystemVerilog

從今天開始新的一章-時(shí)序電路,包括觸發(fā)器、計(jì)數(shù)器、移位寄存器、狀態(tài)機(jī)等。

今天更新移位寄存器,移位寄存器在乘法、除法以及各種矩陣操作中非常重要,熟練使用移位寄存器是基本技能。

移位運(yùn)算符

雖然移位運(yùn)算和本系列沒什么太大關(guān)系,但是還是回顧一下:

<SystemVerilog-移位運(yùn)算符>

Problem 106-Shift4

題目說明

構(gòu)建一個(gè) 4 位移位寄存器(右移),具有異步復(fù)位、同步加載和使能。

- areset:將移位寄存器重置為零。

- load : 用數(shù)據(jù) [3:0]加載移位寄存器而不是移位。

- ena:右移(q[3]變?yōu)榱悖琿[0]移出并消失)。

- q:移位寄存器的內(nèi)容。

如果load和ena輸入均有效 (1),則load輸入具有更高的優(yōu)先級。

模塊端口聲明

moduletop_module(

inputclk,

inputareset,//asyncactive-highresettozero

inputload,

inputena,

input[3:0]data,

outputreg[3:0]q);

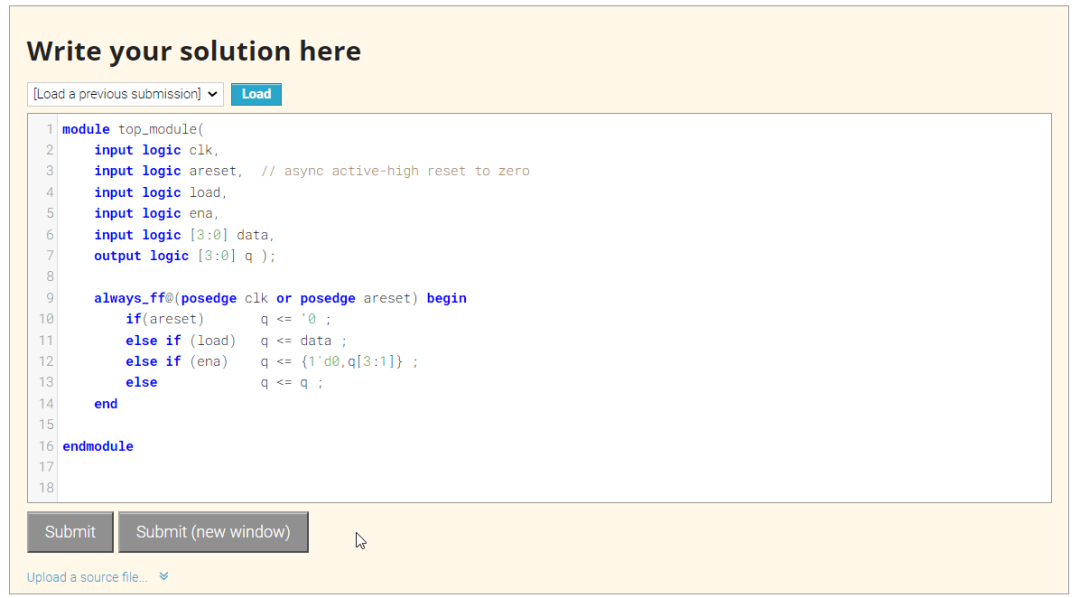

題目解析

這是一個(gè)基本移位寄存器示例。移位過程在ena控制下,實(shí)現(xiàn)q[3]q[2]q[1]q[0] ---> 0 q[3]q[2]q[1]---> 0 0 q[3]q[2]

因?yàn)檫@題增加了很多控制信號,所以只能使用時(shí)序電路進(jìn)行描述。

moduletop_module(

inputlogicclk,

inputlogicareset,//asyncactive-highresettozero

inputlogicload,

inputlogicena,

inputlogic[3:0]data,

outputlogic[3:0]q);

always_ff@(posedgeclkorposedgeareset)begin

if(areset)q<=?'0;

elseif(load)q<=?data?;

????????else?if?(ena)????q?<=?{1'd0,q[3:1]};

elseq<=?q?;

????end

endmodule

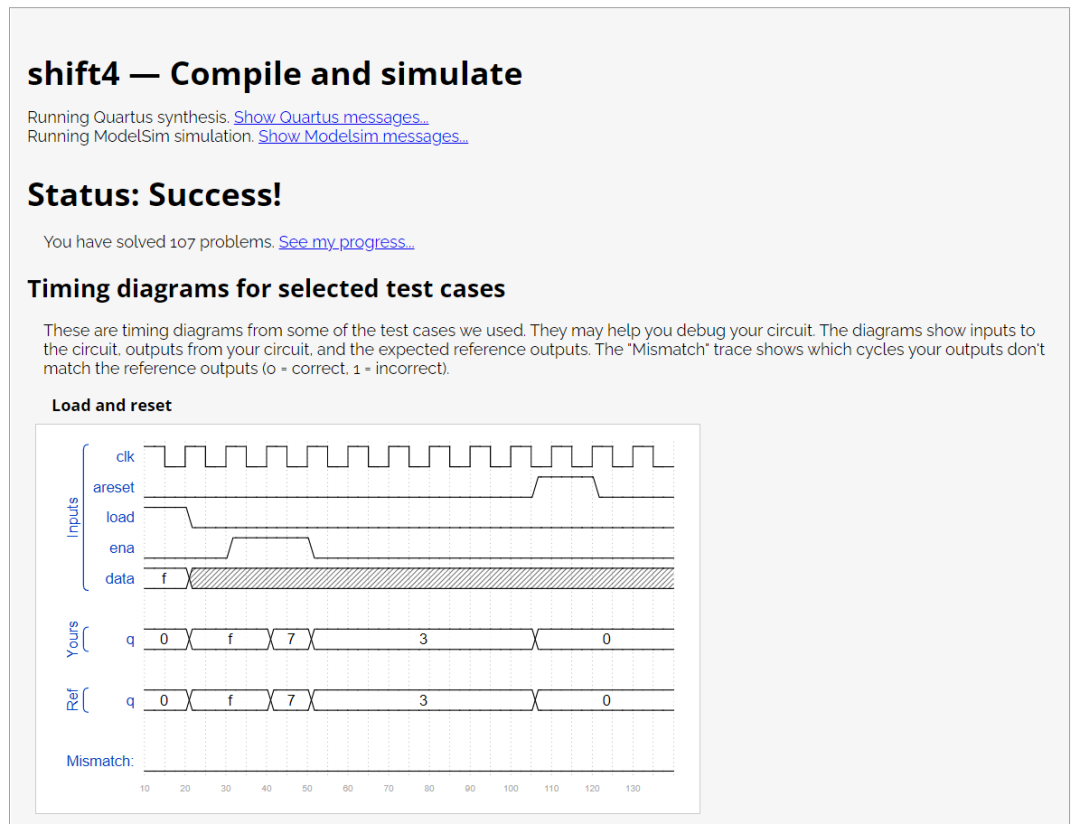

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

Problem 107-Rotate100

題目說明

設(shè)計(jì)一個(gè)100bit的可左移或右移的移位寄存器,附帶同步置位和左移或右移的使能信號。本題中,移位寄存器在左移或右移時(shí),不同于Problem106的補(bǔ)0和直接舍棄某一bit位,本題是要求在100bit內(nèi)循環(huán)移動(dòng),不舍棄某一位同時(shí)也不補(bǔ)0。

比如說左移1bit,在Problem106就是補(bǔ)0和丟棄q[0]。而在本題中左移1bit為{q[0], q[99:1]}。

load:load信號將data[99:0] 輸入至寄存器內(nèi)。ena[1:0] 信號選擇是否移位和移位的具體方向2'b01 右移一位2'b10 左移一位2'b00 和 2'b11不移動(dòng)q:移位后寄存器內(nèi)的數(shù)據(jù)

模塊端口聲明

moduletop_module(

inputclk,

inputload,

input[1:0]ena,

input[99:0]data,

outputreg[99:0]q);

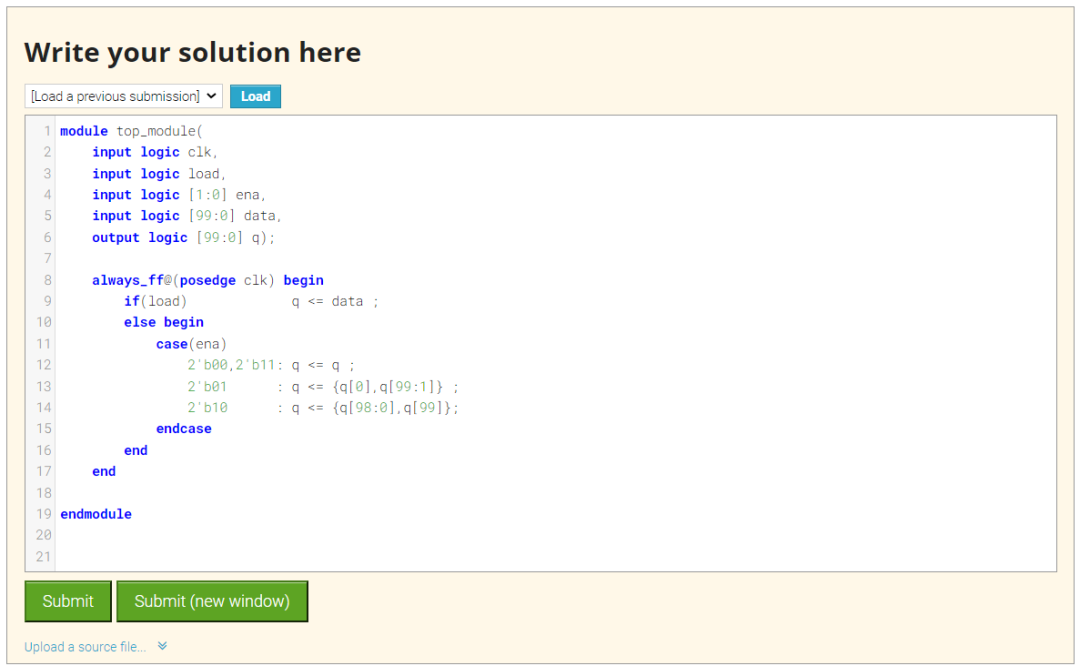

題目解析

本題是一個(gè)桶型移位寄存器,題目的解答就是:{q[0], q[99:1]}。

moduletop_module(

inputlogicclk,

inputlogicload,

inputlogic[1:0]ena,

inputlogic[99:0]data,

outputlogic[99:0]q);

always_ff@(posedgeclk)begin

if(load)q<=?data?;

????????elsebegin

case(ena)

2'b00,2'b11:q<=?q?;

????????????????2'b01:q<=?{q[0],q[99:1]}?;

????????????????2'b10:q<=?{q[98:0],q[99]};

????????????endcase

????????end

????end

endmodule

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中無波形。

這一題就結(jié)束了。

Problem 108-Shift18

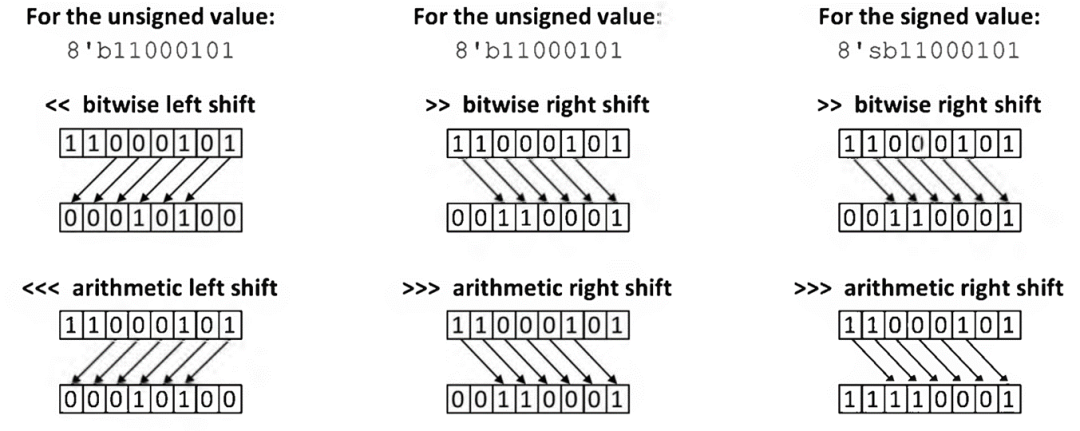

先補(bǔ)充一下算術(shù)移位寄存器和按位移位寄存器:

SystemVerilog具有按位和算術(shù)移位運(yùn)算符。

按位移位只是將向量的位向右或向左移動(dòng)指定的次數(shù),移出向量的位丟失。移入的新位是零填充的。例如,操作8’b11000101 << 2將產(chǎn)生值8’b00010100。按位移位將執(zhí)行相同的操作,無論被移位的值是有符號的還是無符號的。

算術(shù)左移位對有符號和無符號表達(dá)式執(zhí)行與按位右移位相同的操作。算術(shù)右移位對“無符號”和“有符號”表達(dá)式執(zhí)行不同的運(yùn)算。如果要移位的表達(dá)式是無符號的,算術(shù)右移位的行為與按位右移相同,即用零填充輸入位。如果表達(dá)式是有符號的,則算術(shù)右移將通過用符號位的值填充每個(gè)輸入位來保持值的有符號性。

具體如下:

題目說明

構(gòu)建一個(gè)具有同步加載功能的 64 位算術(shù)移位寄存器。移位器可以左右移動(dòng),移動(dòng) 1 位或 8 位,由amount選擇。

算術(shù)右移將移位寄存器(在本例中為q[63] )中數(shù)字的符號位移位,而不是像邏輯右移那樣移入零。考慮算術(shù)右移的另一種方法是,它假設(shè)被移位的數(shù)字是帶符號的并保留符號,因此算術(shù)右移將帶符號的數(shù)字除以 2 的冪。

邏輯左移和算術(shù)左移之間沒有區(qū)別。

- load :用數(shù)據(jù) [63:0]加載移位寄存器而不是移位。

- ena:選擇是否移動(dòng)。

- amount:選擇移動(dòng)的方向和移動(dòng)量。

2'b00:左移一位。

2'b01:左移 8 位。

2'b10:右移一位。

2'b11:右移 8 位。

- q:移位器的內(nèi)容。

模塊端口聲明

moduletop_module(

inputclk,

inputload,

inputena,

input[1:0]amount,

input[63:0]data,

outputreg[63:0]q);

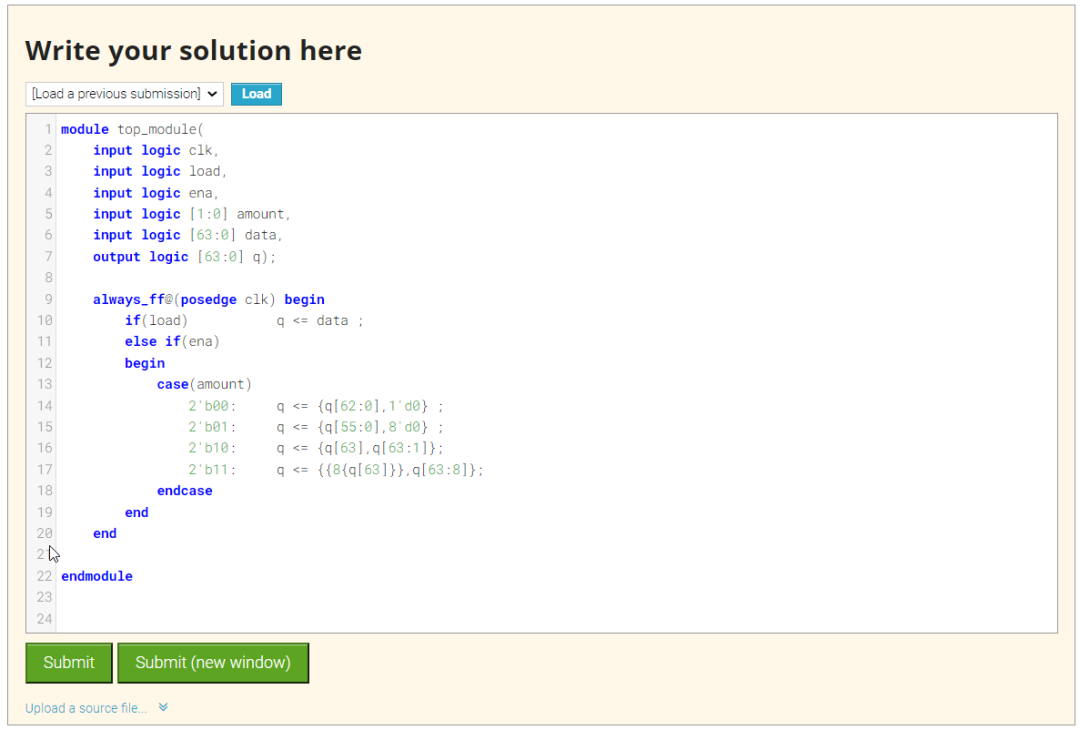

題目解析

moduletop_module(

inputlogicclk,

inputlogicload,

inputlogicena,

inputlogic[1:0]amount,

inputlogic[63:0]data,

outputlogic[63:0]q);

always_ff@(posedgeclk)begin

if(load)q<=?data?;

????????elseif(ena)

begin

case(amount)

2'b00:q<=?{q[62:0],1'd0};

2'b01:q<=?{q[55:0],8'd0};

2'b10:q<=?{q[63],q[63:1]};

????????????????2'b11:q<=?{{8{q[63]}},q[63:8]};

????????????endcase

????????end

????end

endmodule

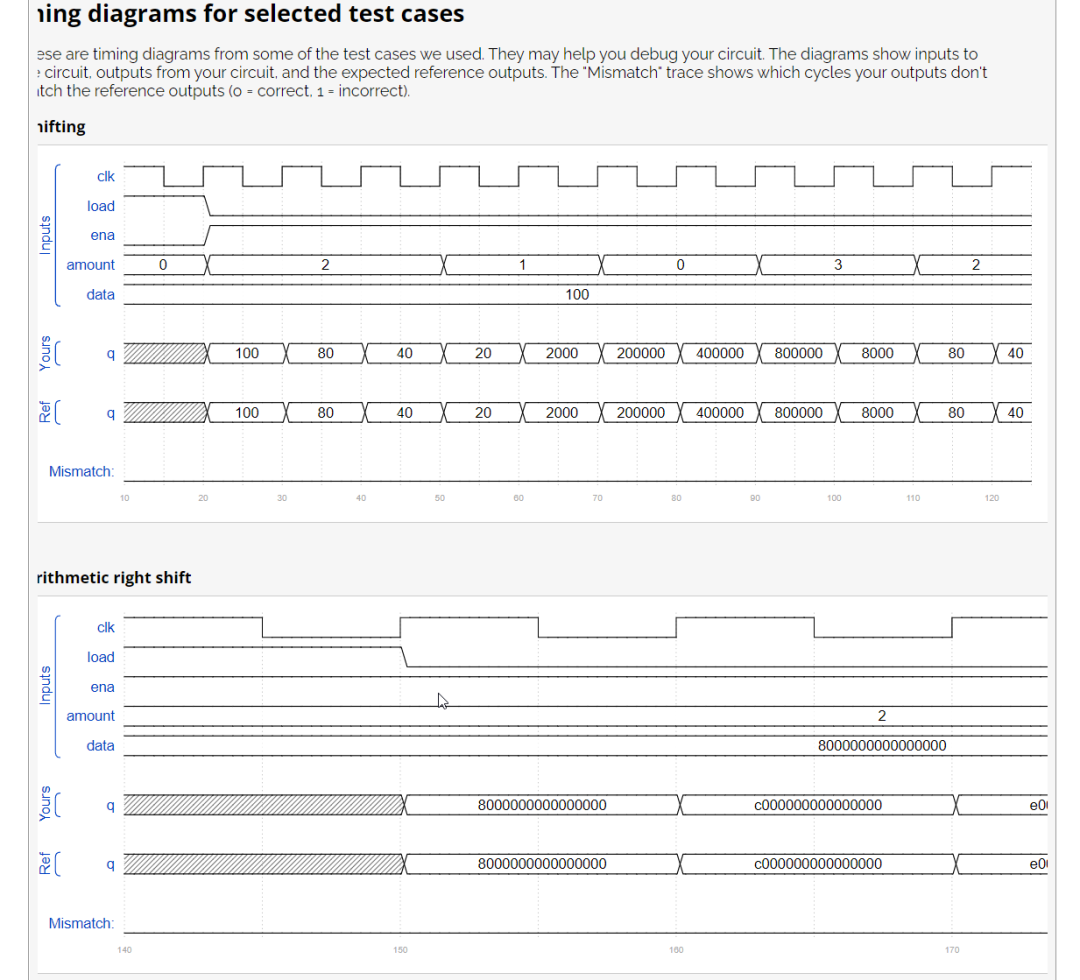

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

Problem 109-Lfsr5

題目說明

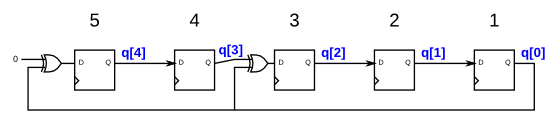

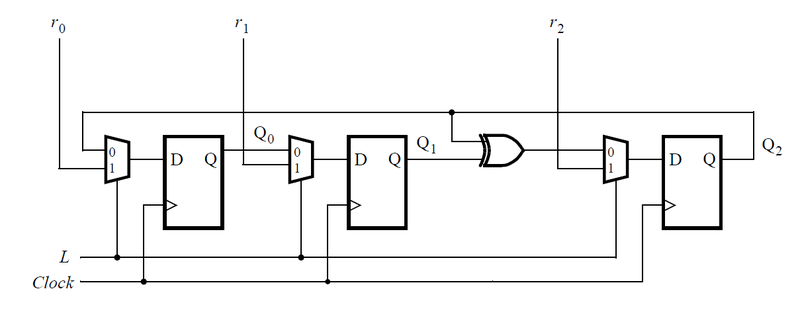

線性反饋移位寄存器(LFSR)是一種移位寄存器,通常帶有幾個(gè)異或門(XOR)來產(chǎn)生移位寄存器的下一個(gè)狀態(tài)。Galois LFSR 是一種特殊的排列方式,其中帶有“抽頭(tap)”的位位置與輸出位進(jìn)行異或以產(chǎn)生其下一個(gè)值,而沒有抽頭移位的位位置。如果仔細(xì)選擇抽頭位置,則可以將 LFSR 設(shè)為“最大長度”。n 位的最大長度 LFSR 在重復(fù)之前循環(huán)通過 2^n -1 個(gè)狀態(tài)(永遠(yuǎn)不會(huì)達(dá)到全零狀態(tài))。

下圖顯示了一個(gè) 5 位最大長度的 Galois LFSR,在位置 5 和 3 處有抽頭。(抽頭位置通常從 1 開始編號)。請注意,為了保持一致性,我在位置 5 處繪制了 XOR 門,但其中一個(gè) XOR 門輸入為 0。

構(gòu)建這個(gè) LFSR。復(fù)位將 LFSR 重置為 1 。

模塊端口聲明

moduletop_module(

inputclk,

inputreset,//Active-highsynchronousresetto5'h1

output[4:0]q

);

題目解析

moduletop_module(

inputlogicclk,

inputlogicreset,//Active-highsynchronousresetto5'h1

outputlogic[4:0]q

);

always_ff@(posedgeclk)begin

if(reset)q<=?5'h1;

elsebegin

q[4]<=?1'd0^q[0];

q[3]<=?q[4];

????????q[2]?<=?q[3]?^?q[0]?;

????????q[1]?<=?q[2]?;

????????q[0]?<=?q[1]?;

????????end

????end

????????

endmodule

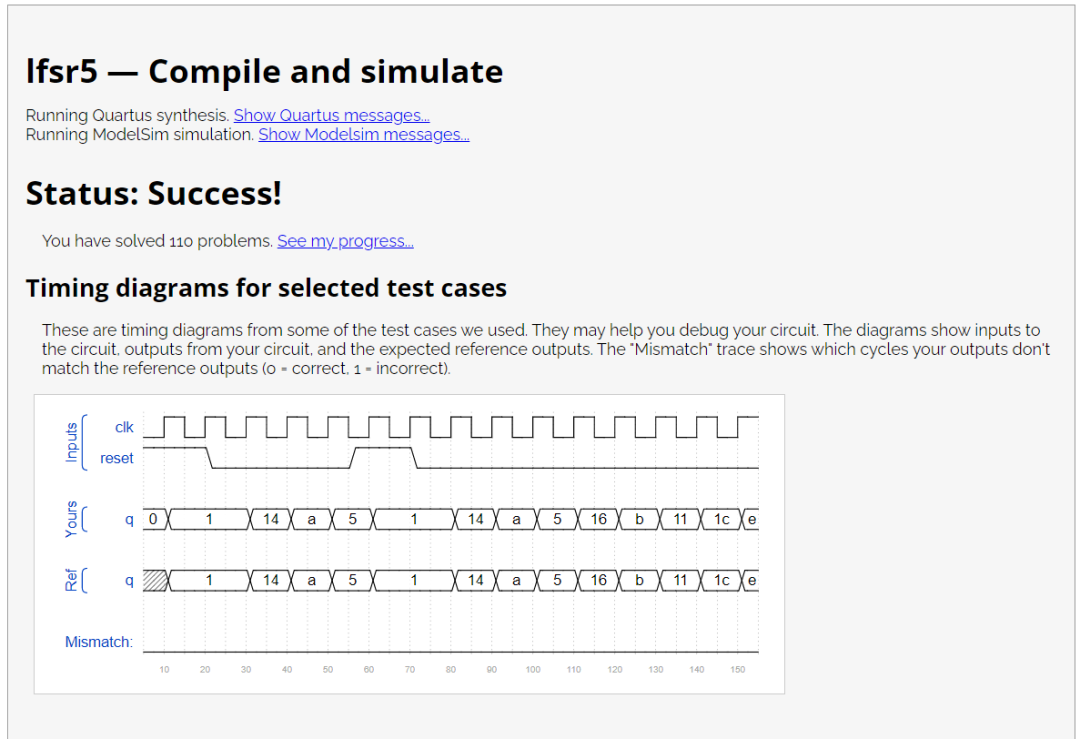

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

Problem 110-Mt2015_lfsr

題目說明

編寫此時(shí)序電路的 Verilog 代碼(可以使用子模塊進(jìn)行構(gòu)建,但頂層要命名為 top_module)。

模塊端口聲明

moduletop_module(

input[2:0]SW,//R

input[1:0]KEY,//Landclk

output[2:0]LEDR);//Q

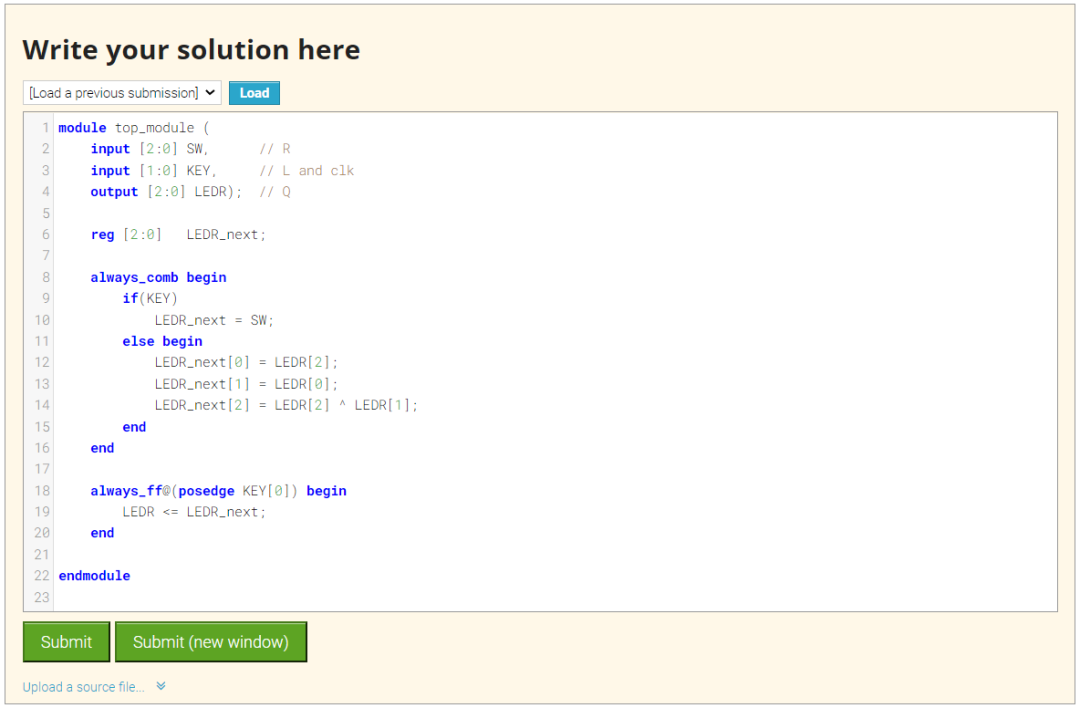

題目解析

本題的解答思路是將三個(gè)觸發(fā)器的輸出端 Q,輸入端 D,組合成一個(gè) 3bit 寬度的向量進(jìn)行設(shè)計(jì),使用一個(gè) always 塊實(shí)現(xiàn)寄存器組。與之相對的是思路是例化三個(gè)選擇器+觸發(fā)器的電路,分別連接三個(gè)部分的輸入輸出。

根據(jù)選擇器的 select 端的電平,觸發(fā)器組的輸入分別為外部輸入 SW 或者觸發(fā)器組輸出序列的組合邏輯,這里用:{LEDR[1]^LEDR[2],LEDR[0],LEDR[2]} 表示。

其他信號根據(jù)題目的要求連接。

moduletop_module(

input[2:0]SW,//R

input[1:0]KEY,//Landclk

output[2:0]LEDR);//Q

reg[2:0]LEDR_next;

always_combbegin

if(KEY)

LEDR_next=SW;

elsebegin

LEDR_next[0]=LEDR[2];

LEDR_next[1]=LEDR[0];

LEDR_next[2]=LEDR[2]^LEDR[1];

end

end

always_ff@(posedgeKEY[0])begin

LEDR<=?LEDR_next;

????end

????

endmodule

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中無波形。

這一題就結(jié)束了。

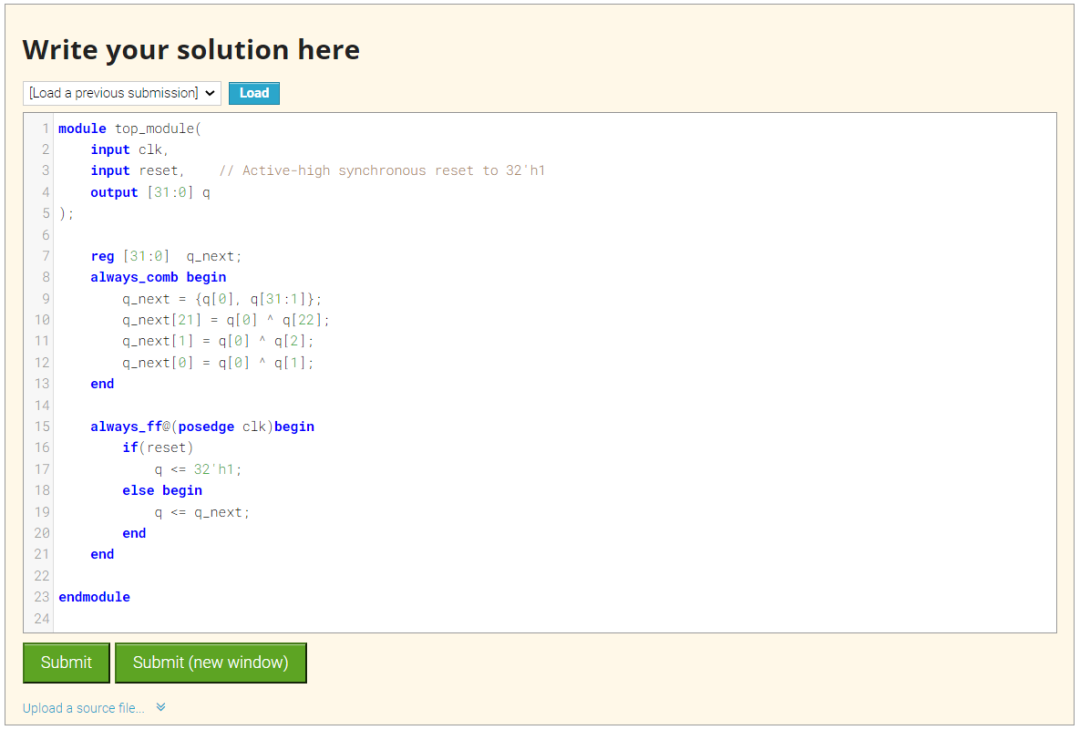

Problem 111-Lfsr32

題目說明

參考109題中的 5bit LFSR,實(shí)現(xiàn)一個(gè) 32bit LFSR,

抽頭點(diǎn)為32,22,2,1。

提示:32bit 的 LFSR 最好使用向量實(shí)現(xiàn),而不是例化 32 個(gè)觸發(fā)器。

模塊端口聲明

moduletop_module(

inputclk,

inputreset,//Active-highsynchronousresetto32'h1

output[31:0]q

);

題目解析

moduletop_module(

inputclk,

inputreset,//Active-highsynchronousresetto32'h1

output[31:0]q

);

reg[31:0]q_next;

always_combbegin

q_next={q[0],q[31:1]};

q_next[21]=q[0]^q[22];

q_next[1]=q[0]^q[2];

q_next[0]=q[0]^q[1];

end

always_ff@(posedgeclk)begin

if(reset)

q<=?32'h1;

elsebegin

q<=?q_next;

????????end

????end

?

endmodule

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中無波形。

這一題就結(jié)束了。

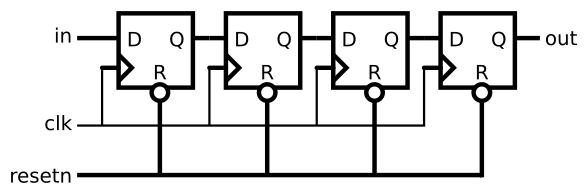

Problem 112-m2014_q4k

題目說明

實(shí)現(xiàn)下圖中的電路

模塊端口聲明

moduletop_module(

inputclk,

inputresetn,//synchronousreset

inputin,

outputout);

題目解析

實(shí)現(xiàn)一個(gè)帶有異步復(fù)位的移位寄存器。

moduletop_module(

inputlogicclk,

inputlogicresetn,//synchronousreset

inputlogicin,

outputlogicout);

varlogic[3:0]Q;

always_ff@(posedgeclk)begin

if(!resetn)Q<=?'0;

elseQ<=?{in,Q[3:1]}?;

????end

????

????assign?out?=?Q[0]?;

endmodule

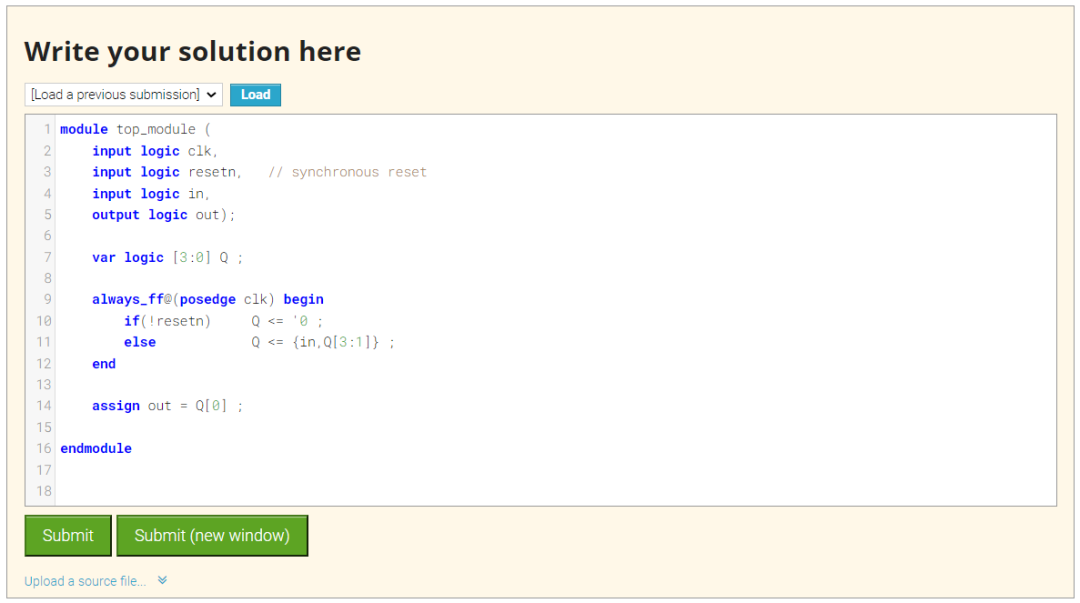

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中無波形。

這一題就結(jié)束了。

Problem 113-2014_q4b

題目說明

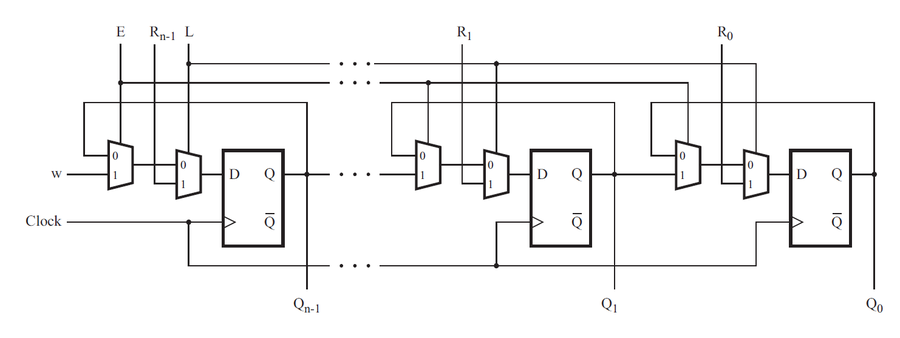

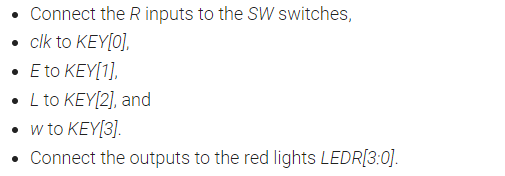

實(shí)現(xiàn)下圖中的 n bit 移位寄存器電路,這題希望使用例化的方式,例化 4 個(gè)選擇器+觸發(fā)器模塊實(shí)現(xiàn)一個(gè) 4bit 移位寄存器。另外還要進(jìn)行一些連線工作。

模塊端口聲明

moduletop_module(

input[3:0]SW,

input[3:0]KEY,

output[3:0]LEDR

);

題目解析

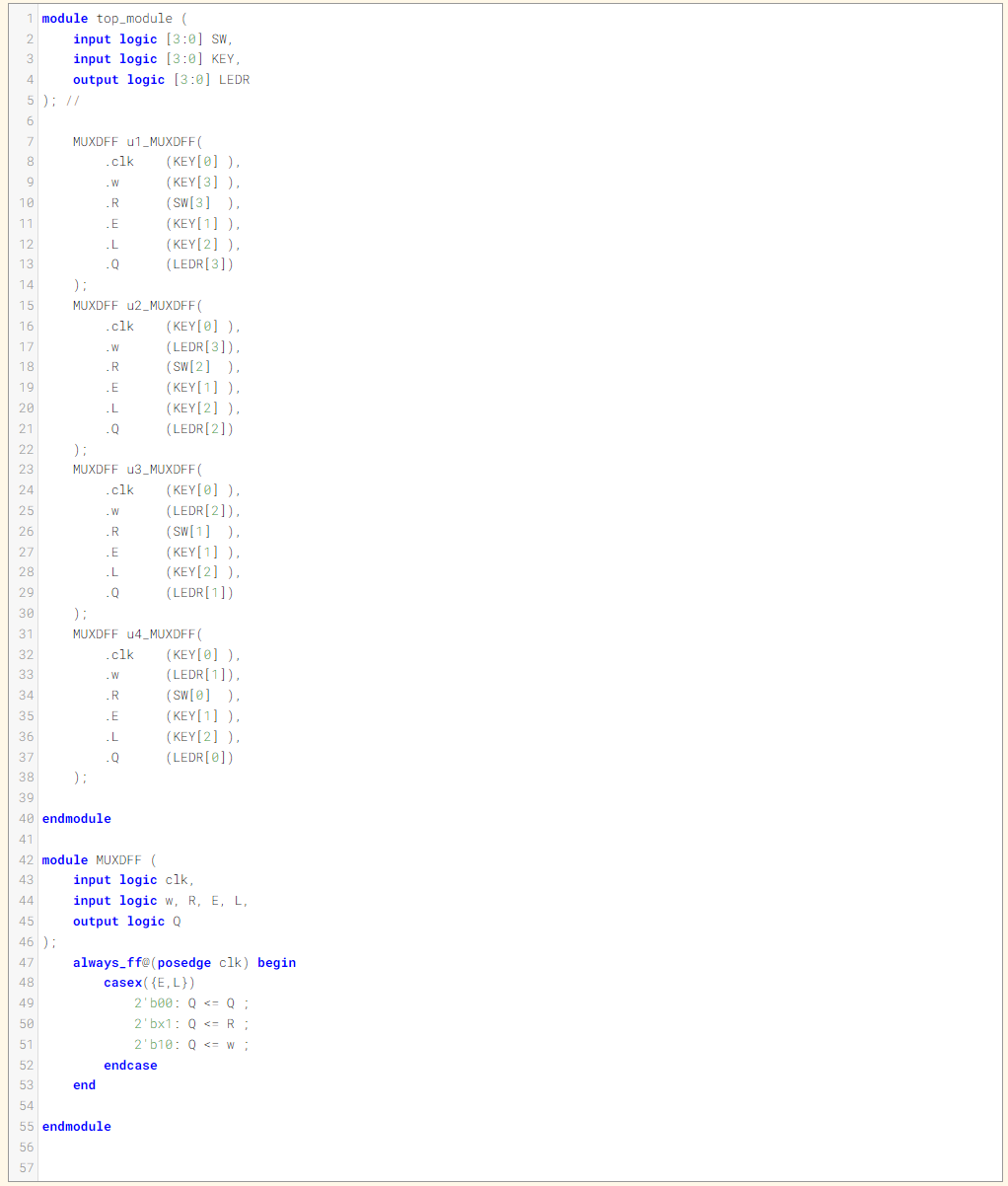

MUXDFT 模塊之前已經(jīng)實(shí)現(xiàn)了,復(fù)制過來即可,剩下的就是例化。

moduletop_module(

inputlogic[3:0]SW,

inputlogic[3:0]KEY,

outputlogic[3:0]LEDR

);//

MUXDFFu1_MUXDFF(

.clk(KEY[0]),

.w(KEY[3]),

.R(SW[3]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[3])

);

MUXDFFu2_MUXDFF(

.clk(KEY[0]),

.w(LEDR[3]),

.R(SW[2]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[2])

);

MUXDFFu3_MUXDFF(

.clk(KEY[0]),

.w(LEDR[2]),

.R(SW[1]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[1])

);

MUXDFFu4_MUXDFF(

.clk(KEY[0]),

.w(LEDR[1]),

.R(SW[0]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[0])

);

endmodule

moduleMUXDFF(

inputlogicclk,

inputlogicw,R,E,L,

outputlogicQ

);

always_ff@(posedgeclk)begin

casex({E,L})

2'b00:Q<=?Q?;

????????????2'bx1:Q<=?R?;

????????????2'b10:Q<=?w?;

????????endcase

????end

endmodule

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中無波形。

這一題就結(jié)束了。

Problem 114-ece241_2013_q12

題目說明

本題中實(shí)現(xiàn)的是一個(gè)和 8x1 結(jié)構(gòu)的存儲(chǔ)體相關(guān)的電路。存儲(chǔ)的輸入通過移入比特進(jìn)行,存儲(chǔ)的讀取類似于傳統(tǒng) RAM 中的隨機(jī)讀取,即可以指定讀出比特的位置,通過 3 個(gè)輸入端口指定讀取位置。

首先通過 8 個(gè)觸發(fā)器實(shí)現(xiàn)一個(gè) 8bit 深的移位寄存器。8個(gè)寄存器的輸出依次為 Q[0]...Q[7]。移位寄存器的輸入為 S,輸入首先會(huì)填充到 MSB(最高位),Q[0]。當(dāng) enable 信號控制移位,當(dāng)其有效時(shí)輸入數(shù)據(jù)并移位。此外,該電路有三個(gè)輸入端口 A,B,C 以及輸出端口 Z。工作的功能如下:當(dāng) ABC = 000 時(shí),Z = Q[0],當(dāng) ABC = 001 時(shí),Z = Q[1],以此類推。你的電路中只能包括一個(gè) 8bit 移位寄存器以及一個(gè)多路選擇器。(這就是個(gè)三輸入查找表 LUT 電路)

模塊端口聲明

moduletop_module(

inputclk,

inputenable,

inputS,

inputA,B,C,

outputZ);

題目解析

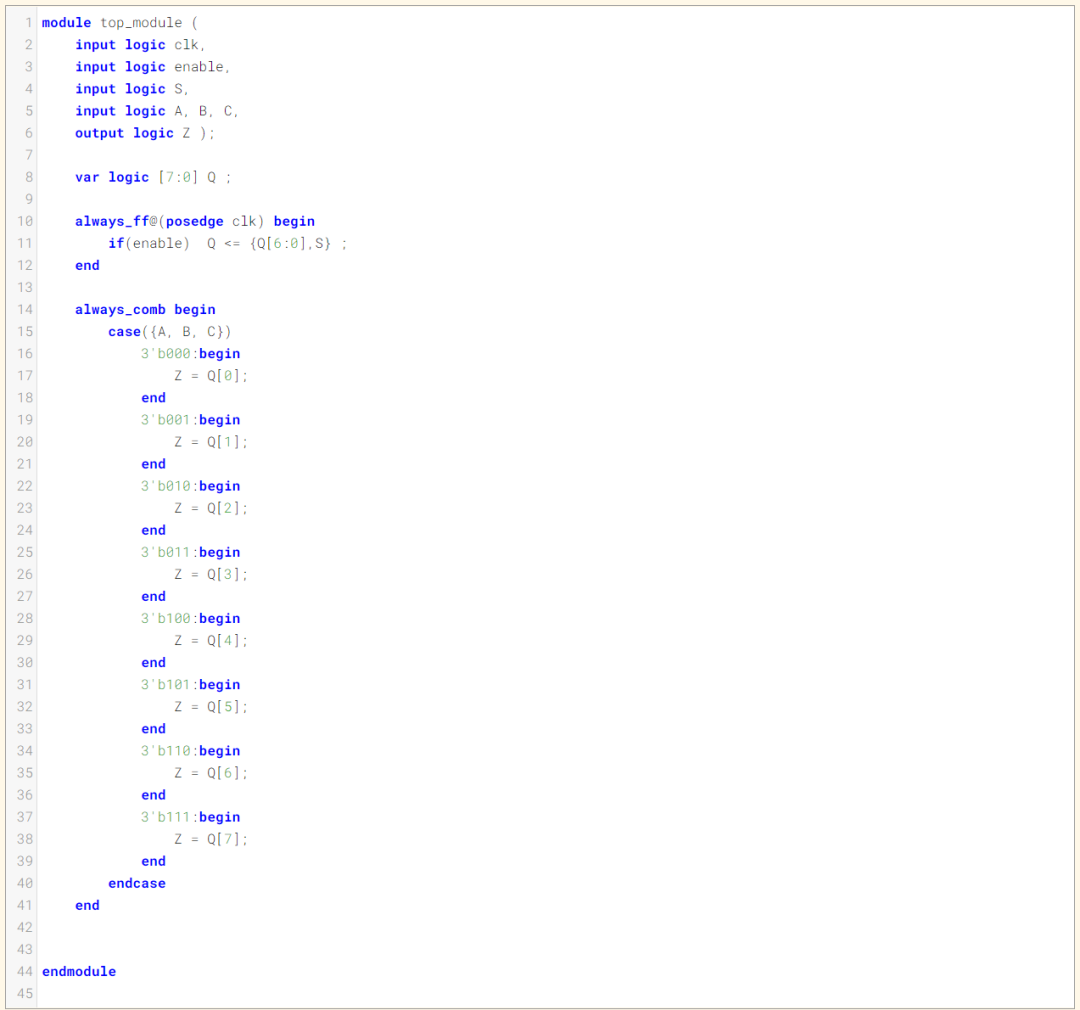

moduletop_module(

inputlogicclk,

inputlogicenable,

inputlogicS,

inputlogicA,B,C,

outputlogicZ);

varlogic[7:0]Q;

always_ff@(posedgeclk)begin

if(enable)Q<=?{Q[6:0],S}?;

????end

????

????always_comb?begin

????????case({A,B,C})

3'b000:begin

Z=Q[0];

end

3'b001:begin

Z=Q[1];

end

3'b010:begin

Z=Q[2];

end

3'b011:begin

Z=Q[3];

end

3'b100:begin

Z=Q[4];

end

3'b101:begin

Z=Q[5];

end

3'b110:begin

Z=Q[6];

end

3'b111:begin

Z=Q[7];

end

endcase

end

endmodule

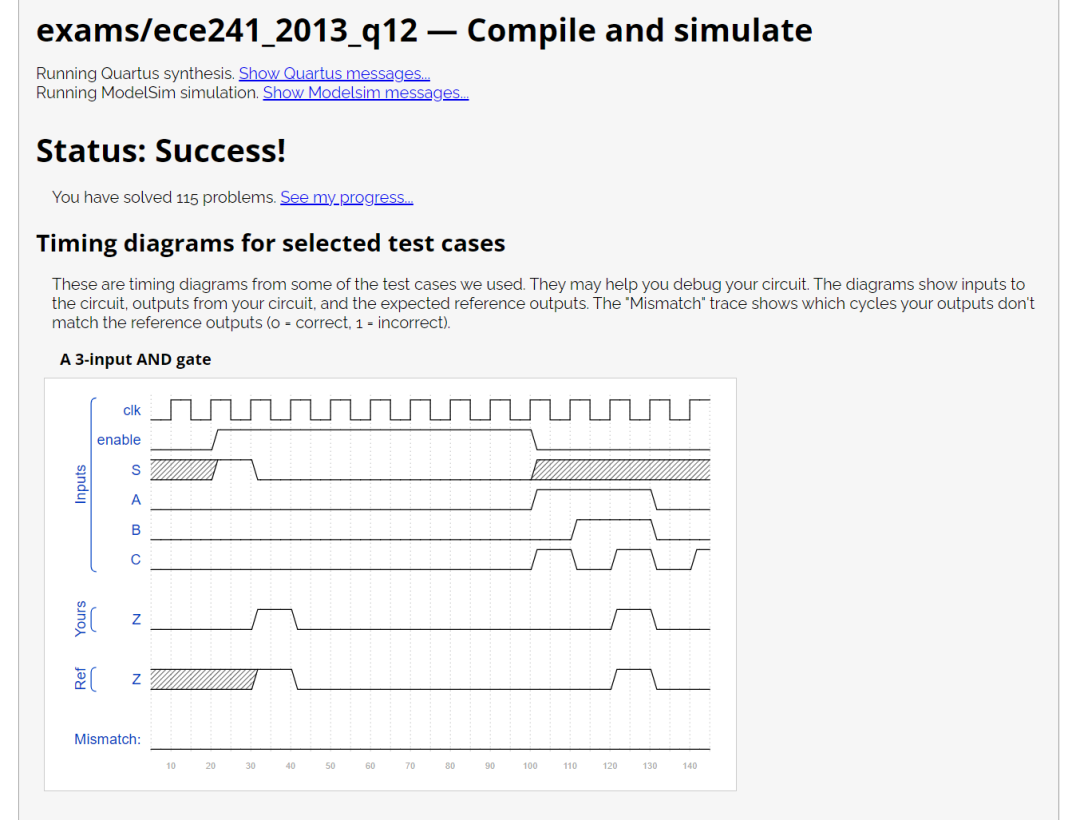

點(diǎn)擊Submit,等待一會(huì)就能看到下圖結(jié)果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網(wǎng)站會(huì)對比這兩個(gè)波形,一旦這兩者不匹配,仿真結(jié)果會(huì)變紅。

這一題就結(jié)束了。

總結(jié)

今天的幾道題就結(jié)束了,對于移位寄存器的使用以及算術(shù)/按位移位的理解還是有益處的。

最后我這邊做題的代碼也是個(gè)人理解使用,有錯(cuò)誤歡迎大家批評指正,祝大家學(xué)習(xí)愉快~

代碼鏈接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

審核編輯 :李倩

-

HDL

+關(guān)注

關(guān)注

8文章

332瀏覽量

49038 -

時(shí)序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

22361 -

移位寄存器

+關(guān)注

關(guān)注

4文章

352瀏覽量

23414

原文標(biāo)題:HDLBits: 在線學(xué)習(xí) SystemVerilog(十七)-Problem 106-114(移位寄存器)

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

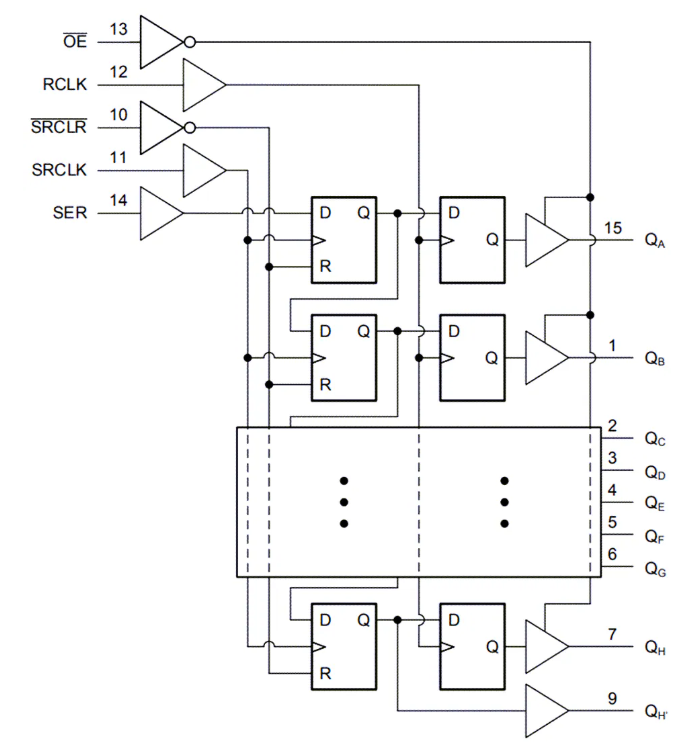

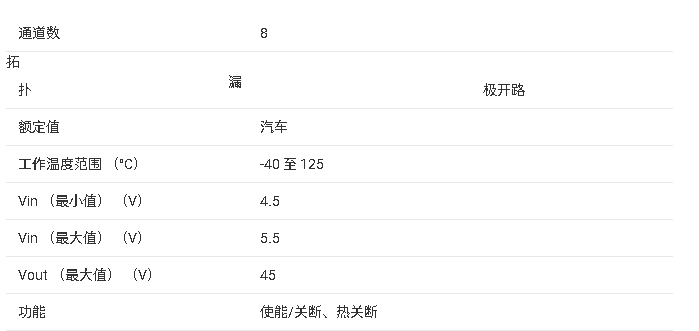

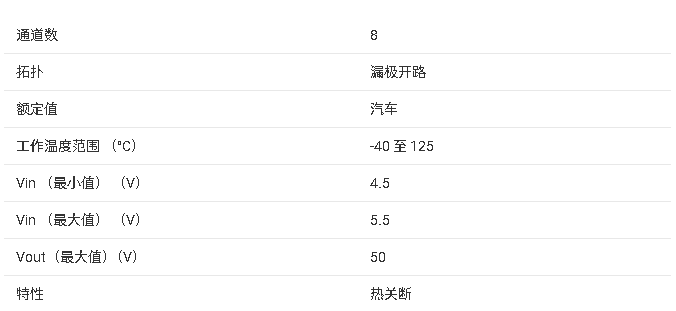

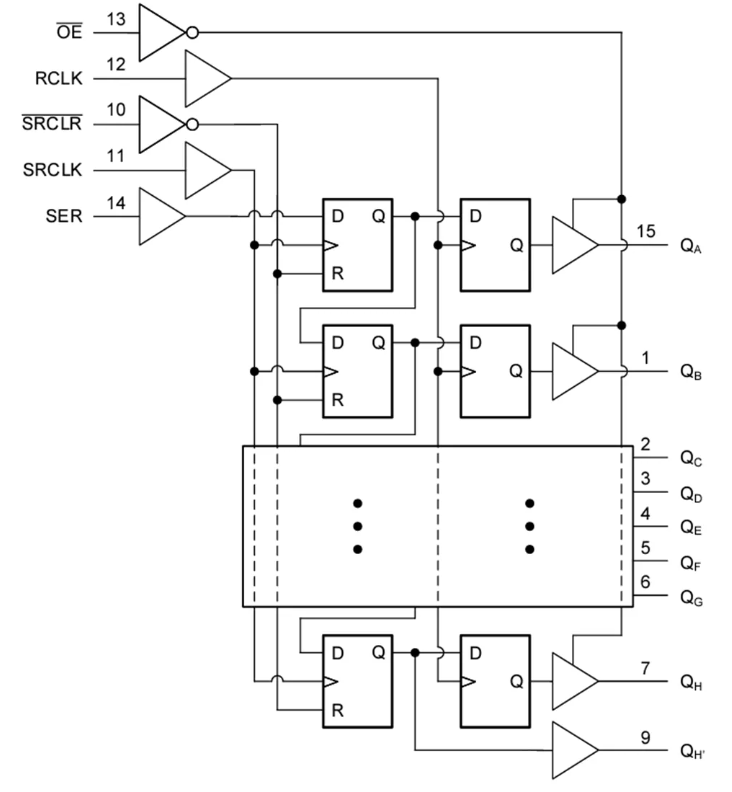

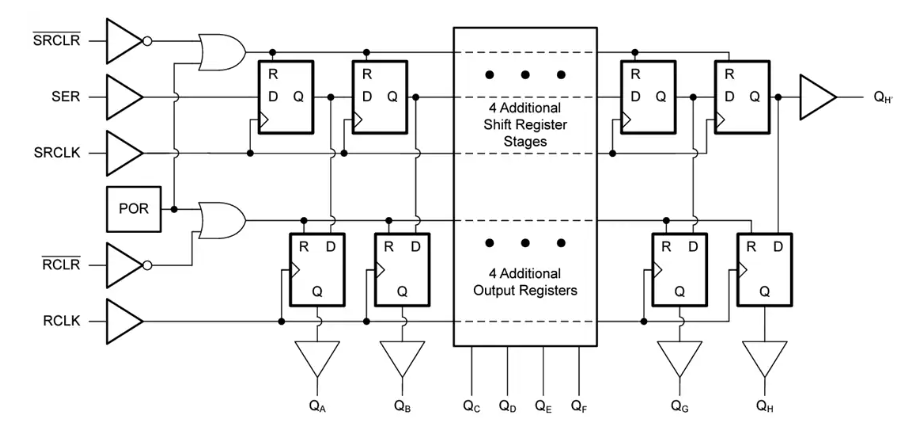

74AHC594:8位移位寄存器的詳細(xì)解析與應(yīng)用

74AHC595Q:汽車級8位移位寄存器的深度解析

74HC595 8位移位寄存器:設(shè)計(jì)與應(yīng)用全解析

74LV595A:8位移位寄存器的全方位解析

深入剖析74HCT595:8位移位寄存器的卓越之選

74AHCT595F:8位移位寄存器的特性與應(yīng)用解析

74HC164:8位串行輸入并行輸出移位寄存器的詳細(xì)解析

STP08CP05:低電壓、低電流8位移位寄存器的性能與設(shè)計(jì)解析

?SN74LVC595A 8位移位寄存器技術(shù)文檔總結(jié)

?SN74HCT595 8位移位寄存器技術(shù)解析與應(yīng)用指南

TPIC6595 8位功率移位寄存器技術(shù)文檔摘要

?TPIC6B595 8位功率移位寄存器技術(shù)文檔總結(jié)

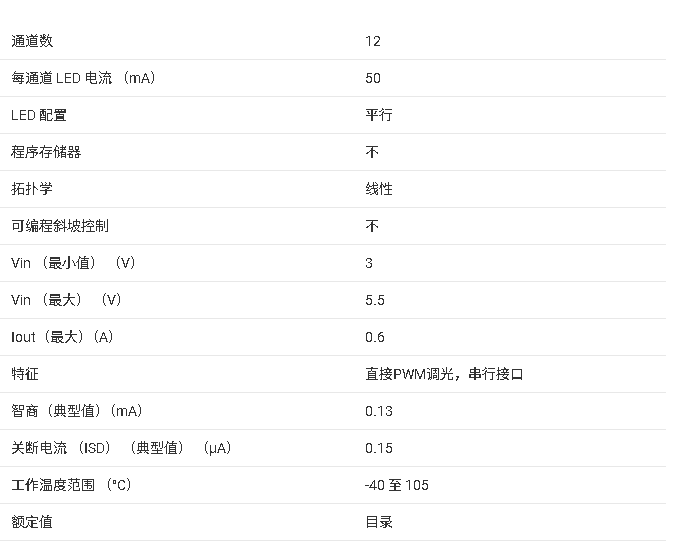

?TLC6C5912 12通道移位寄存器LED驅(qū)動(dòng)器技術(shù)文檔總結(jié)

SN74LV595B-EP低噪聲8位移位寄存器技術(shù)解析與應(yīng)用指南

Texas Instruments SN74LV8T594/SN74LV8T594-Q1移位寄存器特性/應(yīng)用/框圖

在線學(xué)習(xí)SystemVerilog:移位寄存器

在線學(xué)習(xí)SystemVerilog:移位寄存器

評論