如今,人們對先進封裝所面臨的挑戰(zhàn)已充分了解。然而,在薄化的器件芯片被封裝之前,就在晶圓級克服這些挑戰(zhàn)可以進一步增加價值和性能,同時降低擁有成本。

這些新材料已展示出超越其他現有解決方案的更出色性能,我們將結合示例,探討受益于使用經新技術制造的芯片的應用。

概述

更好的系統性能和功能、更低的功耗以及更小的外形尺寸是驅動當今封裝技術需要的主要因素。

廣泛用于大規(guī)模生產的晶圓級封裝 (WLP) 技術目前主要用于制造消費類產品,如智能手機、平板電腦和其他手持設備等。

許多封裝平臺正在部署,以便能夠實現更高性能的封裝、更低的成本、更小的外形尺寸,以及更高級別的集成。

晶圓級芯片尺寸封裝 (WLCSP) 因其成本性能比和無襯底封裝而具吸引力,但卻受到芯片尺寸的限制。

另一種替代方案,扇出型晶圓級封裝 (FOWLP) 技術正在研發(fā)和應用,因為它允許通過“扇出”與外部襯墊互連來增加 I/O 密度。最終使其具有更小的外形尺寸和更低的功耗。

異構集成的半導體封裝技術,如系統級封裝 (SIP) 和堆疊封裝 (PoP) 基礎結構,由于日益復雜的集成而面臨著重大挑戰(zhàn)。

晶圓級封裝挑戰(zhàn)

對于許多此類技術來說,薄化器件的襯底處理是制造流程中的一個主要挑戰(zhàn)。

硅晶片薄化至 <50 微米 (μm),或使用一個 RDL-first流程創(chuàng)建的重分布層 (RDL) 需非常小心且制造成本很昂貴。

處理過程要求使用通過臨時鍵合和解鍵合 (TBDB) 技術處理支撐襯底,以方便構建復雜的封裝基礎機構【1】。

使用熱塑性聚合物制造的臨時鍵合材料通常用于 TB/DB 工藝。

當與載體襯底一起使用時,它們能夠提供熱機械穩(wěn)定性,并使薄型器件襯底更易于處理。

然而,在更高的溫度下,這些材料表現得更像液體,隨著熔體粘度的降低,機械穩(wěn)定性也逐漸消失,材料軟化,從而降低了鍵合層的穩(wěn)定性。

器件晶圓可能發(fā)生變形和分層,導致下游工藝出現問題【2】。

現在我們已經對先進封裝目前所面臨的一些挑戰(zhàn)進行了高層次的研究,接下來,我們將更深入地探索其中的一些技術。

第 II 部分將研究chip-first和chip-last工藝程流之間的區(qū)別,以及為什么后者更受關注和歡迎。

Chip-First或Chip-Last流程

兩類主要的扇出型晶圓級封裝 (FOWLP) 技術是chip-first和chip-last工藝,又稱 RDL-first。

chip-first和chip-last工藝流程都需要高溫和高真空工藝來創(chuàng)建重分布層 (RDL)。

當今的 FOWLP 工藝所需的材料需要能夠承受高溫和惡劣的化學環(huán)境,同時保持對器件襯底的機械支持。

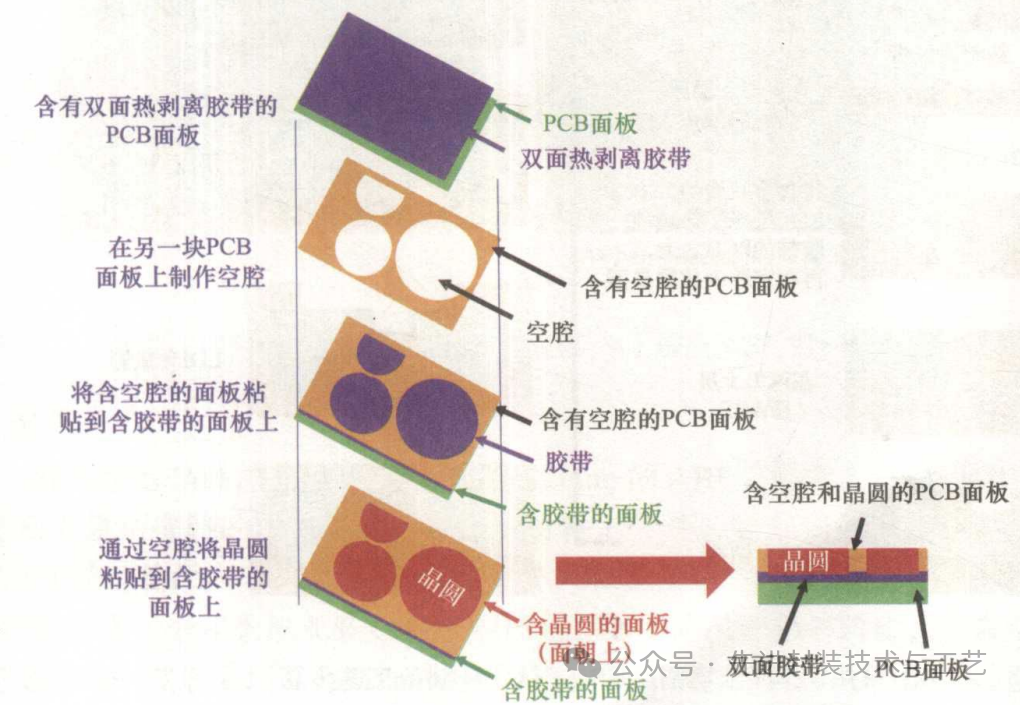

對于chip-first工藝來說,在熱壓過程中,先將單一芯片放置在用臨時鍵合材料或熱釋放膠帶 (TRT) 處理過的襯底上,然后再用環(huán)氧樹脂成型化合物 (EMC) 包覆成型并固化。

高溫電介質處理會產生應力并導致載體晶圓與 EMC 之間產生翹曲。

在 EMC 工藝流程中,由于襯底翹曲和鍵合材料軟化導致的芯片移動和偏離會造成 RDL 與嵌入芯片的錯位【1】。

晶圓在晶圓廠加工完畢后,芯片就會被切成小塊。然后,通過取放系統將芯片放置在基于環(huán)氧樹脂模塑料上的新的 200 毫米或 300 毫米圓晶圓上。

封裝工藝在這個新的晶圓上進行,切割芯片,以便獲得在扇出型封裝中的芯片。

盡管chip-first封裝在過去 10 年里一直用于生產,但這一工藝也存在一些挑戰(zhàn)。

在工藝流程中,晶圓可能會發(fā)生翹曲,嵌入的芯片可能會發(fā)生位移,從而導致良率下降。

另一方面,Chip-last/RDL-first還沒有得到廣泛應用,但是人們對這種方法的興趣正在增加,因為它使用了與chip-first非常不同的工藝。

RDL-first對于希望從chip-first FOWLP 過渡到尚未準備好應對 2.5D/3D 封裝的芯片制造商來說,是一種理想的工藝。

在 RDL-first工藝流程中,玻璃載體晶圓被涂上可去除的激光脫模材料,而 RDL 將在此基礎上構建。

激光脫模材料需要具有良好的熱穩(wěn)定性、機械穩(wěn)定性和化學穩(wěn)定性,才能經受住薄化、背面介質和沉淀這幾道工藝。

首先構建 RDL,然后安裝芯片。在該流程中,RDL 結構既可以進行電子測試,也可以進行目視檢查,以確定良率損失,從而避免將好的芯片放置在不好的位置。該流程特別適合于良率至關重要的大型 I/O 芯片。

為了確保 FOWLP 成功,無論采用chip-first還是 RDL-first方法,使用合適的鍵合材料來確保重組晶圓的穩(wěn)定性和均勻性則至關重要。Brewer Science 已經為此研制了一系列材料。

BrewerBOND?T1100和BrewerBOND?C1300系列材料代表了新一代鍵合系統,能夠提供更高的產量和熱穩(wěn)定性。

這些材料在較高的工藝溫度下提供了更好的機械穩(wěn)定性、良好的化學耐受性,不管是晶圓級或面板級工藝,都能在室溫下進行鍵合和解鍵合。

較低的總厚度變化 (TTV) 加上該系統機械強度的增加,可使超薄背面晶圓進行薄化,實現研磨后晶圓厚度小于50μm。

BrewerBUILD? 材料是單層高吸收材料,可用于 RDL 的構建和組裝,并專為激光燒蝕工藝而設計。

這些材料增加了 308 nm 至 355 nm 波長的吸光度,并在激光燒蝕工藝中為器件晶圓提供保護。

除了在激光燒蝕工藝中提高性能之外,新一代材料還具有較強的耐溶劑性,對多種材料的附著力高,并且燒蝕后具很好的溶劑清洗效果【2】。

用于FOWLP工藝的材料

本部分,我們將進一步探討在上文中介紹的用于扇出型晶圓級封裝 (FOWLP)的BrewerScience的BrewerBOND? T1100和BrewerBOND? C1300系列材料。

該系統由一種應用于玻璃載體晶圓的低 Tg 熱固性材料組成,然后鍵合至器件晶圓上,而器件晶圓上已經涂有相應的高 Tg 鍵合材料。

在室溫下鍵合之后,鍵合對既可以暴露在紫外線 (UV) 下,也可以在熱板上烘烤以固化熱固性材料

圖 1:典型工藝流程

當在 350°C 溫度下處理時,BrewerBOND?T1100 系列材料仍然可溶于溶劑,且在 300°C 以下幾乎沒有熔體流動。

涂層后,這種材料可以高度適形,甚至可以薄涂一層來覆蓋嚴重不平的表面。

圖 2 是使用掃描電子顯微鏡 (SEM),在 80-μm 焊料隆起焊盤上加工的 BrewerBOND?T1100 系列材料的 2.15-μm 薄膜的橫截面。

圖 2:BrewerBOND? T1100 材料的保形涂敷

BrewerBOND? C1300 系列材料擁有較高的熔態(tài)流動性(低 Tg),在固化前為液體的形態(tài)。

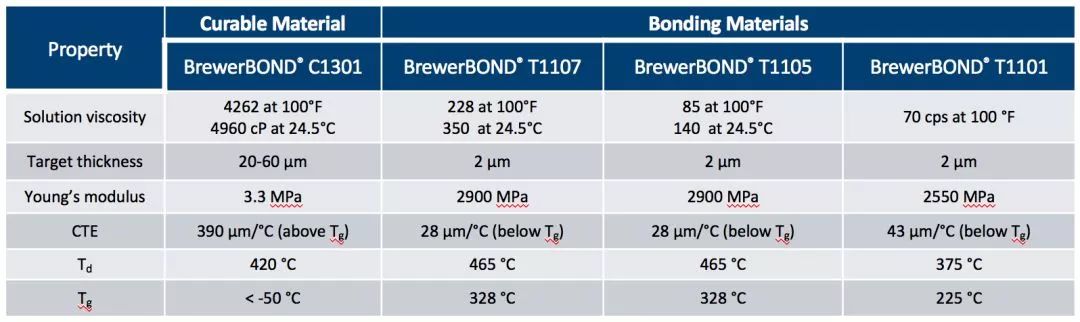

這樣能夠無需施壓就能在室溫下與 BrewerBOND?T1100 系列材料鍵合。鍵合后,這種材料需要一個固化過程來形成鍵合層。這一特性使得該系統即使在高溫下也具有較高的機械強度(表 1)。

表 1:材料屬性

電介質處理、金屬沉淀和金屬退火是需要使用高溫的工藝。

這些新一代 BrewerBOND? 材料能夠維持鍵合層的完整性,不會分解、釋氣或回流。

這些材料在 350°C 下加熱三個小時后,在氮氣中進行的等溫熱重分析 (TGA) 顯示,其重量損失不到 6%。

在 FOWLP 技術中,材料對有機和無機襯底以及金屬層的附著也是必要的。

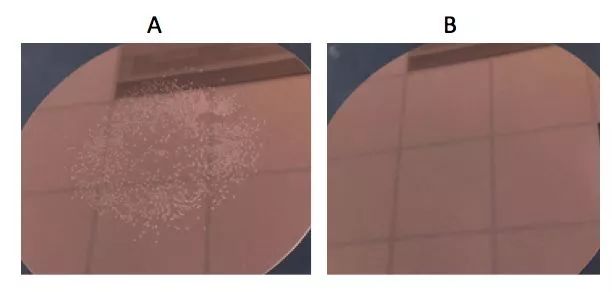

如圖 3 所示,新型鍵合材料對銅板和環(huán)氧樹脂成型化合物 (EMC) 均展示出良好的附著性。

圖 3:鍵合材料上的銅沉淀:(A) 材料附著性差,顯示有缺陷;(B)材料附著性好,無缺陷。

在鍵合過程中,BrewerBOND?T1100 系列材料連同 BrewerBOND?C1300 系列材料都顯示出對常見的下游濕化學工藝的耐受性。

工藝完成后,載體襯底可以通過機械釋放或激光燒蝕技術從薄化的器件上移除。

這兩種工藝均可在室溫下完成,且都是輕力技術,可與薄化襯底一起使用。

當使用激光燒蝕工藝時,BrewerBOND?T1100 系列材料吸收激光燒蝕過程中用于在 308 nm 和 355 nm 解鍵合時的能量,從而防止激光直接損傷器件晶圓。

解鍵合完成后,可以使用溶劑或氧等離子體蝕刻工藝從器件襯底上去除 BrewerBOND?T1100 系列材料。

可以使用 Dynaloy 出售的 Dynasolve? 220 清潔劑材料,從載體襯底上去除 BrewerBOND? C1300 系列材料。

總結

Brewer Science公司正在研發(fā)新型臨時鍵合材料和工藝,為 FOWLP 技術的發(fā)展鋪平道路。

當作為一個系統使用時,這些材料能夠改善在高真空和高溫下加工的薄化、鍵合晶圓的機械穩(wěn)定性。

耐化學性與室溫鍵合和解鍵合技術相結合,在降低擁有成本的同時,提供了附加價值并提高了性能。

對于 RDL-first工藝,Brewer Science 最近推出了用于構建和裝配的 BrewerBUILD? 材料,它可以成為熱釋放膠帶的優(yōu)選替代品。

這些新材料促進了低能量激光解鍵合工藝,為擁有低碳殘留的器件晶圓提供了更好的保護。

Brewer Science公司 將通過提供新一代材料來支持 FOWLP 技術,從而繼續(xù)推進晶圓級封裝 (WLP) 技術的發(fā)展。

-

晶圓

+關注

關注

53文章

5410瀏覽量

132310 -

封裝

+關注

關注

128文章

9251瀏覽量

148663

原文標題:解決晶圓級封裝難題的新方案

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

華為將向業(yè)界發(fā)布核心網網絡智能新方案

晶圓級MOSFET的直接漏極設計

什么是晶圓級扇入封裝技術

解決晶圓級封裝難題的新方案

解決晶圓級封裝難題的新方案

評論