ADCLK944:高速低抖動(dòng)時(shí)鐘扇出緩沖器的設(shè)計(jì)與應(yīng)用

在高速電路設(shè)計(jì)中,時(shí)鐘信號(hào)的穩(wěn)定性和低抖動(dòng)特性至關(guān)重要。今天我們來(lái)詳細(xì)探討一款由Analog Devices公司推出的高性能時(shí)鐘扇出緩沖器——ADCLK944。

文件下載:ADCLK944.pdf

1. 產(chǎn)品概述

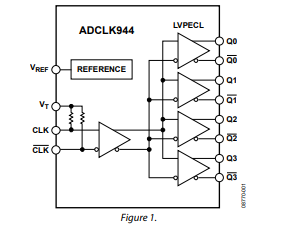

ADCLK944是一款基于Analog Devices專有XFCB3硅鍺(SiGe)雙極工藝制造的超快速時(shí)鐘扇出緩沖器,專為需要低抖動(dòng)的高速應(yīng)用而設(shè)計(jì)。它具有以下顯著特點(diǎn):

- 高工作頻率:最高可達(dá)7.0 GHz,能夠滿足高速數(shù)據(jù)傳輸和處理的需求。

- 低寬帶隨機(jī)抖動(dòng):僅50 fs rms,確保時(shí)鐘信號(hào)的穩(wěn)定性和準(zhǔn)確性。

- 片上輸入終端:集成了中心抽頭、差分、100 Ω的片上終端電阻,方便與各種輸入信號(hào)匹配。

- 寬電源電壓范圍:電源電壓(VCC - VEE)為2.5 V至3.3 V,具有良好的電源適應(yīng)性。

2. 應(yīng)用領(lǐng)域

ADCLK944的應(yīng)用非常廣泛,涵蓋了多個(gè)領(lǐng)域:

- 低抖動(dòng)時(shí)鐘分配:為系統(tǒng)提供穩(wěn)定、低抖動(dòng)的時(shí)鐘信號(hào),確保各模塊同步工作。

- 時(shí)鐘和數(shù)據(jù)信號(hào)恢復(fù):在信號(hào)傳輸過(guò)程中,恢復(fù)時(shí)鐘和數(shù)據(jù)信號(hào)的完整性。

- 電平轉(zhuǎn)換:實(shí)現(xiàn)不同電平信號(hào)之間的轉(zhuǎn)換,方便不同器件之間的接口。

- 無(wú)線和有線通信:在通信系統(tǒng)中,保證時(shí)鐘信號(hào)的穩(wěn)定傳輸,提高通信質(zhì)量。

- 醫(yī)療和工業(yè)成像:為成像設(shè)備提供精確的時(shí)鐘信號(hào),確保圖像質(zhì)量。

- ATE和高性能儀器:滿足測(cè)試和測(cè)量設(shè)備對(duì)高精度時(shí)鐘信號(hào)的需求。

3. 功能特性

3.1 輸入特性

ADCLK944具有差分輸入,可接受多種類型的輸入信號(hào),包括直流耦合的LVPECL、CML、3.3 V CMOS(單端),以及交流耦合的1.8 V CMOS、LVDS和LVPECL輸入。VREF引腳用于偏置交流耦合輸入。輸入電阻在單端模式下為50 Ω,差分模式下也為50 Ω。在實(shí)際應(yīng)用中,我們需要注意保持差分輸入電壓擺幅在大約400 mV p-p至不超過(guò)3.4 V p-p之間,輸入擺率應(yīng)不低于1 V/ns,否則會(huì)顯著影響輸出抖動(dòng)性能。

3.2 輸出特性

該器件具有四個(gè)全擺幅發(fā)射極耦合邏輯(ECL)輸出驅(qū)動(dòng)器。對(duì)于LVPECL(正ECL)操作,將VCC偏置到正電源,VEE偏置到地;對(duì)于ECL操作,將VCC偏置到地,VEE偏置到負(fù)電源。ECL輸出級(jí)設(shè)計(jì)為直接驅(qū)動(dòng)800 mV到50 Ω負(fù)載,總差分輸出擺幅為1.6 V。輸出上升/下降時(shí)間典型值為50 ps(20% - 80%,差分測(cè)量),傳播延遲溫度系數(shù)為100 fs/°C。

3.3 電源特性

電源電壓要求為2.375 V至3.63 V,在不同電源電壓下,電源電流有所不同。例如,當(dāng)VCC - VEE = 2.5 V ± 5%時(shí),負(fù)電源電流典型值為35 mA,正電源電流典型值為139 mA;當(dāng)VCC - VEE = 3.3 V ± 10%時(shí),負(fù)電源電流典型值為37 mA,正電源電流典型值為138 mA。此外,還具有電源抑制特性,如電源抑制比PSR_VCC為 -3 ps/V,輸出擺幅電源抑制比為28 dB。

4. 性能參數(shù)

4.1 時(shí)鐘輸入和輸出參數(shù)

| 參數(shù) | 符號(hào) | 最小值 | 典型值 | 最大值 | 單位 | 測(cè)試條件/注釋 |

|---|---|---|---|---|---|---|

| 輸入電阻(單端模式/差分模式) | 50 | Ω | ||||

| 輸出電壓高電平 | VOH | Vcc - 1.26 | Vcc - 0.76 | V | 負(fù)載 = 50 Ω至(Vcc - 2.0V) | |

| 輸出電壓低電平 | VoL | Vcc - 1.99 | Vcc - 1.54 | V | 負(fù)載 = 50 Ω至(Vcc - 2.0V) | |

| 單端輸出電壓 | Vo | 600 | 960 | mV | VOH - VoL,輸出靜態(tài) -500 μA至 +500 μA | |

| 電壓參考輸出電壓 | VREF | (Vcc + 1)/2 | V | |||

| 輸出電阻 | 250 | Ω |

4.2 時(shí)序特性參數(shù)

| 參數(shù) | 符號(hào) | 最小值 | 典型值 | 最大值 | 單位 | 測(cè)試條件/注釋 |

|---|---|---|---|---|---|---|

| 最大輸出頻率 | 6.2 | 7.0 | GHz | 差分輸出電壓擺幅 > 0.8V | ||

| 輸出上升/下降時(shí)間 | tR | 35 | 50 | 75 | ps | 20% - 80%,差分測(cè)量 |

| 傳播延遲溫度系數(shù) | tpp | 70 | 100 | 130 | fs/°C | ViD = 1.6Vp-p |

| 輸出到輸出偏斜 | 15 | ps | ViD = 1.6Vp-p | |||

| 器件間偏斜 | 35 | ps | ViD = 1.6Vp-p | |||

| 寬帶隨機(jī)抖動(dòng) | 50 | fs rms | ViD = 1.6Vp-p,8 V/ns,Vicm = 2V | |||

| 時(shí)鐘輸出相位噪聲(fIN = 1 GHz) | -118(100 Hz偏移) -135(1 kHz偏移) -144(10 kHz偏移) -150(100 kHz偏移) -150(>1 MHz偏移) |

dBc/Hz | 輸入擺率 > 1 V/ns |

5. 工作原理

5.1 時(shí)鐘輸入

ADCLK944接收差分時(shí)鐘輸入,并將其分配到四個(gè)LVPECL輸出。輸入配備了中心抽頭、差分、100 Ω的片上終端電阻,可接受多種類型的輸入信號(hào)。為了獲得良好的輸出抖動(dòng)性能,應(yīng)盡量避免輸入擺率低于1 V/ns的情況。同時(shí),對(duì)于過(guò)大的輸入信號(hào),可使用快速肖特基二極管進(jìn)行鉗位,以防止衰減器降低擺率。

5.2 時(shí)鐘輸出

LVPECL輸出設(shè)計(jì)為直接驅(qū)動(dòng)800 mV到50 Ω負(fù)載,為了確保最佳性能,需要使用適當(dāng)?shù)膫鬏斁€終端。當(dāng)高速信號(hào)需要路由超過(guò)一厘米時(shí),應(yīng)采用微帶線或帶狀線技術(shù),以保證適當(dāng)?shù)霓D(zhuǎn)換時(shí)間,防止輸出振鈴和脈沖寬度相關(guān)的傳播延遲色散。

6. PCB布局考慮

由于ADCLK944是為高速應(yīng)用設(shè)計(jì)的,因此在PCB布局時(shí)需要采用高速設(shè)計(jì)技術(shù)。具體注意事項(xiàng)如下:

- 電源平面:使用低阻抗的電源平面,為負(fù)電源(VEE)和正電源(VCC)提供低電感的回流路徑,確保最佳性能。

- 旁路電容:在每個(gè)VCC電源引腳附近放置1 μF的電解旁路電容和多個(gè)0.001 μF的高質(zhì)量旁路電容,并通過(guò)冗余過(guò)孔連接到地平面,以減少寄生電感和ESR。

- 傳輸線:避免輸入和輸出傳輸線的不連續(xù)性,因?yàn)檫@些不連續(xù)性可能會(huì)影響抖動(dòng)性能。

- 輸入匹配:在50 Ω環(huán)境中,輸入和輸出匹配對(duì)性能有顯著影響。緩沖器為CLK和CLK輸入提供內(nèi)部50 Ω終端電阻,需要使用陶瓷電容對(duì)終端電位進(jìn)行旁路,以防止輸入信號(hào)出現(xiàn)異常。

- ESD保護(hù):輸入引腳之間的ESD/鉗位二極管可防止輸入晶體管出現(xiàn)過(guò)大偏移,但由于ESD二極管的交流性能并非最優(yōu),當(dāng)需要鉗位時(shí),建議使用適當(dāng)?shù)耐獠慷O管。

- 散熱設(shè)計(jì):ADCLK944封裝上的暴露金屬焊盤(pán)既是電氣連接,也是散熱增強(qiáng)措施。需要將焊盤(pán)正確連接到VEE引腳,并通過(guò)PCB上的過(guò)孔網(wǎng)格將熱量傳遞到VEE電源平面,以實(shí)現(xiàn)良好的散熱效果。

7. 輸入終端選項(xiàng)

ADCLK944提供了多種輸入終端選項(xiàng),以適應(yīng)不同的輸入信號(hào)類型,如CML輸入、PECL輸入、交流耦合差分信號(hào)輸入和交流耦合單端輸入等。在實(shí)際應(yīng)用中,需要根據(jù)具體的輸入信號(hào)類型選擇合適的終端方式,以確保信號(hào)的穩(wěn)定傳輸。

8. 訂購(gòu)信息

ADCLK944有多種型號(hào)可供選擇,包括不同的溫度范圍和封裝選項(xiàng)。例如,ADCLK944BCPZ - R2、ADCLK944BCPZ - R7和ADCLK944BCPZ - WP等型號(hào)適用于 -40°C至 +85°C的溫度范圍,采用16引腳LFCSP_WQ封裝。此外,還有ADCLK944/PCBZ評(píng)估板可供使用。

總之,ADCLK944是一款性能優(yōu)異的時(shí)鐘扇出緩沖器,在高速電路設(shè)計(jì)中具有廣泛的應(yīng)用前景。在實(shí)際設(shè)計(jì)中,我們需要充分考慮其各項(xiàng)特性和參數(shù),合理進(jìn)行PCB布局和輸入輸出匹配,以確保系統(tǒng)的穩(wěn)定性和可靠性。你在使用類似時(shí)鐘緩沖器時(shí)遇到過(guò)哪些問(wèn)題呢?歡迎在評(píng)論區(qū)分享你的經(jīng)驗(yàn)和見(jiàn)解。

-

高速電路設(shè)計(jì)

+關(guān)注

關(guān)注

2文章

26瀏覽量

8373 -

adclk944

+關(guān)注

關(guān)注

0文章

3瀏覽量

1184

發(fā)布評(píng)論請(qǐng)先 登錄

ADCLK954:高性能時(shí)鐘扇出緩沖器的深度解析

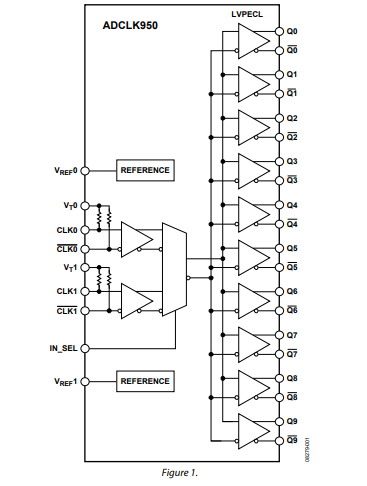

ADCLK950:高性能時(shí)鐘扇出緩沖器的技術(shù)剖析

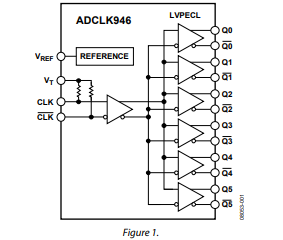

高速低抖動(dòng)時(shí)鐘扇出緩沖器ADCLK946:設(shè)計(jì)應(yīng)用全解析

ADCLK948:高性能時(shí)鐘扇出緩沖器的全面解析

探索ADCLK914:超快SiGe高速時(shí)鐘/數(shù)據(jù)緩沖器的卓越性能

高速電路的理想之選:ADCLK905/ADCLK907/ADCLK925 ECL時(shí)鐘/數(shù)據(jù)緩沖器

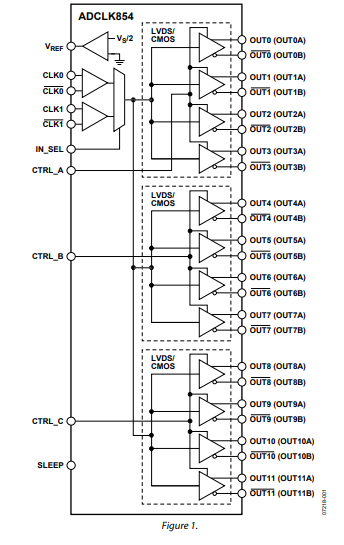

ADCLK854:低抖動(dòng)、低功耗時(shí)鐘扇出緩沖器的卓越之選

AD9508:低抖動(dòng)時(shí)鐘扇出緩沖器的卓越之選

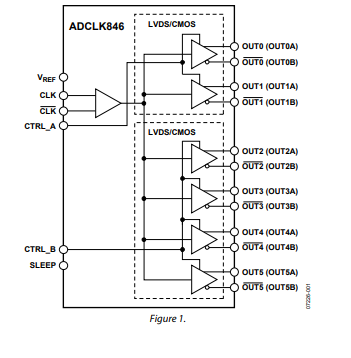

ADCLK846:低抖動(dòng)低功耗時(shí)鐘扇出緩沖器的卓越之選

深入解析LMK00105:超低抖動(dòng)LVCMOS扇出緩沖器與電平轉(zhuǎn)換器

ADCLK854 1.8 V、12 LVDS/24 CMOS輸出的低功耗時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK946采用SiGe工藝的6 LVPECL輸出時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK846 1.8 V、6 LVDS/12 CMOS輸出低功耗時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK950 2路可選輸入、10路LVPECL輸出、SiGe時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK944 2.5 V/3.3 V、4路LVPECL輸出、SiGe時(shí)鐘扇出緩沖器技術(shù)手冊(cè)

ADCLK944:高速低抖動(dòng)時(shí)鐘扇出緩沖器的設(shè)計(jì)與應(yīng)用

ADCLK944:高速低抖動(dòng)時(shí)鐘扇出緩沖器的設(shè)計(jì)與應(yīng)用

評(píng)論