探索ADCLK914:超快SiGe高速時鐘/數據緩沖器的卓越性能

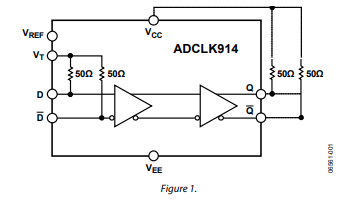

在高速電子設備中,時鐘和數據信號處理至關重要。Analog Devices推出的ADCLK914是一款采用專有互補雙極(XFCB - 3)硅鍺(SiGe)工藝制造的超快時鐘/數據緩沖器,在高速信號處理領域表現卓越。下面就為大家詳細介紹ADCLK914的特性、應用以及相關設計要點。

文件下載:ADCLK914.pdf

一、ADCLK914主要特性

1. 高速性能

ADCLK914具備高達7.5 GHz的工作頻率,160 ps的傳播延遲,輸出上升/下降時間僅為100 ps,隨機抖動低至110 fs。這些特性使得它在高速信號處理中能夠準確、快速地傳輸數據,有效減少信號延遲和失真。

2. 輸入特性

芯片具有片上輸入終端,輸入可接受LVPECL、CML、CMOS、LVTTL或LVDS(僅交流耦合)信號,并且提供VREF引腳用于偏置交流耦合輸入,增強了其與不同信號源的兼容性。

3. 輸出特性

采用高壓差分信號(HVDS)輸出級,可直接驅動1.9 V的信號到50 Ω負載,總差分輸出擺幅達3.8 V,能夠滿足驅動最新Analog Devices高速數模轉換器(DAC)的需求。

4. 溫度范圍

支持擴展工業溫度范圍(?40°C至 +125°C),適用于各種惡劣的工業環境,保證了在不同溫度條件下的穩定性能。

5. 電源要求

使用3.3 V電源((V{CC}-V{EE})),電源電流在一定范圍內變化,同時具備良好的電源抑制比,確保在電源電壓波動時仍能穩定工作。

二、ADCLK914應用領域

1. 時鐘和數據信號恢復

在高速通信系統中,信號在傳輸過程中可能會受到干擾和衰減,ADCLK914可以對時鐘和數據信號進行恢復,保證信號的準確性和穩定性。

2. 高速轉換器時鐘

為高速數模轉換器(DAC)提供精確的時鐘信號,確保轉換器能夠高速、準確地進行數模轉換。

3. 寬帶通信

在寬帶通信系統中,需要處理高速、高頻的信號,ADCLK914的高速性能和低抖動特性使其能夠滿足寬帶通信的需求。

4. 蜂窩基礎設施

在蜂窩基站等基礎設施中,需要穩定、高速的時鐘和數據信號處理,ADCLK914可以為其提供可靠的信號處理解決方案。

5. 高速線路接收器

用于高速線路接收器中,對輸入的高速信號進行緩沖和處理,提高接收器的性能。

6. 自動測試設備(ATE)和高性能儀器

在ATE和高性能儀器中,需要精確的時鐘和數據信號處理,ADCLK914可以滿足這些設備對高速、高精度信號處理的要求。

7. 電平轉換和閾值檢測

可以實現信號的電平轉換和閾值檢測功能,在不同電平的信號之間進行轉換和檢測。

三、ADCLK914設計要點

1. 電源和接地布局

由于ADCLK914是為高速應用設計的,因此在設計時必須采用高速設計技術。使用多層板的低阻抗電源平面(VEE和VCC),為開關電流提供最低電感的返回路徑,同時對輸入和輸出電源進行充分旁路。在每個電源引腳附近放置1 μF電解旁路電容和多個0.001 μF高質量旁路電容,并通過冗余過孔連接到GND平面,選擇低電感和低ESR的高頻旁路電容,避免寄生布局電感。

2. 輸入輸出匹配

ADCLK914內部為D和(overline{D})輸入提供了50 Ω終端電阻。返回端可以連接到提供的參考引腳,或連接到VCC - 2 V的電流源用于差分PECL,或連接到VCC用于直接耦合CML。當不使用(V_{REF})引腳時,應將其浮空以最小化功耗。同時,使用陶瓷電容對終端電位進行旁路,防止輸入信號因終端返回路徑中的寄生電感而出現異常。

3. 隨機抖動控制

ADCLK914在寬輸入范圍內可將隨機抖動降至最低。為了控制隨機抖動,應確保輸入信號有足夠的電壓擺幅,因為隨機抖動主要受輸入信號的壓擺率影響。盡可能使用快速肖特基二極管鉗位過大的輸入信號,避免使用衰減器,因為衰減器會降低壓擺率。輸入信號走線應采用低損耗電介質或具有良好高頻特性的電纜。

4. ESD防護

ADCLK914是靜電放電(ESD)敏感設備,盡管產品具有專利或專有保護電路,但高能量ESD仍可能對設備造成損壞。因此,在設計和使用過程中,應采取適當的ESD預防措施,避免性能下降或功能喪失。

四、總結

ADCLK914憑借其高速性能、廣泛的輸入兼容性、高壓差分輸出以及寬溫度范圍等特性,在高速時鐘和數據信號處理領域具有重要的應用價值。在設計使用ADCLK914時,需要注意電源和接地布局、輸入輸出匹配、隨機抖動控制以及ESD防護等要點,以確保其性能的充分發揮。大家在實際應用中是否遇到過類似高速緩沖器的設計挑戰呢?歡迎在評論區分享你的經驗和見解。

-

高速信號處理

+關注

關注

0文章

47瀏覽量

6551 -

adclk914

+關注

關注

0文章

4瀏覽量

1980

發布評論請先 登錄

探索ADCLK914:超快SiGe高速時鐘/數據緩沖器的卓越性能

探索ADCLK914:超快SiGe高速時鐘/數據緩沖器的卓越性能

評論