ADCLK948:高性能時鐘扇出緩沖器的全面解析

在高速電路設(shè)計領(lǐng)域,時鐘信號的精確分配和低抖動特性至關(guān)重要。ADCLK948作為一款由Analog Devices公司推出的時鐘扇出緩沖器,憑借其卓越的性能和豐富的功能,成為眾多工程師的首選。本文將對ADCLK948進行詳細的剖析,為電子工程師們在設(shè)計過程中提供全面的參考。

文件下載:ADCLK948.pdf

一、ADCLK948概述

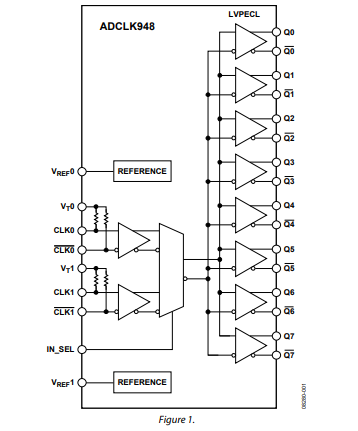

ADCLK948采用了Analog Devices專有的XFCB3硅鍺(SiGe)雙極工藝制造,是一款超快速時鐘扇出緩沖器,專為低抖動的高速應(yīng)用而設(shè)計。它具有兩個可選擇的差分輸入,能夠通過IN_SEL控制引腳進行切換,并且輸入配備了中心抽頭的100Ω片上終端電阻,可接受多種類型的輸入信號,包括直流耦合的LVPECL、CML、3.3V CMOS(單端)以及交流耦合的1.8V CMOS、LVDS和LVPECL輸入。同時,該器件擁有八個全擺幅發(fā)射極耦合邏輯(ECL)輸出驅(qū)動器,適用于LVPECL和ECL兩種工作模式。

二、關(guān)鍵特性與應(yīng)用場景

(一)關(guān)鍵特性

- 輸入靈活性:具備兩個可選擇的差分輸入,為設(shè)計提供了更多的靈活性。

- 高頻性能:高達4.8 GHz的工作頻率,滿足高速應(yīng)用的需求。

- 低抖動特性:75 fs rms的寬帶隨機抖動,確保時鐘信號的穩(wěn)定性。

- 片上輸入終端:集成了片上輸入終端電阻,簡化了電路設(shè)計。

- 電源兼容性:采用3.3 V電源供電,與常見的電源系統(tǒng)兼容。

(二)應(yīng)用場景

- 低抖動時鐘分配:在高速數(shù)字系統(tǒng)中,為多個器件提供穩(wěn)定的時鐘信號。

- 時鐘和數(shù)據(jù)信號恢復:對受損的時鐘和數(shù)據(jù)信號進行恢復和整形。

- 電平轉(zhuǎn)換:實現(xiàn)不同電平標準之間的轉(zhuǎn)換。

- 通信領(lǐng)域:廣泛應(yīng)用于無線和有線通信系統(tǒng)中。

- 醫(yī)療和工業(yè)成像:為成像設(shè)備提供精確的時鐘信號。

- ATE和高性能儀器:滿足測試和測量設(shè)備對時鐘信號的高要求。

三、電氣特性分析

(一)時鐘輸入和輸出特性

ADCLK948的時鐘輸入和輸出具有一系列重要的電氣特性。輸入方面,其輸入共模電壓范圍為VEE + 1.5 V至VCC - 0.1 V,輸入差分范圍為0.4 Vp-p,輸入電容為50 pF,輸入電阻在單端模式下為100 Ω,差分模式下為50 Ω。輸出方面,輸出電壓高電平為VCC - 1.26 V,輸出電壓低電平為VCC - 1.99 V,單端輸出電壓為610 mV,參考電壓輸出為(VCC + 1)/2,輸出電阻為235 Ω。

(二)時序特性

在時序特性方面,ADCLK948表現(xiàn)出色。其最大輸出頻率可達4.8 GHz,輸出上升時間和下降時間在40 - 90 ps之間,傳播延遲為175 - 245 ps,溫度系數(shù)為50 fs/°C,輸出到輸出的偏斜為9 - 25 ps,器件間的偏斜為45 ps。此外,該器件的集成隨機抖動為28 fs rms,寬帶隨機抖動為75 fs rms,串擾引起的抖動為90 fs rms。

(三)輸入選擇控制引腳特性

IN_SEL引腳用于選擇輸入信號,邏輯1電壓范圍為VCC - 0.4 V至VCC,邏輯0電壓范圍為VEE至1 V,邏輯1電流最大為100 μA,邏輯0電流最大為0.6 mA,電容為2 pF。

(四)電源特性

電源方面,ADCLK948的電源電壓要求為2.97 - 3.63 V,負電源電流典型值為96 mA,正電源電流典型值為288 mA,電源抑制比PSRvcc小于3 ps/V,輸出擺幅電源抑制比PSRwcc為28 dB。

四、絕對最大額定值與熱性能

(一)絕對最大額定值

為了確保ADCLK948的安全使用,需要了解其絕對最大額定值。電源電壓VCC - VEE最大為6 V,輸入電壓范圍為VEE - 0.5 V至VCC + 0.5 V,輸入電流最大為±40 mA,輸入引腳間的電壓差最大為±1.8 V,輸入終端與時鐘引腳間的電壓差最大為±2 V,輸出引腳的最大電壓為VCC + 0.5 V,最大輸出電流為35 mA,電壓參考范圍為VCC至VEE,工作溫度范圍為 - 40°C至 + 85°C,存儲溫度范圍為 - 65°C至 + 150°C。

(二)熱性能

在熱性能方面,可通過公式(T{J}=T{CASE }+(Psi{JT} × P{D}))來確定結(jié)溫,其中(T{J})為結(jié)溫,(T{CASE })為外殼溫度,(Psi{JT})可從表中獲取,(P{D})為功耗。此外,還提供了不同空氣流動條件下的熱阻參數(shù),如結(jié)到環(huán)境的熱阻(theta{JA})、結(jié)到板的熱阻(theta{JB})和結(jié)到外殼的熱阻(theta_{JC})等,這些參數(shù)對于PCB設(shè)計和散熱考慮非常重要。

五、引腳配置與功能描述

| ADCLK948采用32引腳的LFCSP封裝,其引腳配置和功能描述如下: | Pin No. | Mnemonic | Description |

|---|---|---|---|

| 1 | CLKO | 差分輸入(正)0 | |

| 2 | CLKO | 差分輸入(負)0 | |

| 3 | VREFO | 參考電壓,用于偏置交流耦合的CLKO和CLKO輸入 | |

| 4 | V0 | 中心抽頭,CLKO和CLKO輸入的100 Ω輸入電阻的中心抽頭 | |

| 5 | CLK1 | 差分輸入(正)1 | |

| 6 | CLK1 | 差分輸入(負)1 | |

| 7 | V-1 | 中心抽頭,CLK1和CL1輸入的100 Ω輸入電阻的中心抽頭 | |

| 8 | VREF1 | 參考電壓,用于偏置交流耦合的CLK1和CLK1輸入 | |

| 9 | NC | 無連接 | |

| 10, 15, 16, 25, 26, 31 | Vcc | 正電源引腳 | |

| 11,12 | Q7,Q7 | 差分LVPECL輸出 | |

| 13,14 | Q6,Q6 | 差分LVPECL輸出 | |

| 17,18 | Q5,Q5 | 差分LVPECL輸出 | |

| 19,20 | Q4,Q4 | 差分LVPECL輸出 | |

| 21,22 | Q3,Q3 | 差分LVPECL輸出 | |

| 23,24 | Q2,Q2 | 差分LVPECL輸出 | |

| 27,28 | Q1,Q1 | 差分LVPECL輸出 | |

| 29,30 | Q0,Q0 | 差分LVPECL輸出 | |

| 32 | IN_SEL | 輸入選擇,邏輯0選擇CLKO和CLKO輸入,邏輯1選擇CLK1和CLK1輸入 | |

| EPAD | 暴露焊盤,必須焊接到VEE電源平面 |

六、典型性能特性

(一)輸出波形

在典型性能特性方面,通過一系列圖表展示了ADCLK948的輸出波形、差分輸出電壓與頻率的關(guān)系、傳播延遲與差分輸入電壓和溫度的關(guān)系等。例如,在200 MHz和1000 MHz的時鐘頻率下,LVPECL輸出波形清晰穩(wěn)定,差分輸出電壓隨著頻率的增加而逐漸下降。

(二)傳播延遲

傳播延遲受差分輸入電壓、溫度和直流共模電壓等因素的影響。隨著差分輸入電壓的增加,傳播延遲逐漸減小;在不同溫度下,傳播延遲也會發(fā)生變化;直流共模電壓的變化同樣會對傳播延遲產(chǎn)生影響。

(三)電源特性

電源電壓對差分輸出電壓擺幅和電源電流有顯著影響。隨著電源電壓的增加,差分輸出電壓擺幅增大,電源電流也相應(yīng)增加。

(四)相位噪聲和隨機抖動

絕對相位噪聲在不同頻率偏移下表現(xiàn)良好,隨機抖動與輸入轉(zhuǎn)換速率有關(guān),輸入轉(zhuǎn)換速率低于4 V/ns時,輸出抖動性能會下降。

七、功能描述與設(shè)計考慮

(一)時鐘輸入

ADCLK948接受來自兩個輸入之一的差分時鐘輸入,并將選定的時鐘分配到所有八個LVPECL輸出。為了確保良好的性能,輸入信號的轉(zhuǎn)換速率應(yīng)不低于4 V/ns,對于過大的輸入信號,應(yīng)使用快速肖特基二極管進行鉗位,輸入信號的走線應(yīng)采用低損耗電介質(zhì)或具有良好高頻特性的電纜。

(二)時鐘輸出

ADCLK948的LVPECL輸出設(shè)計用于直接驅(qū)動800 mV到50 Ω的電纜或微帶/帶狀線傳輸線,終端電阻參考VCC - 2 V。在高速信號布線時,應(yīng)采用微帶或帶狀線技術(shù),以確保適當?shù)倪^渡時間,防止輸出振鈴和脈沖寬度相關(guān)的傳播延遲色散。

(三)時鐘輸入選擇

通過IN_SEL引腳的邏輯電平可以選擇不同的輸入信號,邏輯0選擇CLK0和CLK0輸入,邏輯1選擇CLK1和CLK1輸入。

(四)PCB布局考慮

在PCB布局方面,應(yīng)使用低阻抗的電源平面,為開關(guān)電流提供最低電感的返回路徑。同時,要對輸入和輸出電源進行充分的旁路,選擇合適的高頻旁路電容,避免輸入和輸出傳輸線的不連續(xù)性,以提高抖動性能。此外,ADCLK948的暴露金屬焊盤應(yīng)正確連接到VEE電源平面,以實現(xiàn)電氣連接和散熱功能。

(五)輸入終端選項

ADCLK948提供了多種輸入終端選項,包括直流耦合的CML、LVPECL、3.3 V CMOS輸入終端,以及交流耦合的LVDS和LVPECL輸入終端等。不同的終端方式適用于不同的輸入信號類型和應(yīng)用場景。

八、總結(jié)

ADCLK948作為一款高性能的時鐘扇出緩沖器,具有豐富的功能和卓越的性能。在設(shè)計過程中,工程師們需要充分了解其電氣特性、引腳配置、性能特性和設(shè)計考慮因素,以確保在實際應(yīng)用中能夠發(fā)揮其最佳性能。同時,合理的PCB布局和輸入輸出終端設(shè)計對于提高系統(tǒng)的穩(wěn)定性和可靠性至關(guān)重要。希望本文能夠為電子工程師們在使用ADCLK948進行電路設(shè)計時提供有益的參考。你在實際設(shè)計中是否遇到過類似時鐘緩沖器的應(yīng)用問題呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

高速電路設(shè)計

+關(guān)注

關(guān)注

2文章

26瀏覽量

8375 -

adclk948

+關(guān)注

關(guān)注

0文章

4瀏覽量

1195

發(fā)布評論請先 登錄

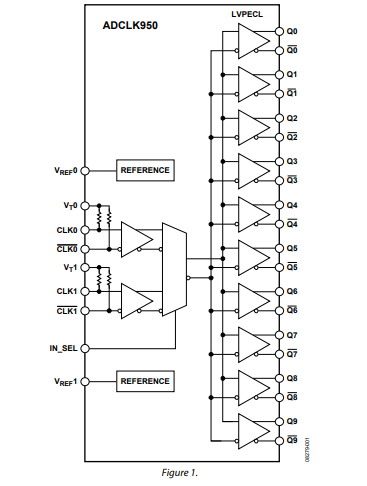

ADCLK950:高性能時鐘扇出緩沖器的技術(shù)剖析

高速低抖動時鐘扇出緩沖器ADCLK946:設(shè)計應(yīng)用全解析

ADCLK944:高速低抖動時鐘扇出緩沖器的設(shè)計與應(yīng)用

高速電路的理想之選:ADCLK905/ADCLK907/ADCLK925 ECL時鐘/數(shù)據(jù)緩沖器

ADCLK854:低抖動、低功耗時鐘扇出緩沖器的卓越之選

ADCLK846:低抖動低功耗時鐘扇出緩沖器的卓越之選

CDCLVC11xx:高性能LVCMOS時鐘緩沖器的卓越之選

探索LMK00101:高性能LVCMOS時鐘扇出緩沖器的卓越性能與應(yīng)用

探索LMK00804B:高性能時鐘扇出緩沖器的卓越之選

深入解析LMK00105:超低抖動LVCMOS扇出緩沖器與電平轉(zhuǎn)換器

深入解析RC190xx:PCIe Gen5/6高性能扇出緩沖器家族

深入解析SN65LVEL11:高性能1:2 ECL扇出緩沖器

ADCLK950 2路可選輸入、10路LVPECL輸出、SiGe時鐘扇出緩沖器技術(shù)手冊

ADCLK948 2路可選輸入、8路LVPECL輸出、SiGe時鐘扇出緩沖器技術(shù)手冊

ADCLK948:高性能時鐘扇出緩沖器的全面解析

ADCLK948:高性能時鐘扇出緩沖器的全面解析

評論