深入解析LMK00105:超低抖動LVCMOS扇出緩沖器與電平轉換器

一、引言

在電子設計領域,時鐘信號的精確分配至關重要。低抖動、高性能的時鐘緩沖器能夠確保系統的穩定性和可靠性。今天,我們將深入探討德州儀器(TI)的LMK00105超低抖動LVCMOS扇出緩沖器與電平轉換器,了解其特性、應用及設計要點。

文件下載:lmk00105.pdf

二、產品特性

2.1 輸出特性

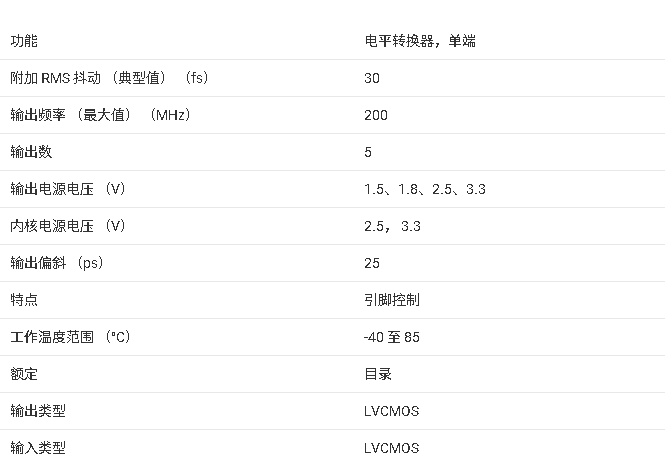

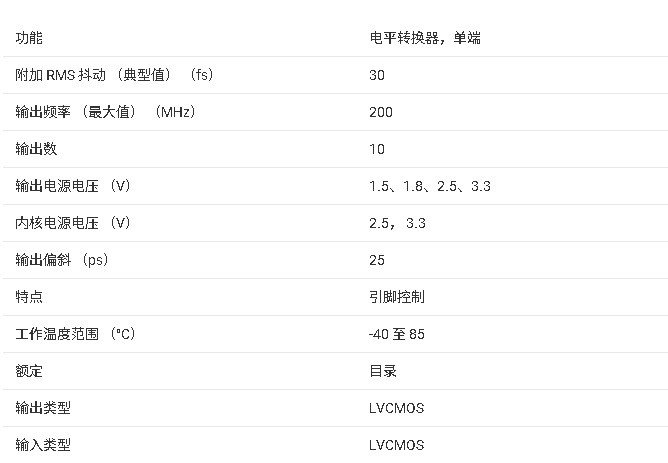

- 輸出數量與頻率:LMK00105擁有5個LVCMOS輸出,頻率范圍從DC到200 MHz,能夠滿足多種應用場景的時鐘分配需求。

- 輸出偏斜:輸出偏斜僅為6 ps,確保了各個輸出時鐘之間的精確同步。

- 附加相位抖動:在156.25 MHz頻率下(12 kHz至20 MHz),附加相位抖動低至30 fs,有效降低了時鐘信號的抖動,提高了系統的穩定性。

2.2 輸入特性

2.3 電源特性

- 核心電源電壓:可選擇3.3 V或2.5 V的核心電源電壓,滿足不同系統的供電需求。

- 可調輸出電源:每個輸出組的電源電壓可獨立調節,支持1.5 V、1.8 V、2.5 V和3.3 V,方便與不同電平的設備進行接口。

2.4 封裝特性

采用24引腳的WQFN封裝(4.0 mm × 4.0 mm × 0.8 mm),體積小巧,適合高密度的電路板設計。

三、應用領域

LMK00105的高性能特性使其在多個領域得到廣泛應用:

- 無線基站:用于RRU(射頻拉遠單元)的LO參考分配,確保射頻信號的穩定傳輸。

- 通信網絡:如SONET、以太網、光纖通道線卡以及光傳輸網絡,提供精確的時鐘信號。

- 服務器和存儲網絡:保障數據傳輸的準確性和穩定性。

- 醫療成像:為醫療設備提供低抖動的時鐘信號,提高圖像質量。

- 便攜式測試和測量設備:滿足設備對高精度時鐘的需求。

- 高端音視頻設備:確保音視頻信號的同步和高質量輸出。

四、詳細描述

4.1 功能框圖

LMK00105的功能框圖展示了其內部結構,包括核心電源(Vdd)、輸出電源(Vddo)、通用輸入、晶體振蕩器接口以及5個LVCMOS輸出。通過SEL引腳可以選擇時鐘輸入,OE引腳用于控制輸出使能。

4.2 特性描述

4.2.1 電源供應

- 雙電源操作:采用獨立的核心和輸出電源,可實現更低的功耗和輸出電平兼容性。Bank A和Bank B的輸出可以使用不同的Vddo電壓,但需確保Vddo不超過Vdd。

- 注意事項:在設計時,要注意避免Vddo電壓超過Vdd,防止內部ESD保護電路啟動。同時,不要斷開或接地任何Vddo引腳,因為這些引腳在輸出組內是內部連接的。

4.2.2 時鐘輸入

- 輸入選擇:通過SEL引腳選擇時鐘輸入,當SEL為0時選擇CLKin,為1時選擇OSCin(晶體模式)。

- 輸入信號要求:CLKin/CLKin*差分輸入可以接受AC或DC耦合的多種信號,但為了獲得最佳的相位噪聲和抖動性能,建議輸入信號的擺率不低于2 V/ns(差分)。

4.2.3 時鐘輸出

- 輸出使能:OE引腳控制輸出使能,當OE為高時,輸出啟用;為低時,輸出處于低電平狀態。OE引腳與輸入時鐘同步,確保無短脈沖輸出。

- 使用部分輸出:如果不需要使用所有5個輸出,未使用的輸出應保持浮空,以減少輸出電流消耗。

五、應用與實現

5.1 時鐘輸入

- 輸入信號兼容性:LMK00105的寬輸入共模電壓范圍和輸入電壓擺幅使其能夠接受多種信號。為了達到最佳性能,建議使用差分輸入信號,并確保輸入信號的擺率足夠高。

- 單端輸入處理:當使用單端輸入時,對于大信號輸入(如3.3 V或2.5 V LVCMOS),應在輸入附近放置50 Ω負載電阻進行信號衰減和線路端接,以防止輸入過驅動和反射。

5.2 時鐘輸出

- 輸出端接:LMK00105的LVCMOS驅動輸出阻抗標稱值為50 Ω,適合驅動50 Ω的傳輸線。如果驅動更高特性阻抗的傳輸線,應在驅動端附近放置串聯電阻進行源端接。

- 輸出銀行:LMK00105有兩個獨立供電的輸出銀行(Bank A和Bank B),可以提供不同的輸出電壓,方便與不同輸入閾值或輸入電源電壓的接收器進行接口。

5.3 典型應用示例

以一個將3.3-V LVCMOS振蕩器扇出到三個接收器設備的應用為例,LMK00105可以根據不同接收器的需求,通過不同的輸出銀行提供合適的時鐘信號。CPU和FPGA需要3.3-V LVCMOS輸入時鐘,而PLL需要1.8-V LVCMOS輸入信號,且需要AC耦合。

5.4 晶體接口

- 設計要求:LMK00105的晶體振蕩器電路支持基模AT切割晶體。電容和電阻的值取決于晶體的特性,例如對于一個25-MHz的晶體,建議選擇C1和C2為6.8 pF,RLIM為1.5 kΩ。

- 詳細設計步驟:根據晶體的負載電容(CL)、OSCin輸入電容(CIN)和PCB雜散電容(CSTRAY)計算離散電容值C1和C2。同時,要注意控制晶體的驅動電平,避免過驅動導致晶體老化、頻率偏移或失效。

六、電源供應建議

6.1 電源濾波

在電路板電源和芯片電源之間插入鐵氧體磁珠可以隔離時鐘驅動器產生的高頻開關噪聲,防止其泄漏到電路板電源中。選擇低直流電阻的鐵氧體磁珠非常重要,以確保為芯片提供足夠的隔離和穩定的電壓。

6.2 電源紋波抑制

電源紋波會對時鐘輸出產生相位調制和幅度調制,影響設備性能。對于LMK00105,通過測量注入紋波信號時時鐘輸出的單邊帶相位雜散電平來評估電源紋波抑制能力(PSRR)。

6.3 電源旁路

在Vdd和Vddo電源引腳附近放置高頻旁路電容(如100 pF),可以提高輸入靈敏度和性能。旁路和去耦電容應通過短走線或過孔與電源和接地平面連接,以減少串聯電感。

七、布局設計

7.1 布局準則

- 接地平面:使用實心接地平面為設備和旁路電容、時鐘源和目標設備之間提供低阻抗返回路徑,避免其他系統電路的返回路徑穿過設備的本地接地,以減少噪聲耦合。

- 電源引腳:遵循電源旁路部分的原理圖和布局示例,確保電源供應穩定。

- 差分輸入端接:輸入端接電阻應盡可能靠近CLKin/CLKin*引腳,避免或減少50-Ω輸入走線中的過孔,以減少阻抗不連續性。

- 輸出端接:串聯端接電阻應靠近CLKoutX輸出端,避免或減少50-Ω走線中的過孔。未使用的CLKoutX輸出應保持浮空,不進行布線。

7.2 熱管理

為了確保設備的可靠性和性能,應將芯片的結溫限制在125°C以內。通過在PCB上設計散熱焊盤和多個過孔連接到接地平面,以及在PCB另一側增加銅面積作為簡單的散熱片,可以有效降低結溫。

八、總結

LMK00105作為一款高性能的超低抖動LVCMOS扇出緩沖器與電平轉換器,具有豐富的特性和廣泛的應用領域。在設計過程中,我們需要充分考慮其電源供應、時鐘輸入輸出、布局設計等方面的要求,以確保系統的穩定性和可靠性。希望本文能夠為電子工程師在使用LMK00105進行設計時提供有價值的參考。

你在使用LMK00105的過程中遇到過哪些問題?或者對其設計有什么獨特的見解?歡迎在評論區分享交流。

-

時鐘緩沖器

+關注

關注

2文章

273瀏覽量

51949 -

電平轉換器

+關注

關注

1文章

267瀏覽量

21170

發布評論請先 登錄

LMK00105 HCMOS與LVCMOS晶振的輸出內阻是一樣的嗎?

LMK00301 3GHz 10路輸出超低附加抖動差動時鐘緩沖器和電平轉換器數據表

LMK00304 3GHz 4路輸出超低附加抖動差動時鐘緩沖器/電平轉換器數據表

LMK00306 3GHz 6路輸出超低附加抖動差動時鐘緩沖器/電平轉換器數據表

LMK00105具有通用輸入的超低抖動LVCMOS扇出緩沖器和電平轉換器數據表

具有通用輸入的LMK00101超低抖動LVCMOS扇出緩沖器/電平轉換器數據表

深入解析LMK00105:超低抖動LVCMOS扇出緩沖器與電平轉換器

深入解析LMK00105:超低抖動LVCMOS扇出緩沖器與電平轉換器

評論