傾佳楊茜-探本溯源:軟開關拓撲中位移電流與輸出電容遲滯損耗的量化難題與物理機制分析

在現代電力電子技術的發展進程中,高效率與高功率密度始終是轉換器設計的核心驅動力與終極目標。為了實現這一目標,提升開關頻率以減小變壓器、電感等無源磁性器件以及濾波電容的體積成為了必然的技術演進趨勢。然而,開關頻率的急劇提升直接導致了半導體功率器件開關損耗的線性甚至指數級增加,這不僅降低了系統的整體能量轉換效率,還引發了嚴重的熱管理難題與過熱風險 。為了打破這一由硬開關機制帶來的物理限制,工業界廣泛采用了零電壓開關(ZVS)和零電流開關(ZCS)等軟開關技術。在諸如LLC諧振轉換器、有源鉗位反激(ACF)轉換器以及移相全橋等軟開關拓撲中,理論上通過諧振網絡的能量交換,可以實現主功率開關管的無損導通與關斷。傳統觀念普遍認為,在理想的ZVS操作下,功率MOSFET的輸出電容(Coss?)在器件導通前已被完全放電,其內部存儲的能量(Eoss?)被無損地回饋到電源或諧振網絡中,從而徹底消除了容性開通損耗 。

然而,隨著電力電子行業邁入兆赫茲(MHz)超高頻應用時代,尤其是在硅超結(Si-SJ)MOSFET、碳化硅(SiC)MOSFET以及氮化鎵(GaN)高電子遷移率晶體管(HEMT)等先進寬禁帶(WBG)器件的廣泛應用過程中,學術界和工程界觀察到了一個打破傳統認知的反常物理現象:即使在完全滿足ZVS條件的諧振轉換器中,器件依然會產生不可忽視的額外溫升和巨大的功率損耗 。深入的物理與電氣特性研究表明,這部分被長期忽略的損耗來源于器件輸出電容的大信號遲滯效應(Hysteresis Behavior)。在器件的每一個充放電循環中,位移電流流經非理想的寄生電容結構,導致累積電荷(Qoss?)與漏源電壓(Vds?)的動態響應軌跡無法重合,從而形成了一個類似于磁性材料磁滯回線的非線性遲滯環。該閉合曲線所包圍的面積,即代表了單次開關周期內被轉化為焦耳熱而永久耗散的能量 。

傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

這一由位移電流引發的遲滯損耗的量化,目前正面臨著極大的工程與理論挑戰。一方面,由于兆赫茲級別頻率下電壓和電流探頭固有的相位偏移(Phase Skew)以及封裝內部復雜寄生參數的嚴重干擾,傳統的基于時域乘積積分的測量方法在量化微小遲滯損耗時會產生災難性的誤差 。另一方面,不同材料體系(如純硅、碳化硅、氮化鎵)內部的微觀物理機制存在根本差異,且此類損耗高度依賴于電壓瞬變率(dv/dt)、開關頻率的非線性動態以及結溫的波動,導致傳統數據手冊中基于靜態小信號測量的器件參數無法真實反映器件在實際大信號軟開關轉換器中的動態特征 。本報告將系統性地剖析高頻軟開關拓撲中位移電流與Coss?遲滯損耗的深層微觀物理機制,深入探討量化測量的技術瓶頸,并系統梳理多維度的數學物理建模方法及系統級拓撲緩解策略。

位移電流與輸出電容遲滯的深層微觀物理機制

在評估功率半導體器件的動態開關瞬態時,必須深刻理解漏極電流在不同階段的物理構成。當MOSFET的柵極被關斷,溝道導電能力急劇下降直至截斷時,外部電路強加于器件兩端的電流并沒有瞬間消失,而是發生物理本質的轉變,由原本的溝道漂移傳導電流轉變為對內部耗盡層寄生電容充電的位移電流(Displacement Current)。位移電流的宏觀數學表達式可以簡化為 Idisp?=Coss?(Vds?)dtdVds??。在理想的無損電容模型中,電場能量的存儲和釋放過程是完全對稱且可逆的,不會產生有功功率消耗。但在實際制造的高壓高頻功率半導體器件中,極其復雜的內部三維幾何結構、摻雜濃度梯度以及半導體材料晶格缺陷,使得結電容呈現出強烈的非線性動態響應與能量不可逆性 。

硅超結(Si-SJ)器件的電荷滯留效應與提取路徑阻抗

硅超結(Super-Junction)器件通過在漂移區引入深度交替的P型和N型摻雜柱(P/N Pillars),實現了內部電場的均勻分布,從而打破了傳統平面硅器件導通電阻與擊穿電壓之間的“硅極限”。然而,正是這種成就了極低導通電阻的復雜三維結構,成為了產生嚴重Coss?遲滯損耗的物理根源。在ZVS軟開關的關斷階段,位移電流需要對這一極其深厚的P/N耗盡層進行充電。在極低的漏源電壓區域,耗盡層的擴展和收縮不僅僅發生在水平方向,更主要的是沿著垂直于源極和漏極電極的方向發生劇烈變化。隨著Vds?以極高的dv/dt速率快速上升或下降,部分電子和空穴在高速電場牽引下,被“滯留”(Stranded Charge)在N柱和P柱的底部或深處 。

當漏源電壓在導通前夕開始下降時,這些被深層滯留的電荷必須響應外部電場的變化,通過已經被高度耗盡、呈現出絕緣體般極高電阻率的硅區域返回金屬電極。在這個電荷抽取的過程中,位移電流被迫流經這些高阻抗的狹窄路徑,不可避免地產生了劇烈的焦耳熱耗散(Resistive Power Dissipation)。這種由微觀電荷提取受阻引起的充放電路徑電氣不對稱,在宏觀的示波器屏幕上便表現為Qoss??Vds?曲線上明顯的發散和遲滯環。研究表明,由于超結MOSFET為了追求更低的特定導通電阻(RDS(on)?)而不斷縮小工藝節點和特征尺寸,增加P/N柱的深寬比,這種遲滯現象在最新一代超結器件中不僅沒有消失,反而變得更加顯著和難以控制 。盡管一些最新的TCAD仿真研究指出,采用溝槽填充外延生長(Trench-filling epitaxial growth)技術的新一代Si-SJ MOSFET能夠在一定程度上改善內部電場分布從而降低遲滯損耗,但硅基超結器件在此領域的固有劣勢依然存在 。

碳化硅(SiC)器件的終端電場耗散與不完全電離現象

對于碳化硅(SiC)寬禁帶器件,其輸出電容遲滯的物理機制與硅超結器件有著本質的區別。早期的工程經驗往往錯誤地認為SiC器件作為單極型多數載流子器件,其輸出電容應表現出近乎理想的無損特性。然而,近期的高端技術計算機輔助設計(TCAD)混合模式物理仿真和高精度實驗測試明確指出,SiC MOSFET中Coss?遲滯損耗的主要物理起源在于器件的邊緣終端區域(Edge Termination Region)以及深能級雜質的不完全電離(Incomplete Ionization)效應 。

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

在當前的SiC器件制造工藝中,鋁(Al)原子是最常用的P型摻雜劑。由于碳化硅材料的寬禁帶特性,鋁在SiC晶格中形成的受主能級非常深(通常在價帶頂上方約200 meV處)。在典型的室溫甚至更高的工作溫度下,這些深能級受主無法獲得足夠的熱激發能量來實現百分之百的完全電離。當SiC MOSFET被應用于諧振轉換器,處于具有極高dv/dt特性的瞬態開關過程中時,空間電荷區(即耗盡層)的邊界會以極高的速度移動。耗盡層的快速擴展與收縮要求晶格中的摻雜原子必須能夠極其迅速地捕獲或釋放載流子。然而,深能級陷阱對載流子的響應具有固有的時間常數,這一時間常數往往遠大于兆赫茲級別高頻開關帶來的納秒級瞬態時間。這種微觀物理上的“響應滯后”導致了瞬態空間電荷量無法緊緊跟隨外部漏源電壓的瞬時變化,形成了由不完全電離主導的位移電流相位延遲。這部分延遲所代表的無功功率未能全額返回電路,而是轉化為遲滯損耗 。

此外,從器件結構的宏觀電流分布來看,在關斷瞬態的高頻階段,流過溝道的電子電流已趨于零,此時外部施加的強電場使得微弱的柵極驅動環路放電電流幾乎全部轉化為對終端區電容(Cterm?)和有源區電容(Cacti?)進行猛烈充電的位移電流。由于邊緣終端區通常包含復雜的結終端擴展(JTE)或保護環結構,這些區域的電阻網絡在承受極高密度的高頻位移電流時會產生顯著的焦耳熱,這進一步加劇了SiC器件在軟開關下的總體開關損耗 。

氮化鎵(GaN)HEMT器件的動態陷阱與界面態效應

氮化鎵(GaN)高電子遷移率晶體管憑借異質結處形成的二維電子氣(2DEG)通道,實現了遠超硅和碳化硅的開關速度。盡管文獻中普遍指出GaN HEMT在三大主流功率器件中往往表現出最低的遲滯損耗水平,但它們同樣不可避免地受到Coss?相關損耗的困擾 。GaN器件中的遲滯損耗主要由外延生長層和絕緣緩沖層中故意引入的碳摻雜(C-doping)陷阱或復雜的材料界面態引起 。

在高電壓和大dv/dt的交變電場激發下,這些深能級陷阱對二維電子氣中的電子進行捕獲(Trapping)和釋放(De-trapping),而這兩個物理過程由于勢壘高度不同,存在極其顯著的時間常數差異。由于釋放過程往往比捕獲過程緩慢得多,導致電荷在充放電循環中的轉移出現嚴重的不對稱性,從而造成能量耗散。與SiC器件的規律類似,GaN HEMT的這種損耗與器件承受的峰值阻斷電壓呈高階指數級關系,并且表現出對開關頻率的非單調強相關性 。進一步的實驗表明,當結溫升高時,被捕獲的載流子能夠獲得更多的熱能,從而更容易擺脫陷阱的束縛(De-trapped)。因此,提高工作溫度可以在一定程度上緩解GaN HEMT的Coss?遲滯損耗,盡管這種溫度依賴性在不同廠商的器件結構中表現出較大差異 。

| 器件技術類型 | 遲滯損耗的核心物理機制 | 對高 dv/dt 的敏感性 | 溫度變化特性 | 參考文獻 |

|---|---|---|---|---|

| 硅超結(Si-SJ)MOSFET | P/N柱深處滯留電荷(Stranded Charge)及高阻抗提取路徑的焦耳熱 | 極高 | 結溫升高時載流子遷移率下降,阻抗增加,特性復雜 | |

| 碳化硅(SiC)MOSFET | 鋁受主深能級的不完全電離響應延遲,及邊緣終端區位移電流焦耳熱 | 極高 | 結溫升高促進深能級雜質電離,遲滯損耗顯著降低 | |

| 氮化鎵(GaN)HEMT | 緩沖層碳摻雜陷阱與異質結界面態的動態電子捕獲/釋放(Trapping/De-trapping)不對稱 | 高 | 溫度依賴性相對平緩,高溫通常有助于緩解陷阱效應 |

軟開關瞬態下位移電流損耗的量化與測量技術瓶頸

在兆赫茲級別的超高頻軟開關拓撲中,準確分離并量化由非線性輸出電容引起的微瓦至毫瓦級別的微小動態損耗,是一項挑戰當前測試儀器物理極限的艱巨任務。傳統的測量手段在面對高頻、大信號、強非線性的寄生參數時往往全面失效,導致對新一代半導體控制策略的評估產生誤導 。

探頭相位偏移(Phase Skew)帶來的虛假無功功率

最直觀也是最經典的開關損耗計算方法,是在示波器的時域窗口內對捕獲的電壓和電流波形乘積進行直接微積分運算(E=∫v(t)?i(t)dt)。然而,對于SiC和GaN這類寬禁帶器件而言,其開關轉換時間往往被壓縮在極短的納秒(ns)甚至亞納秒級別,且伴隨著高達數十千伏每微秒的dv/dt和極高的di/dt 。在此極端嚴苛的電氣條件下,電壓探頭與電流探頭之間固有的物理傳輸延遲差異顯得尤為致命。

即使是幾皮秒(ps)級的相位偏移(Phase Skew),也會導致電壓下降沿與電流上升沿的交疊區域發生錯位。在時域積分過程中,這種微小的時間錯位會將原本應在電路中往復吞吐的無功功率錯誤地計算為有功耗散,從而產生巨大的“虛假”功率,徹底掩蓋住原本就十分微弱的真實Coss?遲滯損耗 。這種測量不確定度在傳統雙脈沖測試(DPT)中被急劇放大,嚴重制約了對新型寬禁帶器件損耗的精準表征。

測量系統中的寄生參數與傳輸線高頻畸變效應

測試系統引入的外部寄生參數進一步惡化了高頻測量的保真度。在高頻下,測試線纜不能再被視為理想導線,而必須使用分布參數的傳輸線模型來分析。線纜的幾何形狀、長度以及絕緣材料構成的寄生電容和寄生電感,會導致高頻信號在傳輸過程中產生嚴重的相位失真和振幅衰減 。同時,高壓差分探頭連接器中心引腳與導電套管之間形成的寄生電容,也會對納秒級上升沿造成類似低通濾波的平滑效應,導致測得的轉換速率低于實際值 。

電流探頭的影響則更為直接。任何鉗形或串聯型電流探頭的接入,都會向原有的功率回路中引入額外的插入阻抗(Insertion Impedance),包括反射次級阻抗和磁芯材料的侵入阻抗 。此外,被測器件(DUT)封裝內部的共源極電感(Common-Source Inductance, CSI),即主功率電流路徑與柵極驅動環路共享的微小電感,在承受高di/dt時會產生反饋電壓,動態抵消實際施加在芯片柵氧層上的驅動電壓,從而拉長開關時間并帶來額外的開關損耗測量誤差 。在幾兆赫茲的高頻操作下,電流探頭磁芯還可能由于激勵損耗過大而發生自熱現象,導致磁芯飽和與非線性失真,使得波形峰值被削頂,最終的積分結果完全失去參考價值 。

小信號數據手冊參數與大信號實際動態的嚴重背離

長期以來,電力電子工程師在設計諧振腔時,高度依賴器件制造商提供的數據手冊(Datasheet)。然而,數據手冊中關于輸出電容Coss?和存儲能量Eoss?的描述存在著嚴重的系統性局限。通常,半導體廠商使用LCR測試表或高頻阻抗分析儀,在給器件施加一定直流偏置(DC Bias)的情況下,通過疊加一個極小振幅(如 VAC?=25mV)的高頻交流信號(典型測試頻率為 f=100kHz 或 1MHz)來測量靜態電容值 。

以BASiC Semiconductor(基本半導體)推出的一系列工業級與車規級高性能SiC MOSFET產品為例,我們可以清晰地看到這些標稱數據的分布狀態:

在TO-247封裝的高壓分立器件中,如B3M011C120Z(1200V, 223A, 典型 RDS(on)?=11mΩ),其在 VDS?=800V、f=100kHz 條件下測得的小信號 Coss? 為 250 pF,標稱的 Coss? 存儲能量 Eoss? 為 106 μJ 。而另一款型號 B3M013C120Z(1200V, 180A, 13.5mΩ)的 Coss? 為 215 pF,Eoss? 為 90 μJ 。

在超高功率的大電流模塊中,數據的量級發生了顯著變化。例如62mm封裝的半橋模塊 BMF540R12KHA3(1200V, 540A),其在極低的 2.2mΩ 導通電阻下,小信號測試的 Coss? 高達 1.26 nF,而 Eoss? 則達到了驚人的 509 μJ 。對于采用相同銅底板但電流等級較低的 BMF240R12KHB3 模塊(1200V, 240A, 5.3mΩ),其 Coss? 為 0.63 nF,Eoss? 為 263 μJ 。另一款34mm半橋模塊 BMF160R12RA3(1200V, 160A, 7.5mΩ)的 Coss? 為 420 pF,Eoss? 為 171 μJ 。

盡管這些詳盡的小信號參數和基于靜態積分計算出的Eoss?數據為軟開關諧振槽的初始無功功率匹配提供了重要基準,但小信號測量方法在微觀物理層面上存在致命缺陷。它本質上假定系統在特定直流偏置點附近是絕對線性的,并且載流子分布處于靜態熱平衡。這種方法完全抹殺了器件在實際變流器中經歷從0V瞬間躍變至800V或更高電壓時,其內部耗盡層所展現出的大信號瞬態非線性和電荷遲滯響應 [5, 11]。如前文所述,實際的瞬態電荷與電壓的非線性關系(Q-V行為)極其強烈地依賴于施加在器件兩端的瞬態電壓掃移速率(dv/dt)。因此,如果設計人員僅僅基于數據手冊中的小信號Coss?和靜態Eoss?直接計算高頻ZVS損耗,得出的理論功耗往往會比系統的實際真實功耗低出數倍,從而導致熱設計嚴重裕度不足 。

突破測量極限:高級表征與量化方法論

鑒于傳統雙脈沖測試和時域乘積積分法在量化極低遲滯損耗時的結構性局限,學術界和領先的工業研究機構發展出了一系列徹底摒棄傳統電流直接測量、專門針對Coss?遲滯量化的高階實驗物理方法 。

改進的Sawyer-Tower (ST) 電路法

Sawyer-Tower電路最初在1930年代被物理學家用于表征鐵電材料的電極化強度和介電常數非線性,近年來被創新性地改進并引入到兆赫茲功率半導體Coss?遲滯損耗的精密測量中 。該方法的核心思想是通過電容串聯分壓的原理,將極難測量的瞬態位移電流轉化為容易高精度捕捉的低壓節點電壓。

在具體實施中,測試系統在被測器件(DUT)的源極與地之間串聯一個經過嚴格校準的高精度、低寄生電感(ESL)、極低等效串聯電阻(ESR)的線性傳感電容(Csense?)。設計上要求 Csense? 的容值必須遠大于 DUT 處于高壓下的 Coss?。由于二者處于同一串聯支路,流經它們的瞬態位移電流在任何時刻都絕對相等。基于電荷守恒定律,DUT 內部寄生結電容上累積或釋放的電荷量,可以直接通過測量 Csense? 兩端的電壓來線性映射計算(Qoss?=Csense??Vsense?) 。

通過將高帶寬示波器的X軸通道設置為 DUT 兩端的漏源電壓降(Vds?),Y軸通道設置為實時推算出的動態電荷量(Qoss?),系統可以直接在屏幕上繪制出實時的大信號 Q-V 遲滯回線。根據能量微積分原理,該閉合非線性曲線所包圍的幾何面積,從物理量綱上講,即為單次充放電循環中不可逆耗散的焦耳能量(Ediss?=∮Vds?dQoss?) 。ST 方法的革命性優勢在于它徹底規避了對極短時間內的高頻大瞬態電流進行直接采樣,完全依賴于兩個電壓探頭信號的獲取,從而從根源上大幅消除了由于 V-I 相位偏移帶來的無功系統誤差。然而,隨著測試頻率逼近十兆赫茲(10 MHz)級別,ST 方法也面臨著由于傳感電容自身寄生電感引發的局部高頻諧振問題,這要求在PCB布線層面進行極端的阻抗控制 。

高精度量熱法(Calorimetric Method)與熱阻抗校準

當量電域的測量受到頻帶和電磁干擾(EMI)的物理限制時,量熱法被視為評估半導體器件總開關損耗的“黃金標準”(Ground Truth),因為它是直接建立在宏觀能量守恒定律基礎之上的 。該方法完全放棄了從容易畸變的電氣端子提取瞬態損耗,而是直接測量 DUT 在特定穩態工作點下產生的焦耳熱。

在高級量熱測試平臺中,通常將器件置于精心設計的絕熱真空腔室中,或者安裝在配備了極高靈敏度熱敏電阻(NTC)和恒溫液冷系統的定制散熱器上。以 BASiC Semiconductor 的工業模塊為例,如 BMF240R12E2G3 和 BMF540R12MZA3,它們內部均原生集成了高精度 NTC 溫度傳感器,其室溫標稱阻值通常設定為 5 kΩ,并通過精確標定的 Steinhart-Hart 方程或 B-Value 公式(如 B25/50?=3375K)進行芯片附近結溫的精準數字反饋 。

在執行量熱法實驗時,首先在嚴苛的ZVS軟開關條件下(例如將其作為 Class-E 逆變器或無源無損諧振電路的主開關)運行測試電路,使其達到長時間的穩態熱平衡,并精確記錄此時 DUT 的熱平衡絕對溫度或 NTC 電阻值。隨后,切斷高頻交流驅動,將電路轉換為純直流校準模式,通過高精度可編程直流電源向器件的體二極管注入非常微弱且精確受控的直流電流,以產生純粹的直流導通焦耳熱。不斷調節直流電流,直至器件達到與高頻 ZVS 運行下完全相同的絕對溫度上升(ΔT) 。此時,系統注入的直流有功功率(Pdiss?=IDC??Vf?)即在物理等效上完全等于高頻運行時的難以測量的位移電流交流遲滯損耗 。盡管量熱法徹底免疫了探頭帶寬限制和惡劣的電磁干擾(EMI),但其由于需要漫長的熱平衡等待時間,測試周期通常極長,且對周邊實驗環境的熱隔離和標定要求極高,通常僅被用作基準測試(Benchmark),而難以作為工業界快速篩選大批量器件的常規流水線手段 。

非線性諧振衰減與能量守恒測試法

非線性諧振法(Non-Linear Resonance Method)提供了一種介于電氣法與量熱法之間的折中表征方案。該方法利用 DUT 本身的非線性寄生輸出電容,與一個外部經過特殊設計、極低損耗的高品質因數(High-Q)空氣芯電感構成一個無源的 RLC 阻尼諧振回路 。

測試開始時,通過外部輔助開關向該 LC 諧振回路注入預定的初始能量(即建立初始的 Vds? 電壓),隨后切斷外界能量源,允許回路在內部物理機制的作用下進行自由阻尼衰減振蕩。工程師只需使用單一的高精度電壓探頭觀測 Vds? 振蕩波形的包絡線衰減速率,結合預先通過網絡分析儀精確表征過的外部高Q電感的寄生電阻與集膚效應損耗,即可利用能量守恒原理反推出器件在特定電壓跨度與特定振蕩頻率下的 Coss? 遲滯積分損耗。這種方法能夠實現貼近實際應用的大信號高頻測量,且只需要電壓測量,避免了電流探頭引入的誤差。然而,由于外部空心電感本身在兆赫茲高頻大電流下仍然不可避免地存在鄰近效應和微弱輻射損耗,將其誤差從系統總衰減量中完美剝離,在數學上是一個十分敏感且復雜的反問題 。

為了挽救時域 V-I 乘積積分法的可用性,研究人員也在致力于開發軟件層面的相位偏移補償(Deskew)算法。最新的研究成果引入了感知波形幾何形狀的機器學習(Machine Learning)算法,例如利用卷積神經網絡(CNN)來自動捕獲寬禁帶器件高頻測量波形中由于探頭延遲造成的非自然形狀不規則性(Shape Irregularity)。通過在大量具有已知精確延遲的合成波形上訓練,該深度學習模型能夠自動找出復雜的特征相關性,并反向推算出納秒乃至皮秒級別的探頭時滯(Probe Skew),從而在后處理中進行高精度的數字對齊校正 。此外,也有文獻提出使用硬件層面的無源無功電壓抵消(Reactive Voltage Cancellation)網絡,將探頭測量點前移至電流傳感器內部,利用輔助繞組主動消除感性壓降,從而大幅降低因相位差異導致的計算敏感度 。

從物理機理到系統宏觀:遲滯損耗的數學與行為建模

在通過先進實驗手段準確量化了 Coss? 遲滯損耗之后,如何建立計算高效且精度可靠的數學模型,并在主流的電路級仿真軟件(如 SPICE、PLECS)中真實復現這種動態損耗,對于現代電力電子變流器的前期架構設計與虛擬原型驗證至關重要。

經驗物理方程擬合:改進的 Steinmetz 方程應用

在傳統磁性材料(如鐵氧體、非晶合金)的磁芯磁化遲滯損耗建模領域,德國物理學家 Charles Steinmetz 在19世紀末提出的經典經驗方程(P=k?fα?Bβ)至今仍占據統治地位 。敏銳的研究人員發現,寬禁帶半導體輸出電容內部微觀缺陷導致的極化遲滯損耗,與鐵磁材料微觀磁疇壁摩擦導致的磁化遲滯損耗,在宏觀參數的依賴性表現上具有高度的數學相似性規律。因此,針對高頻軟開關下的 SiC 和 GaN 功率器件,學者們創造性地提出并驗證了一種用于量化容性遲滯損耗的改進型電學 Steinmetz 經驗模型:

EDISS?=k?fα?Vβ

在這一修正公式中,EDISS? 代表單次遲滯環路的耗散能量;V 代表器件關斷時承受的峰值漏源偏置電壓;f 代表充放電開關頻率(在此處有時也可被等效替換為特征 dv/dt 參數以表征瞬態速率);而 k,α,β 則是針對特定器件型號,通過導入海量 Sawyer-Tower 電路實驗測量數據,運用非線性曲線擬合算法提取出的關鍵經驗材料系數 。這種宏觀經驗模型的最大優勢在于計算速度極快,不會導致系統級仿真變慢,非常適合用于初步評估和預測特定應用工況下變流器整體開關損耗的演變趨勢。然而,由于它本質上是對多維數據的曲面擬合,其在預測嚴重超出原有實驗標定數據區間,或者應用于非標準正弦/方波等奇特電壓波形激勵時,預測精度會大幅下降 。

嚴謹的物理溯源:TCAD 混合模式(Mixed-Mode)仿真

為了深究遲滯現象的底層半導體物理成因,并指導下一代芯片的工藝流片,技術計算機輔助設計(Technology Computer-Aided Design, TCAD)混合模式仿真成為了不可或缺的微觀剖析工具。在常規的 TCAD 仿真中,往往只施加靜態偏置,而在混合模式中,龐大的半導體物理微分方程組(如涵蓋漂移-擴散機制的泊松方程、電子和空穴載流子連續性方程)被強耦合到外部真實的 SPICE 宏觀電路網絡中進行實時的瞬態迭代求解 。

這類高級 TCAD 物理模型在構建時必須包含極其詳盡的器件三維制造數據:包括外延層的精確摻雜濃度分布、硅超結器件內部深槽 P/N 柱的形貌與側壁電荷平衡狀態、甚至必須引入針對 SiC 材料特有的深能級鋁受主的不完全電離與聲子散射物理模型 。通過在有限元網格級別精確復現器件在經歷極高 dv/dt 瞬變時空間電荷邊界移動的物理延遲和載流子被陷阱動態捕獲的過程,仿真引擎能夠精準繪制出漏電流與漏電壓波形的微秒級不對稱性。這種基于底層物理規律的深度模型,從根本上在數學空間內解釋了為什么在電容充放電周期中,即便外部端口測得的總傳遞絕對電荷量嚴格守恒,但由于位移電流在微觀高阻抗耗盡區路徑中產生的焦耳發熱,仍然決定了不可逆耗散能量的宏觀規模 。

宏觀行為等效模型:不對稱雙電容與 Preisach 遲滯網絡

盡管 TCAD 物理模型的精度無可挑剔,但其計算開銷過于龐大,通常模擬一個簡單的開關周期就需要數小時的高性能計算資源,這對于需要評估幾萬個開關周期的系統級拓撲工程師而言是完全不可接受的。因此,在輕量級的 SPICE 或系統級仿真環境中,學界引入了一系列能夠逼真模擬電荷遲滯行為的宏觀等效電路(Behavioral SPICE Model)方案。

一種工程上非常直觀且易于收斂的方法是“雙電容非對稱等效模型”(Dual-Capacitor Behavioral Model) 。該模型摒棄了傳統 SPICE 中單一非線性壓控電容 Coss?(v) 的設定。取而代之的是,它在仿真底層通過邏輯判斷當前漏源電壓瞬時變化率(dv/dt)的代數極性,智能切換兩套截然不同的非線性電容查找表(Look-Up Table):

在 Vds? 處于陡峭上升階段(即主功率器件關斷,外部位移電流強制對輸出電容網絡注入電荷進行充電時):仿真器調用第一套函數 Coss_up?(Vds?)。

在 Vds? 處于下降階段(即器件門極即將被驅動開通前,諧振電感抽取電荷對電容進行軟放電時):仿真器無縫切換并調用第二套函數 Coss_down?(Vds?)。 這種從數學上將充放電物理路徑強行解耦的方法,能夠在極短的仿真時間內,直接在相平面上強制重現一個閉合的 Qoss??Vds? 遲滯能量積分環,極大地提升了 LLC 等軟開關電路的預測精度 。

此外,為了應對更為復雜的開關序列,借鑒于材料磁學分析領域的傳統 Preisach 滯后模型及其反演形式(Stop Model 和 Play Model),也被跨學科地引入到了電力電子非線性電容建模領域 。Preisach 族模型并不試圖解釋電荷運動的微觀物理機理,而是將宏觀的電容電壓滯后響應視為大量離散、具有不同觸發閾值的簡單滯后算子(Hysterons)在統計學上的加權疊加和。這種高級數學模型賦予了仿真器“物理記憶”能力:它不僅能記錄當前的實時瞬態電壓狀態,還能忠實地追蹤并記錄歷史周期內的每一次電壓反轉點(Reversal Points)。這使得該模型在處理變流器在輕載或異常工況下發生的“部分電壓充放電”(Partial ZVS)或不完全電壓換流等高度復雜的瞬態過程中,展現出了比靜態電容查表法無可比擬的 Ediss? 預測精度優勢 。

器件級數據驗證與系統級拓撲能效的深遠影響

將研究視角從孤立的單一晶體管微觀芯片提升至系統級功率變換拓撲層面,輸出電容非理想遲滯損耗在各類隔離型和非隔離型諧振轉換器中產生的影響極其深遠。它不僅實質性地侵蝕了 ZVS 技術原本承諾的“零損耗”理論收益,更是在根本上顛覆和重塑了高頻變流器設計中器件選型準則與閉環控制策略的底層邏輯 。

SiC 模塊的寄生能量特性對比

隨著寬禁帶半導體封裝工藝的不斷迭代,功率器件向著大電流、極低導通壓降的方向飛速演進。結面積的成倍增加,不可避免地帶來了寄生結電容及其所儲能量規模的急劇膨脹。以國內領先的寬禁帶半導體供應商 BASiC Semiconductor(基本半導體)所公布的最新一代大功率工業級與車規級 SiC MOSFET 模塊的規格參數為例,我們可以直觀地感受到這種寄生能量規模帶來的工程壓迫感:

| BASiC SiC 模塊型號 | 封裝形式 | 額定耐壓 | 額定連續電流 (ID?) | 典型導通電阻 (RDS(on)?) | 小信號輸出電容 (Coss? @800V) | 標稱電容儲能 (Eoss? @800V) |

|---|---|---|---|---|---|---|

| BMF120R12RB3 | 34mm半橋 | 1200 V | 120 A | 10.6 mΩ | 314 pF | 131 μJ |

| BMF160R12RA3 | 34mm半橋 | 1200 V | 160 A | 7.5 mΩ | 420 pF | 171 μJ |

| BMF240R12E2G3 | Pcore?2 E2B | 1200 V | 240 A | 5.5 mΩ | ~0.9 nF | 340.8 μJ |

| BMF540R12MZA3 | Pcore?2 ED3 | 1200 V | 540 A | 2.2 mΩ | ~1.26 nF | 509 μJ |

| (數據來源引用:) |

觀察上表中的旗艦級模塊 BMF540R12MZA3,其卓越的并聯芯片設計使得導通電阻被極限壓榨至 2.2mΩ,這在處理百安培級負載電流時無疑能大幅降低傳導損耗。然而,與之相伴的代價是其靜態小信號儲能 Eoss? 也攀升至 509 μJ 。若將該模塊應用于設計頻率為 100 kHz 的大功率高頻軟開關逆變器中,即使忽略諧振腔寄生參數,主開關管在每秒內循環吞吐的無功功率就高達 509μJ×100,000Hz=50.9W。考慮到前文分析的大信號遲滯非理想特性,即使只有極小百分比(如5%~10%)的非可逆遲滯電荷未能通過諧振網絡被有效回收,單管在每個周期內憑空產生的純熱耗散也將達到幾瓦至十幾瓦的驚人規模。這部分損耗疊加在原有的導通損耗之上,極大地考驗了底層散熱基板(如采用高性能 Si3?N4? AMB 氮化硅陶瓷基板與銅底板結合的先進熱設計)的熱導出能力 。

遲滯損耗對 LLC 與有源鉗位(ACF)拓撲的絕對效率侵蝕

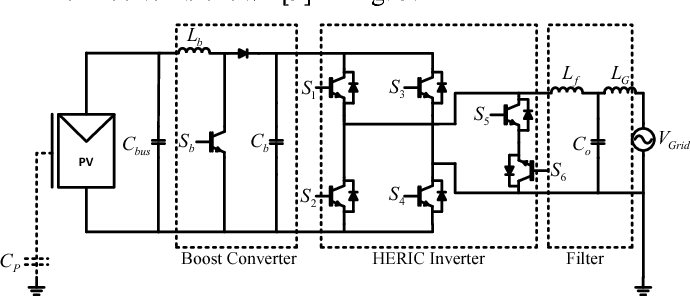

在經典的半橋或全橋 LLC 諧振直流-直流轉換器中,由于高頻運行下高頻變壓器與勵磁電感等磁性元件的物理尺寸得以大幅度縮減,產品的功率密度不斷突破極限。然而,由于 Coss? 遲滯效應的存在不僅發生在其原邊承擔高壓應力的寬禁帶主開關管上,高頻變壓器副邊負責整流的同步整流器(Secondary Side Rectifiers, SRs)中同樣存在著海量且高頻的位移電流充放電損耗,這部分損耗嚴重制約了 LLC 轉換器將開關頻率推向數兆赫茲以上的工程可行性 。

在消費電子快充領域廣泛應用的有源鉗位反激(Active Clamp Flyback, ACF)轉換器中,這一現象尤為典型。ACF 拓撲通過輔助開關與鉗位電容的巧妙配合,實現了漏感能量的完全無損回收并確保了主輔開關的全頻段 ZVS 軟開關。然而,在系統處于低輸入電壓且負載較輕的高頻工作條件下,通道的歐姆傳導損耗占比大幅下降,而開關容性損耗(尤其是由 Coss? 遲滯所引起的耗散)將直接反客為主,占據總功率損耗的絕對主導地位 。

深入的定量研究與實驗剖析顯示,在一款額定功率為 65W 的高頻 ACF 電源適配器原型機中,當主次開關均采用規格為 120 mΩ、耐壓 600V 的傳統硅超結(Si-SJ)MOSFET 進行高頻斬波時,僅僅由 Coss? 充放電不可逆遲滯引起的絕對熱功率損耗,就占到了整個 MOSFET 器件總發熱損耗(包含高低邊)的驚人的 44%,甚至超過了占 40% 比例的溝道傳導損耗,而常規認為的柵極驅動損耗與重疊開關損耗總和不到 20% 。隨著半導體工藝的進步,為了獲取更低的導通電阻,芯片有源區面積不可避免地成比例放大,其等效結電容及其包含的遲滯絕對能量池也隨之水漲船高。這在學術界和工業界揭示了一個極為反直覺的殘酷設計悖論:在追求極高頻率的 ZVS 軟開關電力電子電路中,盲目選用具有極低 RDS(on)? 的超大尺寸功率芯片,非但不能像硬開關時代那樣帶來效率的飛躍,反而會因為龐大且不可完全恢復的容性遲滯損耗抵消掉導通優勢,最終導致系統整體轉換效率發生不可逆的退化 。

系統級硬件與控制軟件的綜合緩解策略

既然 Coss? 大信號遲滯損耗的病根深深植根于硅晶圓內部的微觀物理三維結構與深能級晶格陷阱,那么單純依賴系統級硬件拓撲設計顯然無法將其在物理層面上完全根除。但是,通過引入智能化、自適應的拓撲架構演進與先進的高階數字閉環控制策略,工程界能夠最大程度地壓縮遲滯環的面積,從而有效緩解其對系統能效的吞噬效應 。

自適應精準死區時間控制(Adaptive Dead-Time Control)

在包含 LLC 和 ACF 的各類諧振變流器設計范式中,上管與下管之間的死區時間(Dead-time)必須被極其精準地設定與控制,以允許勵磁電感或諧振電感中積蓄的感性反向電流有足夠的時間,完全且平滑地抽取掉主開關管寄生電容上的全部電荷,這是實現完美 ZVS 軟開關不可或缺的物理前提 。然而,如果控制器內部設定的死區時間是剛性固定的,那么當外部負載發生劇烈動態變化,或者輸入總線電壓出現顯著波動時,諧振槽內的能量平衡被打破,系統將極易偏離其精心設計的最佳 ZVS 工作點。

一旦死區時間過短,電容將放電不完全即被強制硬開通,產生極其劇烈的容性開通沖擊電流;而如果死區時間過長,原本已經放電至零的節點電壓會因為諧振電流的極性反轉,發生諧振腔向寄生電容進行反向盲目充電的惡性現象。這兩種偏離都會在 Qoss??Vds? 相平面上人為地擴大非線性波動的軌跡,顯著加劇微觀遲滯發熱。通過實施基于微控制器(MCU)或現場可編程門陣列(FPGA)的自適應死區時間控制算法,電源系統能夠借助高速比較器實時監測當前的輸出電流與電壓節點斜率,并以極小的步進分辨率動態微調脈寬調制(PWM)的死區延遲窗口,確保外部強制推入的位移電流與內部電容徹底放電的最后期限實現完美的時間軸同步。這種智能調節避免了由于過早或過晚的硬性門極驅動導致 Vds? 崩塌軌跡發生劇烈振蕩,從而極大地收緊并壓縮了單次開關周期內實際發生的遲滯環幾何面積,從根源上降低了損耗 。

混合遲滯控制(HHC)與雙模式拓撲運行切換

對于要求具有超寬電壓轉換比(Wide Voltage Conversion Ratio)和快速動態響應的 LLC 轉換器,為了在輕載和極重負載的極端邊界下均保證輸出穩壓精度,傳統的直接頻率控制(Direct Frequency Control, DFC)架構迫使變流器的開關頻率在幾十千赫茲到數兆赫茲之間進行極為寬泛的大范圍掃頻變化(Frequency Broadening)。然而,當被動拉升的極高工作頻率遇到本文所述的每周期固定損耗的 Coss? 遲滯效應時,系統級熱發散將呈線性爆炸式增長,使器件瞬間進入不理想的惡劣發熱狀態。

現代先進電源控制芯片(例如德州儀器的 UCC256302 等)革命性地采用了混合遲滯控制(Hybrid Hysteretic Control, HHC)閉環策略。HHC 不再單一依賴死板的壓控振蕩器,而是將頻率控制環路與更深層的諧振槽電荷控制環路進行巧妙結合,這不僅通過前饋機制極大地改善了階躍負載下的瞬態響應時間,還將原本極其復雜的非線性系統開環傳遞函數有效降階為一個易于控制的一階系統 。此外,結合創新的可重構諧振電容陣列控制(Adaptive Switched Capacitor Control),前沿變流器能夠“在飛行中”(on-the-fly)通過固態開關的無縫切換,動態重構諧振槽的核心物理參數,強制系統始終維持在最優化的高效低頻段區間運行,從根本上避免了因為調壓被迫拉高頻率而導致的每秒遲滯損耗脈沖線性瘋狂疊加 。

在稍低功率等級的適配器架構中,研究人員提出了一種智能雙模式控制方案(Dual-Mode Control)。通過引入精密的狀態狀態機,ACF 轉換器被允許根據當前的實時負載需求智能改變底層拓撲行為:在重載或滿載區間,轉換器激活標準的有源鉗位模式,全力保證所有主功率管在 ZVS 軟開關狀態下穩定運行;而在檢測到進入輕載或待機條件時,由于此時導通損耗已不再是主要矛盾,且高頻導致的遲滯損耗占比極高,控制器會智能切換至頻限機制主導的準諧振(Quasi-Resonant, QR)谷底開關模式。這一策略通過容忍極小程度的谷底硬開關,換取了大幅度拉低系統整體開關頻率的紅利,徹底規避了高頻下寄生結電容遲滯效應的懲罰性發熱,最終使得低載區間效率實現了兩位數百分比的顯著提升 。

軟開關優值系數(ZVS FOM)的革新與重定義

長久以來,整個電力電子行業的器件選型極度依賴于一種單一且簡陋的靜態綜合品質因數(Figure of Merit, FOM),即 FOMHard?Switch?=RDS(on)?×Qg?(導通電阻乘以總柵極電荷)。這種傳統的評估體系潛意識里假設了一旦進入 ZVS 狀態,所有的容性參數損耗都可以被理想歸零。鑒于上文論述的殘酷現實,全球頂尖學術界提出了一種專門針對高頻軟開關轉換器、更為嚴謹且具有革命指導意義的器件優值系數新定義,用以矯正電路設計者在新一代材料選型時的盲點:

FOMZVS?=RDS(on)?×(Ediss?+Egate?)

在這個全新的等式中,Ediss? 特指在 Sawyer-Tower 精密儀器下或量熱法中測量出的,單次充放電循環不可逆的 Coss? 大信號遲滯耗散能量積分面積;而 Egate? 則代表不可避免的柵極環路驅動耗散能量。這種深刻揭示底層物理權衡的新型評價體系,強有力地促使系統設計者在構建極高頻、高功率密度應用方案時,徹底拋棄一味盲目追求最低導通電阻的固有思維。相反,設計者必須在靜態溝道導通傳導發熱與由不完全電離或陷阱動態充放引發的位移電流高速高頻熱耗散之間,進行極其審慎的數學聯合極值求解,最終在兩者相互掣肘的制約關系中尋找系統全局最高效的最佳帕累托前沿(Pareto Front)配置 。

結論

高頻率零電壓軟開關(ZVS)技術雖然在宏觀電力電子電路拓撲層面上,極大地消除了因大電流與高電壓瞬態重疊所帶來的傳統毀滅性硬開關損耗,卻并未如同魔法般使能量徹底消失,而是將損耗的產生機制從宏觀的阻性重疊區,隱蔽地轉移到了功率器件硅晶圓內部極度微觀的物理與能帶結構層面。位移電流對半導體輸出寄生電容 Coss? 的高速充放電,絕對不是一個完美無損的理想純靜電過程。在硅基超結(Si-SJ)器件內部縱深 P/N 柱區內極度受阻的載流子滯留電荷效應、碳化硅(SiC)寬禁帶器件邊緣脆弱終端區內極其微觀的鋁受主深能級不完全電離響應延遲,以及氮化鎵(GaN)異質結晶體管內晶格缺陷對電子進行的非對稱動態捕獲與釋放釋放效應的共同作用與撕扯下,器件內部瞬態電荷量與外部端電壓的高頻變化呈現出了劇烈且不可逆的遲滯(Hysteresis)行為,從而在系統百萬次的每一個振蕩開關周期中,貪婪地提取并永遠耗散掉了部分原本應回饋給諧振電路的寶貴電網能量。

準確地界定、觀測并從工程上量化這一隱蔽的微小損耗,跨越了從最底層凝聚態半導體物理到最高端微波級精密電磁測量儀器的多重交叉科學挑戰。由于納秒級別瞬態信號微小相位偏移(Phase Skew)以及線路極其復雜的高頻傳輸線效應限制,傳統的基于數字示波器的時域電壓電流直接乘積積分法在量化此類損耗時已完全失效并遭淘汰。工業界與學術前沿目前正普遍采用諸如改進型 Sawyer-Tower 無源電容分壓測量法、具有極高環境抗擾度的高精度穩態量熱隔離腔法,以及專門設計的非線性諧振環衰減測量法等手段,來直接從物理層面捕獲微觀極化能量的閉合面積或熱學溫升特征。與此同時,從宏觀經驗擬合規律(如修正的指數級 Steinmetz 電學方程)到窮盡原子細節的 TCAD 混合模式瞬態物理仿真,再到創新解耦充放電動態物理路徑的雙極性不對稱電容行為模型,當今豐富的復合數學物理分析工具已經能夠非常精準地在虛擬環境中擬合并重現這一棘手的遲滯現象,為其在各類商用電力電子 SPICE 仿真軟件系統中的大規模普及化應用徹底鋪平了理論道路。

在更為廣闊的實際產業應用層面,隨著如 BASiC Semiconductor(基本半導體)等領先原廠紛紛向市場大量鋪貨推出諸如 BMF540R12MZA3、BMF240R12E2G3 等具有極低毫歐級導通電阻與超高電流處理能力的新一代大功率SiC碳化硅模塊,下一代高功率密度固變SST與儲能逆變器系統的寄生電容池本身已經膨脹到了具有數百微焦耳(μJ)級別、絕對不容忽視的儲能發熱規模。在這個兆赫茲級的全新時代,工程師們必須清醒地認識到:優化變換器的最終能量轉換效率,已不再僅僅是尋找新型硬件開關拓撲結構的單向問題,它更是一個必須將器件微觀物理遲滯特性與宏觀自適應死區時間控制、具有極寬自適應調控范圍的混合遲滯控制(HHC)以及雙模式開關策略等軟件控制算法緊密咬合的系統級綜合跨界工程。未來的高頻軟開關固態器件的迭代開發與大規模工程應用,只有在極其深刻地理解并應用了新型零電壓軟開關優值系數(ZVS FOM)的科學指導下,在靜態極低導通內阻帶來的傳導收益與動態大信號高頻遲滯損耗帶來的嚴酷發熱懲罰之間實現最精準無誤的多維折中與權衡,方能真正在物理極限的邊緣,將電力電子能量轉換技術推向更高效、更清涼的未來。

審核編輯 黃宇

-

轉換器

+關注

關注

27文章

9418瀏覽量

156320 -

輸出電容

+關注

關注

0文章

121瀏覽量

8892

發布評論請先 登錄

傾佳楊茜-方案實踐:對SiC模塊和單管進行LLC最優參數條件調教

位移電流物理本質與碳化硅(SiC)功率器件應用解析

傾佳電子c技術深度分析:拓撲、原理與應用

傾佳電子基于SiC模塊的120kW級聯SST固態變壓器功率模塊設計與拓撲分析

傾佳電子寬禁帶時代下的效率優化:SiC MOSFET橋式拓撲中同步整流技術的必然性與精確定量分析

傾佳電子SiC廚房革命:B3M042140Z MOSFET取代RC-IGBT在電磁爐應用中的技術與商業分析

傾佳電子Home Battery Storage家儲系統拓撲方案設計與分析報告

傾佳楊茜-探本溯源:軟開關拓撲中位移電流與輸出電容遲滯損耗的量化難題與物理機制分析

傾佳楊茜-探本溯源:軟開關拓撲中位移電流與輸出電容遲滯損耗的量化難題與物理機制分析

評論