傾佳楊茜-方案實踐:對SiC模塊和單管進行LLC最優參數條件調教

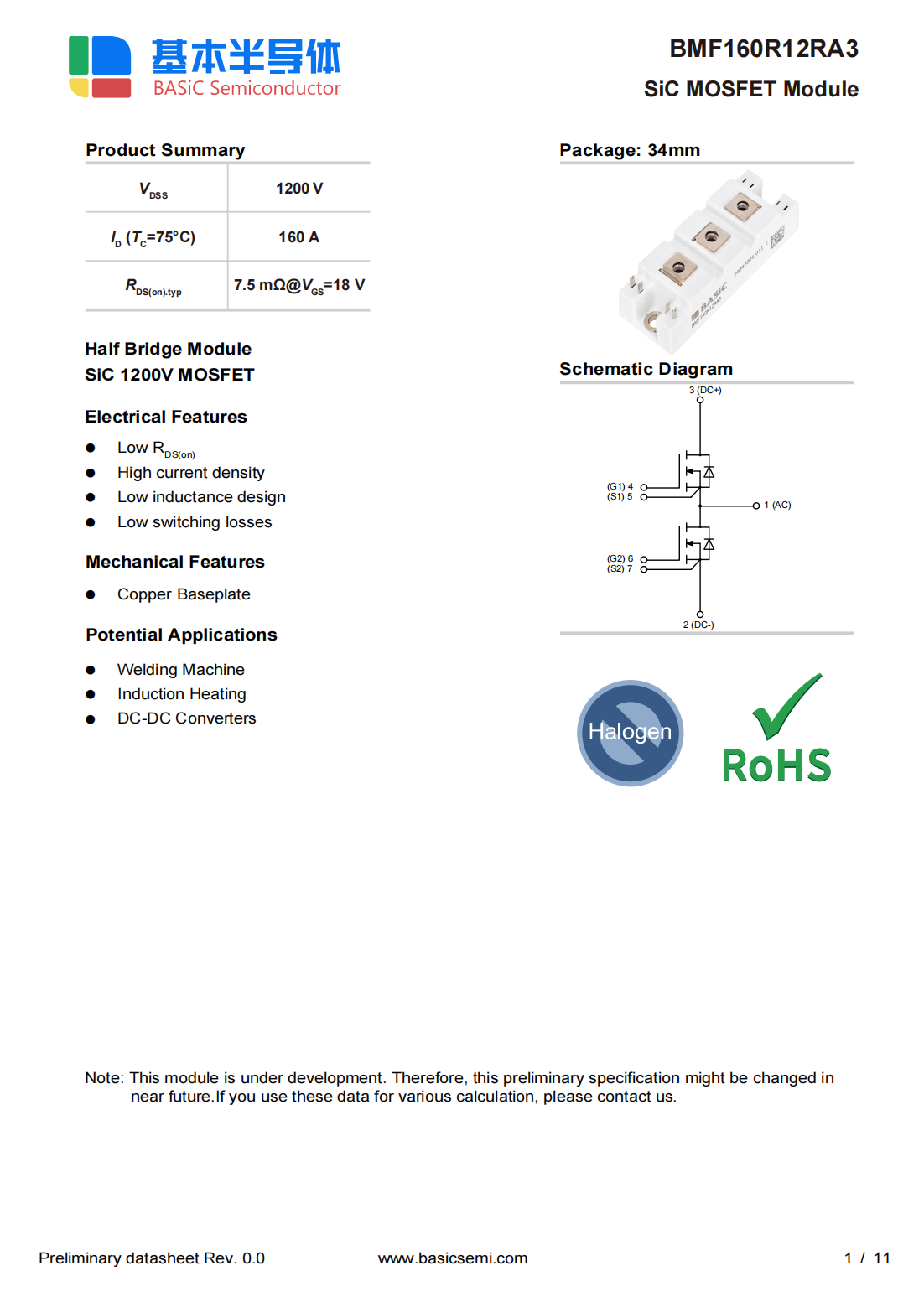

基本半導體(BASiC Semiconductor)大量出貨多款碳化硅(SiC)MOSFET 模塊(如1200V/540A的 BMF540R12KHA3)及單管(如1200V/223A的 B3M011C120Z)的給電力電子客戶帶來了更多選擇,將這些高性能器件應用于 LLC 諧振變換器 時,其參數調教邏輯與傳統的硅基(Si)SJ-MOSFET 或 IGBT 有著本質的區別。

LLC 拓撲的原邊工作特性為:開通是零電壓開通(ZVS),關斷是帶有勵磁電流的硬關斷。結合基本半導體(BASiC Semiconductor)多款碳化硅(SiC)MOSFET 模塊和單管的核心數據,以下是進行 LLC 最優參數調教的工程實踐指南:

傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

一、 諧振腔參數(Lm?)與死區時間(tdead?)的極限協同

這是 SiC 在 LLC 應用中最核心、也最容易影響整機效率的調教環節。

1. 痛點:極致壓縮死區時間 tdead?(對抗極高 VSD?)

- 規格書尋跡:查閱體二極管(Body Diode)特性,SiC MOSFET 的正向壓降 VSD? 極高。在 VGS?=?5V 時,單管(如B3M011C120Z)的 VSD? 典型值為 4.0V,而大功率模塊(如BMF540R12KHA3)甚至高達 5.11V。

-

工程調教:在 LLC 的死區時間內,維持 ZVS 換流的電流會流過體二極管。如果死區時間設置過長(如傳統硅管的 300ns

500ns),高達 45V 的壓降會產生巨大的導通發熱損耗(Pdead?=2×VSD??Im??tdead??fsw?)。 - 實踐動作:必須將死區時間壓縮到極限。由于 SiC 極小的電容充放電極快,死區時間通常可壓縮至 50ns ~ 150ns。在滿載調試時,用示波器雙探頭觀察半橋中點 VSW? 和下管驅動 VGS?:最佳狀態是 VSW? 剛剛諧振跌落至 0V 的瞬間,VGS? 剛好越過閾值開啟。強烈建議在數字控制中引入自適應死區時間(Adaptive Dead-time)算法。

2. 優勢:最大化勵磁電感 Lm?(降低原邊環流)

- 規格書尋跡:SiC 的輸出電容儲能 Eoss? 極小,例如 B3M011C120Z 在 800V 下的 Eoss? 僅為 106 μJ。

- 工程調教:LLC 實現原邊 ZVS 的物理門檻是勵磁能量必須大于節點寄生電容的能量(21?Lm?Im(peak)2?≥2Eoss?)。因為 Eoss? 呈數量級下降,我們需要用來抽電荷的勵磁電流 Im(peak)? 可以變得很小。

- 實踐動作:在變壓器設計時,在滿足 ZVS 的前提下盡可能增大勵磁電感 Lm? (電感比 m=Lm?/Lr? 在 SiC 設計中常推高至 7 ~ 12)。增大的 Lm? 會顯著減小原邊的無功環流,從而將 SiC MOSFET 極低 RDS(on)?(如單管的 11mΩ)的導通損耗優勢發揮到極致,同時大幅降低變壓器原邊銅損。

二、 門極驅動(Gate Drive)的非對稱精準配置

LLC 原邊開關特性決定了驅動電阻必須進行非對稱設計(從規格書的測試條件即可看出,如 RG(on)?=5.1Ω, RG(off)?=1.8Ω)。

1. 開通電阻 RG(on)?:適當偏大(抑制 EMI 與振鈴)

- 邏輯:LLC 原邊為 ZVS 開通,開通損耗 Eon? 本身趨近于零,開關速度再快也不會降低開通損耗。

- 實踐:適當放大 RG(on)?(例如取 5Ω ~ 15Ω),可以減緩開通瞬態的 di/dt 和 dv/dt,有效降低橋臂中點的高頻振鈴,改善 EMI,并降低橋臂對側管因為米勒效應引發的誤導通風險。

2. 關斷電阻 RG(off)?:盡可能極小(強壓關斷損耗)

-

邏輯:LLC 原邊關斷時切斷的是勵磁電流(帶載時還疊加部分負載電流),屬于硬關斷。查閱規格書

Switching Energy vs. External Gate Resistance曲線,關斷損耗 Eoff? 隨 RG? 的增大而陡峭上升。 - 實踐:RG(off)? 應設置得盡可能小(例如 1Ω ~ 2Ω),以最快速度抽取門極電荷,斬斷關斷時的拖尾電流。

3. 強制使用負壓關斷(-4V / -5V)

- 邏輯:規格書指出在 175°C 高溫下,閾值電壓 VGS(th)? 會產生負溫度系數漂移,降至 1.9V 左右。在極高的 dv/dt 瞬態下,位移電流通過 Crss? 極易抬高柵壓。

- 實踐:嚴禁使用 0V 關斷,必須嚴格按照規格書推薦,配置穩定的 +18V / -5V(或 -4V)驅動電壓,保障可靠性。

三、 封裝特性的極致利用與 Layout

1. Kelvin Source(開爾文源極)的絕對分離

- 規格書尋跡:您提供的單管均采用 TO-247-4(Pin 3為 Kelvin Source),模塊也具備輔助驅動源極引腳。

- 實踐動作:在高速硬關斷 Eoff? 期間,di/dt 極大。主功率回路在源極寄生電感 Ls? 上產生的壓降(Ls??di/dt)會嚴重抵消驅動負壓。驅動芯片的 GND 必須獨立且直接地拉線至 Kelvin Source 引腳,若與大電流回路共用,會導致關斷變慢,損耗失控。

2. 高頻吸收(Decoupling/Snubber)

- 雖然模塊內部寄生電感極低(Lσ?≤30nH),但在大功率 LLC 滿載關斷時,外部母排的寄生電感仍會激發出極高的電壓尖峰。高頻 CBB 吸收電容必須直接鎖附/緊貼在模塊的 DC+ 和 DC- 端子上。

四、 容性區(Capacitive Mode)免疫力的利用

- 傳統硅管痛點:LLC 在啟動、輸出短路或負載階躍偏離諧振點時,易短暫掉入容性區(失去 ZVS,硬開通)。傳統 Si MOSFET 的 Qrr? 極大(毫庫侖級別),體二極管在硬恢復時極易造成橋臂直通炸機。

- SiC 優勢:查閱規格書,SiC 的 Qrr? 極小(單管如 B3M010C075Z 僅為 460 nC)。

- 調教紅利:這意味著 SiC MOSFET 對 LLC 容性區硬開通具有極強的免疫力。在 DSP 控制算法調教時,防容性區保護(Anti-Capacitive Mode Protection)的頻率鉗制和判定閾值可以大幅放寬。這讓電源在面對惡劣電網波動或極端動態負載時,不會輕易觸發停機保護,極大提升了系統的動態響應能力和魯棒性。

實機調教 Step-by-Step

- 基礎設定:推高 Lm?;驅動設為 +18V/?5V;RG(on)?=10Ω,RG(off)?=1.5Ω。

- 死區試探:上電時死區時間預設為 250ns。

- 死區壓縮:在半載和滿載下,用示波器盯住 VDS? 下降沿與 VGS? 上升沿,逐步將死區時間縮短至 80ns~120ns 左右,吃干榨凈 VSD? 損耗。

- 溫升復核:滿載拷機,根據規格書中 RDS(on)? 的高溫漂移曲線(175°C 下阻值約是常溫的 1.6 倍),反算殼溫是否符合預期。

-

SiC

+關注

關注

32文章

3720瀏覽量

69382 -

LLC

+關注

關注

38文章

628瀏覽量

80664

發布評論請先 登錄

傾佳電子代理之SiC功率模塊產品矩陣及其對電力電子產業變革的系統級貢獻

傾佳電子SiC功率模塊:超大功率全橋LLC應用技術優勢深度分析報告

傾佳電子推動SiC模塊全面替代IGBT模塊的技術動因

傾佳電子提供SiC碳化硅MOSFET正負壓驅動供電與米勒鉗位解決方案

傾佳楊茜-方案實踐:對SiC模塊和單管進行LLC最優參數條件調教

傾佳楊茜-方案實踐:對SiC模塊和單管進行LLC最優參數條件調教

評論