AI算力中心下一代液冷電源架構研究報告:架構演進、頂部散熱碳化硅MOSFET技術價值與商業(yè)價值

全球能源互聯(lián)網(wǎng)核心節(jié)點賦能者-BASiC Semiconductor基本半導體之一級代理商傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業(yè)電源、電力電子設備和新能源汽車產(chǎn)業(yè)鏈。傾佳電子聚焦于新能源、交通電動化和數(shù)字化轉型三大方向,代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。?

傾佳電子楊茜致力于推動國產(chǎn)SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業(yè)自主可控和產(chǎn)業(yè)升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

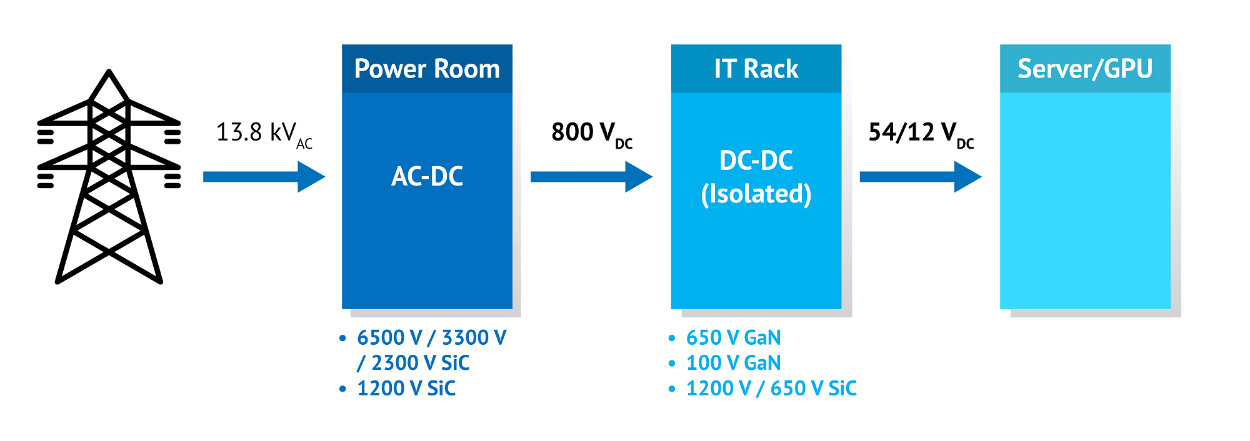

隨著以ChatGPT和Sora為代表的生成式人工智能(Generative AI)和大語言模型(LLM)的爆發(fā)式增長,全球數(shù)據(jù)中心正經(jīng)歷一場前所未有的算力基礎設施重構。計算密度的指數(shù)級躍升導致單機柜功率密度從傳統(tǒng)的5-10kW激增至100kW甚至更高,迫使傳統(tǒng)的風冷散熱和12V分布式電源架構面臨物理極限和經(jīng)濟效益的崩塌。在這一背景下,基于開放計算項目(OCP)Open Rack Version 3 (ORv3) 標準的液冷架構,配合48V/50V母線傳輸,已成為下一代AI算力中心的必然選擇。

傾佳電子在對AI算力中心的液冷電源架構進行詳盡的解構分析,并重點探討頂部散熱(Top-Side Cooled, TSC)碳化硅(SiC)MOSFET器件——特別是基本半導體(BASiC Semiconductor)B3M系列——在這一變革中的關鍵技術地位與商業(yè)價值。通過深入對比傳統(tǒng)封裝與TSC封裝的熱力學特性、寄生參數(shù)及系統(tǒng)集成方案,結合總擁有成本(TCO)模型和電源使用效率(PUE)分析,傾佳電子楊茜揭示了TSC SiC MOSFET不僅是提升電源轉換效率的核心器件,更是實現(xiàn)高密度、高可靠性AI基礎設施的戰(zhàn)略性技術支點。

第一章 AI算力時代的能源與熱力學危機

人工智能算力需求的增長速度已遠超摩爾定律的預測。根據(jù)相關數(shù)據(jù)預測,2022年至2027年中國智能算力規(guī)模的年復合增長率(CAGR)高達34% 。這種算力需求的爆發(fā)直接映射到物理基礎設施上,表現(xiàn)為極端的功率密度和熱流密度挑戰(zhàn)。

1.1 功率密度的指數(shù)級躍升

在傳統(tǒng)企業(yè)級數(shù)據(jù)中心時代,單機柜功率通常維持在3kW至8kW之間,主要承載Web服務、數(shù)據(jù)庫和通用計算負載。然而,AI訓練集群對低延遲通信的嚴苛要求迫使GPU服務器必須在物理空間上高度緊湊部署。目前,NVIDIA H100/H200及Blackwell架構的服務器集群已將單機柜功率推高至40kW以上,部分液冷機柜甚至突破130kW 。

這種密度的提升并非線性增長,而是呈階躍式爆發(fā)。根據(jù)Goldman Sachs的研究,到2027年,AI服務器機架的設計功率將是傳統(tǒng)互聯(lián)網(wǎng)機架的50倍 。這意味著在一個標準占地面積內,熱產(chǎn)生的速率已經(jīng)超過了空氣介質自然對流或強制風冷的熱交換能力極限。

1.2 風冷技術的物理墻

傳統(tǒng)風冷系統(tǒng)依賴于精密空調(CRAC/CRAH)和服務器內部的高速風扇。空氣的比熱容僅為 1.005kJ/(kg?K),而水的比熱容高達 4.18kJ/(kg?K),且水的導熱系數(shù)約為空氣的24倍。物理性質的差異導致風冷在應對高熱流密度時效率極低。

風扇功耗懲罰(Parasitic Power): 為了帶走高密度熱量,風扇必須以極高轉速運行。根據(jù)立方定律,風扇功耗與轉速的立方成正比。在氣冷的高密度AI服務器中,風扇功耗可能占據(jù)IT總功耗的15%-20%,這部分能量不僅沒有用于計算,反而成為了額外的熱源,進一步惡化了PUE 。

聲學與空間限制: 極端的風速帶來了難以忍受的噪音污染(甚至導致硬盤振動故障)和巨大的風道空間占用,限制了數(shù)據(jù)中心的有效部署密度 。

熱阻瓶頸: 當芯片熱流密度(Heat Flux)超過 50?100W/cm2 時,芯片封裝表面到散熱器翅片的熱阻加上空氣對流熱阻,已無法維持結溫在安全范圍內,導致處理器頻繁降頻(Thermal Throttling),直接浪費了昂貴的算力資源 。

1.3 液冷轉型的必然性

基于上述物理限制,液冷不再是“可選的高級特性”,而是AI基礎設施的“生存必需品”。行業(yè)共識表明,當機柜功率超過20-30kW時,液冷在經(jīng)濟性和技術可行性上開始超越風冷;而當功率超過50kW甚至100kW時,液冷成為唯一可行的熱管理方案 。

第二章 液冷電源架構的標準化與技術實現(xiàn)

為了應對高功率密度挑戰(zhàn),全球超大規(guī)模數(shù)據(jù)中心運營商(Hyperscalers)通過OCP組織制定了全新的Open Rack Version 3 (ORv3) 標準,重新定義了機架內的供電與散熱架構。

2.1 從12V到48V/50V母線架構的演進

傳統(tǒng)的12V供電架構在應對單機柜100kW負載時面臨巨大的電流挑戰(zhàn)。根據(jù)歐姆定律 P=VI,在12V電壓下輸送100kW功率需要高達8333A的電流。這將導致巨大的銅排母線尺寸(成本和重量增加)以及難以接受的 I2R 傳輸損耗。

ORv3架構引入了48V(標稱值,實際浮充電壓約50-54V)直流母線系統(tǒng) 。

電流降低: 電壓提升4倍,電流降低至原本的1/4(約2083A)。

損耗驟降: 傳輸損耗與電流的平方成正比。理論上,在相同導體截面積下,傳輸損耗降低至原來的1/16。這極大地提升了端到端的能源效率,是實現(xiàn)綠色數(shù)據(jù)中心的關鍵一步 。

集中式供電(Power Shelf): ORv3摒棄了服務器內置獨立PSU的傳統(tǒng),改用集中式的“電源架”(Power Shelf)。一個標準的ORv3電源架通常包含6個熱插拔整流模塊(Rectifier),單模塊功率從3kW演進至5.5kW乃至12kW,總功率可達18kW-33kW甚至更高,支持N+1冗余 。

2.2 液冷盲插與流體分配網(wǎng)絡

在ORv3液冷機柜中,不僅計算節(jié)點(Compute Tray)需要液冷,高功率密度的電源架同樣需要液冷散熱。

盲插接頭(Blind-Mate UQD): 為了保持類似風冷服務器的運維便捷性,ORv3定義了液冷盲插接口規(guī)范。當電源架或服務器推入機柜時,后部的液冷快接頭(Universal Quick Disconnect, UQD)與機柜側的歧管(Manifold)自動接合,實現(xiàn)冷卻液的導通。這種設計要求極高的機械精度和防泄漏可靠性 。

液冷母線(Liquid-Cooled Busbar): 隨著電流密度的增加,連導電銅排本身的發(fā)熱也不容忽視。TE Connectivity等廠商推出了液冷垂直母線技術,將冷卻液流道集成在母線內部。這種設計能使母線在承載15,000A以上電流(支持750kW機柜)時,溫升控制在30°C以內,實現(xiàn)了5倍于傳統(tǒng)風冷母線的載流能力 。

第三章 高效能電源供應單元(PSU)的拓撲與設計挑戰(zhàn)

AI算力中心的核心能源轉換環(huán)節(jié)發(fā)生在PSU內部。為了滿足ORv3標準對效率(>97.5%峰值效率,即80 PLUS Titanium等級)和功率密度(>100 W/in3)的嚴苛要求,PSU的電路拓撲正在經(jīng)歷深刻變革 。

3.1 80 PLUS Titanium效率挑戰(zhàn)

鈦金級(Titanium)標準要求在50%負載下效率不低于96%,在10%輕載下不低于90% 。對于3kW或更高功率的PSU,這意味著滿載時的總損耗必須控制在極低水平。例如,3kW PSU在97.5%效率下的損耗為75W,而如果是94%效率(鉑金級),損耗則高達180W。這100W的額外熱量在高密度堆疊下將引發(fā)嚴重的熱管理問題。

3.2 圖騰柱PFC(Totem-Pole PFC)的崛起

傳統(tǒng)的Boost PFC電路使用二極管整流橋將交流電(AC)轉換為直流電(DC),二極管的導通壓降導致了顯著的效率損失。為了突破這一瓶頸,無橋圖騰柱PFC(Bridgeless Totem-Pole PFC) 拓撲成為了行業(yè)首選方案。

拓撲原理: 該拓撲移除了輸入端的整流橋,利用有源開關管(MOSFET)進行整流和功率因數(shù)校正。

硬開關挑戰(zhàn): 在圖騰柱PFC的連續(xù)導通模式(CCM)下,開關管必須經(jīng)歷“硬開關”過程,即在體二極管導通續(xù)流時被強行關斷并反向恢復。

硅基器件的局限: 傳統(tǒng)的硅(Si)MOSFET和IGBT由于體二極管的反向恢復電荷(Qrr?)很大,在硬開關過程中會產(chǎn)生巨大的反向恢復損耗,甚至導致器件雪崩擊穿。因此,硅MOSFET無法在CCM模式下用于圖騰柱PFC的高頻橋臂。

3.3 碳化硅(SiC)的關鍵賦能作用

SiC MOSFET的出現(xiàn)完美解決了上述難題,成為高效率AI電源的基石。

極低的反向恢復電荷(Qrr?): SiC MOSFET的體二極管具有極小的Qrr?(通常僅為同規(guī)格Si器件的1/10甚至更低),這使得反向恢復損耗幾乎可以忽略不計,從而允許圖騰柱PFC在CCM模式下高效運行 。

高頻開關能力: SiC器件支持更高的開關頻率(65kHz-100kHz以上),這使得能夠大幅減小PFC電感和EMI濾波器的體積,從而顯著提升功率密度(W/in3),滿足AI機柜寸土寸金的空間要求 。

第四章 頂部散熱(TSC)封裝技術的工程學解析

盡管SiC芯片本身效率極高,但隨著單顆器件功率密度的增加,如何將芯片產(chǎn)生的熱量高效地從封裝內部傳導至冷卻介質(液體)成為了新的瓶頸。傳統(tǒng)的底部散熱(Bottom-Side Cooling, BSC)封裝技術(如TO-247, D2PAK)在液冷架構中顯得力不從心。

4.1 傳統(tǒng)底部散熱(BSC)的熱阻瓶頸

在D2PAK或TOLL等標準貼片封裝中,熱傳導路徑如下:

芯片結(Junction) → 引線框架(Leadframe) → 底部焊盤(Solder) → PCB銅箔 → PCB絕緣層(FR4) → PCB背部 → 散熱器。

PCB的熱阻: FR4材料是熱的不良導體,導熱系數(shù)僅為 0.3W/(m?K)。即使通過密集的過孔(Thermal Vias)增強導熱,PCB層仍然是整個散熱路徑中最大的熱阻來源(Rth(PCB)?)。

熱耦合問題: 功率器件的熱量會傳遞給PCB,導致PCB板溫升高,進而加熱周圍對溫度敏感的元器件(如柵極驅動IC、電容等),降低系統(tǒng)可靠性 。

4.2 頂部散熱(TSC)的架構革命

頂部散熱封裝(如TOLT, QDPAK)通過翻轉內部結構,徹底改變了散熱路徑:

路徑重構: 芯片的漏極(Drain,即產(chǎn)熱面)通過金屬片直接連接到封裝的頂部裸露焊盤(Exposed Pad) 。

直通散熱: 熱傳導路徑變?yōu)椋?strong>芯片結(Junction) → 引線框架/金屬蓋 → 封裝頂部 → 熱界面材料(TIM) → 液冷冷板(Cold Plate) 。

物理隔離: 這一架構完全繞過了PCB。PCB不再承擔主要的散熱任務,僅負責電氣信號傳輸。

4.3 TSC封裝的技術優(yōu)勢量化

熱阻大幅降低: 通過移除PCB這一高熱阻環(huán)節(jié),TSC封裝的結到散熱器熱阻(Rth(j?h)?)相比傳統(tǒng)BSC方案可降低 20%至50% 。這意味著在相同的結溫限制下,TSC器件可以承載更大的電流,或者在相同電流下運行在更低的溫度,從而延長壽命。

PCB熱解耦: 實驗數(shù)據(jù)顯示,采用TSC封裝時,PCB板溫可顯著降低。例如Nexperia的研究表明,在7.5kW轉換器測試中,TSC封裝的殼溫比BSC封裝低 38.8°C 。這種熱解耦極大地提升了系統(tǒng)的整體可靠性。

電氣寄生參數(shù)優(yōu)化: TSC封裝(特別是QDPAK)通常采用開爾文源極(Kelvin Source)設計,并優(yōu)化了內部引線結構,具有極低的寄生電感(Stray Inductance)。相比長引腳的TO-247封裝,TSC SMD封裝的回路電感可降低 3倍 以上 。低電感對于發(fā)揮SiC的高速開關特性至關重要,能有效抑制關斷電壓尖峰(VDS,spike?)和開關振蕩,降低開關損耗(Eon?,Eoff?)。

空間利用率倍增: 由于散熱器不再安裝在PCB背面,PCB背面空間被釋放出來,可以布置其他元器件(如驅動器、去耦電容),從而顯著提升功率密度(Power Density),這對于追求極致密度的AI電源模塊至關重要 。

第五章 基本半導體(BASiC Semiconductor) B3M系列深度技術評測

作為國產(chǎn)碳化硅功率器件的領軍企業(yè),基本半導體(BASiC Semiconductor)針對AI數(shù)據(jù)中心和車載應用推出了第三代(B3M系列)SiC MOSFET,并采用了先進的頂部散熱封裝技術。以下基于其產(chǎn)品數(shù)據(jù)手冊 進行深度技術評測。

5.1 產(chǎn)品規(guī)格概覽

我們選取了兩款代表性產(chǎn)品進行分析:B3M025065B(TOLT封裝)和 AB3M025065CQ(QDPAK封裝)。

| 參數(shù)指標 | B3M025065B (TOLT) | AB3M025065CQ (QDPAK) | AI電源應用價值解析 |

|---|---|---|---|

| 耐壓 (VDS?) | 650 V | 650 V | 適配400V/800V PFC母線及LLC原邊電壓。 |

| 導通電阻 (RDS(on)?) | 25 mΩ (Typ @ 18V) | 25 mΩ (Typ @ 18V) | 極低的導通損耗,支撐Titanium級效率。 |

| 持續(xù)電流 (ID? @ 25°C) | 108 A | 115 A | 高電流能力,適應3kW-12kW高功率模組。 |

| 熱阻 (Rth(j?c)?) | 0.40 K/W | ~0.35 K/W (估算) | 極低熱阻,完美適配液冷冷板高強度散熱。 |

| 結溫 (Tj?) | -55°C 至 175°C | -55°C 至 175°C | 高溫魯棒性,應對瞬時過載。 |

| 封裝形式 | TOLT (MO-332) | QDPAK | 頂部散熱,SMT貼片,自動化生產(chǎn)。 |

| 特殊引腳 | Kelvin Source | Kelvin Source | 解耦柵極驅動回路,提升開關速度與抗干擾能力。 |

| 認證標準 | 工業(yè)級/車規(guī)級 | AEC-Q101 | 車規(guī)級可靠性背書,保障數(shù)據(jù)中心24/7運行。 |

5.2 B3M系列的核心技術優(yōu)勢

低比導通電阻(Low Specific Ron?): B3M系列基于基本半導體第三代工藝平臺,優(yōu)化了元胞結構,實現(xiàn)了在650V耐壓下極具競爭力的25mΩ導通電阻。在AI PSU的大電流輸出工況下(例如50V/100A整流),低阻抗直接轉化為更低的發(fā)熱和更高的效率。

優(yōu)化的柵極電荷(Qg?): 即使在大電流規(guī)格下,B3M系列的柵極電荷依然保持在較低水平(Qg?≈98nC )。這意味著驅動損耗更低,且開關速度更快,有助于降低開關損耗(Switching Loss)。

開爾文源極(Kelvin Source): 無論是TOLT還是QDPAK封裝,B3M系列均配置了開爾文源極引腳(Pin 7 for TOLT, Pin 2 for QDPAK)。這一設計將功率回路的源極與驅動回路的源極在物理上分開,消除了公共源極電感(Common Source Inductance)對柵極驅動信號的負反饋影響,從而顯著提升了開關速度,減少了開通損耗(Eon?)并防止了誤導通風險。

雪崩耐量(Avalanche Ruggedness): 數(shù)據(jù)手冊明確標注了Avalanche Ruggedness ,表明器件在應對電網(wǎng)波動或感性負載關斷時的電壓尖峰具有極強的承受能力,這對于保障AI算力中心的供電穩(wěn)定性至關重要。

5.3 封裝特性的深度對比

TOLT (B3M025065B): 采用了JEDEC MO-332標準封裝。其引腳設計保留了類似TOLL的鷗翼形引腳,但在封裝頂部裸露了散熱金屬片。其 Rth(jc)?=0.40K/W 的指標非常優(yōu)異,且封裝占板面積小,適合緊湊型PSU設計。

QDPAK (AB3M025065CQ): 是一種更為先進的高功率SMD封裝。相比TOLT,QDPAK通常具有更大的散熱面積和更低的寄生電感。其AEC-Q101認證表明該器件達到了汽車電子的嚴苛可靠性標準(如溫度循環(huán)、高濕高壓偏置等),應用在數(shù)據(jù)中心能提供超額的可靠性裕量。

第六章 系統(tǒng)集成與熱管理工程

將TSC SiC MOSFET成功應用于AI液冷電源,不僅僅是器件選型的問題,更是一個涉及機械、材料和熱力學的系統(tǒng)工程。

6.1 機械集成:冷板與TIM的“三明治”結構

在實際應用中,PSU內部會形成一個緊密的“三明治”散熱結構:

PCB層: B3M SiC MOSFET通過回流焊貼裝在PCB上。

器件層: MOSFET頂部金屬面(Drain極,高電位)朝上。

絕緣導熱層(TIM): 這是最關鍵的界面。由于MOSFET頂部帶電(650V/1200V高壓),必須在器件與冷板之間放置高性能的絕緣導熱材料(Thermal Interface Material)。常用的方案包括氮化鋁(AlN)陶瓷片配合導熱硅脂,或者高性能的絕緣導熱墊(Gap Pad)。該層必須具備極高的介電強度(Dielectric Strength)以防止擊穿,同時保持極低的熱阻 。

冷板層(Cold Plate): 通常為鋁制或銅制,內部加工有微流道(Micro-channels),冷卻液在其中高速流動帶走熱量。

壓緊機構: 為了最小化接觸熱阻,必須施加足夠的扣合力(Mounting Force)。然而,過大的壓力可能損壞PCB或器件。TSC封裝通常設計有特殊的“負高度差”(Negative Standoff)或柔性引腳結構,以吸收公差并緩沖機械應力 。

6.2 漏液與冷板設計

OCP ORv3規(guī)范對防漏液設計有嚴格要求。盲插接頭必須具備無滴漏(Non-spill)特性。在PSU內部,冷板設計通常采用一體化釬焊工藝,減少密封圈的使用,以降低長期運行的泄漏風險。此外,通過集成液冷母線,可以將大電流路徑的散熱也納入統(tǒng)一的液冷循環(huán),實現(xiàn)全系統(tǒng)的熱管理閉環(huán)。

第七章 全生命周期成本(TCO)與商業(yè)價值模型

部署液冷TSC SiC電源架構雖然面臨較高的初始資本支出(CAPEX),但其帶來的運營支出(OPEX)節(jié)省和潛在收益在AI算力中心的生命周期內具有壓倒性的商業(yè)價值。

7.1 PUE優(yōu)化帶來的直接電費節(jié)省

PUE降低: 傳統(tǒng)風冷AI數(shù)據(jù)中心的PUE通常在1.4-1.6之間。采用全液冷架構(包括液冷PSU)后,由于移除了高功耗風扇并提高了冷源溫度(支持更高水溫的自然冷卻),PUE可顯著降低至1.05-1.15 。

經(jīng)濟賬: 對于一個100MW的超大型AI計算中心,將PUE從1.5降低到1.1,意味著節(jié)省了26%的非IT能耗。按每度電0.1美元計算,每年僅電費節(jié)省就可達 數(shù)千萬美元 。

7.2 80 PLUS Titanium效率的經(jīng)濟杠桿

BASiC B3M SiC MOSFET賦能的鈦金級PSU(97.5%效率)相比鉑金級PSU(94%效率),減少了3.5%的電能損耗。

計算: 在100MW的負載下,3.5%的效率提升意味著少浪費3.5MW的電力。這不僅直接節(jié)省了電費,還減少了3.5MW的熱負荷,進一步降低了冷卻系統(tǒng)的建設和運行成本。這種“雙重收益”使得SiC器件的投資回報期(ROI)通常縮短至2年以內 。

7.3 密度紅利與地產(chǎn)價值

空間套利: 液冷允許單機柜功率從20kW提升至100kW+。這意味著在同樣的物理建筑面積內,可以部署3-5倍的算力密度 。

商業(yè)邏輯: 對于托管型數(shù)據(jù)中心或云服務商,單位面積的算力產(chǎn)出(Revenue per Square Foot)直接決定了盈利能力。TSC SiC MOSFET通過縮小PSU體積(功率密度>100W/in3),為昂貴的AI加速卡騰出了寶貴的機柜空間。

7.4 可靠性帶來的隱形收益

阿倫尼烏斯定律(Arrhenius Law): 電子元器件的失效率通常隨溫度每升高10°C而翻倍。液冷配合TSC技術可以將功率器件的結溫長期控制在較低且穩(wěn)定的水平(例如80-100°C,遠低于150°C極限)。這大幅延長了電源模塊的平均故障間隔時間(MTBF),減少了停機維護帶來的巨大算力損失 。

去風扇化: 風扇是服務器中最容易發(fā)生機械故障的部件之一。液冷PSU去除了風扇,消除了這一單點故障源,同時也消除了風扇振動對精密硬盤和光學互連器件的潛在影響。

第八章 結論與展望

AI算力革命正在重塑數(shù)據(jù)中心的物理形態(tài)。面對100kW+的機柜功率密度,基于OCP ORv3標準的液冷電源架構不僅是技術演進的必然,更是經(jīng)濟效益的最優(yōu)解。

在此架構中,頂部散熱(TSC)碳化硅(SiC)MOSFET扮演著至關重要的角色。

技術層面: BASiC B3M系列等SiC器件憑借卓越的材料特性和創(chuàng)新的TOLT/QDPAK封裝,打破了傳統(tǒng)硅基器件的效率天花板和PCB散熱瓶頸,實現(xiàn)了97.5%以上的超高轉換效率和極高的功率密度。

商業(yè)層面: 盡管SiC器件單價高于硅器件,但其帶來的PUE降低、電費節(jié)省、機房空間優(yōu)化以及可靠性提升,使得總體擁有成本(TCO)顯著優(yōu)于傳統(tǒng)方案。

展望未來,隨著AI模型參數(shù)量的持續(xù)膨脹,數(shù)據(jù)中心將進一步向800V高壓直流架構和浸沒式液冷演進。而在這一進程中,掌握先進封裝技術和高性能碳化硅芯片技術的企業(yè),將成為支撐AI基礎設施算力底座的核心力量。

審核編輯 黃宇

-

電源

+關注

關注

185文章

18924瀏覽量

264183 -

AI

+關注

關注

91文章

40579瀏覽量

302226 -

算力

+關注

關注

2文章

1600瀏覽量

16814

發(fā)布評論請先 登錄

GTC 2026引爆AI算力新浪潮,芯聯(lián)集成如何為萬億AI算力注入能源動力

TI 攜手 NVIDIA 推出面向下一代 AI 數(shù)據(jù)中心的完整 800 VDC 電源架構

偉創(chuàng)力攜手博通,推進下一代AI液冷解決方案落地

AI算力中心的能耗挑戰(zhàn):CM5A 2000 H01霍爾閉環(huán)電流傳感器在AI算力中心(AIDC)的應用分析

羅姆面向下一代800 VDC架構發(fā)布電源解決方案白皮書

安森美SiC器件賦能下一代AI數(shù)據(jù)中心變革

國產(chǎn)AI芯片真能扛住“算力內卷”?海思昇騰的這波操作藏了多少細節(jié)?

華為聯(lián)合發(fā)布智能算網(wǎng)研究報告

睿海光電領航AI光模塊:超快交付與全場景兼容賦能智算時代——以創(chuàng)新實力助力全球客戶構建高效算力底座

睿海光電以高效交付與廣泛兼容助力AI數(shù)據(jù)中心800G光模塊升級

安森美攜手英偉達推動下一代AI數(shù)據(jù)中心發(fā)展

NVIDIA 采用納微半導體開發(fā)新一代數(shù)據(jù)中心電源架構 800V HVDC 方案,賦能下一代AI兆瓦級算力需求

AI算力中心下一代液冷電源架構研究報告

AI算力中心下一代液冷電源架構研究報告

評論