AI算力基礎設施的能源變革:高功率密度集成機架電源架構、拓撲演進與碳化硅MOSFET的應用價值深度研究報告

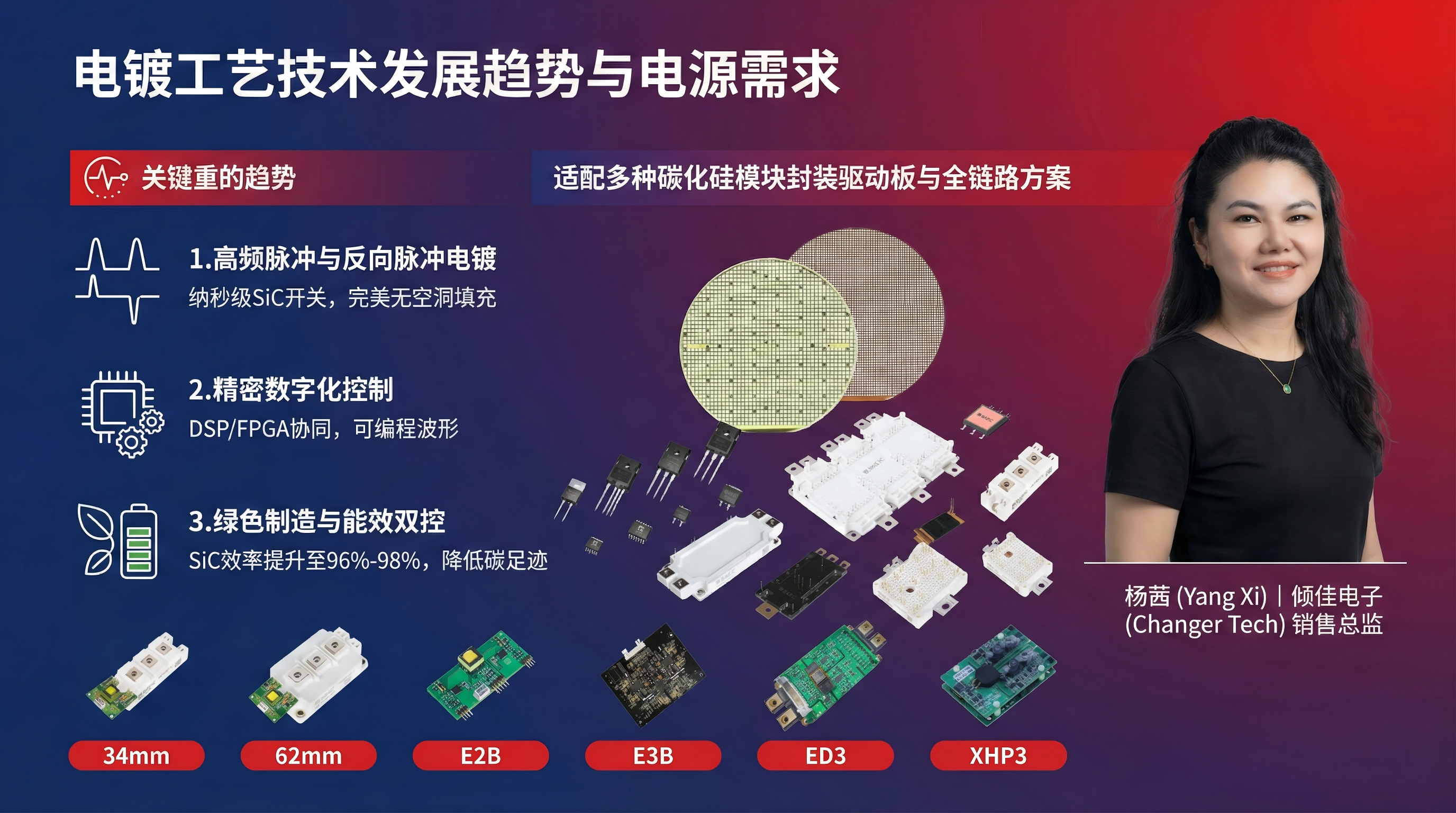

BASiC Semiconductor基本半導體一級代理商傾佳電子(Changer Tech)是一家專注于功率半導體和新能源汽車連接器的分銷商。主要服務于中國工業電源、電力電子設備和新能源汽車產業鏈。傾佳電子聚焦于新能源、交通電動化和數字化轉型三大方向,代理并力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板等功率半導體器件以及新能源汽車連接器。?

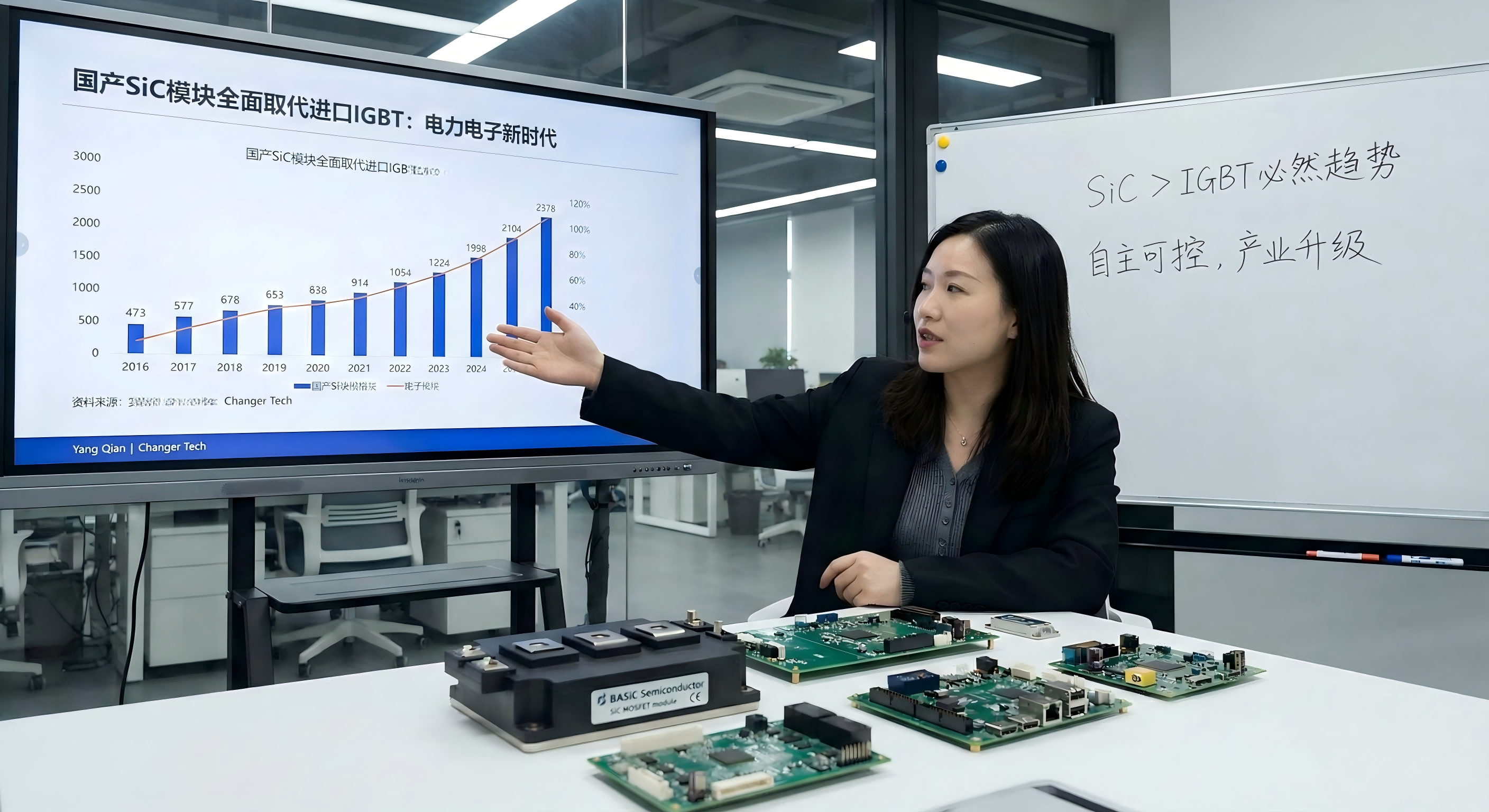

傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

傾佳電子楊茜咬住SiC碳化硅MOSFET功率器件三個必然,勇立功率半導體器件變革潮頭:

傾佳電子楊茜咬住SiC碳化硅MOSFET模塊全面取代IGBT模塊和IPM模塊的必然趨勢!

傾佳電子楊茜咬住SiC碳化硅MOSFET單管全面取代IGBT單管和大于650V的高壓硅MOSFET的必然趨勢!

傾佳電子楊茜咬住650V SiC碳化硅MOSFET單管全面取代SJ超結MOSFET和高壓GaN 器件的必然趨勢!

1. 執行摘要

隨著以ChatGPT、Sora為代表的生成式人工智能(Generative AI)和大語言模型(LLM)的爆發式增長,全球數據中心的算力需求正經歷著前所未有的指數級躍升。這一趨勢不僅重塑了計算芯片的設計邏輯,更對底層能源基礎設施提出了嚴苛的物理挑戰。當單顆GPU加速器的熱設計功耗(TDP)突破1000瓦,單機架功率密度從傳統的10kW飆升至120kW甚至更高時,傳統的分布式電源架構已難以為繼。

傾佳電子全面剖析面向AI算力服務器的高功率密度電源系統——特別是符合Open Compute Project (OCP) Open Rack v3 (ORv3) 標準的集成機架式電源架構。我們將深入探討從傳統的12V分布式供電向48V集中式母線架構的范式轉移,并解析支撐這一變革的核心電路拓撲:無橋圖騰柱功率因數校正(Totem-Pole PFC)與高頻LLC諧振變換器。

在這一技術演進中,寬禁帶(WBG)半導體,尤其是碳化硅(SiC)MOSFET,扮演了決定性的賦能者角色。基于基本半導體(BASIC Semiconductor)等廠商的最新器件規格,本報告將量化分析SiC MOSFET在降低開關損耗、提升熱管理效率以及應對高壓直流(HVDC)趨勢中的獨特價值。結合先進的頂部散熱(Top-Side Cooling, TSC)封裝技術與液冷生態系統的融合,我們描繪了一幅通往每立方英寸100瓦(100 W/in3)以上超高功率密度電源的演進路線圖。

2. AI算力時代的能源挑戰與架構重構

2.1 算力摩爾定律的失效與功率密度的爆發

在過去十年中,摩爾定律主要關注晶體管密度的增加,但在AI時代,"黃氏定律"(Huang’s Law)即GPU性能的提升速度已遠遠超過通用CPU。NVIDIA DGX H100系統的發布標志著單節點功耗正式邁入10kW量級,而隨后的GB200 NVL72機架級系統更是將這一數字推向了120kW的驚人高度 。

這種數量級的跨越導致了傳統數據中心供電設計的全面失效。在傳統的12V供電架構下,若要為一個120kW的機架供電,其總線電流將高達10,000安培。這不僅需要如同手臂般粗細的銅排來承載電流,其產生的I2R傳輸損耗也將達到不可接受的程度 。因此,行業正經歷一場從服務器級電源向機架級電源(Power Shelf)的徹底轉型,電壓等級也無可挽回地從12V轉向48V/54V,并正在向800V HVDC演進。

2.2 Open Rack v3 (ORv3):高密度供電的標準化基石

為了應對超大規模計算的能效挑戰,Open Compute Project (OCP) 制定了Open Rack v3標準,重新定義了機架內的電力分配方式。ORv3摒棄了傳統的內置于服務器機箱內的CRPS(Common Redundant Power Supply)電源,轉而采用集中式的電源架(Power Shelf) 。

2.2.1 集中式電源架架構優勢

ORv3電源架設計為1OU高度,通常包含6個熱插拔整流模塊(PSU),通過背部的匯流排(Busbar)直接向整個機架輸送48V/50V直流電。這種架構帶來了多重優勢:

空間優化: 將AC/DC轉換從計算節點中剝離,使得服務器機箱(Compute Tray)能容納更多的GPU和散熱組件 。

轉換效率提升: 48V母線相比12V母線,電流減少了4倍,傳輸損耗理論上降低了16倍(Ploss?∝I2)。這使得整個機架的端到端效率提升了10%至15% 。

彈性的冗余配置: 集中式電源允許在機架層面實現N+1或N+N冗余,相比于每臺服務器都要配置1+1冗余電源,大幅減少了閑置的電源容量,提高了電源利用率(Stranded Capacity) 。

2.2.2 嚴苛的能效與動態響應指標

ORv3標準對電源模塊的效率提出了極高要求,通常要求滿足或超越80 PLUS Titanium標準:

峰值效率: 在50%負載下必須超過97.5%。

滿載效率: 在100%負載下必須超過96.5%。

輕載效率: 即便在10%的低負載下,也要求效率高于94% 7。

此外,AI訓練負載具有極端的動態特性。GPU在進行大規模矩陣運算時,會在微秒級時間內產生巨大的電流瞬變(di/dt)。ORv3電源必須具備極快的動態響應能力,以維持48V母線的電壓穩定,防止系統掉電或重啟。這對電源內部的控制環路帶寬和功率器件的開關速度提出了嚴峻考驗。

2.3 集成電池備份單元(BBU)的興起

為了應對電網波動和削峰填谷(Peak Shaving)的需求,ORv3架構引入了集成的電池備份單元(BBU)架。這些BBU模塊直接掛載在48V母線上,當AC輸入中斷或瞬時負載超過電源架能力時,BBU會無縫介入供電 。

這引入了雙向DC-DC變換的需求。在正常運行時,電源架為BBU充電(Buck模式);在掉電時,BBU向母線放電(Boost模式)。這種雙向能量流動的需求,使得具備低導通電阻和雙向導通特性的同步整流MOSFET成為了唯一選擇。

3. 高功率密度電源拓撲架構的演進

要實現ORv3所要求的97.5%以上效率和100 W/in3以上的功率密度,傳統的電路拓撲已經觸及了物理天花板。基于硅(Si)器件的傳統PFC(如交錯并聯Boost PFC)受限于二極管整流橋的導通損耗和硅MOSFET的反向恢復損耗,已無法滿足AI服務器電源的需求。

3.1 AC/DC級:圖騰柱PFC(Totem-Pole PFC)的統治地位

圖騰柱PFC拓撲消除了傳統Boost PFC前端的整流二極管橋,從而消除了兩個二極管壓降帶來的顯著導通損耗。在3kW以上的應用中,這部分損耗可占總損耗的20%以上。

3.1.1 連續導通模式(CCM)的關鍵挑戰

圖騰柱PFC分為慢速橋臂(Line Frequency Leg)和快速橋臂(High Frequency Leg)。慢速橋臂以工頻(50/60Hz)切換,負責整流;快速橋臂以高頻(65kHz-150kHz)切換,負責功率因數校正。

在**連續導通模式(CCM)**下,當主開關管開通時,續流管的體二極管會被強制反向恢復。對于傳統的硅超結(Superjunction)MOSFET,其體二極管的反向恢復電荷(Qrr?)非常大,導致巨大的反向恢復電流和開關損耗,甚至可能導致器件失效。這使得硅MOSFET幾乎無法用于CCM模式的圖騰柱PFC 。

3.1.2 碳化硅(SiC)的破局

SiC MOSFET的體二極管具有極低的反向恢復電荷(Qrr?),通常僅為同規格硅器件的1/10甚至更低。例如,基本半導體(BASIC Semiconductor) 的 B3M025075Z(750V SiC MOSFET)在測試條件下表現出優異的反向恢復特性,能夠承受硬開關(Hard Switching)帶來的應力 。這使得圖騰柱PFC能夠工作在CCM模式下,從而在保持低紋波電流的同時,大幅提升效率并減小電感體積。

3.1.3 交錯并聯技術的應用

為了進一步提升功率密度并分散熱量,5.5kW及以上的電源模塊通常采用**交錯并聯(Interleaved)**的圖騰柱PFC架構。通過將兩個或多個快速橋臂并聯并錯相運行(如180度相位差),可以大幅抵消輸入電流紋波,減小EMI濾波器的體積,并分散功率器件的熱應力 。基本半導體的 B3M040065B(650V, 40mΩ)等器件非常適合此類應用,其緊湊的TOLT封裝允許在PCB上高密度布置多個并聯支路 。

3.2 DC/DC級:LLC諧振變換器的高頻化

在PFC之后,DC/DC級負責將400V直流母線電壓隔離降壓至48V。全橋LLC諧振變換器因其能在全負載范圍內實現原邊零電壓開通(ZVS)和副邊零電流關斷(ZCS)而成為主流選擇。

3.2.1 開關頻率與功率密度的博弈

為了縮小變壓器和諧振電容的體積,設計者不斷推高開關頻率(從100kHz向500kHz甚至更高邁進)。然而,頻率的提升受到MOSFET輸出電容(Coss?)和關斷損耗(Eoff?)的制約。

SiC MOSFET相比硅基器件,具有更低的Coss?及更線性的電容特性,這使得實現ZVS所需的死區時間更短,勵磁電流更小,從而提升了循環效率。基本半導體的 B3M040065L 在400V時的Eoss?僅為12 μJ ,這對于提升輕載效率至關重要,有助于滿足ORv3對輕載效率的嚴苛要求。

3.2.2 三相交錯LLC架構

針對8kW及以上的高功率模塊,單路LLC的電流應力過大。三相交錯LLC架構(3-Phase Interleaved LLC)通過三個錯相120度的LLC單元并聯,不僅分攤了電流,還使得輸出紋波頻率提高至開關頻率的6倍,極大地減小了輸出濾波電容的體積,這對于空間受限的1OU電源架至關重要 。

3.3 混合控制策略:TCM與CCM的融合

為了追求極致效率(>98%),控制策略也在進化。三角電流模式(TCM)可以實現軟開關(ZVS),消除開通損耗,但其變頻特性導致EMI濾波器設計困難且峰值電流大。最新的AI服務器電源設計傾向于采用混合控制策略:在輕載時采用TCM以消除開關損耗,在重載時切換至CCM以降低導通損耗和電流應力。SiC MOSFET憑借其在寬頻率和寬電流范圍內的穩健性,完美適配這種復雜的混合控制模式 。

4. 碳化硅MOSFET在AI電源中的核心應用價值

在AI服務器電源這場追求極致效率與密度的競賽中,碳化硅(SiC)MOSFET并非僅僅是硅的替代品,它是實現下一代架構的物理基礎。

4.1 材料物理特性的降維打擊

SiC作為第三代寬禁帶半導體,其帶隙寬度(~3.26 eV)是硅(1.12 eV)的3倍,臨界擊穿電場是硅的10倍 。這些物理特性轉化為具體的器件優勢:

更薄的漂移層: 在相同的耐壓等級下,SiC的漂移層厚度僅為硅的1/10,從而大幅降低了比導通電阻(Ron,sp?)。這意味著在相同的芯片面積下,SiC MOSFET擁有更低的導通損耗。

更高的熱導率: SiC的熱導率(~3.7 W/cm·K)是硅的3倍,使得器件在相同損耗下結溫更低,或者在相同結溫下能承受更大的功率密度 。

4.2 針對AI負載特性的性能優勢

4.2.1 高溫下的導通電阻穩定性

AI服務器通常運行在高負荷狀態,電源模塊內部環境溫度極高。硅超結MOSFET的導通電阻(RDS(on)?)具有很高的正溫度系數,在150°C時,其阻值通常會翻倍(增加約2.5-3倍)。這會導致熱失控的風險,迫使設計者大幅降額使用。

相比之下,SiC MOSFET的RDS(on)?隨溫度變化非常平緩。以 基本半導體 B3M025065Z 為例,其RDS(on)?在高溫下的增幅遠小于硅器件 。這意味著在高溫滿載工況下,SiC的實際導通損耗遠低于硅,從而提升了系統的熱穩定性及實際可用容量。

4.2.2 極低的反向恢復電荷(Qrr?)

如前所述,圖騰柱PFC的高效運行依賴于開關管體二極管的性能。基本半導體 B3M011C120Z(1200V SiC MOSFET)具有極低的反向恢復電荷 14,這在380V/400V高壓直流或三相交流輸入的應用中至關重要。低Qrr?直接消除了硬開關過程中的巨大電流尖峰,不僅降低了損耗,更大幅減少了高頻噪聲(EMI),簡化了濾波電路設計。

4.2.3 提升開關頻率,縮小體積

SiC MOSFET能夠以數倍于硅IGBT或MOSFET的頻率開關而不會產生過熱。在AI服務器電源中,這意味著可以將開關頻率從傳統的65kHz提升至140kHz-300kHz 。頻率的提升直接導致了磁性元件(PFC電感、LLC變壓器)體積的顯著縮小,這是實現ORv3電源架33kW高功率密度的關鍵因素。

4.3 電壓等級的選擇與可靠性裕量

4.3.1 650V vs 750V:可靠性的博弈

在400V直流母線應用中,傳統的650V器件雖然理論上夠用,但在電網波動或雷擊浪涌等極端工況下,電壓裕量(Headroom)較小。此外,宇宙射線(Cosmic Ray)誘發的單粒子燒毀(SEB)效應在高壓偏置下會顯著增加故障率(FIT Rate)。

為了提高超大規模數據中心的可靠性,行業趨勢正在向750V器件遷移。基本半導體 B3M010C075Z(750V, 10mΩ)提供了額外的100V耐壓裕量 。這不僅增強了抗浪涌能力,更重要的是,在相同的400V工作電壓下,750V器件對宇宙射線的免疫力呈指數級提升,極大地降低了隨機失效的概率 。

4.3.2 1200V:面向未來的800V架構

隨著NVIDIA等廠商推動800V HVDC架構,1200V SiC MOSFET成為必須。B3M011C120Z 提供了1200V的耐壓和223A的通流能力 ,使其成為三相480V輸入PFC或直接800V母線轉換器的理想選擇。在這些高壓應用中,SiC相比于1200V硅IGBT,完全消除了拖尾電流(Tail Current),將開關損耗降低了80%以上。

5. 封裝技術的革新與熱管理

僅僅依靠芯片層面的改進不足以解決100kW+機架的散熱問題。封裝技術的創新是釋放SiC潛能、實現高功率密度的最后一塊拼圖。

5.1 頂部散熱(Top-Side Cooling, TSC)的崛起

傳統的SMD封裝(如D2PAK)將熱量通過底部焊盤傳導至PCB。然而,FR4 PCB的熱導率極低(~0.3 W/m·K),即使添加大量熱過孔,PCB本身也成為了散熱瓶頸。

為了打破這一瓶頸,基本半導體推出了采用 QDPAK 和 TOLT 封裝的SiC MOSFET,如 AB3M025065CQ和 B3M025065B 。

結構原理: TSC封裝將散熱焊盤(Drain Pad)置于器件頂部,直接暴露于空氣中。

熱路徑優化: 散熱器或冷板可以直接壓在器件表面,熱量無需經過PCB,熱阻(RthJC?)大幅降低。例如,AB3M025065CQ的結到殼熱阻極低,僅為0.35 K/W 。

電氣優勢: 由于底部不再需要散熱焊盤,PCB底部的空間被釋放出來用于布線或放置其他器件,進一步提升了板級功率密度。此外,TSC封裝通常配備Kelvin Source引腳,解耦了柵極驅動回路與功率回路,消除了源極電感對開關速度的限制。

5.2 液冷技術的深度融合

GB200 NVL72等AI機架已經全面擁抱液冷技術。ORv3電源架的設計也必須融入這一生態。

冷板集成: 采用QDPAK/TOLT封裝的SiC MOSFET提供了平整的頂部表面,非常適合與液冷冷板(Cold Plate)貼合。通過高性能導熱界面材料(TIM),冷板可以直接帶走功率器件產生的熱量。

去風扇化: 液冷的高效散熱使得電源模塊內部的風扇可以被移除或減小,這不僅消除了風扇帶來的寄生功耗(可占電源總功耗的3-5%)和振動(對機械硬盤有害),還大幅提升了系統的平均無故障時間(MTBF)。

盲插流體連接器: 電源模塊與機架流體分配單元(Manifold)之間采用盲插、無滴漏的快速連接器(Quick Disconnects),實現了電源模塊的液冷熱插拔維護 。

6. 集成機架式電源系統架構詳解

6.1 NVIDIA GB200 NVL72 供電架構案例

以目前最先進的NVIDIA GB200 NVL72為例,其供電架構代表了未來的主流方向 :

總功耗: 單機架約120kW。

電源架配置: 一個機架包含6到8個電源架(Power Shelf),每個電源架額定功率33kW。

電源模塊(PSU): 每個電源架容納6個5.5kW的整流模塊,采用N+N或N+1冗余配置。這意味著整個機架可能包含多達48個高功率SiC電源模塊。

輸入電源: 采用三相415 VAC直接輸入到電源架,消除了機架級PDU的中間環節。

直流母線: 電源架輸出48V/50V直流電,通過巨大的銅排(Busbar)傳輸至后方的計算托盤(Compute Tray)。

6.2 48V母線的必然性與挑戰

為何選擇48V而非12V或更高的400V?

對比12V: 48V降低了電流和損耗,使得120kW的功率傳輸在物理上成為可能。

對比400V: 48V(<60V)屬于安全特低電壓(SELV),是非絕緣電路,維護更加安全,且允許在服務器主板上使用更小間距的布線,有利于高密度計算芯片的布局。

中間總線轉換(IBC): 計算托盤上需要高效的IBC模塊將48V轉換為12V或直接轉換為GPU所需的低壓大電流(<1V, >1000A)。這一級轉換同樣大量采用GaN或低壓SiC器件以維持高效率。

7. 邁向800V HVDC

盡管48V架構解決了當前的燃眉之急,但隨著機架功率向1MW邁進(如NVIDIA未來的GB300規劃),48V母線所需的銅排重量將達到數百公斤,物理連接將變得極其困難 。

7.1 800V HVDC 直供技術

未來的AI工廠將趨向于800V HVDC架構:

電網直連: 采用固態變壓器(SST)將中壓交流電(13.8kV)直接轉換為800V直流電。

機架內傳輸: 800V直流電直接進入機架,消除了傳統的AC/DC電源架,取而代之的是機架內的DC/DC轉換模塊。

SiC的終極舞臺: 在800V架構中,1200V和1700V的SiC MOSFET將成為絕對主角。它們需要承受更高的電壓應力,同時保持高頻開關以縮小隔離變壓器的體積。基本半導體的 B3M011C120Z 等1200V產品線正是為這一趨勢做好了技術儲備 。

8. 結論

AI算力需求的爆發正在倒逼數據中心能源基礎設施進行一場徹底的革命。從服務器電源到機架式電源架,從12V到48V再到未來的800V,每一次電壓等級和拓撲架構的躍遷,其核心驅動力都是對功率密度和能源效率的極致追求。

在這一變革中,碳化硅(SiC)MOSFET憑借其無與倫比的開關特性、耐高壓能力和熱導率,成為了不可或缺的技術基石。

拓撲賦能: SiC使得圖騰柱PFC等高效硬開關拓撲成為現實,將AC/DC級效率推向99%的極限。

密度提升: 通過支持高頻開關,SiC大幅減小了磁性元件體積;通過高溫低阻特性,減小了散熱需求。

封裝協同: 結合QDPAK、TOLT等頂部散熱封裝,SiC完美融入了AI時代的液冷生態系統。

對于數據中心運營商和電源制造商而言,盡早布局基于750V/1200V SiC MOSFET的高密度電源方案,不僅是滿足ORv3標準的合規需求,更是贏得AI算力軍備競賽能源入場券的關鍵戰略。

表 1:基本半導體 SiC MOSFET 規格對比及其在 AI 電源中的應用

| 參數 | B3M025065B | AB3M025065CQ | B3M010C075Z | B3M011C120Z |

|---|---|---|---|---|

| 電壓等級 (VDS?) | 650 V | 650 V | 750 V | 1200 V |

| 電流 (ID? @ 25°C) | 108 A | 115 A | 240 A | 223 A |

| 典型導通電阻 (RDS(on)? 18V) | 25 mΩ | 25 mΩ | 10 mΩ | 11 mΩ |

| 封裝形式 | TOLT (頂部散熱) | QDPAK (頂部散熱) | TO-247-4 | TO-247-4 |

| 熱阻 (RthJC?) | 0.40 K/W | 0.35 K/W | 0.20 K/W | 0.15 K/W |

| 核心應用場景 | 3kW-5.5kW PSU PFC/LLC | 液冷電源模塊, 高密度SMPS | 高可靠性PFC (抗浪涌/輻射) | 3相PFC, 800V HVDC架構 |

表 2:AI服務器電源技術演進路線圖

| 階段 | 傳統計算 | 高性能計算 (HPC) | AI工廠 (當前主流) | 下一代 AI (未來) |

|---|---|---|---|---|

| 機架功率 | 10 - 15 kW | 20 - 40 kW | 100 - 132 kW | > 200 kW - 1 MW |

| 電源單元 (PSU) | 800 W - 1.6 kW CRPS | 2 kW - 3 kW CRPS | 5.5 kW - 8 kW 電源架 | 12 kW - 33 kW / 集中整流 |

| 母線電壓 | 12 V | 12 V / 48 V | 48 V / 54 V | 400 V / 800 V HVDC |

| PFC 拓撲 | 硅基 Boost PFC | 交錯并聯 Boost (Si) | SiC 圖騰柱 CCM PFC | 三相圖騰柱 / 維也納整流 |

| 散熱方式 | 風冷 (Fans) | 風冷 + 熱管 | 液冷 (冷板/背門) | 芯片級液冷 / 浸沒式 |

表 3:SiC MOSFET 在 AI 電源關鍵拓撲中的價值分析

| 拓撲級 | 硅器件的瓶頸 | SiC 的解決方案 | 系統級價值 |

|---|---|---|---|

| 圖騰柱 PFC (快橋臂) | 體二極管反向恢復電荷 (Qrr?) 過大,導致CCM模式下嚴重的開關損耗和炸管風險。 | 近零 Qrr? ,允許在CCM模式下進行高效硬開關。 | 實現99%以上的PFC效率;大幅減小電感體積 (頻率提升2-3倍)。 |

| DC-DC (LLC 原邊) | 輸出電容 (Coss?) 較大且非線性,限制了死區時間優化和開關頻率。 | 更低且線性的 Coss?,更低的關斷損耗 (Eoff?)。 | 支持 >500 kHz 開關頻率;縮小變壓器和諧振腔體積。 |

| BBU 雙向變換 | 導通電阻隨溫度急劇上升,雙向效率難以兼顧。 | 高溫下 RDS(on)? 極其穩定 (175°C僅增加~40%)。 | 提升電池充放電效率;減少散熱需求,延長電池壽命。 |

| 熱管理與封裝 | 只能通過底部PCB散熱,熱阻大,無法應對高密度熱流。 | QDPAK/TOLT 頂部散熱封裝,直接貼合冷板。 | 解除PCB熱瓶頸;完美適配液冷機架設計;提升功率密度至100 W/in3+。 |

審核編輯 黃宇

-

MOSFET

+關注

關注

151文章

9998瀏覽量

234239 -

機架電源

+關注

關注

0文章

5瀏覽量

6435 -

AI算力

+關注

關注

1文章

153瀏覽量

9983

發布評論請先 登錄

SiC碳化硅MOSFET隔離驅動電源系統中負壓生成的物理機制與工程實現研究報告

碳化硅 (SiC) MOSFET dv/dt 極限物理本質深度研究報告

全碳化硅 (All-SiC) 有源中點鉗位 (ANPC) 拓撲解決方案研究報告

B3M系列碳化硅MOSFET軟反向恢復技術特性及其在橋式拓撲中的應用價值研究報告

MCS兆瓦級充電系統拓撲架構演進與SiC碳化硅模塊升級替代IGBT模塊技術研究報告

陽臺微儲的拓撲架構演進、技術趨勢及碳化硅MOSFET在其中的應用

基于SiC碳化硅功率器件的c研究報告

傾佳電子光伏與儲能產業功率半導體分立器件從IGBT向碳化硅MOSFET轉型的深度研究報告

傾佳電子碳化硅SiC MOSFET驅動特性與保護機制深度研究報告

傾佳電子主流廠商碳化硅 (SiC) MOSFET 驅動 IC 產品及其技術特征深度研究報告

AI算力機架電源架構、拓撲演進與碳化硅MOSFET的應用價值深度研究報告

AI算力機架電源架構、拓撲演進與碳化硅MOSFET的應用價值深度研究報告

評論