LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南

在電子設計領域,時鐘抖動的控制至關重要,它直接影響著系統的性能和穩定性。TI 的 LMK04000 系列低噪聲時鐘抖動清除器,憑借其先進的技術和出色的性能,為眾多應用場景提供了可靠的時鐘解決方案。今天就和大家深入探討一下這款產品,希望能給大家的設計工作帶來一些啟發。

文件下載:lmk04002.pdf

1. 產品概述

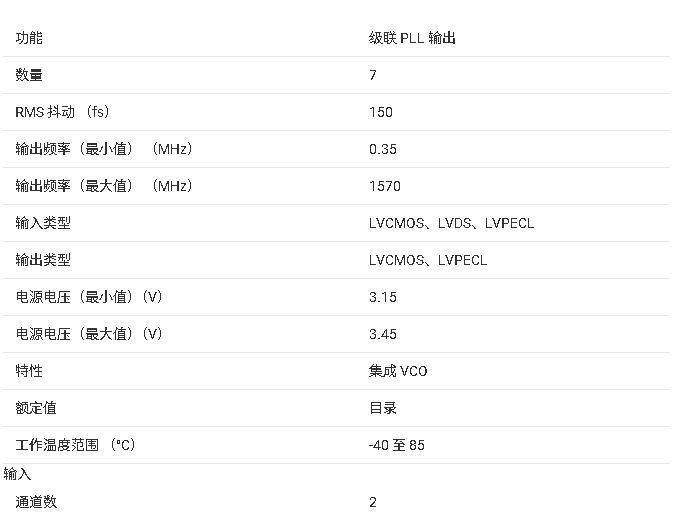

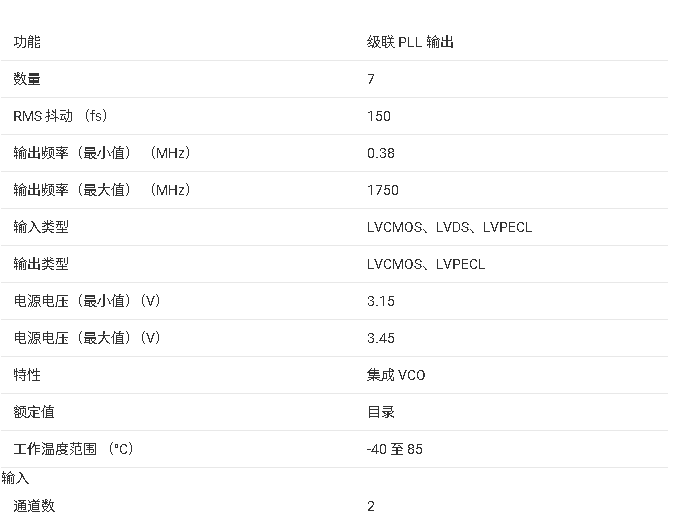

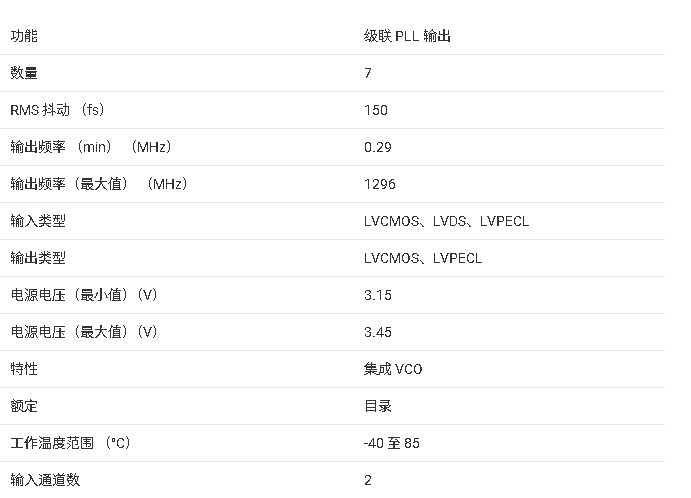

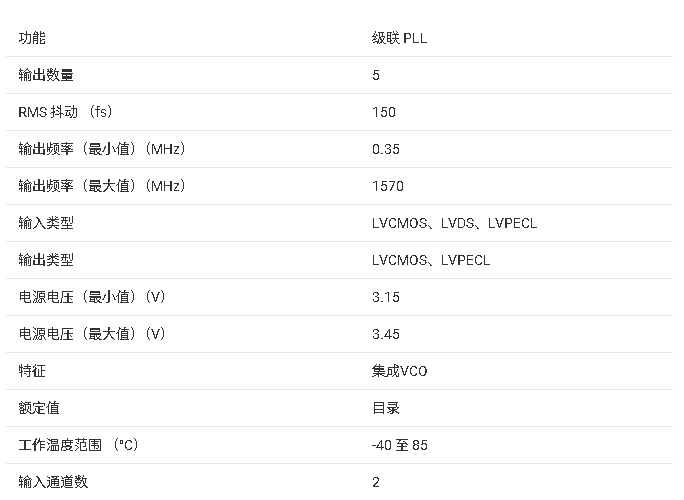

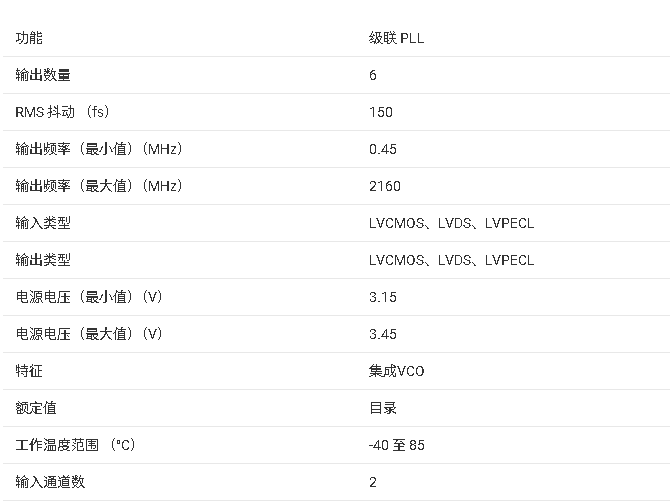

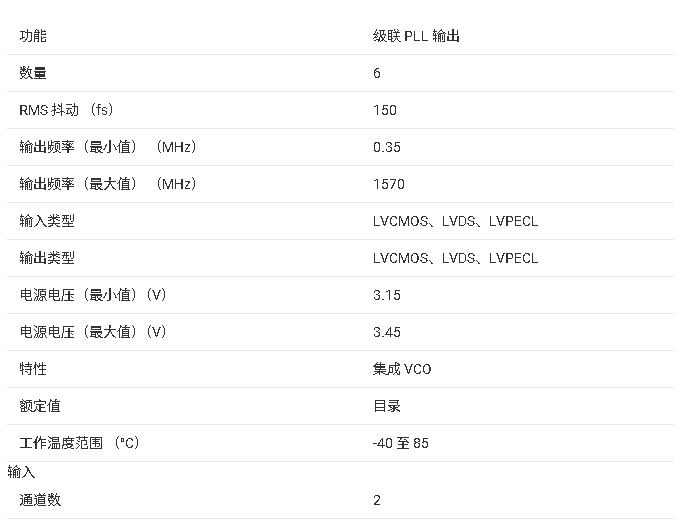

LMK04000 系列包含 LMK04000、LMK04001、LMK04002、LMK04010、LMK04011、LMK04031 和 LMK04033 等型號,采用了級聯的 PLLatinum? 架構,能夠在不需要高性能壓控晶體振蕩器(VCXO)模塊的情況下,實現低噪聲抖動清除、時鐘乘法和分配功能。其超低的 RMS 抖動性能,能為系統提供穩定、精確的時鐘信號。

1.1 主要特點

- 級聯 PLL 架構:由兩個高性能鎖相環(PLL)組成,PLL1 作為低噪聲抖動清除器,使用窄環路帶寬保持輸入時鐘信號的頻率精度,同時抑制高頻偏移相位噪聲;PLL2 負責時鐘生成,可使用較寬的環路帶寬,利用內部 VCO 的優異高頻偏移相位噪聲特性,實現超低抖動輸出。

- 超低 RMS 抖動:在不同頻率范圍內都表現出出色的抖動性能,如 150 fs RMS 抖動(12 kHz – 20 MHz)和 200 fs RMS 抖動(100 Hz – 20 MHz),能夠滿足對時鐘精度要求極高的應用場景。

- 多種輸出類型:支持 LVPECL/2VPECL、LVDS 和 LVCMOS 等多種輸出類型,可適應不同的接口標準,最大時鐘速率可達 1080 MHz。

- 雙冗余輸入和默認時鐘:具備雙冗余輸入,可在自動或手動模式下選擇參考時鐘,提高系統的可靠性;上電時提供默認時鐘輸出(CLKout2),可為系統中的 FPGA 或微控制器提供初始時鐘。

- 靈活配置:擁有五個專用通道分頻器和延遲塊,可對輸出時鐘進行靈活的分頻和延遲調整;引腳兼容,方便在不同設計中進行替換和升級。

- 寬溫度范圍和工作電壓:工業溫度范圍為 -40 至 85 °C,工作電壓為 3.15 V 至 3.45 V,能適應各種惡劣的工作環境。

- 小型封裝:采用 48 引腳 WQFN(7.0 x 7.0 x 0.8 mm)封裝,節省 PCB 空間。

2. 應用領域

LMK04000 系列的出色性能使其廣泛應用于多個領域,以下是一些常見的應用場景:

- 數據轉換器時鐘:為數據轉換器提供精確、低抖動的時鐘信號,確保數據采集和轉換的準確性。

- 無線基礎設施:在無線通信基站等設備中,保證時鐘信號的穩定性和低抖動,提高通信質量。

- 網絡、SONET/SDH 和 DSLAM:滿足高速網絡設備對時鐘精度的要求,確保數據傳輸的可靠性。

- 醫療設備:在醫療成像、檢測等設備中,提供穩定的時鐘信號,保障設備的正常運行。

- 軍事/航空航天:適應惡劣的工作環境,為軍事和航空航天設備提供可靠的時鐘解決方案。

- 測試和測量:為測試儀器提供精確的時鐘參考,確保測量結果的準確性。

- 視頻設備:保證視頻信號的同步和穩定,提高視頻質量。

3. 系統架構與工作原理

3.1 級聯 PLL 架構

級聯 PLL 架構是 LMK04000 系列的核心,它由 PLL1 和 PLL2 組成。PLL1 與外部參考時鐘和 VCXO 配合,為 PLL2 提供頻率準確、低相位噪聲的參考時鐘。PLL1 通常采用窄環路帶寬(10 Hz 至 200 Hz),以保留參考時鐘輸入信號的頻率精度,并抑制高頻偏移相位噪聲。PLL2 則利用較寬的環路帶寬(50 kHz 至 200 kHz),充分發揮內部 VCO 的高性能,在高頻偏移時提供低相位噪聲。這種架構使得外部 VCXO 的相位噪聲在低頻偏移時主導最終輸出相位噪聲,而內部 VCO 的相位噪聲在高頻偏移時主導,從而實現了最佳的整體相位噪聲和抖動性能。

3.2 冗余參考輸入和 LOS 檢測

該系列產品具有兩個與 LVDS/LVPECL/LVCMOS 兼容的參考時鐘輸入(CLKin0 和 CLKin1),用戶可以手動選擇輸入,也可以配置自動切換模式。當選擇自動切換模式時,CLKinX_LOS(信號丟失)輸出會指示所選參考時鐘輸入的狀態,用戶可將其配置為 CMOS、NMOS 開漏或 PMOS 開漏輸出。如果 PLL1 原本已鎖定,但兩個參考時鐘都丟失,設備的頻率精度將由 VCXO 的絕對調諧范圍決定。

3.3 集成環路濾波器極點

LMK04000 系列為 PLL2 提供了可編程的 3rd 和 4th 階環路濾波器極點。啟用后,用戶可以從固定范圍內選擇內部電阻和電容值,以實現所需的環路濾波器響應,這些可編程組件與芯片附近的外部組件相輔相成。

3.4 時鐘分配

時鐘分配模塊至少提供五個輸出,輸出類型包括 LVPECL、2VPECL、LVDS 和 LVCMOS,具體組合取決于產品型號。每個時鐘輸出通道都包含一個可編程分頻器、一個相位同步電路、一個可編程延遲和一個輸出緩沖器,用戶可以對每個通道的輸出進行獨立配置。

4. 電氣特性

4.1 電源電壓和溫度范圍

絕對最大電源電壓范圍為 -0.3 至 3.6 V,輸入電壓范圍為 -0.3 至 (VCC + 0.3) V。建議的工作溫度范圍為 -40 至 85 °C,工作電壓為 3.15 至 3.45 V。

4.2 電流消耗

不同的工作模式和配置下,電流消耗會有所不同。例如,在所有時鐘啟用、所有延遲旁路且 Fout 禁用的情況下,LMK04000、LMK04001 和 LMK04002 的典型電流消耗為 380 mA(最大值 435 mA),LMK04010 和 LMK04011 的典型電流消耗為 378 mA(最大值 435 mA),LMK04031 和 LMK04033 的典型電流消耗為 335 mA(最大值 385 mA)。

4.3 時鐘輸入規格

CLKin0/0 和 CLKin1/1 的時鐘輸入頻率在手動選擇模式下為 0.001 至 400 MHz,自動切換模式下為 1 至 400 MHz。為了滿足數據手冊中列出的抖動性能要求,所有輸入時鐘的最小推薦壓擺率為 0.5 V/ns。

4.4 PLL 規格

- PLL1:相位檢測器頻率最高可達 40 MHz,電荷泵源電流和吸收電流可編程,可根據不同的增益設置提供不同的電流值。

- PLL2:參考輸入(OSCin)頻率在 EN_PLL2_REF2X = 0 時最高為 250 MHz,在 EN_PLL2_REF2X = 1 時最高為 50 MHz;相位檢測器頻率最高可達 100 MHz,電荷泵源電流和吸收電流同樣可編程。

4.5 VCO 規格

內部 VCO 的調諧范圍根據不同型號有所不同,如 LMK040x0 為 1185 至 1296 MHz,LMK040x1 為 1430 至 1570 MHz 等。VCO 輸出功率到 50 Ω 負載的典型值也因型號而異,在不同溫度和頻率下有不同的表現。

4.6 時鐘輸出規格

不同輸出類型(LVPECL/2VPECL、LVDS、LVCMOS)的時鐘輸出在頻率、抖動、電壓等方面都有相應的規格要求。例如,LVDS 輸出的最大頻率可達 1080 MHz,差分輸出電壓在特定條件下為 250 至 450 mV;LVPECL 輸出的最大頻率也為 1080 MHz,輸出電壓和擺幅等也有相應的規定。

5. 典型性能特性

通過一系列圖表展示了該系列產品的典型性能特性,包括不同輸出類型的 VOD 與頻率的關系、時鐘通道延遲噪聲地板與頻率的關系、時鐘輸出噪聲地板與頻率的關系等。這些特性有助于工程師在設計過程中更好地了解器件的性能,進行合理的參數選擇和優化。

6. 應用設計要點

6.1 系統級布局

在典型的時鐘應用中,需要合理連接外部電路。例如,將主參考時鐘輸入連接到 CLKin0/0,副參考時鐘連接到 CLKin1/1,VCXO 連接到 OSCin/OSCin* 端口。PLL2 的環路濾波器可由三個外部組件實現兩個低階極點,根據需要還可使用內部集成組件實現 3rd 或 4th 階極點;PLL1 的環路濾波器則必須使用外部組件。同時,要注意電源引腳的連接和電源管理,將時鐘輸出的電源引腳連接到專用電源平面,其他電源引腳連接到另一個電源平面。

6.2 環路濾波器設計

每個 PLL 都需要一個專用的環路濾波器,PLL1 的環路濾波器帶寬應控制在 10 Hz 至 200 Hz,以抑制系統或輸入時鐘的噪聲;PLL2 的環路濾波器帶寬應設計在 50 kHz 至 200 kHz 范圍內,以充分利用內部 VCO 的低帶內相位噪聲和低高頻偏移相位噪聲特性。設計環路濾波器時,要考慮參考時鐘的相位噪聲、VCXO 相位噪聲和相位檢測器頻率等因素,可參考 National 的 Clock Conditioner Owner’s Manual 和使用 Clock Design Tool 進行模擬設計。

6.3 電源供應和熱管理

為了保證器件的性能和可靠性,要采用合適的電源供應技術。建議將時鐘輸出的電源引腳連接到專用電源平面,其他電源引腳連接到另一個電源平面。同時,由于該系列器件的功耗可能較高,需要注意熱管理,將芯片的管芯溫度限制在 125 °C 以下。可通過在 PCB 上設計熱焊盤和多個過孔連接到接地層,以及在 PCB 另一側設計銅面積較大的區域作為散熱片等方式來提高散熱效果。

6.4 晶體振蕩器實現

該系列產品支持使用外部晶體實現離散振蕩器。在選擇晶體時,需要根據電路的負載電容要求來確定晶體的負載電容值。負載電容由調諧電容、OSCin 端口的輸入電容和 PCB 寄生電容組成。同時,要注意晶體的等效串聯電阻(ESR)和功耗能力,確保振蕩器電路能夠正常啟動和穩定工作。

6.5 時鐘輸出端接和使用

為了實現最佳的相位噪聲和抖動性能,在終端時鐘驅動器時,要遵循傳輸線理論,進行良好的阻抗匹配,防止反射。不同類型的時鐘驅動器(如 LVDS、LVPECL)需要提供適當的負載,接收器需要偏置到其指定的直流偏置電平(共模電壓)。對于不同的耦合方式(DC 耦合、AC 耦合)和操作模式(差分操作、單端操作),需要采用不同的端接方法,如 DC 耦合的 LVDS 驅動器需要用 100 Ω 電阻端接到接收器附近,AC 耦合的 LVPECL 驅動器需要用 120 Ω 發射極電阻提供接地直流路徑等。

7. 編程與配置

7.1 寄存器編程

LMK040xx 器件使用多個 32 位寄存器進行編程,每個寄存器由 4 位地址字段和 28 位數據字段組成。編程時,數據按 MSB 優先的順序在 CLK 信號的上升沿時鐘輸入,最后通過 LE 信號的跳變將數據鎖存到所選寄存器中。為了實現正確的頻率校準,需要在編程寄存器 15 之前確保 OSCin 端口有有效信號輸入;當 PLL2_R 計數器或 OSCin 端口信號發生變化時,需要重新加載寄存器 15 以激活頻率校準過程。

7.2 推薦編程順序

推薦的編程順序是先將寄存器 R7 的復位位設置為 1,確保器件處于默認狀態;然后根據需要編程寄存器 R0 至 R4,配置時鐘輸出;接著將寄存器 R5、R6、R8 至 R10 編程為默認值;再編程寄存器 R11 配置參考時鐘輸入,寄存器 R12 配置 PLL1,寄存器 R13 至 R15 配置 PLL2 參數、晶體模式選項和全局功能;最后編程寄存器 R15。

7.3 寄存器功能

不同的寄存器控制著器件的不同功能,如寄存器 R0 至 R4 控制五個時鐘輸出的相關參數(分頻、延遲、使能等),寄存器 R11 控制 PLL1 參考時鐘的輸入類型、選擇模式和 LOS 檢測等,寄存器 R12 配置 PLL1 的電荷泵增益、極性和計數器值等,寄存器 R13 控制晶體振蕩器選項、Fout 使能、全局時鐘使能等,寄存器 R14 配置 PLL2 參考輸入頻率和 LD 引腳輸出選擇等,寄存器 R15 配置 PLL2 的計數器值、電荷泵增益和 VCO 分頻等。

8. 總結

LMK04000 系列低噪聲時鐘抖動清除器憑借其先進的級聯 PLL 架構、超低的 RMS 抖動性能、多種輸出類型和靈活的配置選項,為各種對時鐘精度要求較高的應用提供了優秀的解決方案。在設計過程中,工程師需要充分了解其電氣特性、典型性能特性和應用設計要點,合理進行系統布局、環路濾波器設計、電源供應和熱管理等方面的工作,同時正確進行器件的編程和配置,以確保系統的性能和穩定性。

大家在使用 LMK04000 系列產品的過程中,有沒有遇到一些特別的問題或者有什么獨特的設計經驗呢?歡迎在評論區分享交流!

-

應用設計

+關注

關注

0文章

278瀏覽量

8637

發布評論請先 登錄

LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南

LMK04000 系列低噪聲時鐘抖動清除器:功能、應用與設計指南

評論