LMK5B12212網絡同步器:以太網網絡應用的高性能解決方案

在以太網網絡應用領域,對于高性能網絡同步器和抖動清理器的需求日益增長。TI推出的LMK5B12212正是滿足這一需求的優秀產品,下面我們就來詳細了解一下它。

文件下載:lmk5b12212.pdf

核心特性:超低抖動與高性能鎖相環

超低抖動BAW VCO時鐘

LMK5B12212采用了超低抖動的BAW VCO(體聲波壓控振蕩器)技術,這使得它在時鐘性能上表現卓越。在不同頻率下,它的典型RMS抖動表現出色,如在625MHz時,典型RMS抖動僅為13fs(搭配4MHz 1st order HPF),在312.5MHz時,典型RMS抖動為24fs(同樣搭配4MHz 1st order HPF)。這種超低抖動特性能夠有效減少信號傳輸中的誤差,提高數據傳輸的準確性和穩定性。

高性能鎖相環配置

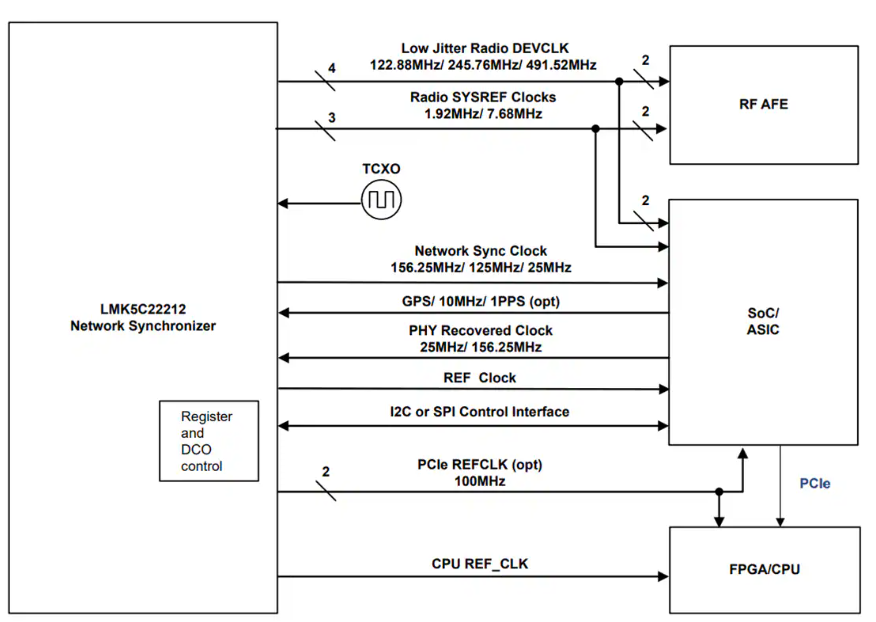

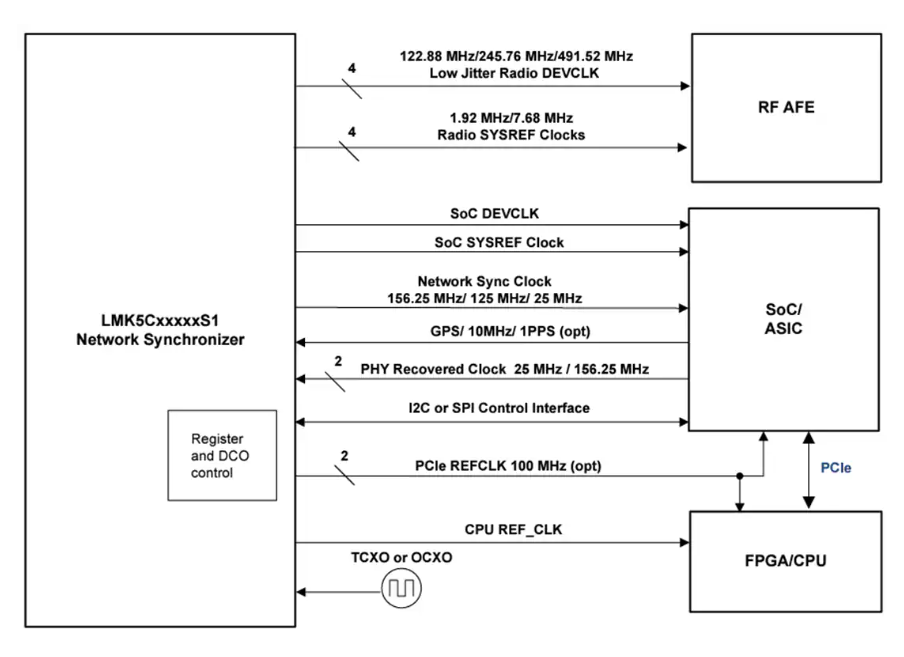

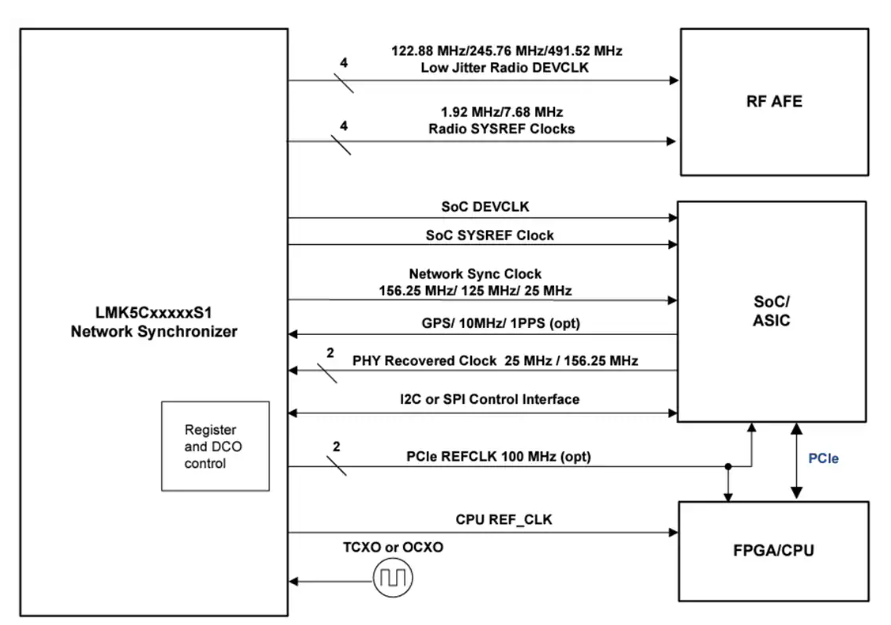

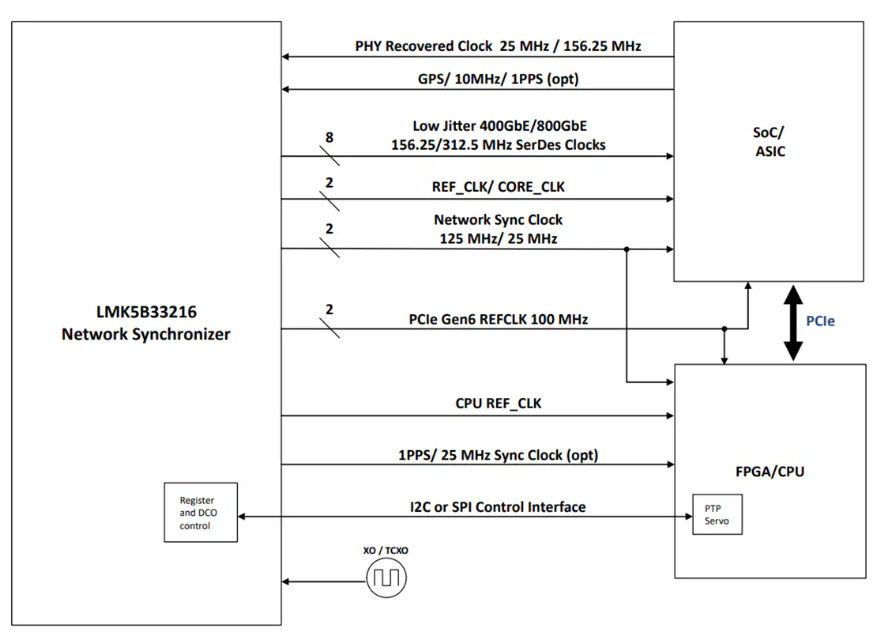

它集成了1個高性能數字鎖相環(DPLL)和2個模擬鎖相環(APLLs)。DPLL的環路濾波器帶寬可編程,范圍從1mHz到4kHz,并且DCO頻率調整步長小于1ppt,這為精確的頻率控制提供了可能。同時,它具有2個差分或單端DPLL輸入,支持1Hz(1PPS)到800MHz的輸入頻率,還具備數字保持和無縫切換功能,確保在不同輸入條件下都能穩定工作。

豐富的輸出配置

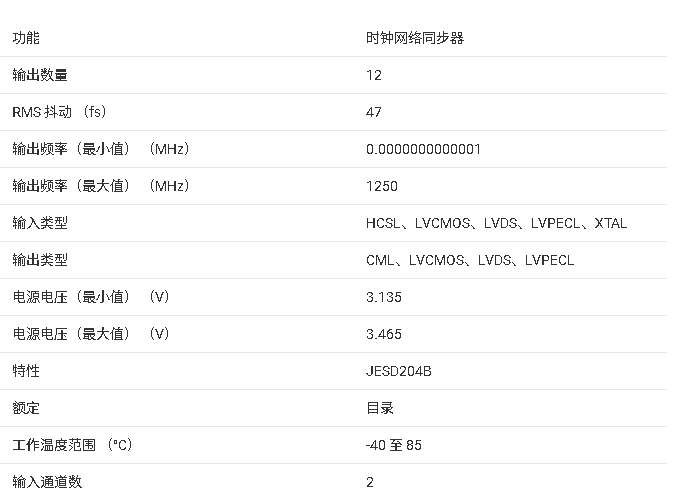

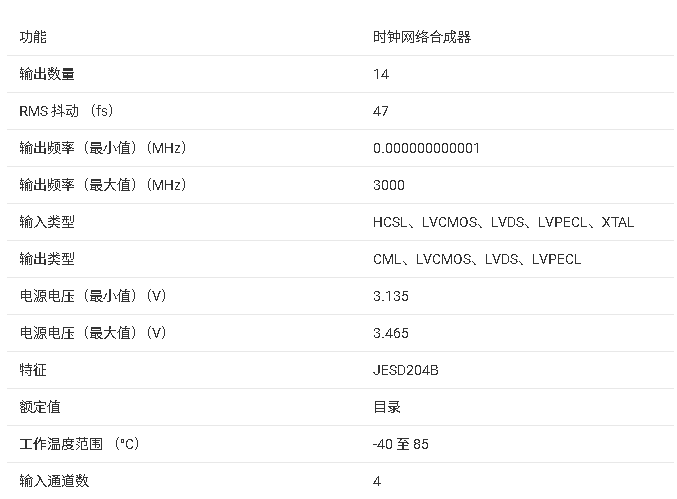

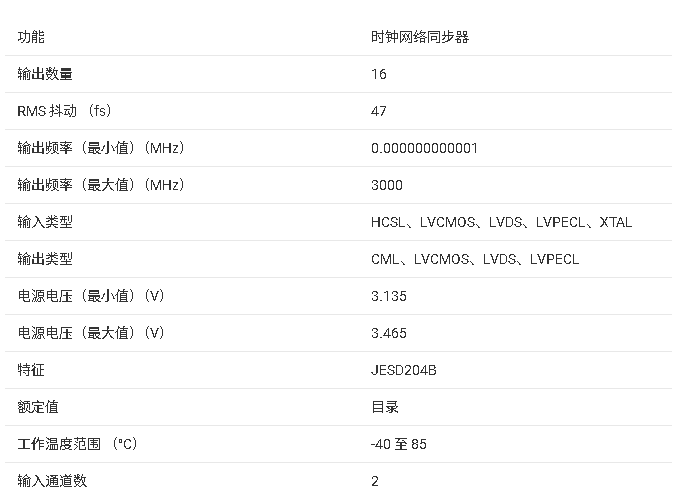

該器件擁有12個差分輸出,輸出格式可編程,包括HSDS、AC - LVPECL、LVDS和HSCL等。當配置為6個LVCMOS頻率輸出和10個差分輸出時,總共可提供多達16個頻率輸出。輸出頻率范圍為1Hz(1PPS)到1250MHz,并且輸出擺幅和共模電壓可編程,能夠滿足不同應用場景的需求。此外,它還兼容PCIe Gen 1到6,通信接口支持I2C或3 - 線/4 - 線SPI,方便與其他設備進行連接和通信。

廣泛應用:多領域的精準同步

有線網絡領域

在有線網絡中,LMK5B12212可用于數據中心互連、定時卡、線路卡等設備。它支持SyncE(G.8262)、SONET/SDH(Stratum 3/3E,G.813,GR - 1244,GR - 253)、IEEE - 1588 PTP二級時鐘等標準,能夠實現抖動清理、漂移衰減和參考時鐘生成,為112G/224G PAM - 4 SerDes、100G - 800G數據中心交換機、核心路由器、邊緣路由器和WLAN等設備提供精確的時鐘信號。

數據中心與企業計算

在數據中心和企業計算中,智能網絡接口卡(NIC)和光傳輸網絡(OTN G.709)等設備對時鐘的準確性和穩定性要求極高。LMK5B12212能夠滿足這些需求,確保數據的高效傳輸和處理。

其他領域

此外,它還可應用于寬帶固定線路接入、工業、測試與測量、醫療成像等領域,展現出了其廣泛的適用性。

技術原理:多鎖相環協同工作

PLL架構

LMK5B12212的PLL架構由數字PLL(DPLL1)和模擬PLL(APLL1)組成主通道,APLL1采用了集成的BAW VBCO(VCO1),而APLL2則集成了LC VCO(VCO2),可以生成輔助頻率域。DPLL由時間 - 數字轉換器(TDC)、數字環路濾波器(DLF)和可編程40位分數反饋(FB)分頻器組成,APLLs則由參考(R)分頻器、相位 - 頻率檢測器(PFD)、環路濾波器(LF)、分數反饋(N)分頻器和VCO組成。

DPLL工作模式

DPLL有多種工作模式,如獨立DPLL操作、APLL級聯DPLL等。在獨立DPLL操作中,DPLL可以選擇參考輸入,當檢測到有效參考輸入時,開始鎖定過程。在APLL級聯DPLL模式下,使用VCBO作為級聯源為APLL提供高頻、超低抖動的參考時鐘,能夠提高近端相位噪聲性能。

APLL工作模式

APLL在自由運行模式下,BAW APLL使用XO輸入作為VCBO的初始參考時鐘,PFD比較分數 - N分頻時鐘和參考時鐘,生成控制信號,經過環路濾波器生成控制電壓來設置VCBO輸出頻率。在DPLL模式下,APLL分數SDM由DPLL環路控制,使VCO頻率與DPLL參考輸入鎖定。

設計要點:從輸入到輸出的全面考量

輸入接口設計

振蕩器輸入(XO)

XO輸入是分數 - N APLLs的參考時鐘,對于DPLL的正常工作,XO頻率與VCO頻率必須具有非整數關系,以確保APLL N分頻器具有分數分頻比。同時,該輸入支持可編程的片上輸入端接和交流耦合輸入偏置配置,以適應不同的時鐘接口類型。

參考輸入

參考輸入(IN0和IN1)可以接受差分或單端時鐘,每個輸入都有可編程的輸入類型、端接和交流/直流耦合輸入偏置配置。DPLL的參考輸入多路復用器支持自動輸入選擇和手動輸入選擇,用戶可以根據實際需求進行配置。

輸出接口設計

時鐘輸出

每個時鐘輸出(OUTx_P和OUTx_N)可以單獨配置為差分輸出驅動器,OUT0或OUT1還可以額外配置為兩個1.8V或2.65V LVCMOS輸出驅動器。輸出具有可編程的延遲功能,可以調整輸出時鐘的相位。同時,輸出支持自動靜音功能,當所選輸出多路復用器時鐘源無效時,輸出驅動器可以自動靜音。

輸出同步

輸出同步(SYNC)功能可以使兩個或多個輸出時鐘在相同的PLL輸出時鐘周期上退出復位,實現相位對齊。用戶可以通過硬件引腳或軟件位觸發SYNC事件,確保輸出時鐘的同步性。

電源設計

在電源設計方面,要注意電源的旁路電容放置,可將其放置在PCB的背面或元件面。同時,要確保所有VDD和VDDO電源由相同的3.3V電源軌驅動,并且在單調上升時,從0V到3.135V的時間小于1ms。如果電源上升緩慢或非單調,建議延遲VCO校準,直到所有核心電源上升到3.135V以上。

編程與配置:靈活定制工作模式

內存空間

LMK5B12212具有四個內存空間,分別是寄存器、ROM、EEPROM和SRAM。寄存器包含設備當前使用的活動寄存器設置;ROM包含所有寄存器設置,但默認ROM頁面不可由用戶編程;EEPROM包含部分寄存器設置,可以通過I2C或SPI進行多次編程;SRAM用于編程EEPROM。

編程方法

用戶可以使用TICS Pro編程軟件進行配置,該軟件提供了逐步的設計流程,幫助用戶輸入設計參數、計算頻率計劃并生成所需配置的寄存器設置。用戶還可以通過I2C或SPI接口對設備進行編程,實現對設備的靈活控制。

總結

LMK5B12212以其卓越的性能、廣泛的應用場景和靈活的配置方式,成為以太網網絡應用中高性能網絡同步和抖動清理的理想選擇。在實際設計中,電子工程師需要綜合考慮輸入輸出接口設計、電源設計和編程配置等方面,以充分發揮該器件的優勢,為不同的應用場景提供精確、穩定的時鐘解決方案。大家在使用過程中遇到任何問題,都可以在評論區交流討論。

-

以太網網絡

+關注

關注

0文章

6瀏覽量

5375 -

網絡同步器

+關注

關注

0文章

35瀏覽量

3021

發布評論請先 登錄

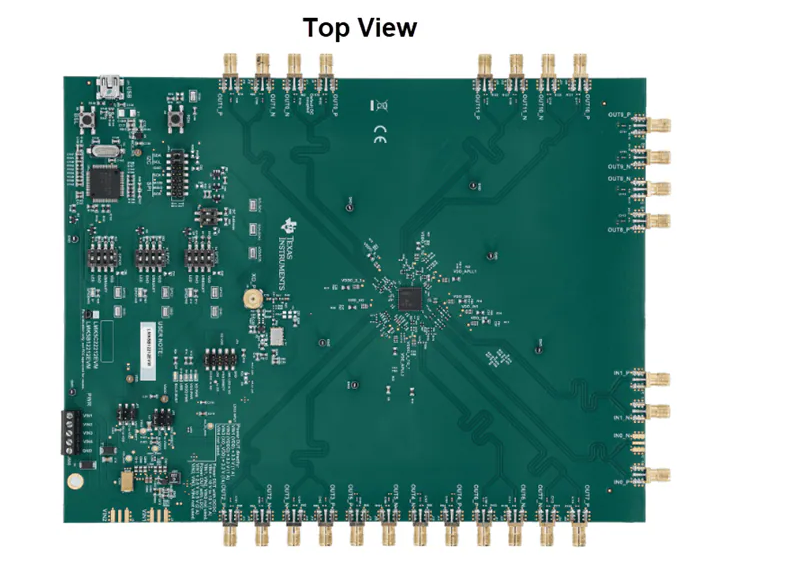

Texas Instruments LMK5B12212EVM 評估模塊(EVM)特性/應用/布局

LMK5B12212網絡同步器:以太網網絡應用的高性能解決方案

LMK5B12212網絡同步器:以太網網絡應用的高性能解決方案

評論