LMK05318B-Q1:高性能網絡同步器的深度解析

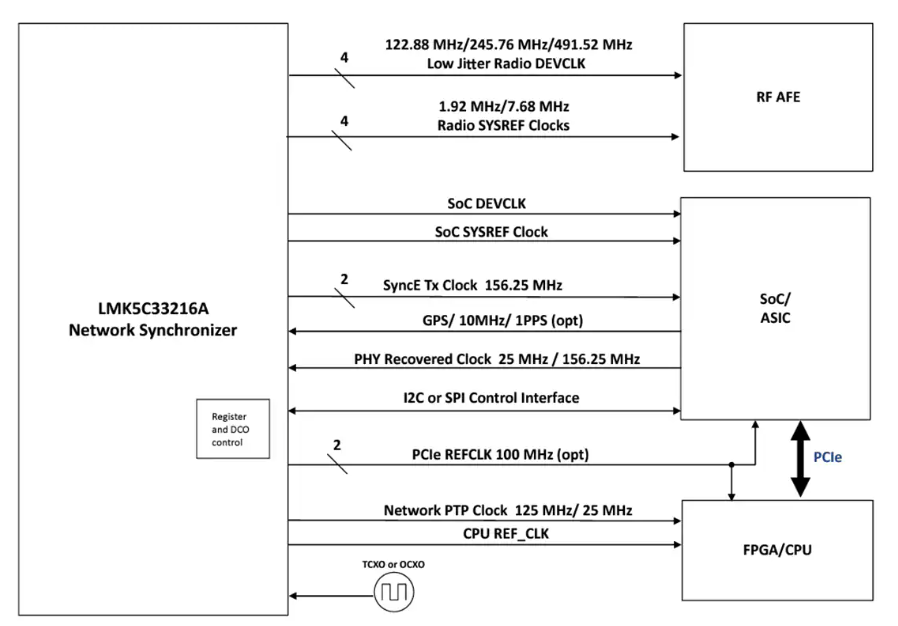

在當今高速發展的電子領域,以太網網絡應用對時鐘同步和抖動控制提出了極高要求。LMK05318B-Q1作為一款高性能網絡同步器和抖動清理器,專為滿足這些嚴苛需求而設計。本文將深入探討它的特性、應用、工作原理以及設計要點。

文件下載:lmk05318b-q1.pdf

1. 特性亮點

1.1 汽車級認證與寬溫范圍

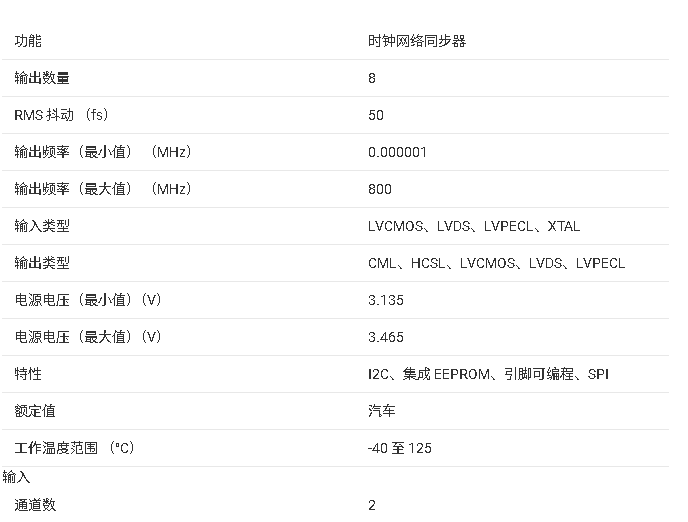

LMK05318B-Q1通過了AEC - Q100汽車應用認證,可在 - 40°C至105°C的寬溫度范圍內穩定工作,這為汽車電子系統的可靠性提供了有力保障。

1.2 超低抖動性能

采用超低抖動BAW VCO技術,在312.5MHz時典型RMS抖動僅為32fs(搭配4MHz一階高通濾波器),在不同頻率下都展現出出色的抖動控制能力,有效降低了高速串行鏈路中的誤碼率。

1.3 靈活的鎖相環架構

集成一個數字鎖相環(DPLL)和兩個模擬鎖相環(APLLs),提供無中斷切換和抖動衰減功能。APLL1使用BAW VCO,可產生典型RMS抖動為50fs的312.5MHz輸出時鐘,且不受DPLL參考輸入頻率和抖動特性的影響;APLL2則使用傳統LC VCO,提供了更多頻率和同步域的選擇。

1.4 豐富的輸入輸出接口

具備兩個差分或單端DPLL輸入,頻率范圍從1Hz(1PPS)到800MHz,支持數字保持和無中斷切換。八個差分輸出可選擇多種輸出格式,如LVPECL、CML、LVDS、HSCL和1.8V LVCMOS,輸出頻率范圍為1Hz(1PPS)到1250MHz,并且兼容PCIe Gen 1到6。

1.5 多種通信接口與電源配置

支持I2C、3線SPI或4線SPI通信接口,方便與外部設備進行通信和配置。采用3.3V核心電源和1.8V、2.5V或3.3V輸出電源,為不同應用場景提供了靈活的電源解決方案。

2. 應用領域

2.1 通信網絡

適用于SyncE(G.8262)、SONET/SDH(Stratum 3/3E、G.813、GR - 1244、GR - 253)、IEEE 1588 PTP從時鐘等網絡同步應用,為高速數據傳輸提供穩定的時鐘信號。

2.2 工業與醫療

在56G/112G PAM4 SerDes的抖動清理、漂移衰減和參考時鐘生成中發揮重要作用。同時,也可應用于工業測試測量和醫療成像等領域,滿足對高精度時鐘的需求。

2.3 汽車電子

在先進駕駛輔助系統(ADAS)、信息娛樂系統、集群顯示、車身電子和照明等汽車電子系統中,為各個模塊提供精確的時鐘同步,確保系統的穩定運行。

3. 工作原理與架構

3.1 鎖相環架構

DPLL由時間 - 數字轉換器(TDC)、數字環路濾波器(DLF)和40位分數反饋(FB)分頻器組成。APLLs則包括參考(R)分頻器、相位 - 頻率檢測器(PFD)、環路濾波器(LF)、分數反饋(N)分頻器和VCO。APLL2可選擇鎖定到APLL1的VCO域或XO輸入,為系統提供了更多的時鐘生成選擇。

3.2 工作模式

3.2.1 DPLL模式

在DPLL模式下,外部XO輸入源決定了輸出時鐘的自由運行和保持頻率的穩定性和準確性。BAW VCO1決定了APLL1輸出時鐘在12kHz至20MHz積分帶內的相位噪聲和抖動性能。當APLL2級聯時,VCO2跟蹤VCO1域,實現時鐘域的同步;當APLL2非級聯時,VCO2獨立鎖定到XO輸入。

3.2.2 APLL - 僅模式

該模式下,APLL1和APLL2的工作原理與DPLL模式類似,但DPLL模塊不參與工作。APLL2級聯時,可利用VCO1的低抖動特性,降低APLL2的帶內相位噪聲或抖動影響。

3.3 參考輸入與監控

DPLL的參考輸入多路復用器可通過內部狀態機自動選擇或通過軟件或引腳控制手動選擇輸入。每個參考輸入都有獨立的監控模塊,包括幅度、頻率、缺失脈沖、矮脈沖和1PPS相位驗證檢測器,確保輸入時鐘的有效性和穩定性。

3.4 輸出時鐘分布

八個輸出通道具有可編程的輸出驅動器,可選擇PLL1或PLL2的VCO時鐘源。輸出分頻器具有SYNC功能,可實現多個輸出的相位對齊。同時,支持輸出自動靜音功能,在PLL鎖定丟失時自動靜音輸出時鐘,避免產生干擾信號。

4. 設計要點與注意事項

4.1 電源設計

所有VDD核心電源必須使用相同的3.3V電源軌,輸出電源可根據需要選擇1.8V、2.5V或3.3V。在電源上電時,要確保電源的單調性和穩定性,避免VCO校準失敗。對于非單調或緩慢上電的情況,可通過延遲PDN引腳的上升沿或在所有核心電源穩定后進行軟復位來觸發VCO校準。

4.2 時鐘輸入與輸出接口

時鐘輸入和輸出接口需要進行適當的阻抗匹配和端接,以減少信號反射和干擾。對于不同類型的時鐘信號,如LVCMOS、LVDS、LVPECL等,要根據其特點選擇合適的接口電路。同時,要注意輸入時鐘的上升沿速率,建議最小上升沿速率為0.5V/ns,以保證抖動性能。

4.3 寄存器編程

使用TICS Pro軟件工具進行寄存器配置和頻率規劃,可大大簡化設計過程。在編程時,要注意寄存器的寫入順序和掩碼設置,避免誤操作。對于EEPROM編程,可采用寄存器提交或直接寫入SRAM的方法,確保配置數據的正確存儲。

4.4 布局布線

在PCB布局時,要將輸入、XO和輸出時鐘與其他不同頻率的時鐘和動態信號隔離,避免相互干擾。同時,要合理放置旁路電容和外部電容,確保電源的穩定性。對于高頻時鐘信號,要采用阻抗控制的布線方式,減少信號損耗。

5. 總結

LMK05318B-Q1憑借其超低抖動、靈活的鎖相環架構、豐富的接口和強大的監控功能,成為以太網網絡應用中時鐘同步和抖動控制的理想選擇。在設計過程中,我們需要充分考慮其特性和要求,合理進行電源設計、接口匹配、寄存器編程和布局布線,以發揮其最佳性能。希望本文能為電子工程師在使用LMK05318B-Q1進行設計時提供有價值的參考。你在使用這款芯片的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

網絡同步器

+關注

關注

0文章

35瀏覽量

2831

發布評論請先 登錄

LMK05318具有兩個頻域的超低抖動網絡同步器時鐘數據表

LMK05318 帶BAW的超低抖動單通道網絡同步器時鐘技術手冊

LMK05318B-Q1:高性能網絡同步器的深度解析

LMK05318B-Q1:高性能網絡同步器的深度解析

評論