Texas Instruments LMK5B33216網絡同步器和抖動清除器設計用于滿足基于以太網的網絡應用的嚴格要求,計時精度 < 5ns(D類)。該網絡同步器集成了三個DPLL,可提供無中斷切換。它還具有抖動衰減、可編程環路帶寬和無外部環路濾波器。該特性可最大限度地提高靈活性和易用性。每個DPLL相位將配對的APLL鎖定到參考輸入。APLL3采用TI專有的體聲波 (BAW) 技術,具有超高性能PLL。無論DPLL基準輸入頻率和抖動特性如何,均可生成312.5MHz輸出時鐘,RMS抖動為42fs(典型值)/60fs(最大值)。APLL2和APLL1提供了用于第二或第三頻率和/或同步域的選項。

數據手冊:*附件:Texas Instruments LMK5B33216網絡同步器和抖動清除器數據手冊.pdf

參考驗證電路監視DPLL參考時鐘,并在檢測到切換事件時在它們之間執行無中斷切換。可以啟用零延遲和相位構建,以控制從輸入到輸出的相位關系。該器件可通過I^2^C或SPI接口完全編程。板載EEPROM可用于定制系統啟動時鐘。Texas Instruments LMK5B33216還具有出廠默認ROM配置文件作為回退選項。

特性

- 超低抖動BAW基于VCO的以太網時鐘

- RMS抖動:42fs典型值/60fs最大值(312.5MHz時)

- RMS抖動:47fs典型值/65fs最大值(156.25MHz時)

- 三個高性能數字鎖相環 (DPLL),帶配對模擬鎖相環 (APLL)

- 可編程DPLL環路帶寬:1mHz到4kHz

- DCO頻率調整步長:<1ppt

- 2個差分或單端DPLL輸入

- 輸入頻率范圍:1Hz (1PPS) 至800MHz

- 數字保持和無中斷切換

- 16個差分輸出,具有可編程HDS/LVPECL、LVDS和HSCL輸出格式

- 配置6個LVCMOS頻率輸出時,多達20個總頻率輸出

- 輸出頻率:1Hz (1PPS) 至1250MHz,帶可編程擺幅和共模

- 符合PCIe Gen 1至6標準

- I^2^C或3線/4線SPI接口

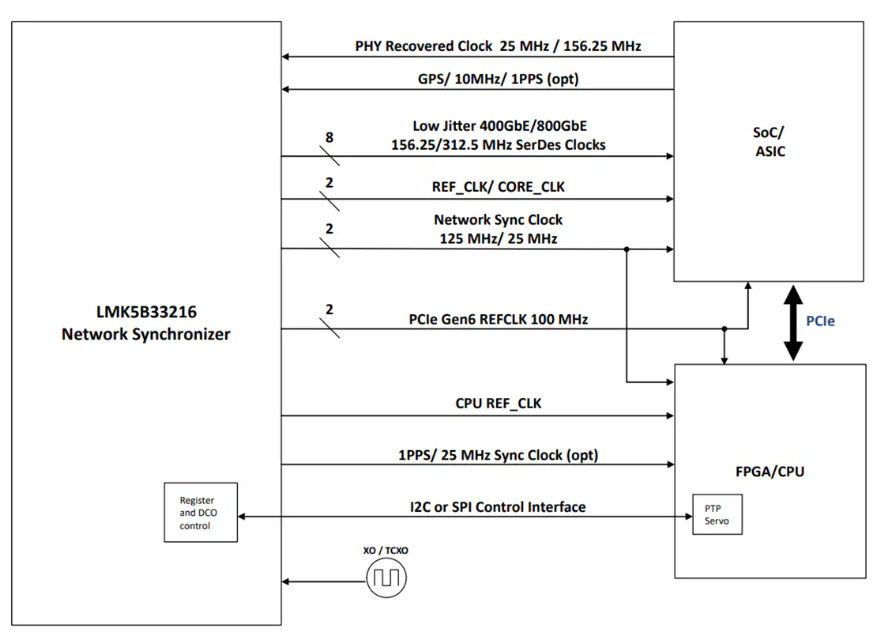

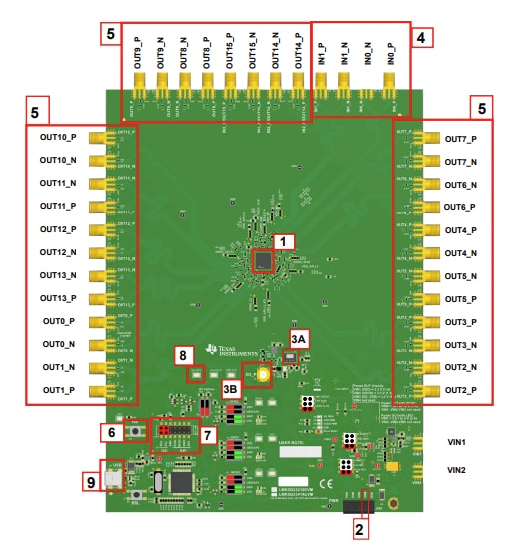

系統方框圖

?基于LMK5B33216網絡同步器的時鐘系統設計與應用?

一、引言

在現代通信和網絡設備中,高精度時鐘同步是確保數據傳輸可靠性和系統性能的關鍵。Texas Instruments推出的LMK5B33216是一款高性能網絡同步器和抖動清除器,專為以太網應用設計,具備超低抖動、多PLL架構和靈活的輸出配置。本文將從核心特性、應用場景及設計要點三個方面展開分析。

二、核心特性

- ?超低抖動性能?

- 采用BAW(體聲波)VCO技術,典型RMS抖動低至13fs(625MHz,4MHz高通濾波)和24fs(312.5MHz),滿足高速SerDes和PCIe Gen 6的嚴苛要求。

- 支持三路數字鎖相環(DPLL)和模擬鎖相環(APLL),可編程帶寬范圍1mHz至4kHz,適應不同同步場景。

- ?靈活的輸入輸出配置?

- ?高集成度與低功耗?

- 集成EEPROM存儲自定義啟動配置,支持I2C/SPI控制接口,工作溫度范圍-40°C至85°C。

- 典型功耗850mA(全輸出啟用),支持按需關閉未使用模塊以節能。

三、典型應用場景

- ?數據中心與交換機?

- 為100G-800G交換機提供低抖動時鐘,支持SyncE(G.8262)和IEEE-1588協議,滿足時間敏感網絡(TSN)需求。

- 通過Zero-Delay Mode(ZDM)實現輸入輸出相位對齊,適用于1PPS同步。

- ? 光傳輸網絡(OTN) ?

- 符合G.709標準,通過APLL級聯實現多域時鐘同步,降低參考時鐘抖動對系統的影響。

- ?工業與醫療設備?

- 在測試儀器和醫療成像中,利用其高穩定性(±100ppm VCO調諧范圍)和快速鎖相能力(APLL鎖定時長35ms)。

四、設計要點與建議

-

以太網

+關注

關注

41文章

5997瀏覽量

180806 -

清除器

+關注

關注

0文章

56瀏覽量

6087 -

同步器

+關注

關注

1文章

117瀏覽量

15653

發布評論請先 登錄

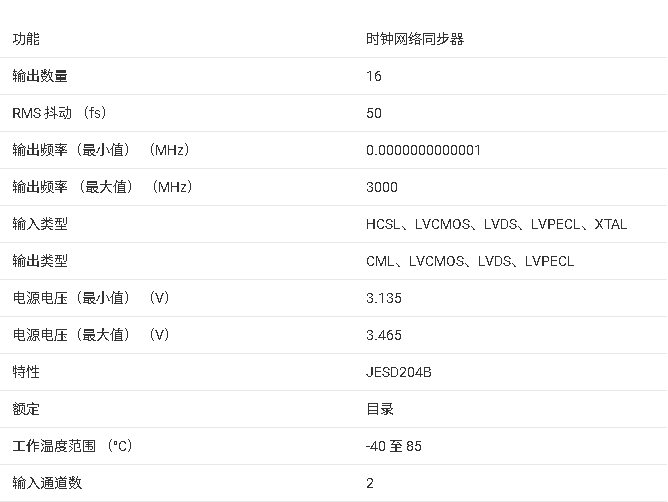

LMK5B33216 3 DPLL、3 APLL、2路輸入、16路輸出網絡同步器數據表

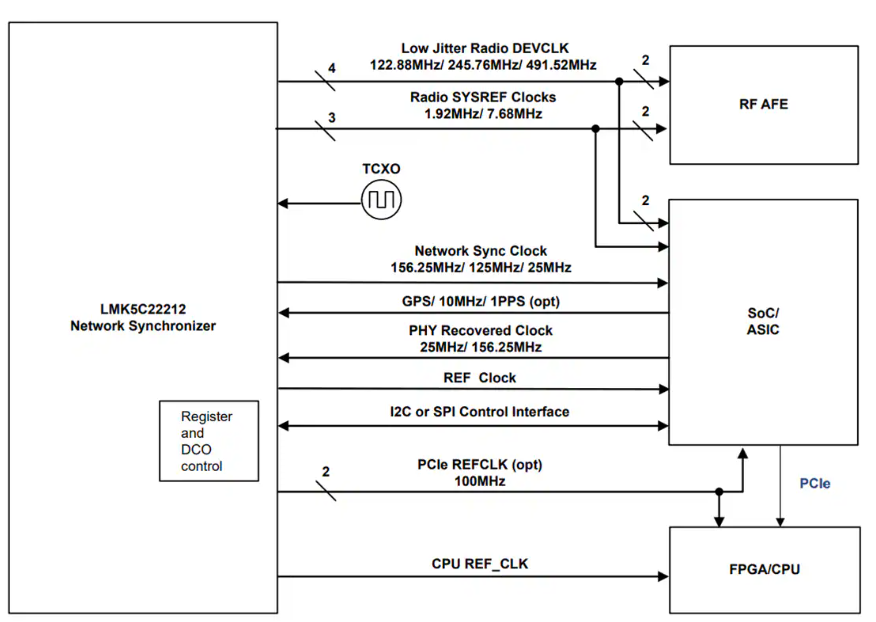

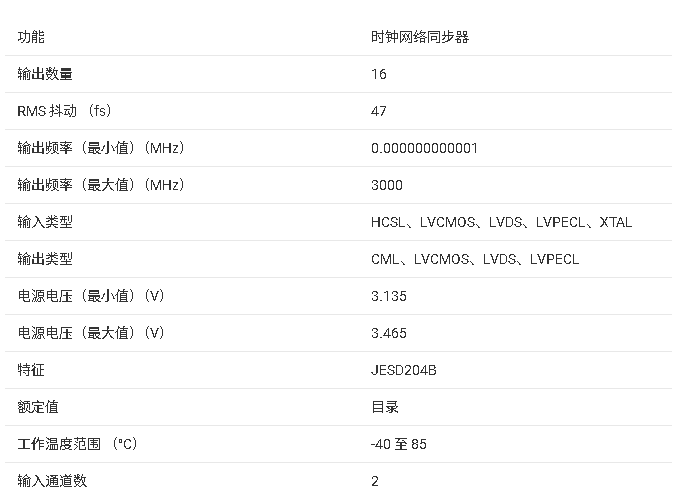

采用JESD204B的LMK5C33216超低抖動時鐘同步器數據表

?基于LMK5B33216網絡同步器的時鐘系統設計與應用

?基于LMK5B33216網絡同步器的時鐘系統設計與應用

評論