本文要點

容性耦合噪聲取決于電路中的電壓變化和耦合電容的值,其中耦合電容受兩個電路之間距離的影響。

雜散電容會增大耦合電容值。如果減少或消除雜散電容,耦合電容值會隨之降低,從而抑制電路中的容性耦合噪聲。

常用的容性耦合噪聲抑制方法是采用屏蔽裝置,例如法拉第籠,可有效減少耦合干擾。

#

電路中的模擬信號有時與數(shù)字信號會發(fā)生混合。多數(shù)情況下,這種混合源于噪聲耦合——無論是容性噪聲耦合還是感性噪聲耦合。在電路中,此類耦合噪聲稱為串擾,即一種共模干擾。防止信號混合至關重要,為此,我們可以采用容性耦合噪聲抑制方法。

電路中的耦合噪聲稱為串擾

容性耦合噪聲

當兩個電路或導線彼此靠近時,它們之間會形成固有電容。該電容構成一條導電路徑,使信號在線路之間混合,從而將噪聲引入電路。這類容性耦合噪聲也可稱為電場耦合或近場干擾。

容性耦合噪聲取決于電路中的電壓變化和耦合電容值。耦合電容受兩個電路之間距離的影響。距離越近,耦合電容越大,距離越遠,耦合電容越小。耦合電容也可稱為互容。

容性耦合噪聲抑制方法

抑制容性耦合噪聲的最佳方法是減小耦合電容。如上所述,耦合電容與電路之間的距離成反比,因此,我們可以增加兩個電路之間的距離。然而,隨著電路日益小型化,這種方法往往不具可行性。在這種情況下,我們可以考慮以下推薦的方法。

屏蔽

常用的抑制容性耦合噪聲方法是采用屏蔽裝置,例如法拉第籠,可有效減少耦合干擾。將屏蔽裝置放在電容耦合的電路之間,并在信號源連接點之外的位置進行接地,將噪聲電流直接導入大地。使用法拉第籠時,必須將屏蔽裝置接地。若處于開路或懸浮狀態(tài),可能會增加系統(tǒng)中的容性耦合噪聲。

限制平行導線長度

兩條平行導線之間會形成天然的電容器。兩條導線充當電容器的極板,空氣作為電介質。限制平行導線的長度可以降低耦合電容值。

高 DV/DT 信號

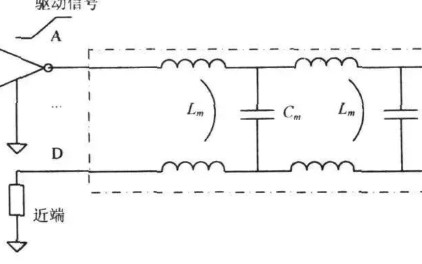

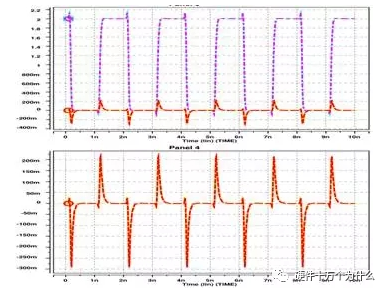

在開關電路中,高 dv/dt 信號是耦合電容的來源。它們大多會在開關點與地之間形成耦合電容,從而引發(fā)共模干擾噪聲。通過降低信號的 dv/dt 值或增加信號上升時間,可有效抑制由此產(chǎn)生的容性耦合噪聲。

接地方式

在電路中采用適當?shù)慕拥胤桨?/strong>,是抑制容性耦合噪聲的首選方法。選擇單點、多點或混合接地等接地方法時,需要考慮電路規(guī)格,尤其是工作頻率。

走線長度

在電路板中,縮短走線長度是抑制容性耦合噪聲的有手段。此外,均衡輸入引線長度也有助于降低耦合電容。

雜散電容

雜散電容會增大耦合電容值。如果減少或消除雜散電容,耦合電容值也會隨之降低,從而抑制電路中的容性耦合噪聲。

其他降噪手段

除了上文討論的容性耦合噪聲抑制方法外,也可采用其他降噪技術,通過將信號線絞合來減小電容,是另一種可行的噪聲抑制手段。不過,應當審慎采用降噪技術,以免引發(fā)其他電路問題。

當電路間距離較近時,容性耦合噪聲的抑制至關重要。點擊下圖查看白皮書,了解Cadence Sigrity X 所提供的兼顧電源影響的信號完整性分析,可以如何將反射、串擾、時序和其它效應一起進行分析,最終使產(chǎn)品與規(guī)格相符,并實現(xiàn)更好的性能。

-

電路

+關注

關注

173文章

6080瀏覽量

178612 -

串擾

+關注

關注

4文章

196瀏覽量

27856

發(fā)布評論請先 登錄

什么是串擾?如何減少串擾?

技術資訊 I 容性耦合噪聲抑制方法如何減少串擾

技術資訊 I 容性耦合噪聲抑制方法如何減少串擾

評論